Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 13x10b/12b; D/A 2x16b                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp804-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

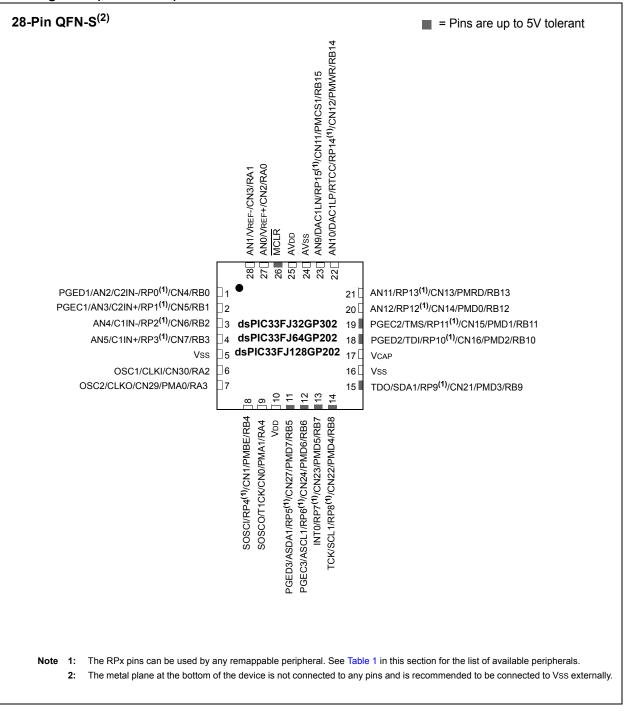

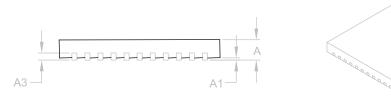

#### Pin Diagrams (Continued)

#### TABLE 4-19: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1(FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/804) (CONTINUED)

| File Name  | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7                   | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|--------|-----------|--------|--------|--------|--------|-------|----------|-------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11EID | 046E |        | EID<15:8> |        |        |        |        |       |          |                         | EID<7:0> |       |       |       |       |       |       | XXXX          |

| C1RXF12SID | 0470 |        | SID<10:3> |        |        |        |        |       |          | SID<2:0>                |          | _     | EXIDE |       | EID<1 | 7:16> | xxxx  |               |

| C1RXF12EID | 0472 |        | EID<15:8> |        |        |        |        |       | EID<7:0> |                         |          |       |       |       |       | XXXX  |       |               |

| C1RXF13SID | 0474 |        | SID<10:3> |        |        |        |        |       | SID<2:0> |                         | —        | EXIDE | —     | EID<1 | 7:16> | XXXX  |       |               |

| C1RXF13EID | 0476 |        |           |        | EID<   | 15:8>  |        |       |          | EID<7:0>                |          |       |       |       |       |       | XXXX  |               |

| C1RXF14SID | 0478 |        |           |        | SID<   | 10:3>  |        |       |          | SID<2:0> — EXIDE — EID< |          |       |       |       | EID<1 | 7:16> | XXXX  |               |

| C1RXF14EID | 047A |        | EID<15:8> |        |        |        |        |       |          |                         |          | EID<  | 7:0>  |       |       |       | XXXX  |               |

| C1RXF15SID | 047C |        | SID<10:3> |        |        |        |        |       | SID<2:0> |                         | —        | EXIDE | —     | EID<1 | 7:16> | XXXX  |       |               |

| C1RXF15EID | 047E |        |           |        | EID<   | 15:8>  |        |       |          |                         |          |       | EID<  | 7:0>  |       |       |       | XXXX          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: DCI REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12                          | Bit 11 | Bit 10                                                        | Bit 9    | Bit 8       | Bit 7      | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0   |         | Reset Sta | ate     |

|----------|-------|--------|--------|---------|---------------------------------|--------|---------------------------------------------------------------|----------|-------------|------------|-------|-------|-------|-------|---------|---------|---------|---------|-----------|---------|

| DCICON1  | 0280  | DCIEN  | —      | DCISIDL | —                               | DLOOP  | CSCKD                                                         | CSCKE    | COFSD       | UNFM       | CSDOM | DJST  | —     | —     | _       | COFSM1  | COFSM0  | 0000    | 0000 00   | 00 0000 |

| DCICON2  | 0282  | _      | _      |         | _                               | BLEN1  | N1 BLEN0 — COFSG<3:0> — WS<3:0>                               |          |             |            |       |       |       |       | 0000    | 0000 00 | 00 0000 |         |           |         |

| DCICON3  | 0284  | —      | —      | _       | —                               |        | BCG<11:0>                                                     |          |             |            |       |       |       | 0000  | 0000 00 | 00 0000 |         |         |           |         |

| DCISTAT  | 0286  | —      | —      | _       | —                               | SLOT3  | SLOT2                                                         | SLOT1    | SLOT0       | —          | —     | _     | _     | ROV   | RFUL    | TUNF    | TMPTY   | 0000    | 0000 00   | 00 0000 |

| TSCON    | 0288  | TSE15  | TSE14  | TSE13   | TSE12                           | TSE11  | TSE10                                                         | TSE9     | TSE8        | TSE7       | TSE6  | TSE5  | TSE4  | TSE3  | TSE2    | TSE1    | TSE0    | 0000    | 0000 00   | 00 0000 |

| RSCON    | 028C  | RSE15  | RSE14  | RSE13   | RSE12                           | RSE11  | E11 RSE10 RSE9 RSE8 RSE7 RSE6 RSE5 RSE4 RSE3 RSE2 RSE1 RSE0 0 |          |             |            |       |       |       |       | 0000    | 0000 00 | 00 0000 |         |           |         |

| RXBUF0   | 0290  |        |        |         |                                 |        | Receive Buffer 0 Data Register                                |          |             |            |       |       |       |       |         |         | 0000    | 0000 00 | 00 0000   |         |

| RXBUF1   | 0292  |        |        |         |                                 |        |                                                               | Receive  | Buffer 1 Da | ata Regist | er    |       |       |       |         |         |         | 0000    | 0000 00   | 00 0000 |

| RXBUF2   | 0294  |        |        |         |                                 |        |                                                               | Receive  | Buffer 2 Da | ata Regist | er    |       |       |       |         |         |         | 0000    | 0000 00   | 00 0000 |

| RXBUF3   | 0296  |        |        |         |                                 |        |                                                               | Receive  | Buffer 3 Da | ata Regist | er    |       |       |       |         |         |         | 0000    | 0000 00   | 00 0000 |

| TXBUF0   | 0298  |        |        |         |                                 |        |                                                               | Transmit | Buffer 0 Da | ata Regis  | ter   |       |       |       |         |         |         | 0000    | 0000 00   | 00 0000 |

| TXBUF1   | 029A  |        |        |         | Transmit Buffer 1 Data Register |        |                                                               |          |             |            |       |       |       |       | 0000    | 0000 00 | 00 0000 |         |           |         |

| TXBUF2   | 029C  |        |        |         |                                 |        |                                                               | Transmit | Buffer 2 Da | ata Regis  | ter   |       |       |       |         |         |         | 0000    | 0000 00   | 00 0000 |

| TXBUF3   | 029E  |        |        |         |                                 |        |                                                               | Transmit | Buffer 3 Da | ata Regis  | ter   |       |       |       |         |         |         | 0000    | 0000 00   | 00 0000 |

Legend: — = unimplemented, read as '0'.

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 | Interrupt Flag Status bit |

|-------|---------------------------------|---------------------------|

|-------|---------------------------------|---------------------------|

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 IC1IF: Input Capture Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| R/W-0                   | R/W-0                              | U-0                              | U-0             | U-0                      | U-0              | U-0             | U-0   |

|-------------------------|------------------------------------|----------------------------------|-----------------|--------------------------|------------------|-----------------|-------|

| DAC1LIE <sup>(2)</sup>  | DAC1RIE <sup>(2)</sup>             | _                                | _               | —                        | —                | —               |       |

| bit 15                  |                                    |                                  |                 |                          |                  |                 | bit   |

|                         |                                    |                                  |                 |                          |                  |                 |       |

| U-0                     | R/W-0                              | R/W-0                            | R/W-0           | R/W-0                    | R/W-0            | R/W-0           | U-0   |

| —                       | C1TXIE <sup>(1)</sup>              | DMA7IE                           | DMA6IE          | CRCIE                    | U2EIE            | U1EIE           | —     |

| bit 7                   |                                    |                                  |                 |                          |                  |                 | bit   |

| Lowandi                 |                                    |                                  |                 |                          |                  |                 |       |

| Legend:<br>R = Readable | , hit                              | \\/ = \\/ritabla                 | hit             | II – Unimplor            | monted hit read  |                 |       |

| -n = Value at           |                                    | W = Writable<br>'1' = Bit is set |                 | '0' = Bit is cle         | mented bit, read | x = Bit is unkn | 0.000 |

|                         | FUR                                |                                  | L               |                          | aleu             |                 |       |

| bit 15                  | DAC1LIE: DA                        | C Left Channe                    | el Interrupt En | able bit <sup>(2)</sup>  |                  |                 |       |

|                         | 1 = Interrupt r                    |                                  |                 |                          |                  |                 |       |

|                         | 0 = Interrupt r                    | •                                |                 |                          |                  |                 |       |

| bit 14                  | DAC1RIE: DA                        |                                  |                 | nable bit <sup>(2)</sup> |                  |                 |       |

|                         | 1 = Interrupt r                    | •                                |                 |                          |                  |                 |       |

| bit 13-7                | 0 = Interrupt r<br>Unimplement     | •                                |                 |                          |                  |                 |       |

| bit 6                   | •                                  |                                  |                 | nterrupt Enable          | o hit(1)         |                 |       |

|                         | 1 = Interrupt r                    |                                  | •               | nterrupt Enable          |                  |                 |       |

|                         |                                    | equest not occ                   |                 |                          |                  |                 |       |

| bit 5                   | DMA7IE: DM                         | A Channel 7 D                    | ata Transfer C  | Complete Interr          | upt Enable bit   |                 |       |

|                         |                                    | equest enable                    |                 |                          |                  |                 |       |

|                         | -                                  | equest not en                    |                 |                          |                  |                 |       |

| bit 4                   |                                    |                                  |                 | Complete Interr          | upt Enable bit   |                 |       |

|                         | 1 = Interrupt r<br>0 = Interrupt r | equest enable                    |                 |                          |                  |                 |       |

| bit 3                   | CRCIE: CRC                         | •                                |                 | oit                      |                  |                 |       |

| DIL 3                   | 1 = Interrupt r                    |                                  | •               | JIL                      |                  |                 |       |

|                         | 0 = Interrupt r                    |                                  |                 |                          |                  |                 |       |

| bit 2                   | U2EIE: UART                        | 2 Error Interru                  | pt Enable bit   |                          |                  |                 |       |

|                         | 1 = Interrupt r                    | equest enable                    | d               |                          |                  |                 |       |

|                         | 0 = Interrupt r                    | equest not en                    | abled           |                          |                  |                 |       |

| bit 1                   | U1EIE: UART                        |                                  | -               |                          |                  |                 |       |

|                         | 1 = Interrupt r<br>0 = Interrupt r | equest enable                    |                 |                          |                  |                 |       |

|                         |                                    |                                  |                 |                          |                  |                 |       |

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

2: Interrupts are disabled on devices without Audio DAC modules.

| R/W-0          | R/W-0                                    | R/W-0                               | R/W-0               | R/W-0              | U-0           | U-0             | R/W-0 |

|----------------|------------------------------------------|-------------------------------------|---------------------|--------------------|---------------|-----------------|-------|

| T5MD           | T4MD                                     | T3MD                                | T2MD                | T1MD               |               | _               | DCIMD |

| oit 15         |                                          |                                     |                     |                    |               |                 | bit 8 |

| R/W-0          | R/W-0                                    | R/W-0                               | R/W-0               | R/W-0              | U-0           | R/W-0           | R/W-0 |

| I2C1MD         | U2MD                                     | U1MD                                | SPI2MD              | SPI1MD             |               | C1MD            | AD1MD |

| pit 7          | OZINB                                    | 0 mile                              |                     | GITTIND            |               | 0 THE           | bit   |

| Legend:        |                                          |                                     |                     |                    |               |                 |       |

| R = Readabl    | le bit                                   | W = Writable                        | bit                 | U = Unimpleme      | ented bit rea | id as '0'       |       |

| -n = Value at  |                                          | '1' = Bit is set                    |                     | '0' = Bit is clear |               | x = Bit is unkr | nown  |

|                |                                          |                                     |                     |                    |               |                 |       |

| bit 15         |                                          | 5 Module Disat<br>odule is disable  |                     |                    |               |                 |       |

|                |                                          | odule is disable                    |                     |                    |               |                 |       |

| bit 14         |                                          | 4 Module Disat                      | -                   |                    |               |                 |       |

|                | -                                        | odule is disable                    |                     |                    |               |                 |       |

|                | -                                        | odule is enable                     |                     |                    |               |                 |       |

| bit 13         | T3MD: Timer                              | 3 Module Disat                      | ole bit             |                    |               |                 |       |

|                | 1 = Timer3 m                             | odule is disable                    | ed                  |                    |               |                 |       |

|                | 0 = Timer3 m                             | odule is enable                     | d                   |                    |               |                 |       |

| bit 12         | T2MD: Timer                              | 2 Module Disat                      | ole bit             |                    |               |                 |       |

|                | -                                        | odule is disable                    |                     |                    |               |                 |       |

|                |                                          | odule is enable                     |                     |                    |               |                 |       |

| bit 11         | -                                        | 1 Module Disat                      |                     |                    |               |                 |       |

|                | -                                        | odule is disable<br>odule is enable |                     |                    |               |                 |       |

| bit 10-9       |                                          | ted: Read as '                      |                     |                    |               |                 |       |

| bit 8          | -                                        | Module Disable                      |                     |                    |               |                 |       |

|                | -                                        | ule is disabled                     |                     |                    |               |                 |       |

|                | 0 = DCI modu                             |                                     |                     |                    |               |                 |       |

| bit 7          |                                          | 1 Module Disab                      | le bit              |                    |               |                 |       |

|                | $1 = I^2 C1 \mod 1$                      | ule is disabled                     |                     |                    |               |                 |       |

|                | 0 = I <sup>2</sup> C1 mod                | ule is enabled                      |                     |                    |               |                 |       |

| bit 6          |                                          | 2 Module Disa                       |                     |                    |               |                 |       |

|                |                                          | odule is disabl                     |                     |                    |               |                 |       |

|                |                                          | odule is enable                     |                     |                    |               |                 |       |

| bit 5          |                                          | 1 Module Disa                       |                     |                    |               |                 |       |

|                | -                                        | odule is disabl<br>odule is enable  |                     |                    |               |                 |       |

| bit 4          |                                          | 2 Module Disal                      |                     |                    |               |                 |       |

| Dit 4          |                                          | lule is disabled                    |                     |                    |               |                 |       |

|                |                                          | lule is enabled                     |                     |                    |               |                 |       |

| bit 3          |                                          | 1 Module Disal                      | ole bit             |                    |               |                 |       |

|                |                                          | lule is disabled                    |                     |                    |               |                 |       |

|                | 0 = SPI1 mod                             | lule is enabled                     |                     |                    |               |                 |       |

| bit 2          | Unimplemen                               | ted: Read as '                      | o'                  |                    |               |                 |       |

|                | C1MD: ECAN                               | 1 Module Disa                       | ble bit             |                    |               |                 |       |

| bit 1          |                                          | adula ia diaabl                     | ed                  |                    |               |                 |       |

| bit 1          | 1 = ECAN1 m                              | iouule is uisabi                    |                     |                    |               |                 |       |

| bit 1          | -                                        | nodule is enable                    |                     |                    |               |                 |       |

| bit 1<br>bit 0 | 0 = ECAN1 m                              |                                     | ed                  |                    |               |                 |       |

|                | 0 = ECAN1 m<br>AD1MD: AD0<br>1 = ADC1 mo | nodule is enable                    | ed<br>ible bit<br>d |                    |               |                 |       |

# 10.6 Power-Saving Control Registers

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER     | 10-3: PMD3   | B: PERIPHER                      | AL MODULI     | E DISABLE O      | CONTROL RE      | EGISTER 3       |       |

|--------------|--------------|----------------------------------|---------------|------------------|-----------------|-----------------|-------|

| U-0          | U-0          | U-0                              | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0 |

|              | _            | —                                |               | —                | CMPMD           | RTCCMD          | PMPMD |

| bit 15       |              |                                  |               |                  |                 |                 | bit 8 |

| R/W-0        | R/W-0        | U-0                              | U-0           | U-0              | U-0             | U-0             | U-0   |

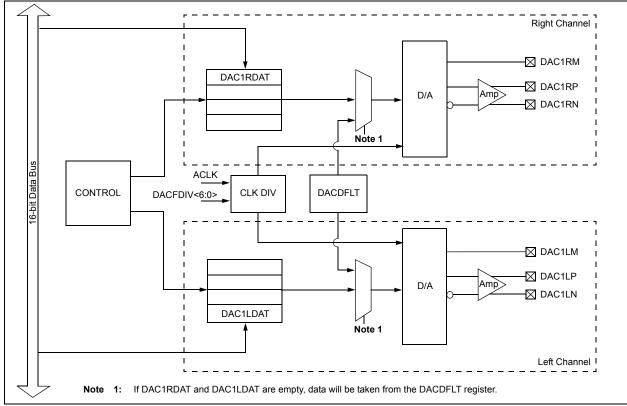

| CRCMD        | DAC1MD       |                                  |               |                  |                 |                 | _     |

| bit 7        | Briomi       |                                  |               |                  |                 |                 | bit ( |

|              |              |                                  |               |                  |                 |                 |       |

| Legend:      |              |                                  |               |                  |                 |                 |       |

| R = Readab   | le bit       | W = Writable b                   | bit           | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value a | t POR        | '1' = Bit is set                 |               | '0' = Bit is cle | eared           | x = Bit is unkn | iown  |

|              |              |                                  |               |                  |                 |                 |       |

| bit 15-11    | Unimplemen   | ted: Read as '0                  | ,             |                  |                 |                 |       |

| bit 10       | CMPMD: Con   | mparator Module                  | e Disable bit |                  |                 |                 |       |

|              |              | tor module is dis                |               |                  |                 |                 |       |

|              | 0 = Comparat | tor module is er                 | abled         |                  |                 |                 |       |

| bit 9        |              | CC Module Dis                    |               |                  |                 |                 |       |

|              |              | dule is disabled                 |               |                  |                 |                 |       |

| 1.11.0       |              | dule is enabled                  |               |                  |                 |                 |       |

| bit 8        |              | P Module Disab                   | ie dit        |                  |                 |                 |       |

|              |              | lule is disabled lule is enabled |               |                  |                 |                 |       |

| bit 7        |              | C Module Disab                   | le bit        |                  |                 |                 |       |

|              |              | lule is disabled                 |               |                  |                 |                 |       |

|              | 0 = CRC mod  | lule is enabled                  |               |                  |                 |                 |       |

| bit 6        | DAC1MD: DA   | AC1 Module Dis                   | able bit      |                  |                 |                 |       |

|              | 1 = DAC1 mo  | dule is disabled                 | ł             |                  |                 |                 |       |

|              | 0 = DAC1 mo  | dule is enabled                  |               |                  |                 |                 |       |

| bit 5-0      | Unimplemen   | ted: Read as '0                  | ,             |                  |                 |                 |       |

|              |              |                                  |               |                  |                 |                 |       |

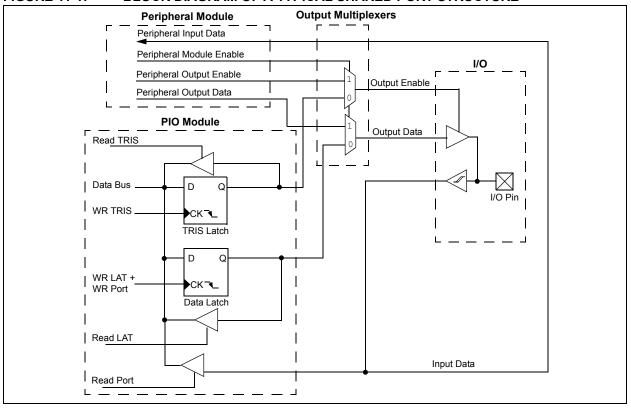

### 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section "30. I/O Ports with Peripheral Pin Select" (DS70190) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### 11.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2012 Microchip Technology Inc.

| U-0                                | U-0 | U-0 | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |  |

|------------------------------------|-----|-----|-------|-----------------------------------------|-----------------|-----------|-------|--|--|

| —                                  | —   | —   |       |                                         | RP13R<4:0       | >         |       |  |  |

| bit 15                             |     |     |       |                                         |                 |           | bit 8 |  |  |

|                                    |     |     |       |                                         |                 |           |       |  |  |

| U-0                                | U-0 | U-0 | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |  |

| —                                  | —   | —   |       |                                         | RP12R<4:0       | >         |       |  |  |

| bit 7                              |     |     |       |                                         |                 |           | bit C |  |  |

| Legend:                            |     |     |       |                                         |                 |           |       |  |  |

| R = Readable bit W = Writable bit  |     |     |       | U = Unimpler                            | mented bit, rea | ad as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set |     |     |       | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |  |

| DIL 15-13 | Unimplemented: Read as 0                                                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP13R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 11-2 for peripheral function numbers) |

| bit 7-5   | Unimplemented: Read as '0'                                                                                                               |

| bit 4-0   | <b>RP12R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 11-2 for peripheral function numbers) |

#### REGISTER 11-24: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP15R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP14R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP15R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP14R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin bits (see Table 11-2 for peripheral function numbers)

The Timer2/3 and Timer4/5 modules can operate in one of the following modes:

- · Timer mode

- · Gated Timer mode

- Synchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous Counter mode, the input clock is derived from the external clock input at TxCK pin.

The timer modes are determined by the following bits:

- TCS (TxCON<1>): Timer Clock Source Control bit

- TGATE (TxCON<6>): Timer Gate Control bit

Timer control bit settings for different operating modes are given in the Table 13-1.

| Mode                | TCS | TGATE |

|---------------------|-----|-------|

| Timer               | 0   | 0     |

| Gated timer         | 0   | 1     |

| Synchronous counter | 1   | Х     |

#### 13.1 16-bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

| Note: | Only Timer2 and Timer3 can trigger a | ı |

|-------|--------------------------------------|---|

|       | DMA data transfer.                   |   |

#### 13.2 32-bit Operation

A 32-bit timer module can be formed by combining a Type B and a Type C 16-bit timer module. For 32-bit timer operation, the T32 control bit in the Type B Timer Control register (TxCON<3>) must be set. The Type C timer holds the most significant word (msw) and the Type B timer holds the least significant word (lsw) for 32-bit operation.

When configured for 32-bit operation, only the Type B Timer Control register (TxCON) bits are required for setup and control. Type C timer control register bits are ignored (except TSIDL bit). For interrupt control, the combined 32-bit timer uses the interrupt enable, interrupt flag and interrupt priority control bits of the Type C timer. The interrupt control and status bits for the Type B timer are ignored during 32-bit timer operation.

The Type B and Type C timers that can be combined to form a 32-bit timer are listed in Table 13-2.

#### TABLE 13-2: 32-BIT TIMER

| TYPE B Timer (Isw) | TYPE C Timer (msw) |  |

|--------------------|--------------------|--|

| Timer2             | Timer3             |  |

| Timer4             | Timer5             |  |

A block diagram representation of the 32-bit timer module is shown in Figure 13-3. The 32-bit timer module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- · Synchronous Counter mode

To configure the features of Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 control bit.

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- Load the timer period value. PR3 or PR5 contains the most significant word of the value, while PR2 or PR4 contains the least significant word.

- If interrupts are required, set the interrupt enable bits, T3IE or T5IE. Use the priority bits, T3IP<2:0> or T5IP<2:0> to set the interrupt priority. While Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2 or TMR5:TMR4, which always contains the most significant word of the count, while TMR2 or TMR4 contains the least significant word.

## 18.3 UART Control Registers

#### REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|-------|-------|

| UARTEN <sup>(1)</sup> | —   | USIDL | IREN <sup>(2)</sup> | RTSMD | —   | UEN   | <1:0> |

| bit 15                |     |       |                     |       |     |       | bit 8 |

| R/W-0 HC | R/W-0  | R/W-0 HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|--------|----------|--------|-------|-------|-------|-------|

| WAKE     | LPBACK | ABAUD    | URXINV | BRGH  | PDSEL | <1:0> | STSEL |

| bit 7    |        |          |        |       |       |       | bit 0 |

| Legend:           | HC = Hardware cleared |                             |                    |

|-------------------|-----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | <ul> <li>UARTEN: UARTx Enable bit<sup>(1)</sup></li> <li>1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN&lt;1:0&gt;</li> <li>0 = UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption minimal</li> </ul>                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 13  | USIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                           |

| bit 12  | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = IrDA<sup>®</sup> encoder and decoder enabled</li> <li>0 = IrDA<sup>®</sup> encoder and decoder disabled</li> </ul>                                                                                                                                                                                                                                                                 |

| bit 11  | <b>RTSMD:</b> Mode Selection for UxRTS Pin bit                                                                                                                                                                                                                                                                                                                                                  |

|         | 1 = <u>UxRTS</u> pin in Simplex mode<br>0 = UxRTS pin in Flow Control mode                                                                                                                                                                                                                                                                                                                      |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 9-8 | UEN<1:0>: UARTx Enable bits                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>11 = UxTX, UxRX and BCLK pins are enabled and used; UxCTS pin controlled by port latches</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches</li> <li>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by port latches</li> </ul> |

| bit 7   | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = UARTx continues to sample the UxRX pin; interrupt generated on falling edge; bit cleared<br/>in hardware on following rising edge</li> <li>0 = No wake-up enabled</li> </ul>                                                                                                                                                                                                       |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                                                                                                                                                                                                                                                          |

|         | 1 = Enable Loopback mode<br>0 = Loopback mode is disabled                                                                                                                                                                                                                                                                                                                                       |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul>                                                                                                                                                           |

| Note 1: | Refer to <b>Section 17. "UART"</b> (DS70188) in the <i>"dsPIC33F/PIC24H Family Reference Manual"</i> for information on enabling the UART module for receive or transmit operation.                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                                                                                                                                                                                                                 |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### 21.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

#### 21.5 ADC Resources

Many useful resources related to ADC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

#### 21.5.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

|                 |                                                                                                                                                                                                             |                                                                                                                                                                                                                          | -                                                                                                                                                                                                                 |                                     |                   | •               |       |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|-----------------|-------|--|

| R/W-0           | U-0                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                             | R/W-0                               | R/W-0             | R/W-0           | R/W-0 |  |

| CH0NB           |                                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     | CH0SB<4:0>        |                 |       |  |

| bit 15          |                                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 | bit   |  |

| R/W-0           | U-0                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                             | R/W-0                               | R/W-0             | R/W-0           | R/W-0 |  |

| <b>CH0NA</b>    | _                                                                                                                                                                                                           |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     | CH0SA<4:0>        |                 |       |  |

| bit 7           |                                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 | bit   |  |

| Legend:         |                                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

| R = Readable    | e bit                                                                                                                                                                                                       | W = Writable I                                                                                                                                                                                                           | bit                                                                                                                                                                                                               | U = Unimple                         | emented bit, read | l as '0'        |       |  |

| -n = Value at I | POR                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                         |                                                                                                                                                                                                                   | '0' = Bit is c                      | eared             | x = Bit is unki | nown  |  |

| bit 15          |                                                                                                                                                                                                             | nnel 0 Negative                                                                                                                                                                                                          | e Input Select                                                                                                                                                                                                    | for Sample B                        | bit               |                 |       |  |

|                 | Same definition                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

| bit 14-13       | -                                                                                                                                                                                                           | ted: Read as 'o                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

| bit 12-8        |                                                                                                                                                                                                             | Channel 0 Po                                                                                                                                                                                                             | -                                                                                                                                                                                                                 |                                     | le B bits         |                 |       |  |

|                 |                                                                                                                                                                                                             | nnel 0 positive<br>nnel 0 positive                                                                                                                                                                                       |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 | •                                                                                                                                                                                                           | inei o positive                                                                                                                                                                                                          | input is ANTT                                                                                                                                                                                                     |                                     |                   |                 |       |  |

|                 | •                                                                                                                                                                                                           |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 | •<br>01000 = Channel 0 positive input is AN8 <sup>(1)</sup>                                                                                                                                                 |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 | 01111 = Channel 0 positive input is AN3 <sup>(1)</sup>                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 | 00110 = Channel 0 positive input is AN6(1)                                                                                                                                                                  |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 |                                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 | •                                                                                                                                                                                                           | ·                                                                                                                                                                                                                        |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 | •<br>•                                                                                                                                                                                                      | ·                                                                                                                                                                                                                        |                                                                                                                                                                                                                   |                                     |                   |                 |       |  |

|                 |                                                                                                                                                                                                             | nnel 0 positive                                                                                                                                                                                                          | input is AN2                                                                                                                                                                                                      |                                     |                   |                 |       |  |

|                 | 00001 <b>= Cha</b> i                                                                                                                                                                                        | nnel 0 positive<br>nnel 0 positive                                                                                                                                                                                       | input is AN2<br>input is AN1                                                                                                                                                                                      |                                     |                   |                 |       |  |

| hit 7           | 00001 <b>= Cha</b> i<br>00000 <b>= Cha</b> i                                                                                                                                                                | nnel 0 positive<br>nnel 0 positive<br>nnel 0 positive                                                                                                                                                                    | input is AN2<br>input is AN1<br>input is AN0                                                                                                                                                                      |                                     | bit               |                 |       |  |

| bit 7           | 00001 <b>= Cha</b> i<br>00000 <b>= Chai</b><br><b>CH0NA: Cha</b> i                                                                                                                                          | nnel 0 positive<br>nnel 0 positive<br>nnel 0 positive<br>nnel 0 Negative                                                                                                                                                 | input is AN2<br>input is AN1<br>input is AN0<br>e Input Select                                                                                                                                                    |                                     | bit               |                 |       |  |

| bit 7           | 00001 = Char<br>00000 = Char<br><b>CH0NA:</b> Char<br>1 = Channel 0                                                                                                                                         | nnel 0 positive<br>nnel 0 positive<br>nnel 0 positive<br>nnel 0 Negative<br>negative input                                                                                                                               | input is AN2<br>input is AN1<br>input is AN0<br>e Input Select<br>t is AN1                                                                                                                                        |                                     | bit               |                 |       |  |

|                 | 00001 = Char<br>00000 = Char<br><b>CH0NA:</b> Char<br>1 = Channel 0<br>0 = Channel 0                                                                                                                        | nnel 0 positive<br>nnel 0 positive<br>nnel 0 positive<br>nnel 0 Negative<br>negative input                                                                                                                               | input is AN2<br>input is AN1<br>input is AN0<br>e Input Select<br>t is AN1<br>t is VREF-                                                                                                                          |                                     | bit               |                 |       |  |

| bit 6-5         | 00001 = Char<br>00000 = Char<br><b>CH0NA:</b> Char<br>1 = Channel 0<br>0 = Channel 0<br><b>Unimplement</b>                                                                                                  | nnel 0 positive<br>nnel 0 positive<br>nnel 0 positive<br>nnel 0 Negative<br>negative input<br>negative input<br>ted: Read as (0                                                                                          | input is AN2<br>input is AN1<br>input is AN0<br>Input Select<br>t is AN1<br>t is VREF-<br>o'                                                                                                                      | for Sample A                        |                   |                 |       |  |

|                 | 00001 = Char<br>00000 = Char<br>CH0NA: Char<br>1 = Channel 0<br>0 = Channel 0<br>Unimplement<br>CH0SA<4:0>                                                                                                  | nnel 0 positive<br>nnel 0 positive<br>nnel 0 positive<br>negative input<br>negative input<br>negative input<br>ted: Read as '0<br>channel 0 Po                                                                           | input is AN2<br>input is AN1<br>input is AN0<br>e Input Select<br>t is AN1<br>t is VREF-<br>o'<br>sitive Input Se                                                                                                 | for Sample A<br>elect for Samp      |                   |                 |       |  |