Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

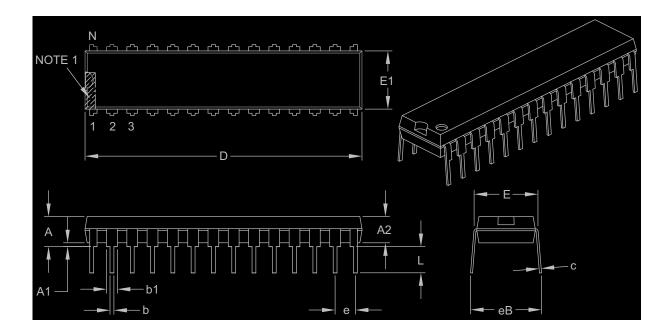

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp302-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:          | PINOU       | T I/O DESC     | CRIPTI     | ONS                                                                                                                                                                                |

|---------------------|-------------|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name            | Pin<br>Type | Buffer<br>Type | PPS        | Description                                                                                                                                                                        |

| AN0-AN12            | I           | Analog         |            | Analog input channels.                                                                                                                                                             |

| CLKI                | I           | ST/CMOS        | No         | External clock source input. Always associated with OSC1 pin function.                                                                                                             |

| CLKO                | 0           | _              | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                | I           | ST/CMOS        | No         | Oscillator crystal input. ST buffer when configured in RC mode;<br>CMOS otherwise.                                                                                                 |

| OSC2                | I/O         | —              | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| SOSCI<br>SOSCO      | I<br>O      | ST/CMOS        | No<br>No   | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.<br>32.768 kHz low-power oscillator crystal output.                                                                  |

| CN0-CN30            | I           | ST             | No<br>No   | Change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                |

| IC1-IC2<br>IC7-IC8  | I<br>I      | ST<br>ST       | Yes<br>Yes | Capture inputs 1/2.<br>Capture inputs 7/8.                                                                                                                                         |

| OCFA<br>OC1-OC4     | I<br>O      | ST<br>—        | Yes<br>Yes | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).<br>Compare outputs 1 through 4.                                                                                        |

| INT0                | I           | ST             | No         | External interrupt 0.                                                                                                                                                              |

| INT1<br>INT2        | 1           | ST             | Yes        | External interrupt 1.                                                                                                                                                              |

|                     |             | ST             | Yes        | External interrupt 2.                                                                                                                                                              |

| RA0-RA4<br>RA7-RA10 | 1/O<br>1/O  | ST<br>ST       | No<br>No   | PORTA is a bidirectional I/O port.<br>PORTA is a bidirectional I/O port.                                                                                                           |

| RB0-RB15            | I/O         | ST             | No         | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC9             | I/O         | ST             | No         | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| TICK                | 1           | ST             | No         | Timer1 external clock input.                                                                                                                                                       |

| T2CK                | i           | ST             | Yes        | Timer2 external clock input.                                                                                                                                                       |

| ТЗСК                | I           | ST             | Yes        | Timer3 external clock input.                                                                                                                                                       |

| T4CK                |             | ST             | Yes        | Timer4 external clock input.                                                                                                                                                       |

| T5CK                |             | ST             | Yes        | Timer5 external clock input.                                                                                                                                                       |

| U1CTS               | 0           | ST             | Yes<br>Yes | UART1 clear to send.<br>UART1 ready to send.                                                                                                                                       |

| U1RTS               | I I         | ST             | Yes        | UART1 receive.                                                                                                                                                                     |

| U1RX<br>U1TX        | Ó           | _              | Yes        | UART1 transmit.                                                                                                                                                                    |

| U2CTS               | 1           | ST             | Yes        | UART2 clear to send.                                                                                                                                                               |

| U2RTS               | 0           | _              | Yes        | UART2 ready to send.                                                                                                                                                               |

| U2RX                |             | ST             | Yes        | UART2 receive.                                                                                                                                                                     |

| U2TX                | 0           | _              | Yes        | UART2 transmit.                                                                                                                                                                    |

| SCK1                | I/O         | ST             | Yes        | Synchronous serial clock input/output for SPI1.                                                                                                                                    |

| SDI1<br>SDO1        |             | ST             | Yes        | SPI1 data in.                                                                                                                                                                      |

| SS1                 | 0<br>I/O    | ST             | Yes<br>Yes | SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                                                                   |

| SCK2                | I/O         | ST             | Yes        | Synchronous serial clock input/output for SPI2.                                                                                                                                    |

| SDI2                | г<br>Г      | ST             | Yes        | SPI2 data in.                                                                                                                                                                      |

| SDO2                | Ó           | _              | Yes        | SPI2 data out.                                                                                                                                                                     |

| SS2                 | I/O         | ST             | Yes        | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                     |

|                     |             | S compatible   |            |                                                                                                                                                                                    |

| TABLE 1-1: PINOUT I/O DESCRIPTIONS | TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS</b> |

|------------------------------------|------------|--------------------------------|

|------------------------------------|------------|--------------------------------|

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

= Analog Input O = Output I = Input PPS = Peripheral Pin Select

#### **Special Function Register Maps** 4.4

#### TABLE 4-1: **CPU CORE REGISTERS MAP**

| DS70   |  |

|--------|--|

| 292G   |  |

| i-page |  |

| 42     |  |

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8       | Bit 7        | Bit 6    | Bit 5    | Bit 4           | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|------------------------------|--------|--------|--------|--------|---------|-------------|--------------|----------|----------|-----------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000        |        |                              |        |        |        |        |         | Working Re  | gister 0     |          |          |                 |              |              |         |       | 0000          |

| WREG1    | 0002        |        |                              |        |        |        |        |         | Working Re  | gister 1     |          |          |                 |              |              |         |       | 0000          |

| WREG2    | 0004        |        |                              |        |        |        |        |         | Working Re  | gister 2     |          |          |                 |              |              |         |       | 0000          |

| WREG3    | 0006        |        |                              |        |        |        |        |         | Working Re  | gister 3     |          |          |                 |              |              |         |       | 0000          |

| WREG4    | 0008        |        |                              |        |        |        |        |         | Working Re  | gister 4     |          |          |                 |              |              |         |       | 0000          |

| WREG5    | 000A        |        |                              |        |        |        |        |         | Working Re  | gister 5     |          |          |                 |              |              |         |       | 0000          |

| WREG6    | 000C        |        |                              |        |        |        |        |         | Working Re  | gister 6     |          |          |                 |              |              |         |       | 0000          |

| WREG7    | 000E        |        |                              |        |        |        |        |         | Working Re  | gister 7     |          |          |                 |              |              |         |       | 0000          |

| WREG8    | 0010        |        |                              |        |        |        |        |         | Working Re  | gister 8     |          |          |                 |              |              |         |       | 0000          |

| WREG9    | 0012        |        |                              |        |        |        |        |         | Working Re  | gister 9     |          |          |                 |              |              |         |       | 0000          |

| WREG10   | 0014        |        |                              |        |        |        |        | ,       | Working Reg | jister 10    |          |          |                 |              |              |         |       | 0000          |

| WREG11   | 0016        |        |                              |        |        |        |        |         | Working Reg | jister 11    |          |          |                 |              |              |         |       | 0000          |

| WREG12   | 0018        |        | Working Register 12          |        |        |        |        |         |             |              |          |          |                 | 0000         |              |         |       |               |

| WREG13   | 001A        |        | Working Register 13          |        |        |        |        |         |             |              |          |          |                 | 0000         |              |         |       |               |

| WREG14   | 001C        |        | Working Register 14          |        |        |        |        |         |             |              |          |          |                 |              | 0000         |         |       |               |

| WREG15   | 001E        |        | Working Register 15          |        |        |        |        |         |             |              |          |          |                 |              | 0800         |         |       |               |

| SPLIM    | 0020        |        | Stack Pointer Limit Register |        |        |        |        |         |             |              |          |          |                 |              | XXXX         |         |       |               |

| ACCAL    | 0022        |        |                              |        |        |        |        |         | ACCA        | L            |          |          |                 |              |              |         |       | XXXX          |

| ACCAH    | 0024        |        |                              |        |        |        |        |         | ACCA        | Н            |          |          |                 |              |              |         |       | XXXX          |

| ACCAU    | 0026        |        |                              |        | ACCA<  | 39>    |        |         |             |              |          |          | AC              | CAU          |              |         |       | XXXX          |

| ACCBL    | 0028        |        |                              |        |        |        |        |         | ACCB        | L            |          |          |                 |              |              |         |       | XXXX          |

| ACCBH    | 002A        |        |                              |        |        |        |        |         | ACCB        | Н            |          |          |                 |              |              |         |       | XXXX          |

| ACCBU    | 002C        |        |                              |        | ACCB<  | 39>    |        |         |             |              |          |          | AC              | CBU          |              |         |       | XXXX          |

| PCL      | 002E        |        |                              |        |        |        |        | Program | Counter Lov | w Word Reg   | ister    |          |                 |              |              |         |       | XXXX          |

| PCH      | 0030        | _      |                              | —      |        |        | _      | _       | _           |              |          | Progra   | am Counter      | High Byte F  | Register     |         |       | 0000          |

| TBLPAG   | 0032        | _      |                              | —      | _      |        | —      | _       | —           |              |          | Table    | Page Addre      | ss Pointer F | Register     |         |       | 0000          |

| PSVPAG   | 0034        | _      |                              | —      |        |        | _      | _       | _           |              | Progr    | am Memor | y Visibility Pa | age Addres   | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036        |        |                              |        |        |        |        | Repe    | at Loop Cou | nter Registe | r        |          |                 |              |              |         |       | XXXX          |

| DCOUNT   | 0038        |        |                              |        |        |        |        |         | DCOUNT<     | :15:0>       |          |          |                 |              |              |         |       | XXXX          |

| DOSTARTL | 003A        |        |                              |        |        |        |        | DOST    | TARTL<15:1  | >            |          |          |                 |              |              |         | 0     | XXXX          |

| DOSTARTH | 003C        | _      |                              | _      | _      | _      | _      | _       | _           | _            | _        |          |                 | DOSTAF       | RTH<5:0>     |         |       | 00xx          |

| DOENDL   | 003E        |        |                              |        |        |        |        | DOE     | NDL<15:1>   |              |          |          |                 |              |              |         | 0     | XXXX          |

| DOENDH   | 0040        | _      | _                            | _      | _      | _      | _      | _       | _           | _            | _        |          |                 | DOE          | ENDH         |         |       | 00xx          |

| SR       | 0042        | OA     | OB                           | SA     | SB     | OAB    | SAB    | DA      | DC          |              | IPL<2:0> |          | RA              | Ν            | OV           | Z       | С     | 0000          |

| CORCON   | 0044        | _      | _                            | _      | US     | EDT    |        | DL<2:0> |             | SATA         | SATB     | SATDW    | ACCSAT          | IPL3         | PSV          | RND     | IF    | 0020          |

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

© 2007-2012 Microchip Technology Inc.

## TABLE 4-10: UART2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7                                         | Bit 6  | Bit 5 | Bit 4       | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|-----------------------------------------------|--------|-------|-------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230        | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0       | WAKE                                          | LPBACK | ABAUD | URXINV      | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA    | 0232        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |        |       |             |              |       | 0110   |       |               |

| U2TXREG  | 0234        | _        | _      | —        | _      | —      | _      | _     | UTX8       |                                               |        | U     | ART Transn  | nit Register |       |        |       | XXXX          |

| U2RXREG  | 0236        | —        | _      | —        | _      | —      | -      | _     | URX8       |                                               |        | U     | IART Receiv | e Register   |       |        |       | 0000          |

| U2BRG    | 0238        |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc                                  | aler   |       |             |              |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-11: SPI1 REGISTER MAP

| SFR Name | SFR<br>Addr                                    | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4               | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|------------------------------------------------|--------|--------|---------|--------|--------|--------|-------|-------|-------|--------|-------|---------------------|-------|-------|--------|--------|---------------|

| SPI1STAT | 0240                                           | SPIEN  | _      | SPISIDL | —      | _      | —      |       |       |       | SPIROV | —     | -                   | —     |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242                                           | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE<2:0> PPRE<1:0> |       |       |        |        | 0000          |

| SPI1CON2 | 0244                                           | FRMEN  | SPIFSD | FRMPOL  | _      | —      | —      | _     | _     | _     | _      | —     | _                   | _     | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248 SPI1 Transmit and Receive Buffer Register |        |        |         |        |        |        |       |       |       |        |       | 0000                |       |       |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                    | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|-------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN  | -                                         | SPISIDL | _      | —      | —      |       | —     |       | SPIROV | _     | -     | —         | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | _      | _                                         | -       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN  | SPIFSD                                    | FRMPOL  | _      | _      | —      | _     | _     | _     | _      | _     | —     | _         | _     | FRMDLY | _      | 0000          |

| SPI2BUF  | 0268        |        | SPI2 Transmit and Receive Buffer Register |         |        |        |        |       |       |       |        |       | 0000  |           |       |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

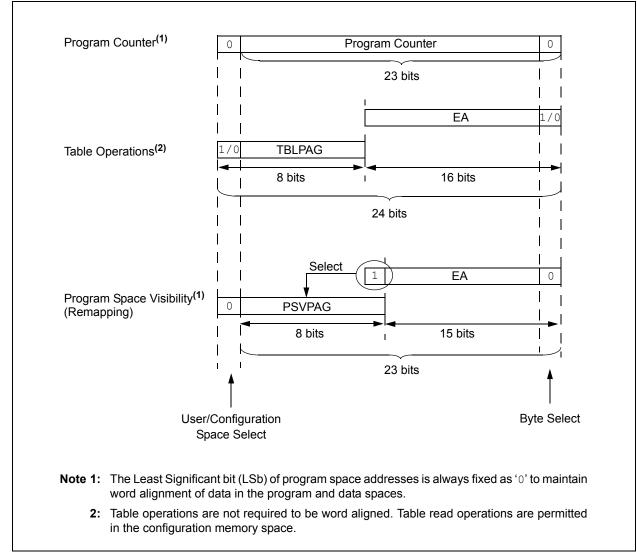

### 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 architecture uses a 24 bit wide program space and a 16 bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

#### 4.8.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-39 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

#### TABLE 4-39: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        | Program Space Address |           |               |                              |     |  |  |  |  |  |

|--------------------------|---------------|-----------------------|-----------|---------------|------------------------------|-----|--|--|--|--|--|

| Access Type              | Space         | <23>                  | <22:16>   | <15>          | <14:1>                       | <0> |  |  |  |  |  |

| Instruction Access       | User          | 0                     |           | 0             |                              |     |  |  |  |  |  |

| (Code Execution)         |               |                       | XXX XXX   |               |                              |     |  |  |  |  |  |

| TBLRD/TBLWT              | User          | TB                    | LPAG<7:0> | Data EA<15:0> |                              |     |  |  |  |  |  |

| (Byte/Word Read/Write)   |               | 0                     | XXX XXXX  | XXXX XX       | XXXX XXXX XXXX               |     |  |  |  |  |  |

|                          | Configuration | TB                    | LPAG<7:0> | Data EA<15:0> |                              |     |  |  |  |  |  |

|                          |               | 1                     | XXX XXXX  | XXXX X        | XXX XXXX XXXX                |     |  |  |  |  |  |

| Program Space Visibility | User          | 0                     | PSVPAG<7  | 7:0>          | Data EA<14:0> <sup>(1)</sup> |     |  |  |  |  |  |

| (Block Remap/Read)       |               | 0                     | XXXX XXXX | ĸ             | XXX XXXX XXXX XXX            |     |  |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

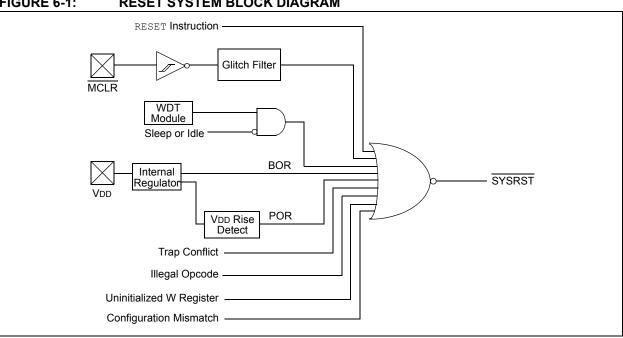

#### 6.0 RESETS

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304. of the dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

The status bits in the RCON register Note: should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

| REGISTER      |                                                                              | : INTERRUPT F            |               | CONTROL R               | EGISTER 8      |                  |       |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------|--------------------------|---------------|-------------------------|----------------|------------------|-------|--|--|--|--|--|

| U-0           | R/W-1                                                                        | R/W-0                    | R/W-0         | U-0                     | R/W-1          | R/W-0            | R/W-0 |  |  |  |  |  |

| —             |                                                                              | C1IP<2:0> <sup>(1)</sup> |               |                         |                | C1RXIP<2:0>(1)   |       |  |  |  |  |  |

| bit 15        |                                                                              |                          |               |                         |                |                  | bi    |  |  |  |  |  |

| U-0           | R/W-1                                                                        | R/W-0                    | R/W-0         | U-0                     | R/W-1          | R/W-0            | R/W-0 |  |  |  |  |  |

|               |                                                                              | SPI2IP<2:0>              |               | _                       |                | SPI2EIP<2:0>     |       |  |  |  |  |  |

| bit 7         |                                                                              |                          |               |                         |                |                  | bi    |  |  |  |  |  |

| Legend:       |                                                                              |                          |               |                         |                |                  |       |  |  |  |  |  |

| R = Readabl   | e bit                                                                        | W = Writable b           | it            | U = Unimpler            | mented bit, re | ad as '0'        |       |  |  |  |  |  |

| -n = Value at | POR                                                                          | '1' = Bit is set         |               | '0' = Bit is cle        |                | x = Bit is unkno | own   |  |  |  |  |  |

|               |                                                                              |                          |               |                         |                |                  |       |  |  |  |  |  |

| bit 15        | Unimpleme                                                                    | ented: Read as '0        | 3             |                         |                |                  |       |  |  |  |  |  |

| bit 14-12     | C1IP<2:0>:                                                                   | ECAN1 Event Int          | errupt Prior  | ity bits <sup>(1)</sup> |                |                  |       |  |  |  |  |  |

|               | 111 = Interr                                                                 | rupt is priority 7 (h    | ighest priori | ty interrupt)           |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | 001 = Interr                                                                 | rupt is priority 1       |               |                         |                |                  |       |  |  |  |  |  |

|               |                                                                              | rupt source is disa      | bled          |                         |                |                  |       |  |  |  |  |  |

| bit 11        | Unimpleme                                                                    | ented: Read as '0        | 3             |                         |                |                  |       |  |  |  |  |  |

| bit 10-8      | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits <sup>(1)</sup> |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | 111 = Interr                                                                 | rupt is priority 7 (h    | ighest priori | ty interrupt)           |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | 001 = Interr                                                                 | rupt is priority 1       |               |                         |                |                  |       |  |  |  |  |  |

|               |                                                                              | upt source is disa       | bled          |                         |                |                  |       |  |  |  |  |  |

| bit 7         | Unimpleme                                                                    | ented: Read as '0        | ,             |                         |                |                  |       |  |  |  |  |  |

| bit 6-4       | SPI2IP<2:0                                                                   | >: SPI2 Event Inte       | errupt Priori | ty bits                 |                |                  |       |  |  |  |  |  |

|               | 111 = Interr                                                                 | rupt is priority 7 (h    | ighest priori | ty interrupt)           |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | 001 = Interr                                                                 | rupt is priority 1       |               |                         |                |                  |       |  |  |  |  |  |

|               |                                                                              | upt source is disa       | bled          |                         |                |                  |       |  |  |  |  |  |

| bit 3         | Unimpleme                                                                    | ented: Read as '0        | ,             |                         |                |                  |       |  |  |  |  |  |

| bit 2-0       | SPI2EIP<2:                                                                   | 0>: SPI2 Error Int       | errupt Prior  | ity bits                |                |                  |       |  |  |  |  |  |

|               | 111 = Interr                                                                 | rupt is priority 7 (h    | ighest priori | ty interrupt)           |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | •                                                                            |                          |               |                         |                |                  |       |  |  |  |  |  |

|               | 001 = Interr                                                                 | rupt is priority 1       |               |                         |                |                  |       |  |  |  |  |  |

|               |                                                                              | upt source is disa       | blod          |                         |                |                  |       |  |  |  |  |  |

#### -.... -----

#### 7.6 Interrupt Setup Procedures

#### 7.6.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level depends on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

Note: At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.6.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development tool suite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program re-enters the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.6.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.6.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

## 9.1 CPU Clocking System

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- FRC Oscillator with postscaler

## 9.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> bits (CLKDIV<10:8>).

The primary oscillator can use one of the following as its clock source:

- Crystal (XT): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- High-Speed Crystal (HS): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- External Clock (EC): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip PLL to provide a wide range of output frequencies for device operation. PLL configuration is described in Section 9.1.4 "PLL Configuration".

The FRC frequency depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

## 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 27.1 "Configuration Bits" for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Configuration Select bits. POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 40 MHz are supported by the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

#### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

#### 9.1.3 AUXILIARY OSCILLATOR

The Auxiliary Oscillator (AOSC) can be used for peripherals that need to operate at a frequency unrelated to the system clock such as a Digital-to-Analog Converter (DAC).

The Auxiliary Oscillator can use one of the following as its clock source:

- Crystal (XT): Crystal and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the SOCI and SOSCO pins.

- High-Speed Crystal (HS): Crystals in the range of 10 to 40 MHz. The crystal is connected to the SOSCI and SOSCO pins.

- External Clock (EC): External clock signal up to 64 MHz. The external clock signal is directly applied to SOSCI pin.

| REGISTER      | 9-2: CLKD                  | DIV: CLOCK DI       | VISOR RE           | GISTER <sup>(2)</sup> |                 |                    |           |

|---------------|----------------------------|---------------------|--------------------|-----------------------|-----------------|--------------------|-----------|

| R/W-0         | R/W-0                      | R/W-1               | R/W-1              | R/W-0                 | R/W-0           | R/W-0              | R/W-0     |

| ROI           |                            | DOZE<2:0>           |                    | DOZEN <sup>(1)</sup>  |                 | FRCDIV<2:0>        |           |

| bit 15        |                            |                     |                    |                       |                 |                    | bit 8     |

| R/W-0         | R/W-1                      | U-0                 | R/W-0              | R/W-0                 | R/W-0           | R/W-0              | R/W-0     |

| PLLPC         | ST<1:0>                    | —                   |                    |                       | PLLPRE<4:0      | >                  |           |

| bit 7         |                            |                     |                    |                       |                 |                    | bit C     |

| Legend:       |                            | v = Value set f     | rom Configu        | ration bits on P      | OR              |                    |           |

| R = Readable  | a bit                      | W = Writable b      | -                  |                       | nented bit, rea | d as '0'           |           |

| -n = Value at |                            | '1' = Bit is set    | Л                  | '0' = Bit is cle      |                 |                    |           |

|               | PUR                        | I = DILIS SEL       |                    |                       | areu            | x = Bit is unki    | IOWII     |

| bit 15        | ROI: Recove                | er on Interrupt bit |                    |                       |                 |                    |           |

|               |                            | ts clears the DO    |                    | the processor c       | lock/periphera  | l clock ratio is s | et to 1:1 |

|               |                            | ts have no effect   |                    |                       |                 |                    |           |

| bit 14-12     | DOZE<2:0>:                 | Processor Cloc      | k Reduction        | Select bits           |                 |                    |           |

|               | 111 = Fcy/1                | 28                  |                    |                       |                 |                    |           |

|               | 110 = Fcy/6                |                     |                    |                       |                 |                    |           |

|               | 101 = Fcy/3                |                     |                    |                       |                 |                    |           |

|               | 100 = Fcy/1<br>011 = Fcy/8 |                     |                    |                       |                 |                    |           |

|               | 010 = Fcy/4                |                     |                    |                       |                 |                    |           |

|               | 001 = FCY/2                |                     |                    |                       |                 |                    |           |

|               | 000 = Fcy/1                |                     |                    |                       |                 |                    |           |

| bit 11        | DOZEN: Doz                 | ze Mode Enable      | bit <sup>(1)</sup> |                       |                 |                    |           |

|               |                            | 2:0> field specifie |                    |                       | ipheral clocks  | and the process    | or clocks |

| bit 10-8      |                            | >: Internal Fast    |                    |                       | S               |                    |           |

|               | 111 <b>= FRC (</b>         | divide by 256       |                    |                       |                 |                    |           |

|               | 110 <b>= FRC d</b>         |                     |                    |                       |                 |                    |           |

|               | 101 <b>= FRC d</b>         |                     |                    |                       |                 |                    |           |

|               | 100 <b>= FRC</b> (         |                     |                    |                       |                 |                    |           |

|               | 011 = FRC o<br>010 = FRC o |                     |                    |                       |                 |                    |           |

|               | 010 = FRC (<br>001 = FRC ( | -                   |                    |                       |                 |                    |           |

|               |                            | divide by 1 (defai  | ult)               |                       |                 |                    |           |

| bit 7-6       |                            | I:0>: PLL VCO C     |                    | er Select bits (al    | so denoted as   | 'N2', PLL posts    | caler)    |

|               | 11 = Output/               |                     |                    |                       |                 | , .                | ,         |

|               | 10 = Reserv                |                     |                    |                       |                 |                    |           |

|               | 01 = Output/               |                     |                    |                       |                 |                    |           |

|               | 00 = Output/               | 2                   |                    |                       |                 |                    |           |

| bit 5         | Unimpleme                  | nted: Read as '0    | ,                  |                       |                 |                    |           |

| bit 4-0       | PLLPRE<4:                  | 0>: PLL Phase D     | etector Inpu       | ıt Divider bits (a    | lso denoted as  | s 'N1', PLL pres   | caler)    |

|               | 11111 <b>= Inp</b>         | ut/33               |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | 00000 <b>= Inp</b>         | ut/2 (default)      |                    |                       |                 |                    |           |

|               | 00001 = Inp                |                     |                    |                       |                 |                    |           |

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

**Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

2: This register is reset only on a Power-on Reset (POR).

#### 11.9 Peripheral Pin Select Registers

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 family of devices implement 33 registers for remappable peripheral configuration:

- 16 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR11 and PRINR18-RPINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

| Note: | Inpu             | t and Output  | t Re  | gister | valu | es can | only  |

|-------|------------------|---------------|-------|--------|------|--------|-------|

|       | be               | changed       | if    | the    | IOI  | _OCK   | bit   |

|       | (OS              | CCON<6>)      | is    | set    | to   | '0'.   | See   |

|       | Section 11.6.3.1 |               |       | "Cont  | rol  | Reg    | ister |

|       | Loc              | k" for a spec | cific | comm   | and  | seque  | nce.  |

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | _   | —   |       |       | INT1R<4:0> |       |       |

| bit 15 |     |     | •     |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 Unimplemented: Read as '0 | Inimplemented: Read as '0' |

|-------------------------------------|----------------------------|

|-------------------------------------|----------------------------|

```

bit 12-8

INT1R<4:0>: Assign External Interrupt 1 (INTR1) to the corresponding RPn pin

1111 = Input tied to Vss

11001 = Input tied to RP25

•

•

00001 = Input tied to RP1

00000 = Input tied to RP0

bit 7-0

Unimplemented: Read as '0'

```

#### REGISTER 11-17: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                             | U-0 | U-0                                    | R/W-0 | R/W-0                                | R/W-0     | R/W-0 | R/W-0 |

|---------------------------------|-----|----------------------------------------|-------|--------------------------------------|-----------|-------|-------|

| —                               | _   | —                                      |       |                                      | RP1R<4:0> |       |       |

| bit 15                          |     |                                        |       |                                      |           |       | bit 8 |

|                                 |     |                                        |       |                                      |           |       |       |

| U-0                             | U-0 | U-0                                    | R/W-0 | R/W-0                                | R/W-0     | R/W-0 | R/W-0 |

| —                               | _   | —                                      |       |                                      | RP0R<4:0> |       |       |

| bit 7                           |     |                                        |       |                                      |           |       | bit 0 |

|                                 |     |                                        |       |                                      |           |       |       |

| Legend:                         |     |                                        |       |                                      |           |       |       |

| R = Readable bit W = Writable b |     | bit U = Unimplemented bit, read as '0' |       |                                      |           |       |       |

| -n = Value at P                 | OR  | '1' = Bit is set                       |       | '0' = Bit is cleared x = Bit is unkn |           |       | iown  |

bit 12-8 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-18: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP2R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-21: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| -n = Value at P                  | POR | '1' = Bit is set |                                        | '0' = Bit is cle | ared      | x = Bit is unkr | iown  |

|----------------------------------|-----|------------------|----------------------------------------|------------------|-----------|-----------------|-------|

| R = Readable bit W = Writable bi |     | bit              | bit U = Unimplemented bit, read as '0' |                  |           |                 |       |

| Legend:                          |     |                  |                                        |                  |           |                 |       |

|                                  |     |                  |                                        |                  |           |                 |       |

| bit 7                            |     |                  |                                        |                  |           |                 | bit 0 |

| —                                | _   | —                |                                        |                  | RP8R<4:0> |                 |       |

| U-0                              | U-0 | U-0              | R/W-0                                  | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

|                                  |     |                  |                                        |                  |           |                 |       |

| bit 15                           |     |                  | •                                      |                  |           |                 | bit 8 |

| _                                |     | _                |                                        |                  | RP9R<4:0> |                 |       |

| U-0                              | U-0 | U-0              | R/W-0                                  | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-22: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP11R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|------------|-------|-------|-------|-------|

| —     | —   | —   | RP10R<4:0> |       |       |       |       |

| bit 7 |     |     |            |       |       |       | bit 0 |

| Legend:           |                                                                      |                      |                    |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 11-2 for peripheral function numbers)

# 14.2 Input Capture Registers

# **REGISTER 14-1:** ICxCON: INPUT CAPTURE x CONTROL REGISTER (x = 1, 2, 7 OR 8)

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | —   | —   |     |     | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0    | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0    | R/W-0 |

|-------|----------|-------|---------|---------|-------|----------|-------|

| ICTMR | ICI<1:0> |       | ICOV    | ICBNE   |       | ICM<2:0> |       |

| bit 7 |          |       |         |         |       |          | bit 0 |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                             |

|           | 1 = Input capture module halts in CPU Idle mode                                                                                                                   |

|           | 0 = Input capture module continues to operate in CPU Idle mode                                                                                                    |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                        |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                            |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                      |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                            |

|           | 11 = Interrupt on every fourth capture event                                                                                                                      |

|           | 10 = Interrupt on every third capture event<br>01 = Interrupt on every second capture event                                                                       |

|           | 00 = Interrupt on every capture event                                                                                                                             |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                          |

|           | 1 = Input capture overflow occurred                                                                                                                               |

|           | 0 = No input capture overflow occurred                                                                                                                            |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                          |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                                |

|           | 0 = Input capture buffer is empty                                                                                                                                 |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                          |

|           | 111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br>(Rising edge detect only, all other control bits are not applicable.) |

|           | 110 = Unused (module disabled)                                                                                                                                    |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                        |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                         |

|           | 011 = Capture mode, every rising edge<br>010 = Capture mode, every falling edge                                                                                   |

|           | 001 = Capture mode, every edge (rising and falling)                                                                                                               |

|           | (ICI<1:0> bits do not control interrupt generation for this mode.)                                                                                                |

|           | 000 = Input capture module turned off                                                                                                                             |

|           |                                                                                                                                                                   |

# 15.3 Output Compare Control Register

# REGISTER 15-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2, 3 OR 4)

| U-0          | U-0                                                                                                                                  | R/W-0                                                                                                                              | U-0        | U-0              | U-0             | U-0             | U-0   |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| —            | —                                                                                                                                    | OCSIDL                                                                                                                             | —          | —                | —               | —               |       |  |  |  |  |

| bit 15       |                                                                                                                                      |                                                                                                                                    |            |                  |                 |                 | bit 8 |  |  |  |  |

|              |                                                                                                                                      |                                                                                                                                    |            |                  |                 |                 |       |  |  |  |  |

| U-0          | U-0                                                                                                                                  | U-0                                                                                                                                | R-0 HC     | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

|              | —                                                                                                                                    | —                                                                                                                                  | OCFLT      | OCTSEL           |                 | OCM<2:0>        |       |  |  |  |  |

| bit 7        |                                                                                                                                      |                                                                                                                                    |            |                  |                 |                 | bit C |  |  |  |  |

| Legend:      |                                                                                                                                      | HC = Cleared ir                                                                                                                    | n Hardware | HS = Set in H    | lardware        |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                                                                               | W = Writable bi                                                                                                                    | t          | U = Unimpler     | nented bit, rea | id as '0'       |       |  |  |  |  |

| -n = Value a | t POR                                                                                                                                | '1' = Bit is set                                                                                                                   |            | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |  |  |  |  |