Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp302-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304, the of dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

- VREF+/VREF- pins used when external voltage reference for ADC module is implemented

- Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

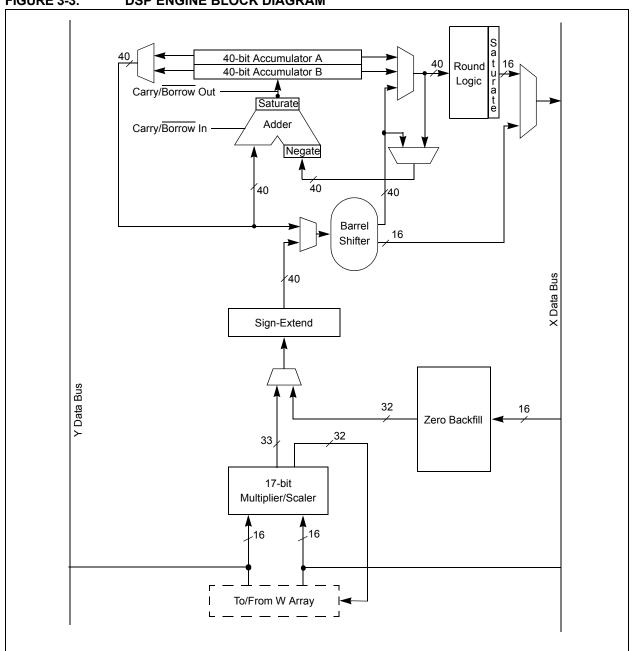

## FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

### 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 architecture uses a 24 bit wide program space and a 16 bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

### 4.8.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-39 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

### TABLE 4-39: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        | Program Space Address    |            |                      |                    |       |  |  |

|--------------------------|---------------|--------------------------|------------|----------------------|--------------------|-------|--|--|

| Access Type              | Space         | <23>                     | <22:16>    | <15>                 | <14:1>             | <0>   |  |  |

| Instruction Access       | User          | 0                        |            | PC<22:1>             |                    | 0     |  |  |

| (Code Execution)         |               |                          | 0xx xxxx x | XXX XXX              |                    |       |  |  |

| TBLRD/TBLWT              | User          | TB                       | LPAG<7:0>  | Data EA<15:0>        |                    |       |  |  |

| (Byte/Word Read/Write)   |               | 0xxx xxxx xxxx xxxx xxxx |            |                      |                    |       |  |  |

|                          | Configuration | TBLPAG<7:0>              |            | Data EA<15:0>        |                    |       |  |  |

|                          |               | 1xxx xxxx                |            | XXXX XXXX XXXX XXXX  |                    |       |  |  |

| Program Space Visibility | User          | 0                        | PSVPAG<7   | G<7:0> Data EA<14:0> |                    | 0>(1) |  |  |

| (Block Remap/Read)       |               | 0                        |            |                      | XXX XXXX XXXX XXXX |       |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| REGISTER 8-3: | DMAxSTA: DMA CHANNEL x RAM START ADDRESS REGISTER A <sup>(1)</sup> |

|---------------|--------------------------------------------------------------------|

|---------------|--------------------------------------------------------------------|

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | STA   | <15:8>                                  |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | STA   | <7:0>                                   |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

**Note 1:** A read of this address register returns the current contents of the DMA RAM Address register, not the contents written to STA<15:0>. If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS REGISTER B<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|-----------------|-------|

|                                   |       |                  | STB                                | <15:8>               |       |                 |       |

| bit 15                            |       |                  |                                    |                      |       |                 | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | STE                                | 3<7:0>               |       |                 |       |

| bit 7                             |       |                  |                                    |                      |       |                 | bit 0 |

| Legend:                           |       |                  |                                    |                      |       |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                 |       |

| -n = Value at P                   | POR   | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unkr | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

**Note 1:** A read of this address register returns the current contents of the DMA RAM Address register, not the contents written to STB<15:0>. If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### 11.9 Peripheral Pin Select Registers

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 family of devices implement 33 registers for remappable peripheral configuration:

- 16 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR11 and PRINR18-RPINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

| Note: | Inpu             | t and Output  | t Re  | gister | valu | es can | only  |

|-------|------------------|---------------|-------|--------|------|--------|-------|

|       | be               | changed       | if    | the    | IOI  | _OCK   | bit   |

|       | (OS              | CCON<6>)      | is    | set    | to   | '0'.   | See   |

|       | Section 11.6.3.1 |               |       | "Cont  | rol  | Reg    | ister |

|       | Loc              | k" for a spec | cific | comm   | and  | seque  | nce.  |

### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | —   |       |       | INT1R<4:0> |       |       |

| bit 15 |     |     | •     |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15-13 Unimplemented: Read as '0 | Inimplemented: Read as '0' |

|-------------------------------------|----------------------------|

|-------------------------------------|----------------------------|

```

bit 12-8

INT1R<4:0>: Assign External Interrupt 1 (INTR1) to the corresponding RPn pin

1111 = Input tied to Vss

11001 = Input tied to RP25

•

•

00001 = Input tied to RP1

00000 = Input tied to RP0

bit 7-0

Unimplemented: Read as '0'

```

| REGISTER 11-27: | <b>RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10<sup>(1)</sup></b> |

|-----------------|-----------------------------------------------------------------------|

|-----------------|-----------------------------------------------------------------------|

| U-0                               | U-0 | U-0                                | R/W-0                | R/W-0 | R/W-0     | R/W-0              | R/W-0 |  |

|-----------------------------------|-----|------------------------------------|----------------------|-------|-----------|--------------------|-------|--|

| —                                 | _   | —                                  |                      |       | RP21R<4:0 | >                  |       |  |

| bit 15                            |     |                                    |                      |       |           |                    | bit 8 |  |

|                                   |     |                                    |                      |       |           |                    |       |  |

| U-0                               | U-0 | U-0                                | R/W-0                | R/W-0 | R/W-0     | R/W-0              | R/W-0 |  |

| —                                 | _   | -                                  |                      |       | RP20R<4:0 | >                  |       |  |

| bit 7                             |     |                                    |                      |       |           |                    | bit 0 |  |

|                                   |     |                                    |                      |       |           |                    |       |  |

| Legend:                           |     |                                    |                      |       |           |                    |       |  |

| R = Readable bit W = Writable bit |     | U = Unimplemented bit, read as '0' |                      |       |           |                    |       |  |

| -n = Value at PO                  | OR  | '1' = Bit is set                   | '0' = Bit is cleared |       |           | x = Bit is unknown |       |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP21R<4:0>:** Peripheral Output Function is Assigned to RP21 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP20R<4:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-2 for peripheral function numbers)

Note 1: This register is implemented in 44-pin devices only.

## REGISTER 11-28: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11<sup>(1)</sup>

| U-0          | U-0        | U-0                               | R/W-0          | R/W-0            | R/W-0            | R/W-0             | R/W-0        |

|--------------|------------|-----------------------------------|----------------|------------------|------------------|-------------------|--------------|

| _            | —          | —                                 |                |                  | RP23R<4:0>       |                   |              |

| bit 15       |            |                                   |                |                  |                  |                   | bit 8        |

|              |            |                                   |                |                  |                  |                   |              |

| U-0          | U-0        | U-0                               | R/W-0          | R/W-0            | R/W-0            | R/W-0             | R/W-0        |

| _            | —          |                                   |                |                  | RP22R<4:0>       |                   |              |

| bit 7        |            | •                                 | •              |                  |                  |                   | bit 0        |

|              |            |                                   |                |                  |                  |                   |              |

| Legend:      |            |                                   |                |                  |                  |                   |              |

| R = Readab   | le bit     | W = Writable                      | bit            | U = Unimpler     | nented bit, read | d as '0'          |              |

| -n = Value a | t POR      | '1' = Bit is set                  | t              | '0' = Bit is cle | ared             | x = Bit is unkr   | iown         |

|              |            |                                   |                |                  |                  |                   |              |

| bit 15-13    | Unimplemen | ted: Read as '                    | 0'             |                  |                  |                   |              |

| bit 12-8     |            | : Peripheral Ou<br>action numbers | •              | is Assigned to   | RP23 Output I    | Pin bits (see Tat | ole 11-2 for |

| bit 7-5      |            | ted: Read as '                    |                |                  |                  |                   |              |

| bit 4-0      | RP22R<4:0> |                                   | utput Function | is Assigned to   | RP22 Output I    | Pin bits (see Tat | ble 11-2 for |

Note 1: This register is implemented in 44-pin devices only.

### 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                          |

|       | Devices.aspx?dDocName=en532311                                                                                 |

### 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# $dsPIC33FJ32GP302/304,\, dsPIC33FJ64GPX02/X04,\, AND\, dsPIC33FJ128GPX02/X04$

| U-0          | U-0                                                                                         | R-0                                                                          | R-0              | R-0              | R-0            | R-0             | R-0   |  |

|--------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|------------------|----------------|-----------------|-------|--|

| _            |                                                                                             | FBP<5:0>                                                                     |                  |                  |                |                 |       |  |

| bit 15       |                                                                                             |                                                                              |                  |                  |                |                 | bit 8 |  |

| U-0          | U-0                                                                                         | R-0                                                                          | R-0              | R-0              | R-0            | R-0             | R-0   |  |

| _            | —                                                                                           |                                                                              |                  | FNR              | B<5:0>         |                 |       |  |

| bit 7        |                                                                                             |                                                                              |                  |                  |                |                 | bit ( |  |

| Legend:      |                                                                                             | C = Writable b                                                               | oit, but only '0 | ' can be writter | n to clear the | bit             |       |  |

| R = Readab   | le bit                                                                                      | W = Writable                                                                 | bit              | U = Unimpler     | mented bit, re | ad as '0'       |       |  |

| -n = Value a | t POR                                                                                       | '1' = Bit is set                                                             |                  | '0' = Bit is cle | ared           | x = Bit is unki | nown  |  |

| bit 7-6      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | RB30 buffer<br>IRB1 buffer<br>IRB0 buffer<br>ented: Read as '0               | o <b>'</b>       |                  |                |                 |       |  |

| bit 5-0      | 011111 =  <br>011110 =  <br>•                                                               | >: FIFO Next Rea<br>RB31 buffer<br>RB30 buffer<br>IRB1 buffer<br>IRB1 buffer | id Buffer Poin   | ter bits         |                |                 |       |  |

## REGISTER 25-2: CRCXOR: CRC XOR POLYNOMIAL REGISTER

| R/W-0                      | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|----------------------------|-------|------------------|--------|------------------------------------|-------|--------------------|-------|

|                            |       |                  | Х<     | :15:8>                             |       |                    |       |

| bit 15                     |       |                  |        |                                    |       |                    | bit 8 |

|                            |       |                  |        |                                    |       |                    |       |

| R/W-0                      | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0              | U-0   |

|                            |       |                  | X<7:1> |                                    |       |                    | _     |

| bit 7                      |       |                  |        |                                    |       |                    | bit 0 |

|                            |       |                  |        |                                    |       |                    |       |

| Legend:                    |       |                  |        |                                    |       |                    |       |

| R = Readable bit W = Writa |       | W = Writable     | bit    | U = Unimplemented bit, read as '0' |       | ad as '0'          |       |

| -n = Value at POR          |       | '1' = Bit is set |        | '0' = Bit is cleared               |       | x = Bit is unknown |       |

bit 15-1 X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '0'

### 26.1 **PMP** Resources

Many useful resources related to PMP are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532311              |

### 26.1.1 KEY RESOURCES

- Section 35. "Parallel Master Port (PMP)" (DS70299)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 26.2 PMP Control Registers

## REGISTER 26-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-------|---------|---------|--------|--------|--------|

| PMPEN  | _   | PSIDL | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN | PTRDEN |

| bit 15 |     |       |         |         |        |        | bit 8  |

| R/W-0 | R/W-0 | R/W-0 <sup>(1)</sup> | U-0 | R/W-0 <sup>(1)</sup> | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|----------------------|-----|----------------------|-------|-------|-------|

| CSF1  | CSF0  | ALP                  | —   | CS1P                 | BEP   | WRSP  | RDSP  |

| bit 7 |       |                      |     |                      |       |       | bit 0 |

| Legend:       |                                                                                     |                                                                                           |                                    |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|

| R = Readabl   | e bit W = Writable I                                                                | Dit U = Unimplemented b                                                                   | bit, read as '0'                   |  |  |  |  |  |

| -n = Value at | POR '1' = Bit is set                                                                | '0' = Bit is cleared                                                                      | x = Bit is unknown                 |  |  |  |  |  |

| bit 15        | <b>PMPEN:</b> Parallel Master Por<br>1 = PMP enabled<br>0 = PMP disabled, no off-ch |                                                                                           |                                    |  |  |  |  |  |

| bit 14        | Unimplemented: Read as '0                                                           |                                                                                           |                                    |  |  |  |  |  |

| bit 13        | PSIDL: Stop in Idle Mode bit                                                        |                                                                                           |                                    |  |  |  |  |  |

|               | •                                                                                   | ration when device enters Idle mode                                                       | 9                                  |  |  |  |  |  |

| bit 12-11     | ADRMUX1:ADRMUX0: Add                                                                | ress/Data Multiplexing Selection bits                                                     | <sub>S</sub> (1)                   |  |  |  |  |  |

|               |                                                                                     | e multiplexed on PMD<7:0> pins<br>s are multiplexed on PMD<7:0> pi<br>ar on separate pins | ns, upper 3 bits are multiplexed o |  |  |  |  |  |

| bit 10        | PTBEEN: Byte Enable Port I                                                          | PTBEEN: Byte Enable Port Enable bit (16-bit Master mode)                                  |                                    |  |  |  |  |  |

|               | <ul><li>1 = PMBE port enabled</li><li>0 = PMBE port disabled</li></ul>              |                                                                                           |                                    |  |  |  |  |  |

| bit 9         | PTWREN: Write Enable Stro                                                           | be Port Enable bit                                                                        |                                    |  |  |  |  |  |

|               | <ul><li>1 = PMWR/PMENB port ena</li><li>0 = PMWR/PMENB port dis</li></ul>           |                                                                                           |                                    |  |  |  |  |  |

| bit 8         | PTRDEN: Read/Write Strobe                                                           |                                                                                           |                                    |  |  |  |  |  |

|               | 1 = PMRD/PMWR port enable<br>0 = PMRD/PMWR port disal                               |                                                                                           |                                    |  |  |  |  |  |

| bit 7-6       | CSF1:CSF0: Chip Select Fu                                                           | nction bits                                                                               |                                    |  |  |  |  |  |

|               | 11 = Reserved<br>10 = PMCS1 functions as ch<br>0x = PMCS1 functions as ac           | •                                                                                         |                                    |  |  |  |  |  |

| bit 5         | ALP: Address Latch Polarity                                                         | ALP: Address Latch Polarity bit <sup>(1)</sup>                                            |                                    |  |  |  |  |  |

|               | 1 = Active-high (PMALL and<br>0 = Active-low (PMALL and                             |                                                                                           |                                    |  |  |  |  |  |

| bit 4         | Unimplemented: Read as '0                                                           | ,                                                                                         |                                    |  |  |  |  |  |

| bit 3         | CS1P: Chip Select 1 Polarity                                                        | bit <sup>(1)</sup>                                                                        |                                    |  |  |  |  |  |

|               | 1 = Active-high (PMCS1/PM<br>0 = Active-low (PMCS1/PM                               |                                                                                           |                                    |  |  |  |  |  |

Note 1: These bits have no effect when their corresponding pins are used as address lines.

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0                     | U-0    |

|-----------------|-----|------------------|-----|-----------------------------------------|-----|-------------------------|--------|

| —               |     | —                |     |                                         |     | —                       | —      |

| bit 15          |     |                  |     |                                         |     |                         | bit 8  |

|                 |     |                  |     |                                         |     |                         |        |

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | R/W-0                   | R/W-0  |

|                 | _   | —                | _   |                                         | —   | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7           |     |                  |     |                                         |     |                         | bit 0  |

|                 |     |                  |     |                                         |     |                         |        |

| Legend:         |     |                  |     |                                         |     |                         |        |

| R = Readable    | bit | W = Writable I   | oit | U = Unimplemented bit, read as '0'      |     |                         |        |

| -n = Value at P | POR | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |                         | wn     |

| utput Select bit <sup>(1)</sup> |

|---------------------------------|

| for the RTCC pin the RTCC pin   |

| the RICC pill                   |

| fer Select bit                  |

| ers                             |

| er input buffers                |

| f                               |

**Note 1:** To enable the actual RTCC output, the RTCOE bit (RCFGCAL<10>) needs to be set.

## 27.4 Watchdog Timer (WDT)

For dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

### 27.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler than can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TwDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any form of device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### All Device Resets Transition to New Clock Source Exit Sleep or Idle Mode PWRSAV Instruction CLRWDT Instruction Watchdog Timer Sleep/Idle WDTPRE WDTPOST<3:0> SWDTEN WDT Wake-up FWDTEN Prescaler Postscaler WDT LPRC Clock (divide by N1) (divide by N2) Reset WDT Window Select WINDIS CLRWDT Instruction

## FIGURE 27-2: WDT BLOCK DIAGRAM

## 27.4.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) needs to be cleared in software after the device wakes up.

## 27.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

| Note: | If the WINDIS bit (FWDT<6>) is cleared, the   |

|-------|-----------------------------------------------|

|       | CLRWDT instruction should be executed by      |

|       | the application software only during the last |

|       | 1/4 of the WDT period. This CLRWDT win-       |

|       | dow can be determined by using a timer. If    |

|       | a CLRWDT instruction is executed before       |

|       | this window, a WDT Reset occurs.              |

|       |                                               |

The WDT flag, WDTO bit (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

|              |        |                                                                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |                    |     |       |                              |

|--------------|--------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|------------------------------|

| Param<br>No. | Symbol | Characteristic                                                      |                                                                                                                                                                                                       | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                   |

| OS50         | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                                                                                                                                                                                                       | 0.8 |                    | 8   | MHz   | ECPLL, HSPLL, XTPLL<br>modes |

| OS51         | Fsys   | On-Chip VCO System<br>Frequency                                     |                                                                                                                                                                                                       | 100 | —                  | 200 | MHz   | —                            |

| OS52         | TLOCK  | PLL Start-up Time (Lock Time)                                       |                                                                                                                                                                                                       | 0.9 | 1.5                | 3.1 | mS    | —                            |

| OS53         | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                              |                                                                                                                                                                                                       | -3  | 0.5                | 3   | %     | Measured over 100 ms period  |

### TABLE 30-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral Clock Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: Fosc = 32 MHz, DCLK = 3%, SPI bit rate clock, (i.e., SCK) is 2 MHz.

$$SPI SCK Jitter = \left\lfloor \frac{D_{CLK}}{\sqrt{\left(\frac{32 \ MHz}{2 \ MHz}\right)}} \right\rfloor = \left\lfloor \frac{3\%}{\sqrt{16}} \right\rfloor = \left\lfloor \frac{3\%}{4} \right\rfloor = 0.75\%$$

### TABLE 30-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHA       | RACTERISTICS                                      | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |     |     |       |                                         |                |  |

|--------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------------------------------|----------------|--|

| Param<br>No. | Characteristic                                    | Min                                                                                                                                                                                                                                                                            | Тур | Max | Units | Conditions                              |                |  |

|              | Internal FRC Accuracy @ 7.3728 MHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                                |     |     |       |                                         |                |  |

| F20a         | FRC                                               | -2                                                                                                                                                                                                                                                                             | —   | +2  | %     | $-40^\circ C \le T A \le +85^\circ C$   | VDD = 3.0-3.6V |  |

| F20b         | FRC                                               | -5                                                                                                                                                                                                                                                                             | _   | +5  | %     | $-40^{\circ}C \le TA \le +125^{\circ}C$ | VDD = 3.0-3.6V |  |

Note 1: Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

### TABLE 30-19: INTERNAL RC ACCURACY

| AC CH        | ARACTERISTICS                    | $\begin{array}{ c c c c c c } \hline Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) \\ \hline Operating temperature & -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ for Extended} \\ \hline \end{array}$ |     |     |       |                                        |                |  |

|--------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|----------------------------------------|----------------|--|

| Param<br>No. | Characteristic                   | Min                                                                                                                                                                                                                                                                                                 | Тур | Max | Units | Conditions                             |                |  |

|              | LPRC @ 32.768 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                     |     |     |       |                                        |                |  |

| F21a         | LPRC                             | -20                                                                                                                                                                                                                                                                                                 | ±6  | +20 | %     | $-40^{\circ}C \le TA \le +85^{\circ}C$ | VDD = 3.0-3.6V |  |

| F21b         | LPRC                             | -30                                                                                                                                                                                                                                                                                                 | _   | +30 | %     | $-40^\circ C \le T_A \le +125^\circ C$ | VDD = 3.0-3.6V |  |

**Note 1:** Change of LPRC frequency as VDD changes.

<sup>© 2007-2012</sup> Microchip Technology Inc.

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

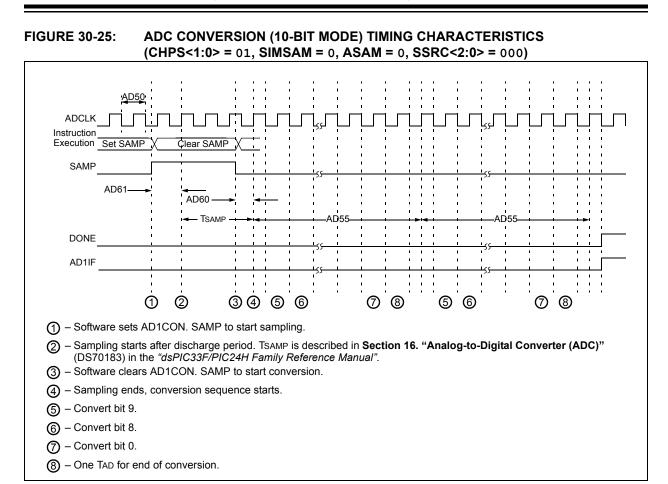

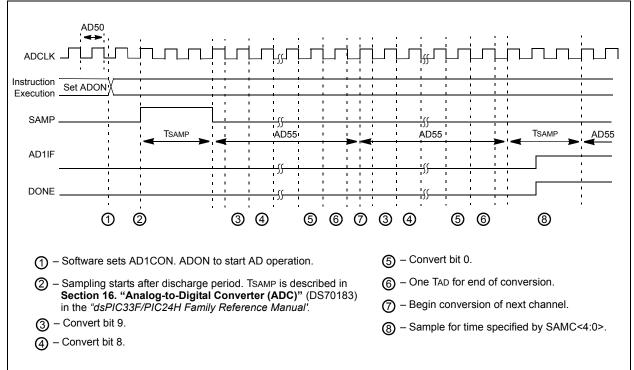

FIGURE 30-26:ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01,<br/>SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

#### © 2007-2012 Microchip Technology Inc.

### TABLE 31-14: ADC MODULE SPECIFICATIONS

| -                   | AC<br>TERISTICS  | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature-40°C ≤TA ≤+150°C for High Temperature |     |          |           |          |                                                  |  |

|---------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------|----------|--------------------------------------------------|--|

| Param<br>No. Symbol |                  | Characteristic                                                                                                                   | Min | Тур      | Мах       | Units    | Conditions                                       |  |

|                     | Reference Inputs |                                                                                                                                  |     |          |           |          |                                                  |  |

| HAD08               | IREF             | Current Drain                                                                                                                    |     | 250<br>— | 600<br>50 | μΑ<br>μΑ | ADC operating, See Note 1<br>ADC off, See Note 1 |  |

Note 1: These parameters are not characterized or tested in manufacturing.

2: These parameters are characterized, but are not tested in manufacturing.

## TABLE 31-15: ADC MODULE SPECIFICATIONS (12-BIT MODE)

| -            | AC<br>TERISTICS |                            |           |           |            |                   |                                                  |

|--------------|-----------------|----------------------------|-----------|-----------|------------|-------------------|--------------------------------------------------|

| Param<br>No. | Symbol          | Characteristic Min Typ Max |           | Units     | Conditions |                   |                                                  |

|              | ADO             | C Accuracy (12-bit Mode    | ) – Meas  | urement   | ts with Ex | cternal V         | /REF+/VREF- <sup>(1)</sup>                       |

| HAD20a       | Nr              | Resolution <sup>(3)</sup>  | 1         | 2 data bi | its        | bits              |                                                  |

| HAD21a       | INL             | Integral Nonlinearity      | -2        | _         | +2         | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD22a       | DNL             | Differential Nonlinearity  | > -1      | _         | < 1        | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD23a       | Gerr            | Gain Error                 | -2        | —         | 10         | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD24a       | EOFF            | Offset Error               | -3        | _         | 5          | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

|              | AD              | C Accuracy (12-bit Mode    | e) – Meas | uremen    | ts with In | ternal V          | /REF+/VREF- <sup>(1)</sup>                       |

| HAD20a       | Nr              | Resolution <sup>(3)</sup>  | 1         | 2 data bi | its        | bits              |                                                  |

| HAD21a       | INL             | Integral Nonlinearity      | -2        | _         | +2         | LSb               | VINL = AVSS = 0V, AVDD = 3.6V                    |

| HAD22a       | DNL             | Differential Nonlinearity  | > -1      | —         | < 1        | LSb               | VINL = AVSS = 0V, AVDD = 3.6V                    |

| HAD23a       | Gerr            | Gain Error                 | 2         |           | 20         | LSb               | VINL = AVSS = 0V, AVDD = 3.6V                    |

| HAD24a       | EOFF            | Offset Error               | 2         | —         | 10         | LSb               | VINL = AVSS = 0V, AVDD = 3.6V                    |

|              |                 | Dynamic I                  | Performa  | nce (12   | -bit Mode  | e) <sup>(2)</sup> |                                                  |

| HAD33a       | Fnyq            | Input Signal Bandwidth     | —         | —         | 200        | kHz               | —                                                |

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

128:1

40

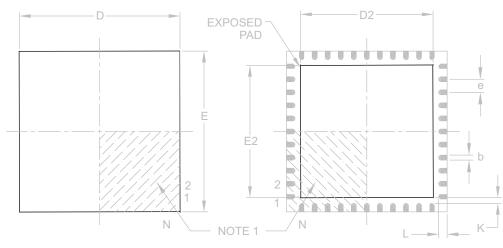

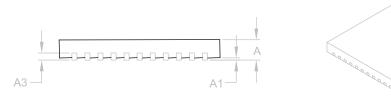

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

**BOTTOM VIEW**

|                        | Units           |          | MILLIMETERS | 6    |

|------------------------|-----------------|----------|-------------|------|

| Dimens                 | sion Limits     | MIN      | NOM         | MAX  |

| Number of Pins         | Ν               |          | 44          |      |

| Pitch                  | е               |          | 0.65 BSC    |      |

| Overall Height         | Α               | 0.80     | 0.90        | 1.00 |

| Standoff               | A1              | 0.00     | 0.02        | 0.05 |

| Contact Thickness      | A3              | 0.20 REF |             |      |

| Overall Width          | E               | 8.00 BSC |             |      |

| Exposed Pad Width      | E2              | 6.30     | 6.45        | 6.80 |

| Overall Length         | ngth D 8.00 BSC |          |             |      |

| Exposed Pad Length     | D2              | 6.30     | 6.45        | 6.80 |

| Contact Width          | b               | 0.25     | 0.30        | 0.38 |

| Contact Length         | L               | 0.30     | 0.40        | 0.50 |

| Contact-to-Exposed Pad | K               | 0.20     | -           | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

## APPENDIX A: REVISION HISTORY

### **Revision A (September 2007)**

This is the initial released version of this document.

## **Revision B (March 2008)**

This revision includes minor typographical and formatting changes throughout the data sheet text. In addition, redundant information was removed that is now available in the respective chapters of the *dsPIC33F/PIC24H Family Reference Manual*, which can be obtained from the Microchip website (www.microchip.com).

The major changes are referenced by their respective section in the following table.

### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                    | Update Description                                                                                                                                        |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit Digital Signal Controllers"           | Note 1 added to all pin diagrams (see "Pin Diagrams").                                                                                                    |

|                                                                 | Add External Interrupts column and Note 3 to the<br>"dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and<br>dsPIC33FJ128GPX02/X04 Controller Families" table. |

| Section 1.0 "Device Overview"                                   | Updated parameters PMA0, PMA1, and PMD0 through PMPD7 (Table 1-1).                                                                                        |

| Section 6.0 "Interrupt Controller"                              | IFS0-IFSO4 changed to IFSx (see Section 6.3.2 "IFSx").                                                                                                    |

|                                                                 | IEC0-IEC4 changed to IECx (see Section 6.3.3 "IECx").                                                                                                     |

|                                                                 | IPC0-IPC19 changed to IPCx (see Section 6.3.4 "IPCx").                                                                                                    |

| Section 7.0 "Direct Memory Access (DMA)"                        | Updated parameter PMP (see Table 7-1).                                                                                                                    |

| Section 8.0 "Oscillator Configuration"                          | Updated the third clock source item (External Clock) in Section 8.1.1 "System Clock Sources".                                                             |

|                                                                 | Updated TUN<5:0> (OSCTUN<5:0>) bit description (see Register 8-4).                                                                                        |

| Section 20.0 "10-bit/12-bit Analog-to-Digital Converter (ADC1)" | Added Note 2 to Figure 20-3.                                                                                                                              |

| Section 26.0 "Special Features"                                 | Added Note 2 to Figure 26-1.                                                                                                                              |

|                                                                 | Added Note after second paragraph in <b>Section 26.2 "On-Chip Voltage Regulator".</b>                                                                     |

| Section 29.0 "Electrical Characteristics"                       | Updated Max MIPS for temperature range of -40°C to +125°C in Table 29-1.                                                                                  |

|                                                                 | Updated typical values in Thermal Packaging Characteristics in Table 29-3.                                                                                |

|                                                                 | Added parameters DI11 and DI12 to Table 29-9.                                                                                                             |

|                                                                 | Updated minimum values for parameters D136 (TRw) and D137 (TPE) and removed typical values in Table 29-12.                                                |

|                                                                 | Added Extended temperature range to Table 29-13.                                                                                                          |

|                                                                 | Updated parameter AD63 and added Note 3 to Table 29-40 and Table 29-41.                                                                                   |

## Revision F (August 2011)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

### TABLE A-5: MAJOR SECTION UPDATES

| Section Name                                                                        | Update Description                                                                                                                 |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Updated the Recommendation Minimum Connection (see Figure 2-1).                                                                    |

| Section 27.0 "Special Features"                                                     | Added Note 3 to the Connections for the On-chip Voltage Regulator diagram (see Figure 27-1).                                       |

| Section 30.0 "Electrical Characteristics"                                           | Removed Voltage on VCAP with respect to Vss from the Absolute Maximum Ratings.                                                     |

|                                                                                     | Removed Note 3 and parameter DC10 (VCORE) from the DC Temperature and Voltage Specifications (see Table 30-4).                     |

|                                                                                     | Updated the Characteristics definition and Conditions for parameter BO10 in the Electrical Characteristics: BOR (see Table 30-11). |

|                                                                                     | Added Note 1 to the Internal Voltage Regulator Specifications (see Table 30-13).                                                   |

## **Revision G (April 2012)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 9.2 "Oscillator Resources" and Section 21.4 "ADC Helpful Tips".

All other major changes are referenced by their respective section in the following table.

### TABLE A-6: MAJOR SECTION UPDATES

| Section Name                                                                        | Update Description                                                                                                                                     |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Added two new tables:<br>• Crystal Recommendations (see Table 2-1)                                                                                     |

|                                                                                     | Resonator Recommendations (see Table 2-2)                                                                                                              |

| Section 30.0 "Electrical Characteristics"                                           | Updated parameters DO10 and DO20 and removed parameters<br>DO16 and DO26 in the DC Characteristics: I/O Pin Output<br>Specifications (see Table 30-10) |