#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp302t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04 PRODUCT **FAMILIES**

The device names, pin counts, memory sizes, and peripheral availability of each device are listed below. The following pages show their pinout diagrams.

#### TABLE 1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04 **CONTROLLER FAMILIES**

|                   |      |                                 |                            |                 |                             | Rem           | appabl                         | e Peri                   | phera | al  |       |                                    |      |                                |               |                                 |                         | r)                                                  |                                               |          |                        |

|-------------------|------|---------------------------------|----------------------------|-----------------|-----------------------------|---------------|--------------------------------|--------------------------|-------|-----|-------|------------------------------------|------|--------------------------------|---------------|---------------------------------|-------------------------|-----------------------------------------------------|-----------------------------------------------|----------|------------------------|

| Device            | Pins | Program Flash Memory<br>(Kbyte) | RAM (Kbyte) <sup>(1)</sup> | Remappable Pins | 16-bit Timer <sup>(2)</sup> | Input Capture | Output Compare<br>Standard PWM | Data Converter Interface | UART  | IdS | ECAN™ | External Interrupts <sup>(3)</sup> | RTCC | I <sup>2</sup> C <sup>TM</sup> | CRC Generator | 10-bit/12-bit ADC<br>(Channels) | 16-bit Audio DAC (Pins) | Analog Comparator<br>(2 Channels/Voltage Regulator) | 8-bit Parallel Master<br>Port (Address Lines) | I/O Pins | Packages               |

| dsPIC33FJ128GP804 | 44   | 128                             | 16                         | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 13                              | 6                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128GP802 | 28   | 128                             | 16                         | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 10                              | 4                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ128GP204 | 44   | 128                             | 8                          | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 13                              | 0                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ128GP202 | 28   | 128                             | 8                          | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 10                              | 0                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64GP804  | 44   | 64                              | 16                         | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 13                              | 6                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64GP802  | 28   | 64                              | 16                         | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 1     | 3                                  | 1    | 1                              | 1             | 10                              | 4                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ64GP204  | 44   | 64                              | 8                          | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 13                              | 0                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ64GP202  | 28   | 64                              | 8                          | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 10                              | 0                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

| dsPIC33FJ32GP304  | 44   | 32                              | 4                          | 26              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 13                              | 0                       | 1/1                                                 | 11                                            | 35       | QFN<br>TQFP            |

| dsPIC33FJ32GP302  | 28   | 32                              | 4                          | 16              | 5                           | 4             | 4                              | 1                        | 2     | 2   | 0     | 3                                  | 1    | 1                              | 1             | 10                              | 0                       | 1/0                                                 | 2                                             | 21       | SPDIP<br>SOIC<br>QFN-S |

Note RAM size is inclusive of 2 Kbytes of DMA RAM for all devices except dsPIC33FJ32GP302/304, which include 1 Kbyte of DMA RAM. 1:

2: 3: Only four out of five timers are remappable.

Only two out of three interrupts are remappable.

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) |  |

|------------|-------------------------|-------------|--|

|------------|-------------------------|-------------|--|

| Pin Name | Pin<br>Type | Buffer<br>Type | PPS | Description                                        |

|----------|-------------|----------------|-----|----------------------------------------------------|

| AVss     | Р           | Р              | No  | Ground reference for analog modules.               |

| Vdd      | Р           | —              | No  | Positive supply for peripheral logic and I/O pins. |

| VCAP     | Р           | _              | No  | CPU logic filter capacitor connection.             |

| Vss      | Р           | _              | No  | Ground reference for logic and I/O pins.           |

| VREF+    | I           | Analog         | No  | Analog voltage reference (high) input.             |

| VREF-    | I           | Analog         | No  | Analog voltage reference (low) input.              |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer Analog = Analog inputP = PowerO = OutputI = InputPPS = Peripheral Pin Select

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) DS51749

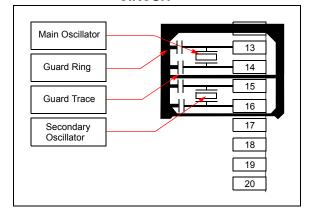

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3. Recommendations for crystals and ceramic resonators are provided in Table 2-1 and Table 2-2, respectively.

# FIGURE 2-3:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| Part<br>Number         | Vendor   | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |

|------------------------|----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|

| ECS-40-20-4DN          | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-80-18-4DN          | ECS Inc. | 8 MHz  | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-100-18-4-DN        | ECS Inc. | 10 MHz | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-200-20-4DN         | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-40-20-5G3XDS-TR    | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-80-20-5G3XDS-TR    | ECS Inc. | 8 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-100-20-5G3XDS-TR   | ECS Inc. | 10 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-200-20-5G3XDS-TR   | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to 125°C           |

| NX3225SA 20MHZ AT-W    | NDK      | 20 MHz | 8 pF         | 3.2 mm x 2.5 mm | ±50 ppm                | SM               | -40°C to 125°C           |

| Legend: TH = Through I | Hole     | SM     | = Surface I  | Nount           |                        |                  |                          |

## TABLE 2-1: CRYSTAL RECOMMENDATIONS

| TABLE 4     | 4-5:        | TIMEF      | R REGIS     | TER MA    | ٨P          |               |             |              |              |                |              |       |        |       |       |       |       |               |

|-------------|-------------|------------|-------------|-----------|-------------|---------------|-------------|--------------|--------------|----------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15     | Bit 14      | Bit 13    | Bit 12      | Bit 11        | Bit 10      | Bit 9        | Bit 8        | Bit 7          | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |            |             |           |             |               |             |              | Timer1       | Register       |              |       |        |       |       |       |       | 0000          |

| PR1         | 0102        |            |             |           |             |               |             |              | Period F     | Register 1     |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON        | _           | TSIDL     | _           | _             | _           | _            | —            | —              | TGATE        | TCKP  | S<1:0> |       | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106        |            |             |           |             |               |             |              | Timer2       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |            |             |           |             |               | Tin         | ner3 Holding | Register (fo | r 32-bit timeı | operations o | only) |        |       |       |       |       | XXXX          |

| TMR3        | 010A        |            |             |           |             |               |             |              | Timer3       | Register       |              |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |            |             |           |             |               |             |              | Period F     | Register 2     |              |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |            |             |           |             |               |             |              | Period F     | Register 3     |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON        | _           | TSIDL     | _           | _             | _           | _            | _            | _              | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112        | TON        |             | TSIDL     |             |               |             | _            | —            | —              | TGATE        | TCKP  | S<1:0> | —     | _     | TCS   | —     | 0000          |

| TMR4        | 0114        |            |             |           |             |               |             |              | Timer4       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        |            |             |           |             |               | Tin         | ner5 Holding | Register (fo | r 32-bit timeı | operations o | only) |        |       |       |       |       | XXXX          |

| TMR5        | 0118        |            |             |           |             |               |             |              | Timer5       | Register       |              |       |        |       |       |       |       | 0000          |

| PR4         | 011A        |            |             |           |             |               |             |              | Period F     | Register 4     |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C        |            |             |           |             |               |             |              | Period F     | Register 5     |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E        | TON        |             | TSIDL     |             |               |             | _            | _            | -              | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON        |             | TSIDL     |             |               |             | _            | _            | -              | TGATE        | TCKP  | S<1:0> | —     | —     | TCS   | _     | 0000          |

| Legend:     | x = un      | known valu | e on Reset, | — = unimp | lemented, r | ead as '0'. F | Reset value | s are showr  | in hexadeo   | cimal.         |              |       |        |       |       |       |       |               |

# TABLE 4-6: INPUT CAPTURE REGISTER MAP

|             |             |        | •/     |        |        | · •••• |        |       |            |               |       |       |       |       |       |          |       |               |

|-------------|-------------|--------|--------|--------|--------|--------|--------|-------|------------|---------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF      | 0140        |        |        |        |        |        |        |       | Input 1 Ca | pture Regist  | er    |       |       |       |       |          |       | XXXX          |

| IC1CON      | 0142        | —      |        | ICSIDL | —      |        | -      |       |            | ICTMR         | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF      | 0144        |        |        |        |        |        |        |       | Input 2 Ca | pture Regist  | er    |       |       |       |       |          |       | XXXX          |

| IC2CON      | 0146        | —      |        | ICSIDL | —      |        | _      |       |            | ICTMR         | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF      | 0158        |        |        |        |        |        |        |       | Input 7 Ca | pture Regist  | er    |       |       |       |       |          |       | XXXX          |

| IC7CON      | 015A        | —      | _      | ICSIDL | —      |        |        |       |            | ICTMR         | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF      | 015C        |        |        |        |        |        |        |       | Input 8Ca  | pture Registe | er    |       |       |       |       |          |       | XXXX          |

| IC8CON      | 015E        | —      |        | ICSIDL | —      |        | _      |       |            | ICTMR         | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

|             |             |        |        |        |        |        |        |       |            |               |       |       |       |       |       |          |       |               |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-22:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ128GP202/802, dsPIC33FJ64GP202/802 AND<br/>dsPIC33FJ32GP302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPOR0     | 06C0 | _      | _      | —      |        |        | RP1R<4:0  | >     |       | —     | _     | _     |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1     | 06C2 | _      | _      | _      |        |        | RP3R<4:0> | >     |       | _     | _     | _     |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2     | 06C4 | _      | _      | _      |        |        | RP5R<4:0> | >     |       | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3     | 06C6 |        | _      | _      |        |        | RP7R<4:0> | >     |       | -     | _     | _     |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4     | 06C8 | _      | _      | _      |        |        | RP9R<4:0> | >     |       | _     | _     | _     |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5     | 06CA | _      | _      | _      |        |        | RP11R<4:0 | >     |       | _     | _     | _     |       | I     | RP10R<4:0> |       |       | 0000          |

| RPOR6     | 06CC | _      | _      | _      |        |        | RP13R<4:0 | >     |       | _     |       | _     |       |       | RP12R<4:0> |       |       | 0000          |

| RPOR7     | 06CE | _      | _      | _      |        |        | RP15R<4:0 | >     |       | _     | _     | _     |       |       | RP14R<4:0> |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ128GP204/804, dsPIC33FJ64GP204/804 AND dsPIC33FJ32GP304

|           |      | 401 100 | 51 552 |        |        |        |           |       |       |       |       |       |       |       |            |       |       |               |

|-----------|------|---------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| File Name | Addr | Bit 15  | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0     | 06C0 | _       | —      | —      |        |        | RP1R<4:0> | >     |       | _     | —     | —     |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1     | 06C2 | _       | —      | _      |        |        | RP3R<4:0> | >     |       | -     | _     | _     |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2     | 06C4 | _       | _      | _      |        |        | RP5R<4:0  | >     |       | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3     | 06C6 | _       | _      | _      |        |        | RP7R<4:0  | >     |       | _     | _     |       |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4     | 06C8 | _       |        | _      |        |        | RP9R<4:0> | >     |       | _     | _     |       |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5     | 06CA | _       | _      | _      |        |        | RP11R<4:0 | >     |       | _     | _     |       |       |       | RP10R<4:0> |       |       | 0000          |

| RPOR6     | 06CC | _       | _      | _      |        |        | RP13R<4:0 | >     |       | _     | _     | _     |       |       | RP12R<4:0> |       |       | 0000          |

| RPOR7     | 06CE | _       | _      | _      |        |        | RP15R<4:0 | >     |       | _     | _     | _     |       |       | RP14R<4:0> |       |       | 0000          |

| RPOR8     | 06D0 | _       | _      | _      |        |        | RP17R<4:0 | >     |       | _     | _     |       |       |       | RP16R<4:0> |       |       | 0000          |

| RPOR9     | 06D2 | _       | _      | _      |        |        | RP19R<4:0 | >     |       | _     | _     |       |       |       | RP18R<4:0> |       |       | 0000          |

| RPOR10    | 06D4 | _       | _      | _      |        |        | RP21R<4:0 | >     |       | _     | _     | _     |       |       | RP20R<4:0> |       |       | 0000          |

| RPOR11    | 06D6 | _       | _      | _      |        |        | RP23R<4:0 | >     |       | _     | _     | _     |       |       | RP22R<4:0> |       |       | 0000          |

| RPOR12    | 06D8 | _       | _      | —      |        |        | RP25R<4:0 | >     |       | _     | _     | _     |       |       | RP24R<4:0> |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|-------|-------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | <ol> <li>Stack error trap has occurred</li> </ol>                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

| REGISTER      | 7-11: IEC1:     | INTERRUPT                          | ENABLE CO       |                  | GISTER 1        |                 |         |

|---------------|-----------------|------------------------------------|-----------------|------------------|-----------------|-----------------|---------|

| R/W-0         | R/W-0           | R/W-0                              | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| U2TXIE        | U2RXIE          | INT2IE                             | T5IE            | T4IE             | OC4IE           | OC3IE           | DMA2IE  |

| bit 15        |                 |                                    |                 |                  |                 |                 | bit 8   |

| R/W-0         | R/W-0           | U-0                                | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0   |

| IC8IE         | IC7IE           |                                    | INT1IE          | CNIE             | CMIE            | MI2C1IE         | SI2C1IE |

| bit 7         | IGHE            |                                    |                 | ONIL             | OWIL            | WIZOTIE         | bit 0   |

|               |                 |                                    |                 |                  |                 |                 |         |

| Legend:       |                 |                                    | L :4            |                  |                 | -l (O'          |         |

| R = Readable  |                 | W = Writable                       |                 |                  | nented bit, rea |                 |         |

| -n = Value at | POR             | '1' = Bit is set                   |                 | '0' = Bit is cle | ared            | x = Bit is unkr | IOWN    |

| bit 15        | U2TXIE: UAF     | RT2 Transmitter                    | r Interrupt Ena | able bit         |                 |                 |         |

|               |                 | request enable                     |                 |                  |                 |                 |         |

|               | 0 = Interrupt i | request not ena                    | abled           |                  |                 |                 |         |

| bit 14        |                 | RT2 Receiver Ir                    | •               | e bit            |                 |                 |         |

|               |                 | request enable                     |                 |                  |                 |                 |         |

| h:+ 40        | •               | request not ena                    |                 |                  |                 |                 |         |

| bit 13        |                 | rnal Interrupt 2<br>request enable |                 |                  |                 |                 |         |

|               |                 | request enable                     |                 |                  |                 |                 |         |

| bit 12        | T5IE: Timer5    | Interrupt Enab                     | le bit          |                  |                 |                 |         |

|               |                 | request enable                     |                 |                  |                 |                 |         |

|               | •               | request not ena                    |                 |                  |                 |                 |         |

| bit 11        |                 | Interrupt Enab                     |                 |                  |                 |                 |         |

|               |                 | request enable<br>request not ena  |                 |                  |                 |                 |         |

| bit 10        | -               | ut Compare Ch                      |                 | upt Enable bit   |                 |                 |         |

|               | •               | request enable                     |                 |                  |                 |                 |         |

|               |                 | request not ena                    |                 |                  |                 |                 |         |

| bit 9         | OC3IE: Output   | ut Compare Ch                      | annel 3 Interr  | upt Enable bit   |                 |                 |         |

|               |                 | request enable<br>request not ena  |                 |                  |                 |                 |         |

| bit 8         | DMA2IE: DM      | IA Channel 2 D                     | ata Transfer C  | Complete Interr  | upt Enable bit  |                 |         |

|               | •               | request enable                     |                 |                  |                 |                 |         |

|               |                 | request not ena                    |                 |                  |                 |                 |         |

| bit 7         |                 | Capture Chann                      | -               | Enable bit       |                 |                 |         |

|               |                 | request enable<br>request not ena  |                 |                  |                 |                 |         |

| bit 6         | -               | Capture Chann                      |                 | Enable bit       |                 |                 |         |

|               | •               | request enable                     |                 |                  |                 |                 |         |

|               | 0 = Interrupt i | request not ena                    | abled           |                  |                 |                 |         |

| bit 5         | Unimplemen      | ted: Read as '                     | 0'              |                  |                 |                 |         |

| bit 4         |                 | rnal Interrupt 1                   |                 |                  |                 |                 |         |

|               |                 | request enable                     |                 |                  |                 |                 |         |

| bit 3         | -               | request not ena<br>Change Notifica |                 | Enable bit       |                 |                 |         |

| DIL D         | -               | request enable                     | -               |                  |                 |                 |         |

|               |                 | request not ena                    |                 |                  |                 |                 |         |

####

| U-0                                  | U-0                        | U-0                                                                                                                                                   | U-0                                                                                                            | U-0                                | R/W-1          | R/W-0           | R/W-0   |

|--------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----------------|---------|

|                                      | —                          | —                                                                                                                                                     | —                                                                                                              | —                                  |                | DMA1IP<2:0>     |         |

| oit 15                               |                            |                                                                                                                                                       |                                                                                                                |                                    |                |                 | bit 8   |

| U-0                                  | R/W-1                      | R/W-0                                                                                                                                                 | R/W-0                                                                                                          | U-0                                | R/W-1          | R/W-0           | R/W-0   |

|                                      | N/W-1                      | AD1IP<2:0>                                                                                                                                            | N/W-U                                                                                                          | 0-0                                | FV/ V V = 1    | U1TXIP<2:0>     | N/ VV-U |

| bit 7                                |                            | 7.D m 32.0                                                                                                                                            |                                                                                                                |                                    |                | 011701 42.02    | bit (   |

| Legend:                              |                            |                                                                                                                                                       |                                                                                                                |                                    |                |                 |         |

| R = Readab                           | le hit                     | W = Writable                                                                                                                                          | hit                                                                                                            | U = Unimplen                       | nented bit rea | ad as '0'       |         |

| -n = Value a                         |                            | '1' = Bit is set                                                                                                                                      | 5 N                                                                                                            | '0' = Bit is cle                   |                | x = Bit is unkn | own     |

|                                      |                            |                                                                                                                                                       |                                                                                                                |                                    |                |                 |         |

| bit 15-11                            | Unimpleme                  | nted: Read as '                                                                                                                                       | )'                                                                                                             |                                    |                |                 |         |

| bit 10-8                             | -                          | 0>: DMA Channe                                                                                                                                        |                                                                                                                | nsfer Complete                     | Interrupt Prio | ritv bits       |         |

|                                      |                            | upt is priority 7 (I                                                                                                                                  |                                                                                                                |                                    |                | ,               |         |

|                                      | •                          |                                                                                                                                                       | •                                                                                                              |                                    |                |                 |         |

|                                      | •                          |                                                                                                                                                       |                                                                                                                |                                    |                |                 |         |

|                                      | •                          | untin mainaite d                                                                                                                                      |                                                                                                                |                                    |                |                 |         |

|                                      |                            | upt is priority 1<br>upt source is dis                                                                                                                | abled                                                                                                          |                                    |                |                 |         |

|                                      |                            |                                                                                                                                                       |                                                                                                                |                                    |                |                 |         |

| bit 7                                | Unimpleme                  | -                                                                                                                                                     |                                                                                                                |                                    |                |                 |         |

|                                      | -                          | nted: Read as '                                                                                                                                       | )'                                                                                                             | e Interrupt Prior                  | itv bits       |                 |         |

|                                      | AD1IP<2:0>                 | nted: Read as '(<br>ADC1 Converse                                                                                                                     | )'<br>sion Complet                                                                                             | •                                  | ity bits       |                 |         |

|                                      | AD1IP<2:0>                 | nted: Read as '                                                                                                                                       | )'<br>sion Complet                                                                                             | •                                  | ity bits       |                 |         |

|                                      | AD1IP<2:0>                 | nted: Read as '(<br>ADC1 Converse                                                                                                                     | )'<br>sion Complet                                                                                             | •                                  | ity bits       |                 |         |

|                                      | AD1IP<2:0><br>111 = Intern | nted: Read as '(<br>ADC1 Converse<br>upt is priority 7 (I                                                                                             | )'<br>sion Complet                                                                                             | •                                  | ity bits       |                 |         |

|                                      | AD1IP<2:0> 111 = Intern    | nted: Read as '(<br>ADC1 Convers<br>upt is priority 7 (I<br>upt is priority 1                                                                         | <sub>)</sub> '<br>sion Complet<br>nighest priori                                                               | •                                  | ity bits       |                 |         |

| bit 6-4                              | AD1IP<2:0> 111 = Intern    | nted: Read as '<br>ADC1 Converse<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is disc                                                   | <sub>)</sub> '<br>sion Complet<br>nighest priori<br>abled                                                      | •                                  | ity bits       |                 |         |

| bit 6-4<br>bit 3                     | AD1IP<2:0> 111 = Intern    | nted: Read as '(<br>: ADC1 Convers<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br>nted: Read as '(                              | <sub>)</sub> ,<br>sion Complet<br>nighest priori<br>abled                                                      | ty interrupt)                      | ity bits       |                 |         |

| bit 6-4<br>bit 3                     | AD1IP<2:0> 111 = Intern    | nted: Read as '(<br>ADC1 Converse<br>upt is priority 7 (I)<br>upt is priority 1<br>upt source is disa<br>nted: Read as '(<br>)>: UART1 Trans          | <sup>o'</sup><br>sion Complet<br>nighest priori<br>abled<br>o'<br>smitter Interru                              | ty interrupt)<br>upt Priority bits | ity bits       |                 |         |

| bit 6-4<br>bit 3                     | AD1IP<2:0> 111 = Intern    | nted: Read as '(<br>: ADC1 Convers<br>upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br>nted: Read as '(                              | <sup>o'</sup><br>sion Complet<br>nighest priori<br>abled<br>o'<br>smitter Interru                              | ty interrupt)<br>upt Priority bits | ity bits       |                 |         |

| bit 6-4<br>bit 3                     | AD1IP<2:0> 111 = Intern    | nted: Read as '(<br>ADC1 Converse<br>upt is priority 7 (I)<br>upt is priority 1<br>upt source is disa<br>nted: Read as '(<br>)>: UART1 Trans          | <sup>o'</sup><br>sion Complet<br>nighest priori<br>abled<br>o'<br>smitter Interru                              | ty interrupt)<br>upt Priority bits | ity bits       |                 |         |

| bit 6-4<br>bit 3                     | AD1IP<2:0> 111 = Intern    | nted: Read as '(<br>ADC1 Conversion<br>upt is priority 7 (I)<br>upt source is disting<br>nted: Read as '(<br>)>: UART1 Trans<br>upt is priority 7 (I) | <sup>o'</sup><br>sion Complet<br>nighest priori<br>abled<br>o'<br>smitter Interru                              | ty interrupt)<br>upt Priority bits | ity bits       |                 |         |

| bit 7<br>bit 6-4<br>bit 3<br>bit 2-0 | AD1IP<2:0> 111 = Intern    | nted: Read as '(<br>ADC1 Converse<br>upt is priority 7 (I)<br>upt is priority 1<br>upt source is disa<br>nted: Read as '(<br>)>: UART1 Trans          | <sup>)'</sup><br>sion Complet<br>nighest priori<br>abled<br><sup>)'</sup><br>smitter Interru<br>nighest priori | ty interrupt)<br>upt Priority bits | ity bits       |                 |         |

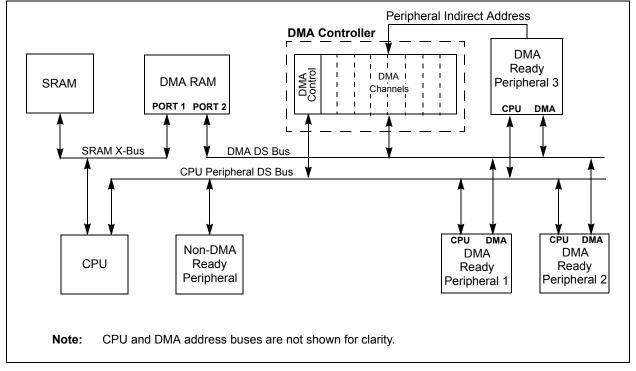

The DMA controller features eight identical data transfer channels.

Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- Eight DMA channels

- Register Indirect With Post-increment Addressing mode

- Register Indirect Without Post-increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- · Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or Automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat block transfer modes

- Ping-Pong mode (automatic switch between two DPSRAM start addresses after each block transfer complete)

- DMA request for each channel can be selected from any supported interrupt source

- · Debug support features

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

### FIGURE 8-1: TOP LEVEL SYSTEM ARCHITECTURE USING A DEDICATED TRANSACTION BUS

#### REGISTER 11-21: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is cleared x = Bit is unknown |       |           | iown  |       |

|------------------------------------|-----|-----|-----------------------------------------|-------|-----------|-------|-------|

| R = Readable bit W = Writable b    |     |     | bit U = Unimplemented bit, read as '0'  |       |           |       |       |

| Legend:                            |     |     |                                         |       |           |       |       |

|                                    |     |     |                                         |       |           |       |       |

| bit 7                              |     |     |                                         |       |           |       | bit 0 |

| —                                  | _   | —   |                                         |       | RP8R<4:0> |       |       |

| U-0                                | U-0 | U-0 | R/W-0                                   | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|                                    |     |     |                                         |       |           |       |       |

| bit 15                             |     |     | •                                       |       |           |       | bit 8 |

| _                                  |     | _   |                                         |       | RP9R<4:0> |       |       |

| U-0                                | U-0 | U-0 | R/W-0                                   | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 11-2 for peripheral function numbers)

#### REGISTER 11-22: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP11R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP10R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                                                                  |                      |                    |  |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 11-2 for peripheral function numbers)

| REGISTER 20 | -5: RSCO | N: DCI RECE | EIVE SLOT C | ONTROL RE | GISTER |        |

|-------------|----------|-------------|-------------|-----------|--------|--------|

|             |          |             |             |           |        | P///_0 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|

| RSE15                             | RSE14 | RSE13            | RSE12 | RSE11                              | RSE10 | RSE9               | RSE8  |

| bit 15                            |       | ·                |       |                                    |       |                    | bit 8 |

|                                   |       |                  |       |                                    |       |                    |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

| RSE7                              | RSE6  | RSE5             | RSE4  | RSE3                               | RSE2  | RSE1               | RSE0  |

| bit 7                             |       | ·                |       |                                    |       | •                  | bit 0 |

|                                   |       |                  |       |                                    |       |                    |       |

| Legend:                           |       |                  |       |                                    |       |                    |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR '1' =           |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |

bit 15-0

RSE<15:0>: Receive Slot Enable bits

1 = CSDI data is received during the individual time slot n

0 = CSDI data is ignored during the individual time slot n

### REGISTER 20-6: TSCON: DCI TRANSMIT SLOT CONTROL REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|-----------------------------------------|-------|-------|-------|-------|

| TSE15                              | TSE14 | TSE13 | TSE12                                   | TSE11 | TSE10 | TSE9  | TSE8  |

| bit 15                             |       | -     |                                         |       | •     |       | bit 8 |

|                                    |       |       |                                         |       |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| TSE7                               | TSE6  | TSE5  | TSE4                                    | TSE3  | TSE2  | TSE1  | TSE0  |

| bit 7                              |       |       |                                         |       | •     |       | bit 0 |

|                                    |       |       |                                         |       |       |       |       |

| Legend:                            |       |       |                                         |       |       |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0'      |       |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |       |

bit 15-0

TSE<15:0>: Transmit Slot Enable Control bits

1 = Transmit buffer contents are sent during the individual time slot n

0 = CSDO pin is tri-stated or driven to logic '0', during the individual time slot, depending on the state of the CSDOM bit

| TABLE 27-2:             | ABLE 27-2: dsPIC CONFIGURATION BITS DESCRIPTION |             |                                                                                                                                                              |  |  |  |  |  |

|-------------------------|-------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field               | Register                                        | RTSP Effect | Description                                                                                                                                                  |  |  |  |  |  |

| BWRP                    | FBS                                             | Immediate   | Boot Segment Program Flash Write Protection<br>1 = Boot segment can be written<br>0 = Boot segment is write-protected                                        |  |  |  |  |  |

| BSS<2:0>                | FBS                                             | Immediate   | Boot Segment Program Flash Code Protection Size<br>x11 = No Boot program Flash segment                                                                       |  |  |  |  |  |

|                         |                                                 |             | Boot space is 1K Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends at<br>0x0007FE                     |  |  |  |  |  |

|                         |                                                 |             | 010 = High security; boot program Flash segment ends at<br>0x0007FE                                                                                          |  |  |  |  |  |

|                         |                                                 |             | Boot space is 4K Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends at<br>0x001FFE                    |  |  |  |  |  |

|                         |                                                 |             | 001 = High security; boot program Flash segment ends at<br>0x001FFE                                                                                          |  |  |  |  |  |

|                         |                                                 |             | Boot space is 8K Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends at<br>0x003FFE                     |  |  |  |  |  |

|                         |                                                 |             | 000 = High security; boot program Flash segment ends at<br>0x003FFE                                                                                          |  |  |  |  |  |

| RBS<1:0> <sup>(1)</sup> | FBS                                             | Immediate   | Boot Segment RAM Code Protection Size<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 bytes<br>01 = Boot RAM is 256 bytes                                |  |  |  |  |  |

| SWRP <sup>(1)</sup>     | FSS <sup>(1)</sup>                              | Immediate   | 00 = Boot RAM is 1024 bytes<br>Secure Segment Program Flash Write-Protect bit<br>1 = Secure Segment can bet written<br>0 = Secure Segment is write-protected |  |  |  |  |  |

| SSS<2:0> <sup>(1)</sup> | FSS <sup>(1)</sup>                              | Immediate   | Secure Segment Program Flash Code Protection Size<br>(Secure segment is not implemented on 32K devices)<br>X11 = No Secure program flash segment             |  |  |  |  |  |

|                         |                                                 |             | Secure space is 4K IW less BS<br>110 = Standard security; secure program flash segment starts at<br>End of BS, ends at 0x001FFE                              |  |  |  |  |  |

|                         |                                                 |             | 010 = High security; secure program flash segment starts at<br>End of BS, ends at 0x001FFE                                                                   |  |  |  |  |  |

|                         |                                                 |             | Secure space is 8K IW less BS<br>101 = Standard security; secure program flash segment starts at<br>End of BS, ends at 0x003FFE                              |  |  |  |  |  |

|                         |                                                 |             | 001 = High security; secure program flash segment starts at<br>End of BS, ends at 0x003FFE                                                                   |  |  |  |  |  |

|                         |                                                 |             | Secure space is 16K IW less BS<br>100 = Standard security; secure program flash segment starts at<br>End of BS, ends at 007FFEh                              |  |  |  |  |  |

|                         |                                                 |             | 000 = High security; secure program flash segment starts at<br>End of BS, ends at 0x007FFE                                                                   |  |  |  |  |  |

| TABLE 27-2: | dsPIC CONFIGURATION BITS DESCRIPTION |

|-------------|--------------------------------------|

|             |                                      |

**Note 1:** This Configuration register is not available on dsPIC33FJ32GP302/304 devices.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------|---------------|----------------|--------------------------|

| 66                 | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f         | 1             | 1              | N,Z                      |

|                    |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f      | 1             | 1              | N,Z                      |

|                    |                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws       | 1             | 1              | N,Z                      |

| 67                 | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                     | 1             | 1              | None                     |

|                    |                      | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator             | 1             | 1              | None                     |

| 68                 | SE                   | SE     | Ws,Wnd          | Wnd = sign-extended Ws                | 1             | 1              | C,N,Z                    |

| 69                 | SETM                 | SETM   | f               | f = 0xFFFF                            | 1             | 1              | None                     |

|                    |                      | SETM   | WREG            | WREG = 0xFFFF                         | 1             | 1              | None                     |

|                    |                      | SETM   | Ws              | Ws = 0xFFFF                           | 1             | 1              | None                     |

| 70                 | SFTAC                | SFTAC  | Acc,Wn          | Arithmetic Shift Accumulator by (Wn)  | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

|                    |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6 | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 71                 | SL                   | SL     | f               | f = Left Shift f                      | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG          | WREG = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd           | Wd = Left Shift Ws                    | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns            | 1             | 1              | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5           | 1             | 1              | N,Z                      |

| 72                 | SUB                  | SUB    | Acc             | Subtract Accumulators                 | 1             | 1              | OA,OB,OAE<br>SA,SB,SAE   |

|                    |                      | SUB    | f               | f = f – WREG                          | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUB    | f,WREG          | WREG = f – WREG                       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUB    | #lit10,Wn       | Wn = Wn - lit10                       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                          | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUB    | Wb,#lit5,Wd     | Wd = Wb - lit5                        | 1             | 1              | C,DC,N,OV,               |

| 73                 | SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBB   | f,WREG          | WREG = f – WREG – $(\overline{C})$    | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$    | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$     | 1             | 1              | C,DC,N,OV,               |

| 74                 | SUBR                 | SUBR   | f               | f = WREG – f                          | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBR   | f,WREG          | WREG = WREG – f                       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                          | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                        | 1             | 1              | C,DC,N,OV,               |

| 75                 | SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBBR  | f,WREG          | WREG = WREG – f – $(\overline{C})$    | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$     | 1             | 1              | C,DC,N,OV,               |

| 76                 | SWAP                 | SWAP.b | Wn              | Wn = nibble swap Wn                   | 1             | 1              | None                     |

|                    |                      | SWAP   | Wn              | Wn = byte swap Wn                     | 1             | 1              | None                     |

| 77                 | TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>           | 1             | 2              | None                     |

| 78                 | TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd                 | 1             | 2              | None                     |

| 79                 | TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16>          | 1             | 2              | None                     |

| 30                 | TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>                | 1             | 2              | None                     |

| 81                 | ULNK                 | ULNK   |                 | Unlink Frame Pointer                  | 1             | 1              | None                     |

| 82                 | XOR                  | XOR    | f               | f = f .XOR. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | XOR    | f,WREG          | WREG = f .XOR. WREG                   | 1             | 1              | N,Z                      |

|                    |                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd                   | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws                      | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5                    | 1             | 1              | N,Z                      |

| 83                 | ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-extend Ws                  | 1             | 1              | C,Z,N                    |

| TABLE 30-7: | DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) |

|-------------|----------------------------------------------|

|-------------|----------------------------------------------|

| TABLE 30-7:                     |                        | <b>ACIERIS</b> | 11C2: 50M   | ER-DOWN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CURREN                   | I (IPD)                                                            |