Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | dsPIC                                                                           |

| Core Size                 | 16-Bit                                                                          |

|                           |                                                                                 |

| Speed                     | 40 MIPs                                                                         |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals               | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O             | 35                                                                              |

| Program Memory Size       | 32KB (32K x 8)                                                                  |

| rogram Memory Type        | FLASH                                                                           |

| EEPROM Size               | -                                                                               |

| AAM Size                  | 4K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| ata Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type           | Internal                                                                        |

| perating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type             | Surface Mount                                                                   |

| Package / Case            | 44-TQFP                                                                         |

| Supplier Device Package   | 44-TQFP (10x10)                                                                 |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp304-e-pt |

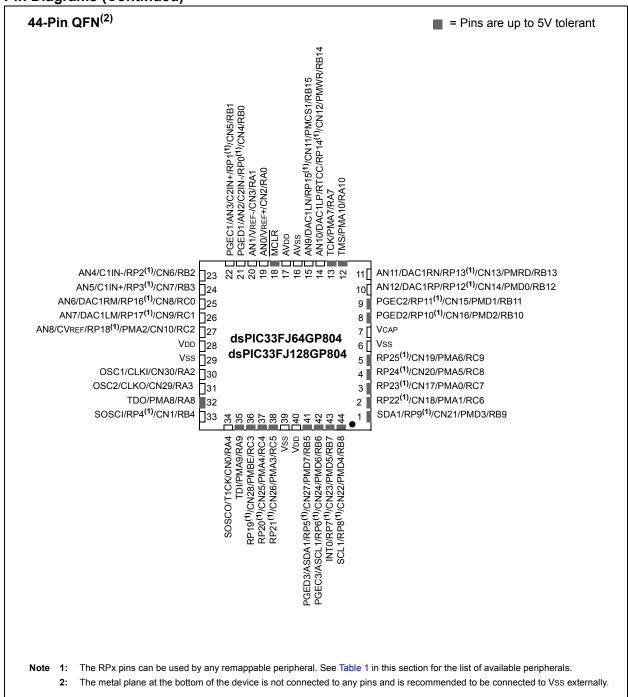

# Pin Diagrams (Continued)

## **Table of Contents**

| dsPI | C33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 Product Families | 2   |

|------|------------------------------------------------------------------------------------|-----|

| 1.0  | Device Overview                                                                    | 13  |

| 2.0  | Guidelines for Getting Started with 16-bit Digital Signal Controllers              | 19  |

| 3.0  | CPU                                                                                | 23  |

| 4.0  | Memory Organization                                                                | 35  |

| 5.0  | Flash Program Memory                                                               | 71  |

| 6.0  | Resets                                                                             | 77  |

| 7.0  | Interrupt Controller                                                               | 87  |

| 8.0  | Direct Memory Access (DMA)                                                         | 129 |

| 9.0  | Oscillator Configuration                                                           | 141 |

| 10.0 | Power-Saving Features                                                              | 153 |

| 11.0 | I/O Ports                                                                          | 159 |

| 12.0 | Timer1                                                                             | 189 |

| 13.0 | Timer2/3 and Timer4/5 Feature                                                      | 193 |

| 14.0 | Input Capture                                                                      | 199 |

|      | Output Compare                                                                     |     |

| 16.0 | Serial Peripheral Interface (SPI)                                                  | 207 |

|      | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                      |     |

|      | Universal Asynchronous Receiver Transmitter (UART)                                 |     |

|      | Enhanced CAN (ECAN™) Module                                                        |     |

|      | Data Converter Interface (DCI) Module                                              |     |

|      | 10-bit/12-bit Analog-to-Digital Converter (ADC)                                    |     |

|      | Audio Digital-to-Analog Converter (DAC)                                            |     |

|      | Comparator Module                                                                  |     |

|      | Real-Time Clock and Calendar (RTCC)                                                |     |

| 25.0 | Programmable Cyclic Redundancy Check (CRC) Generator                               | 301 |

|      | Parallel Master Port (PMP)                                                         |     |

|      | Special Features                                                                   |     |

| 28.0 | Instruction Set Summary                                                            |     |

| 29.0 | · · · · · · · · · · · · · · · · · ·                                                |     |

|      | Electrical Characteristics                                                         |     |

|      | High Temperature Electrical Characteristics                                        |     |

|      | DC and AC Device Characteristics Graphs                                            |     |

|      | Packaging Information                                                              |     |

|      | endix A: Revision History                                                          |     |

|      | x                                                                                  |     |

|      | Microchip Web Site                                                                 |     |

|      | omer Change Notification Service                                                   |     |

|      | omer Support                                                                       |     |

| Read | der Response                                                                       | 432 |

| Prod | uct Identification System                                                          | 433 |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IADLE I-I.   |             | O DEG                                                                                                                                               | J1 (11 11 | ONS (CONTINUED)                                                            |

|--------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------|

| Pin Name     | Pin<br>Type | Buffer<br>Type                                                                                                                                      | PPS       | Description                                                                |

| SCL1         | I/O         | ST                                                                                                                                                  | No        | Synchronous serial clock input/output for I2C1.                            |

| SDA1         | I/O         | ST                                                                                                                                                  | No        | Synchronous serial data input/output for I2C1.                             |

| ASCL1        | I/O         | ST                                                                                                                                                  | No        | Alternate synchronous serial clock input/output for I2C1.                  |

| ASDA1        | I/O         | ST                                                                                                                                                  | No        | Alternate synchronous serial data input/output for I2C1.                   |

| TMS          | ı           | ST                                                                                                                                                  | No        | JTAG Test mode select pin.                                                 |

| TCK          | l i         | ST                                                                                                                                                  | No        | JTAG test clock input pin.                                                 |

| TDI          | l i         | ST                                                                                                                                                  | No        | JTAG test data input pin.                                                  |

| TDO          | Ö           | _                                                                                                                                                   | No        | JTAG test data output pin.                                                 |

| C1RX         | 1           | ST                                                                                                                                                  | Yes       | ECAN1 bus receive pin.                                                     |

| C1TX         | 0           | _                                                                                                                                                   | Yes       | ECAN1 bus transmit pin.                                                    |

| RTCC         | 0           | _                                                                                                                                                   | No        | Real-Time Clock Alarm Output.                                              |

| CVREF        | 0           | ANA                                                                                                                                                 | No        | Comparator Voltage Reference Output.                                       |

| C1IN-        | ı           | ANA                                                                                                                                                 | No        | Comparator 1 Negative Input.                                               |

| C1IN+        |             | ANA                                                                                                                                                 | No        | Comparator 1 Positive Input.                                               |

| C1OUT        | Ö           | — —                                                                                                                                                 | Yes       | Comparator 1 Output.                                                       |

| C2IN-        | ı           | ANA                                                                                                                                                 | No        | Comparator 2 Negative Input.                                               |

| C2IN+        | li          | ANA                                                                                                                                                 | No        | Comparator 2 Positive Input.                                               |

| C2OUT        | Ö           | _                                                                                                                                                   | Yes       | Comparator 2 Output.                                                       |

| PMA0         | I/O         | TTL/ST                                                                                                                                              | No        | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and        |

| 1 107 (0     | "           | 112/01                                                                                                                                              | 110       | Output (Master modes).                                                     |

| PMA1         | I/O         | TTL/ST                                                                                                                                              | No        | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and        |

|              |             |                                                                                                                                                     |           | Output (Master modes).                                                     |

| PMA2 -PMPA10 | 0           |                                                                                                                                                     | No        |                                                                            |

| PMBE         | Ö           | <ul> <li>No</li> <li>Parallel Master Port Address (Demultiplexed Master Mo</li> <li>No</li> <li>Parallel Master Port Byte Enable Strobe.</li> </ul> |           |                                                                            |

| PMCS1        | Ö           |                                                                                                                                                     | No        | Parallel Master Port Chip Select 1 Strobe.                                 |

| PMD0-PMPD7   | I/O         | TTL/ST                                                                                                                                              | No        | Parallel Master Port Data (Demultiplexed Master mode) or Address/          |

|              |             |                                                                                                                                                     |           | Data (Multiplexed Master modes).                                           |

| PMRD         | 0           | _                                                                                                                                                   | No        | Parallel Master Port Read Strobe.                                          |

| PMWR         | 0           | _                                                                                                                                                   | No        | Parallel Master Port Write Strobe.                                         |

| DAC1RN       | 0           | _                                                                                                                                                   | No        | DAC1 Right Channel Negative Output.                                        |

| DAC1RP       | 0           | _                                                                                                                                                   | No        | DAC1 Right Channel Positive Output.                                        |

| DAC1RM       | 0           | _                                                                                                                                                   | No        | DAC1 Right Channel Middle Point Value (typically 1.65V).                   |

| DAC1LN       | 0           | _                                                                                                                                                   | No        | DAC1 Left Channel Negative Output.                                         |

| DAC1LP       | 0           |                                                                                                                                                     | No        | DAC1 Left Channel Positive Output.                                         |

| DAC1LM       | 0           | _                                                                                                                                                   | No        | DAC1 Left Channel Middle Point Value (typically 1.65V).                    |

| COFS         | I/O         | ST                                                                                                                                                  | Yes       | Data Converter Interface frame synchronization pin.                        |

| CSCK         | I/O         | ST                                                                                                                                                  | Yes       | Data Converter Interface serial clock input/output pin.                    |

| CSDI         | I           | ST                                                                                                                                                  | Yes       | Data Converter Interface serial data input pin                             |

| CSDO         | 0           | _                                                                                                                                                   | Yes       | Data Converter Interface serial data output pin.                           |

| PGED1        | I/O         | ST                                                                                                                                                  | No        | Data I/O pin for programming/debugging communication channel 1.            |

| PGEC1        | Ī           | ST                                                                                                                                                  | No        | Clock input pin for programming/debugging communication channel 1.         |

| PGED2        | I/O         | ST                                                                                                                                                  | No        | Data I/O pin for programming/debugging communication channel 2.            |

| PGEC2        | I           | ST                                                                                                                                                  | No        | Clock input pin for programming/debugging communication channel 2.         |

| PGED3        | I/O         | ST                                                                                                                                                  | No        | Data I/O pin for programming/debugging communication channel 3.            |

| PGEC3        | I           | ST                                                                                                                                                  | No        | Clock input pin for programming/debugging communication channel 3.         |

| MCLR         | I/P         | ST                                                                                                                                                  | No        | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| AVDD         | Р           | Р                                                                                                                                                   | No        | Positive supply for analog modules. This pin must be connected at all      |

|              |             |                                                                                                                                                     |           | times.                                                                     |

|              | 1           | i                                                                                                                                                   |           | 1                                                                          |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

Analog = Analog input

P = Power

O = Output

I = Input

PPS = Peripheral Pin Select

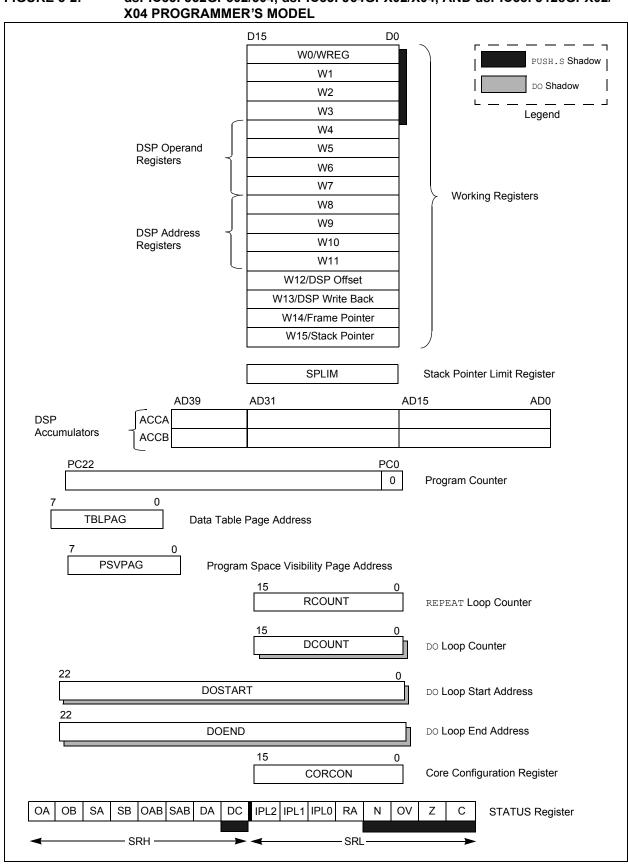

#### 3.0 CPU

Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 3.1 Overview

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any time.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and

a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 is shown in Figure 3-2.

### 3.2 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data-space mapping feature lets any instruction access program space as if it were data space.

#### 3.3 DSP Engine Overview

The DSP engine features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal realtime performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

FIGURE 3-2: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/

| TABLE 4-5: | TIMER | REGISTER | R MAP |

|------------|-------|----------|-------|

|------------|-------|----------|-------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14                                                          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7          | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|-----------------------------------------------------------------|--------|--------|--------|--------|--------------|--------------|----------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100        |        |                                                                 |        |        |        |        |              | Timer1       | Register       |              |       |        |       |       |       |       | 0000          |

| PR1         | 0102        |        |                                                                 |        |        |        |        |              | Period F     | Register 1     |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE        | TCKP  | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |        | Timer2 Register 0000                                            |        |        |        |        |              |              |                |              |       |        |       |       |       |       |               |

| TMR3HLD     | 0108        |        | Timer3 Holding Register (for 32-bit timer operations only) xxxx |        |        |        |        |              |              |                |              |       |        |       |       |       |       |               |

| TMR3        | 010A        |        | Timer3 Register 0000                                            |        |        |        |        |              |              |                |              |       |        |       |       |       |       |               |

| PR2         | 010C        |        | Period Register 2 FFFF                                          |        |        |        |        |              |              |                |              |       | FFFF   |       |       |       |       |               |

| PR3         | 010E        |        |                                                                 |        |        |        |        |              | Period F     | Register 3     |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T3CON       | 0112        | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114        |        |                                                                 |        |        |        |        |              | Timer4       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        |        |                                                                 |        |        |        | Tim    | ner5 Holding | Register (fo | r 32-bit timer | operations o | only) |        |       |       |       |       | xxxx          |

| TMR5        | 0118        |        |                                                                 |        |        |        |        |              | Timer5       | Register       |              |       |        |       |       |       |       | 0000          |

| PR4         | 011A        |        |                                                                 |        |        |        |        |              | Period F     | Register 4     |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C        |        | Period Register 5 FFFF                                          |        |        |        |        |              |              |                |              |       |        |       |       |       |       |               |

| T4CON       | 011E        | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON    | _                                                               | TSIDL  | _      | -      | _      | -            | _            | _              | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### **TABLE 4-6: INPUT CAPTURE REGISTER MAP**

| .,          | . •.        | • .    |                                                 |        | • · • · = · |        |        |       |            |              |       |       |       |       |       |          |       |               |

|-------------|-------------|--------|-------------------------------------------------|--------|-------------|--------|--------|-------|------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14                                          | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF      | 0140        |        | Input 1 Capture Register xxxx                   |        |             |        |        |       |            |              |       |       |       |       |       |          |       |               |

| IC1CON      | 0142        | _      | _ ICSIDL ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> 000 |        |             |        |        |       |            |              |       |       | 0000  |       |       |          |       |               |

| IC2BUF      | 0144        |        | Input 2 Capture Register                        |        |             |        |        |       |            |              |       |       |       |       | xxxx  |          |       |               |

| IC2CON      | 0146        | _      | -                                               | ICSIDL | _           | _      | -      | -     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF      | 0158        |        |                                                 |        |             |        |        |       | Input 7 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC7CON      | 015A        | _      | -                                               | ICSIDL | _           | _      | -      | -     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF      | 015C        |        | Input 8Capture Register xxxx                    |        |             |        |        |       |            |              |       |       |       | xxxx  |       |          |       |               |

| IC8CON      | 015E        | _      | _                                               | ICSIDL | _           | _      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|  | , |   |   |   |

|--|---|---|---|---|

|  | ۶ |   |   |   |

|  |   | , | ٠ |   |

|  | ì | _ | ` | ١ |

|  | ì | 7 | 7 |   |

|  | į | Ċ | š | ) |

|  | 1 | ` | 3 |   |

|  | i | 7 | ۰ | 1 |

|  | ٠ | ī | • |   |

|  |   |   |   |   |

## TABLE 4-21: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File Name              | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|------------------------|------|--------|--------|--------|--------|--------|------------|-------|-------|-------|-------|-------|------------|-------|-----------|-------|-------|---------------|

| RPINR0                 | 0680 | _      | _      | _      |        |        | INT1R<4:0> |       |       | _     | _     | _     | _          | _     | _         | _     | _     | 1F00          |

| RPINR1                 | 0682 | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |            |       | INT2R<4:0 | >     |       | 001F          |

| RPINR3                 | 0686 | _      | _      | -      |        |        | T3CKR<4:0> |       |       | _     | _     | _     |            |       | T2CKR<4:0 | >     |       | 1F1F          |

| RPINR4                 | 0688 | _      | _      | _      |        |        | T5CKR<4:0> | •     |       | _     | _     | _     |            |       | T4CKR<4:0 | >     |       | 1F1F          |

| RPINR7                 | 068E | _      | _      | -      |        |        | IC2R<4:0>  |       |       | _     | _     | _     |            |       | IC1R<4:0> |       |       | 1F1F          |

| RPINR10                | 0694 | _      | _      | _      |        |        | IC8R<4:0>  |       |       | _     | _     | _     | IC7R<4:0>  |       |           | 1F1F  |       |               |

| RPINR11                | 0696 | _      | _      | -      | ı      | _      | _          | _     | _     | _     | _     | _     | OCFAR<4:0> |       |           |       | 001F  |               |

| RPINR18                | 06A4 | _      | _      | 1      |        |        | U1CTSR<4:0 | >     |       | _     | _     | _     |            |       | U1RXR<4:0 | >     |       | 1F1F          |

| RPINR19                | 06A6 | _      | _      |        |        |        | U2CTSR<4:0 | >     |       | _     |       | _     |            |       | U2RXR<4:0 | >     |       | 1F1F          |

| RPINR20                | 06A8 | _      | _      | 1      |        |        | SCK1R<4:0> | •     |       | _     | _     | _     |            |       | SDI1R<4:0 | >     |       | 1F1F          |

| RPINR21                | 06AA | _      | _      | _      | 1      | _      | _          | _     | _     | _     | _     | _     |            |       | SS1R<4:0> | •     |       | 001F          |

| RPINR22                | 06AC | _      | _      | 1      |        |        | SCK2R<4:0> | •     |       | _     | _     | _     |            |       | SDI2R<4:0 | >     |       | 1F1F          |

| RPINR23                | 06AE | _      | _      | _      | 1      | _      | _          | _     | _     | _     | _     | _     | SS2R<4:0>  |       |           | 001F  |       |               |

| RPINR24                | 06B0 | _      | _      |        |        | _      | CSCKR<4:0> | >     |       | _     | _     | _     | CSDIR<4:0> |       |           | 1F1F  |       |               |

| RPINR25                | 06B2 | _      | _      | _      |        | _      | _          |       | _     | _     |       | _     | COFSR<4:0> |       |           | 001F  |       |               |

| RPINR26 <sup>(1)</sup> | 06B4 | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |            |       | C1RXR<4:0 | >     |       | 001F          |

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is present only for dsPIC33FJ128GP802/804 and dsPIC33FJ64GP802/804

# 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture uses a 24 bit wide program space and a 16 bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

#### 4.8.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-39 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

TABLE 4-39: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type                        | Access        | Program Space Address        |           |                                   |                    |     |  |  |  |

|------------------------------------|---------------|------------------------------|-----------|-----------------------------------|--------------------|-----|--|--|--|

| Access Type                        | Space         | <23>                         | <22:16>   | <15>                              | <14:1>             | <0> |  |  |  |

| Instruction Access User 0 PC<22:1> |               |                              |           |                                   |                    |     |  |  |  |

| (Code Execution)                   |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                                   |                    |     |  |  |  |

| TBLRD/TBLWT                        | User          | TB                           | LPAG<7:0> |                                   | Data EA<15:0>      |     |  |  |  |

| (Byte/Word Read/Write)             |               | 0                            | xxx xxxx  | xxxx xx                           | XXX XXXX XXXX      |     |  |  |  |

|                                    | Configuration | TB                           | LPAG<7:0> | Data EA<15:0>                     |                    |     |  |  |  |

|                                    |               | 1                            | xxx xxxx  | xxxx xxxx xxxx xxxx               |                    |     |  |  |  |

| Program Space Visibility           | User          | 0                            | PSVPAG<7  | 7:0> Data EA<14:0> <sup>(1)</sup> |                    |     |  |  |  |

| (Block Remap/Read)                 |               | 0                            | XXXX XXXX | ζ                                 | XXX XXXX XXXX XXXX |     |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

#### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-0   | W-0         | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 |  |  |  |  |  |  |

|-------|-------------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|--|

|       | NVMKEY<7:0> |     |     |     |     |     |     |  |  |  |  |  |  |

| bit 7 | bit 7 bit 0 |     |     |     |     |     |     |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

#### REGISTER 7-23: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

| U-0    | R/W-1 | R/W-0                    | R/W-0 | U-0 | R/W-1 | R/W-0                     | R/W-0 |

|--------|-------|--------------------------|-------|-----|-------|---------------------------|-------|

| _      |       | C1IP<2:0> <sup>(1)</sup> |       | _   | C     | 1RXIP<2:0> <sup>(1)</sup> | )     |

| bit 15 |       |                          |       |     |       |                           | bit 8 |

| U-0   | R/W-1 | R/W-0       | R/W-0 | U-0 | R/W-1 | R/W-0        | R/W-0 |

|-------|-------|-------------|-------|-----|-------|--------------|-------|

| _     |       | SPI2IP<2:0> |       | _   |       | SPI2EIP<2:0> |       |

| bit 7 |       |             |       |     |       |              | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 Unimplemented: Read as '0' C1IP<2:0>: ECAN1 Event Interrupt Priority bits(1) bit 14-12 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits(1) 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 7 Unimplemented: Read as '0' SPI2IP<2:0>: SPI2 Event Interrupt Priority bits bit 6-4 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 SPI2EIP<2:0>: SPI2 Error Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled

Note 1: Interrupts are disabled on devices without ECAN™ modules.

#### REGISTER 7-28: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | R/W-1 | R/W-0      | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-------|------------|-------|-----|-------|------------|-------|

| _      |       | CRCIP<2:0> |       | _   |       | U2EIP<2:0> |       |

| bit 15 |       |            |       |     |       |            | bit 8 |

| U-0   | R/W-1 | R/W-0      | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|------------|-------|-----|-----|-----|-------|

| _     |       | U1EIP<2:0> |       | _   |     | _   | _     |

| bit 7 |       |            |       |     |     |     | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 CRCIP<2:0>: CRC Generator Error Interrupt Flag Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **U2EIP<2:0>:** UART2 Error Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

:

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **U1EIP<2:0>:** UART1 Error Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3-0 **Unimplemented:** Read as '0'

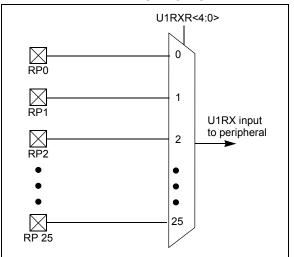

#### 11.6 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 11.6.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 26 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

# 11.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 11.6.2.1 Input Mapping

Note:

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it is mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-16). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 11-2 illustrates remappable pin selection for U1RX input.

For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

FIGURE 11-2: REMAPPABLE MUX INPUT FOR U1RX

#### REGISTER 11-11: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1     | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| _     | _   | _   |       |       | SS1R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

#### REGISTER 13-2: TxCON: TIMER CONTROL REGISTER (x = 3 OR 5)

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(2)</sup> | _   | TSIDL <sup>(1)</sup> | _   | _   | _   | _   | _     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0 | R/W-0                | U-0 | U-0 | R/W-0              | U-0   |

|-------|----------------------|-------|----------------------|-----|-----|--------------------|-------|

| _     | TGATE <sup>(2)</sup> | TCKPS | <1:0> <sup>(2)</sup> | _   | _   | TCS <sup>(2)</sup> | _     |

| bit 7 |                      |       |                      |     |     |                    | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 **TON:** Timery On bit<sup>(2)</sup>

1 = Starts 16-bit Timerx

0 = Stops 16-bit Timerx

bit 14 Unimplemented: Read as '0'

bit 13 **TSIDL:** Stop in Idle Mode bit<sup>(1)</sup>

1 = Discontinue timer operation when device enters Idle mode

0 = Continue timer operation in Idle mode

bit 12-7 **Unimplemented:** Read as '0'

bit 6 TGATE: Timerx Gated Time Accumulation Enable bit<sup>(2)</sup>

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation enabled 0 = Gated time accumulation disabled

bit 5-4 TCKPS<1:0>: Timerx Input Clock Prescale Select bits<sup>(2)</sup>

11 = 1:256 prescale value 10 = 1:64 prescale value 01 = 1:8 prescale value 00 = 1:1 prescale value

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TCS: Timerx Clock Source Select bit<sup>(2)</sup>

1 = External clock from TxCK pin0 = Internal clock (Fosc/2)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), these bits have no effect.

### 19.6 ECAN Message Buffers

ECAN Message Buffers are part of DMA RAM Memory. They are not ECAN special function registers. The user application must directly write into the DMA RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 19-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|-------|-------|-------|

| _      | _   | _   | SID10 | SID9  | SID8  | SID7  | SID6  |

| bit 15 |     |     |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID5  | SID4  | SID3  | SID2  | SID1  | SID0  | SRR   | IDE   |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-2 SID<10:0>: Standard Identifier bits

bit 1 SRR: Substitute Remote Request bit

1 = Message will request remote transmission

0 = Normal message

bit 0 **IDE:** Extended Identifier bit

1 = Message will transmit extended identifier0 = Message will transmit standard identifier

#### BUFFER 19-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0    | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      | _   | _   | _   | EID17 | EID16 | EID15 | EID14 |

| bit 15 |     |     |     |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID13 | EID12 | EID11 | EID10 | EID9  | EID8  | EID7  | EID6  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0' bit 11-0 **EID<17:6>:** Extended Identifier bits

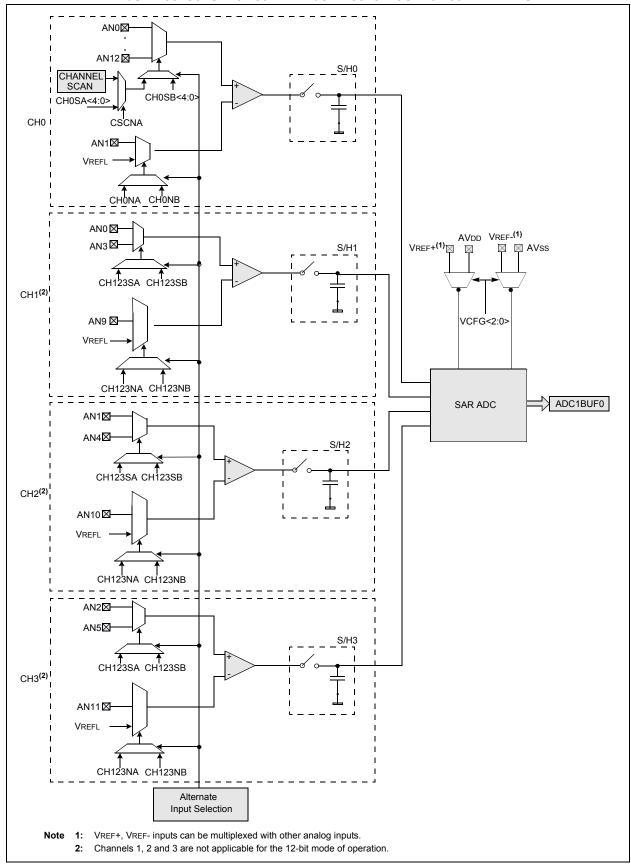

**FIGURE 21-2:** ADC1 MODULE BLOCK DIAGRAM FOR dsPIC33FJ32GP302, dsPIC33FJ64GP202/802 AND dsPIC33FJ128GP202/802 DEVICES

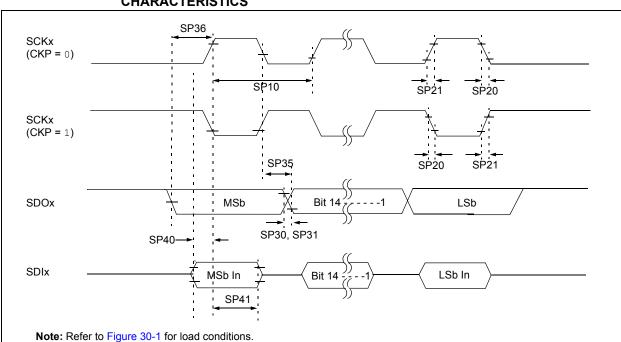

FIGURE 30-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

TABLE 30-30: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING REQUIREMENTS

|                    |                       | <u></u>                                       |                                                                                                                                                             |                    |     |       |                                      |  |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| AC CHARACTERISTICS |                       |                                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                      |  |

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                                                                                                                         | Typ <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP10               | TscP                  | Maximum SCK Frequency                         | _                                                                                                                                                           | _                  | 9   | MHz   | See Note 3                           |  |

| SP20               | TscF                  | SCKx Output Fall Time                         | _                                                                                                                                                           | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP21               | TscR                  | SCKx Output Rise Time                         | _                                                                                                                                                           | _                  | _   | ns    | See parameter DO31 and Note 4        |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | _                                                                                                                                                           | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | _                                                                                                                                                           | _                  | _   | ns    | See parameter DO31 and Note 4        |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | _                                                                                                                                                           | 6                  | 20  | ns    | _                                    |  |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to First SCKx Edge     | 30                                                                                                                                                          | _                  | _   | ns    | _                                    |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                                                                                                                          | _                  | _   | ns    | _                                    |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                                                                                                                                          | _                  |     | ns    | _                                    |  |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 3: The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

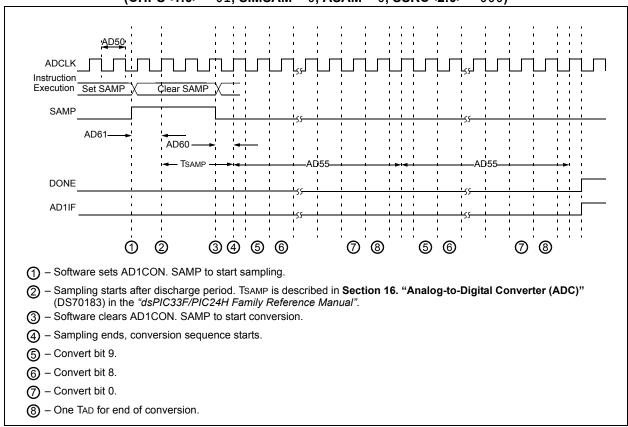

FIGURE 30-25: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000)

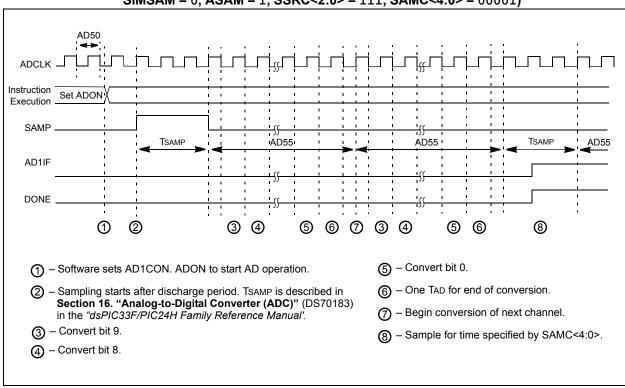

FIGURE 30-26: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

TABLE 31-7: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |        |                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+150°C for High Temperature |     |     |       |                                                                  |

|--------------------|--------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                 | Тур | Max | Units | Conditions                                                       |

|                    |        | Program Flash Memory          |                                                                                                                                     |     |     |       |                                                                  |

| HD130              | EP     | Cell Endurance                | 10,000                                                                                                                              | _   | _   | E/W   | -40° C to +150°C <sup>(2)</sup>                                  |

| HD134              | TRETD  | Characteristic Retention      | 20                                                                                                                                  | _   | _   | Year  | 1000 E/W cycles or less and no other specifications are violated |

Note 1: These parameters are assured by design, but are not characterized or tested in manufacturing.

<sup>2:</sup> Programming of the Flash memory is allowed up to 150°C.

TABLE 31-16: ADC MODULE SPECIFICATIONS (10-BIT MODE)

| AC<br>CHARACTERISTICS                                                  |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+150°C for High Temperature |              |     |      |       |                                                  |  |  |

|------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|------|-------|--------------------------------------------------|--|--|

| Param<br>No.                                                           | Symbol | Characteristic                                                                                                                      | Min          | Тур | Max  | Units | Conditions                                       |  |  |

|                                                                        |        |                                                                                                                                     |              |     |      |       |                                                  |  |  |

| ADC Accuracy (10-bit Mode) – Measurements with External VREF+/VREF-(1) |        |                                                                                                                                     |              |     |      |       |                                                  |  |  |

| HAD20b                                                                 | Nr     | Resolution <sup>(3)</sup>                                                                                                           | 10 data bits |     | bits | _     |                                                  |  |  |

| HAD21b                                                                 | INL    | Integral Nonlinearity                                                                                                               | -3           | _   | 3    | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| HAD22b                                                                 | DNL    | Differential Nonlinearity                                                                                                           | > -1         | _   | < 1  | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| HAD23b                                                                 | GERR   | Gain Error                                                                                                                          | -5           | -   | 6    | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| HAD24b                                                                 | EOFF   | Offset Error                                                                                                                        | -1           | _   | 5    | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| ADC Accuracy (10-bit Mode) – Measurements with Internal VREF+/VREF-(1) |        |                                                                                                                                     |              |     |      |       |                                                  |  |  |

| HAD20b                                                                 | Nr     | Resolution <sup>(3)</sup>                                                                                                           | 10 data bits |     |      | bits  | _                                                |  |  |

| HAD21b                                                                 | INL    | Integral Nonlinearity                                                                                                               | -2           | _   | 2    | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

| HAD22b                                                                 | DNL    | Differential Nonlinearity                                                                                                           | > -1         | -   | < 1  | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

| HAD23b                                                                 | GERR   | Gain Error                                                                                                                          | -5           | _   | 15   | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

| HAD24b                                                                 | Eoff   | Offset Error                                                                                                                        | -1.5         | ı   | 7    | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

| Dynamic Performance (10-bit Mode) <sup>(2)</sup>                       |        |                                                                                                                                     |              |     |      |       |                                                  |  |  |

| HAD33b                                                                 | FNYQ   | Input Signal Bandwidth                                                                                                              | _            | _   | 400  | kHz   | _                                                |  |  |

Note 1: These parameters are characterized, but are tested at 20 ksps only.

<sup>2:</sup> These parameters are characterized by similarity, but are not tested in manufacturing.

<sup>3:</sup> Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.