Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I2S, POR, PWM, WDT                            |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp304-i-ml |

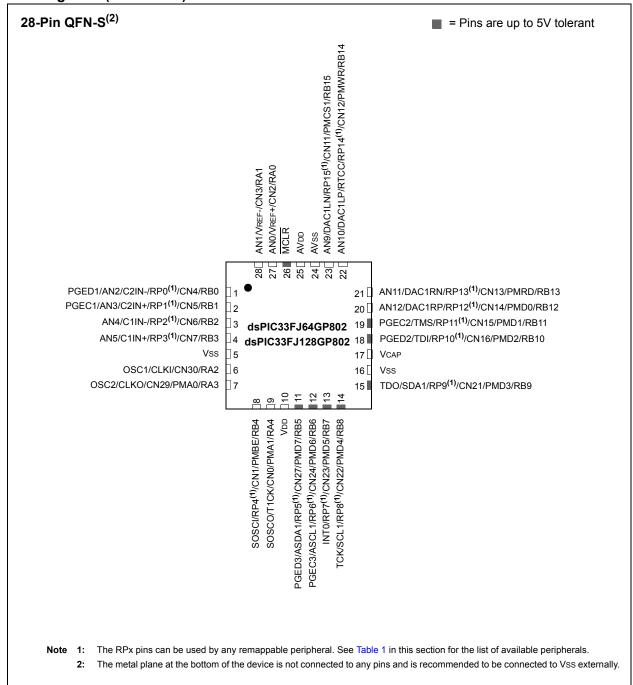

# Pin Diagrams (Continued)

# **Table of Contents**

| dsPI | C33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 Product Families | 2   |

|------|------------------------------------------------------------------------------------|-----|

| 1.0  | Device Overview                                                                    | 13  |

| 2.0  | Guidelines for Getting Started with 16-bit Digital Signal Controllers              | 19  |

| 3.0  | CPU                                                                                | 23  |

| 4.0  | Memory Organization                                                                | 35  |

| 5.0  | Flash Program Memory                                                               | 71  |

| 6.0  | Resets                                                                             | 77  |

| 7.0  | Interrupt Controller                                                               | 87  |

| 8.0  | Direct Memory Access (DMA)                                                         | 129 |

| 9.0  | Oscillator Configuration                                                           | 141 |

| 10.0 | Power-Saving Features                                                              | 153 |

| 11.0 | I/O Ports                                                                          | 159 |

| 12.0 | Timer1                                                                             | 189 |

| 13.0 | Timer2/3 and Timer4/5 Feature                                                      | 193 |

| 14.0 | Input Capture                                                                      | 199 |

|      | Output Compare                                                                     |     |

| 16.0 | Serial Peripheral Interface (SPI)                                                  | 207 |

|      | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                      |     |

|      | Universal Asynchronous Receiver Transmitter (UART)                                 |     |

|      | Enhanced CAN (ECAN™) Module                                                        |     |

|      | Data Converter Interface (DCI) Module                                              |     |

|      | 10-bit/12-bit Analog-to-Digital Converter (ADC)                                    |     |

|      | Audio Digital-to-Analog Converter (DAC)                                            |     |

|      | Comparator Module                                                                  |     |

|      | Real-Time Clock and Calendar (RTCC)                                                |     |

| 25.0 | Programmable Cyclic Redundancy Check (CRC) Generator                               | 301 |

|      | Parallel Master Port (PMP)                                                         |     |

|      | Special Features                                                                   |     |

| 28.0 | Instruction Set Summary                                                            |     |

| 29.0 | · · · · · · · · · · · · · · · · · ·                                                |     |

|      | Electrical Characteristics                                                         |     |

|      | High Temperature Electrical Characteristics                                        |     |

|      | DC and AC Device Characteristics Graphs                                            |     |

|      | Packaging Information                                                              |     |

|      | endix A: Revision History                                                          |     |

|      | x                                                                                  |     |

|      | Microchip Web Site                                                                 |     |

|      | omer Change Notification Service                                                   |     |

|      | omer Support                                                                       |     |

| Read | der Response                                                                       | 432 |

| Prod | uct Identification System                                                          | 433 |

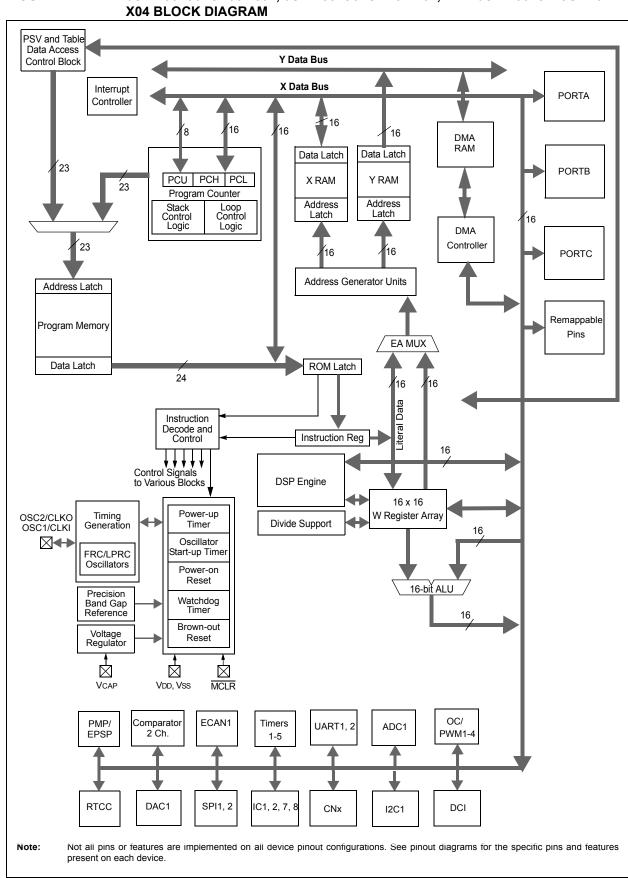

FIGURE 1-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/

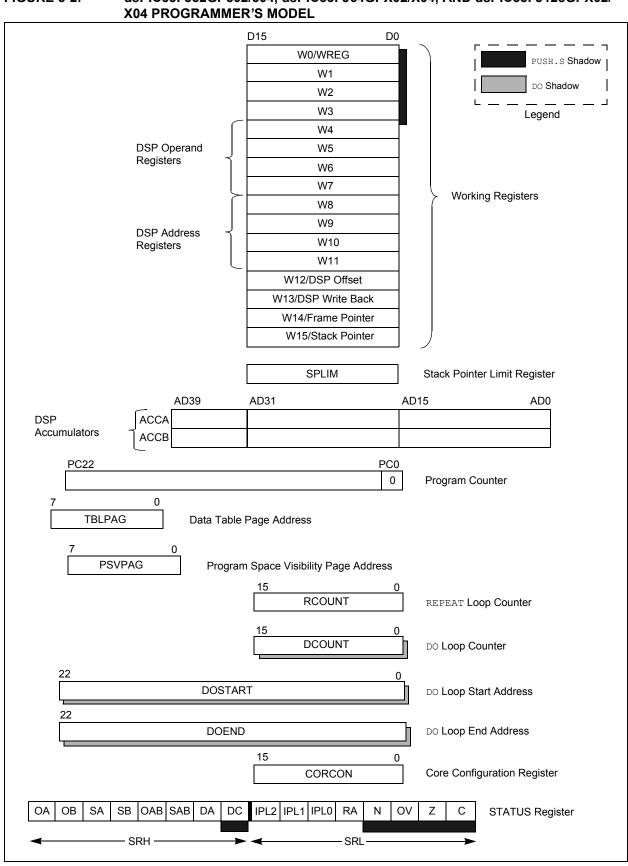

FIGURE 3-2: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

| U-0    | U-0 | U-0 | R/W-0 | R/W-0              | R-0 | R-0     | R-0   |

|--------|-----|-----|-------|--------------------|-----|---------|-------|

| _      | _   | _   | US    | EDT <sup>(1)</sup> |     | DL<2:0> |       |

| bit 15 |     |     |       |                    |     |         | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

| Legend:             | C = Clear only bit  |                                    |                  |  |  |

|---------------------|---------------------|------------------------------------|------------------|--|--|

| R = Readable bit    | W = Writable bit    | -n = Value at POR                  | '1' = Bit is set |  |  |

| 0' = Bit is cleared | 'x = Bit is unknown | U = Unimplemented bit, read as '0' |                  |  |  |

bit 15-13 **Unimplemented:** Read as '0'

bit 12 US: DSP Multiply Unsigned/Signed Control bit

1 = DSP engine multiplies are unsigned0 = DSP engine multiplies are signed

bit 11 **EDT:** Early DO Loop Termination Control bit<sup>(1)</sup>

1 = Terminate executing DO loop at end of current loop iteration

0 = No effect

bit 10-8 **DL<2:0>:** DO Loop Nesting Level Status bits

111 **= 7** DO **loops** active

•

001 **= 1** DO **loop** active

000 = 0 DO loops active

bit 7 SATA: ACCA Saturation Enable bit

1 = Accumulator A saturation enabled0 = Accumulator A saturation disabled

bit 6 SATB: ACCB Saturation Enable bit

1 = Accumulator B saturation enabled 0 = Accumulator B saturation disabled

bit 5 SATDW: Data Space Write from DSP Engine Saturation Enable bit

1 = Data space write saturation enabled0 = Data space write saturation disabled

bit 4 ACCSAT: Accumulator Saturation Mode Select bit

1 = 9.31 saturation (super saturation)0 = 1.31 saturation (normal saturation)

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU interrupt priority level is greater than 7

0 = CPU interrupt priority level is 7 or less

bit 2 PSV: Program Space Visibility in Data Space Enable bit

1 = Program space visible in data space0 = Program space not visible in data space

bit 1 RND: Rounding Mode Select bit

1 = Biased (conventional) rounding enabled

0 = Unbiased (convergent) rounding enabled

1 = Integer mode enabled for DSP multiply ops

0 = Fractional mode enabled for DSP multiply ops

Note 1: This bit is always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

#### 3.8.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 3.8.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 and 31 for right shifts, and between bit positions 0 and 16 for left shifts.

## 6.3 System Reset

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 family of devices have two types of Reset:

- · Cold Reset

- · Warm Reset

A cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a cold Reset, the FNOSC configuration bits in the FOSC device configuration register selects the device clock source.

A warm Reset is the result of all other reset sources, including the RESET instruction. On warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection bits (COSC<2:0>) in the Oscillator Control register (OSCCON<14:12>).

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is shown in Figure 6-2.

TABLE 6-1: OSCILLATOR DELAY

| Oscillator Mode           | Oscillator<br>Startup Delay | Oscillator Startup<br>Timer | PLL Lock Time | Total Delay          |

|---------------------------|-----------------------------|-----------------------------|---------------|----------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd                       | _                           | _             | Toscd                |

| FRCPLL                    | Tosco                       | _                           | TLOCK         | Toscd + Tlock        |

| XT                        | Tosco                       | Tost                        | Tost —        |                      |

| HS                        | Tosco                       | Tost                        | _             | Toscd + Tost         |

| EC                        | _                           | _                           | _             | _                    |

| XTPLL                     | Tosco                       | Tost                        | TLOCK         | Toscd + Tost + Tlock |

| HSPLL                     | Tosco                       | Tost                        | TLOCK         | Toscd + Tost + Tlock |

| ECPLL                     | _                           | _                           | TLOCK         | TLOCK                |

| SOSC                      | Tosco                       | Tost                        | _             | Toscd + Tost         |

| LPRC                      | Tosco                       | _                           | _             | Tosco                |

- Note 1: Toscd = Oscillator Start-up Delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal Oscillator start-up times vary with crystal characteristics, load capacitance, etc.

- 2: Tost = Oscillator Start-up Timer Delay (1024 oscillator clock period). For example, Tost = 102.4 μs for a 10 MHz crystal and Tost = 32 ms for a 32 kHz crystal.

- **3:** TLOCK = PLL lock time (1.5 ms nominal), if PLL is enabled.

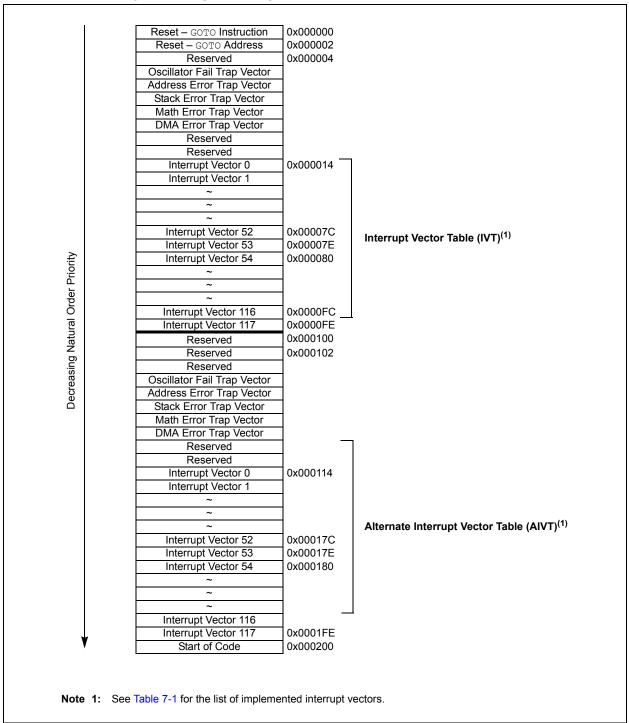

FIGURE 7-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04 INTERRUPT VECTOR TABLE

# REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0    | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0 |

|--------|--------|-------|--------|--------|--------|---------|-------|

| _      | DMA1IE | AD1IE | U1TXIE | U1RXIE | SPI1IE | SPI1EIE | T3IE  |

| bit 15 |        |       |        |        |        |         | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  |

|-------|-------|-------|--------|-------|-------|-------|--------|

| T2IE  | OC2IE | IC2IE | DMA0IE | T1IE  | OC1IE | IC1IE | INT0IE |

| bit 7 |       |       |        |       |       |       | bit 0  |

| Legend:           |                                                       |                      |                    |  |

|-------------------|-------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | t W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                      | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15  | Unimplemented: Read as '0'                                                         |

|---------|------------------------------------------------------------------------------------|

| bit 14  | <b>DMA1IE:</b> DMA Channel 1 Data Transfer Complete Interrupt Enable bit           |

|         | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled                 |

| bit 13  | AD1IE: ADC1 Conversion Complete Interrupt Enable bit                               |

|         | 1 = Interrupt request enabled                                                      |

|         | 0 = Interrupt request not enabled                                                  |

| bit 12  | U1TXIE: UART1 Transmitter Interrupt Enable bit                                     |

|         | 1 = Interrupt request enabled                                                      |

|         | 0 = Interrupt request not enabled                                                  |

| bit 11  | U1RXIE: UART1 Receiver Interrupt Enable bit                                        |

|         | 1 = Interrupt request enabled                                                      |

| 1 11 10 | 0 = Interrupt request not enabled                                                  |

| bit 10  | SPI1IE: SPI1 Event Interrupt Enable bit                                            |

|         | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled                 |

| bit 9   | SPI1EIE: SPI1 Error Interrupt Enable bit                                           |

| Dit 0   | 1 = Interrupt request enabled                                                      |

|         | 0 = Interrupt request not enabled                                                  |

| bit 8   | T3IE: Timer3 Interrupt Enable bit                                                  |

|         | 1 = Interrupt request enabled                                                      |

|         | 0 = Interrupt request not enabled                                                  |

| bit 7   | T2IE: Timer2 Interrupt Enable bit                                                  |

|         | 1 = Interrupt request enabled                                                      |

|         | 0 = Interrupt request not enabled                                                  |

| bit 6   | OC2IE: Output Compare Channel 2 Interrupt Enable bit                               |

|         | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled                 |

| bit 5   |                                                                                    |

| DIL 5   | IC2IE: Input Capture Channel 2 Interrupt Enable bit  1 = Interrupt request enabled |

|         | 0 = Interrupt request enabled                                                      |

| bit 4   | <b>DMA0IE:</b> DMA Channel 0 Data Transfer Complete Interrupt Enable bit           |

|         | 1 = Interrupt request enabled                                                      |

|         | 0 = Interrupt request not enabled                                                  |

| bit 3   | T1IE: Timer1 Interrupt Enable bit                                                  |

|         | 1 = Interrupt request enabled                                                      |

|         | 0 = Interrupt request not enabled                                                  |

## 9.1 CPU Clocking System

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- · Primary (XT, HS or EC) Oscillator

- · Primary Oscillator with PLL

- · Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- · FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> bits (CLKDIV<10:8>).

The primary oscillator can use one of the following as its clock source:

- Crystal (XT): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- High-Speed Crystal (HS): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- External Clock (EC): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip PLL to provide a wide range of output frequencies for device operation. PLL configuration is described in Section 9.1.4 "PLL Configuration".

The FRC frequency depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 27.1 "Configuration Bits" for further details.) The Initial Oscillator Selection Configuration bits. FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Configuration Select bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture.

Instruction execution speed or device operating frequency, Fcy, is given by:

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

#### 9.1.3 AUXILIARY OSCILLATOR

The Auxiliary Oscillator (AOSC) can be used for peripherals that need to operate at a frequency unrelated to the system clock such as a Digital-to-Analog Converter (DAC).

The Auxiliary Oscillator can use one of the following as its clock source:

- Crystal (XT): Crystal and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the SOCI and SOSCO pins.

- High-Speed Crystal (HS): Crystals in the range of 10 to 40 MHz. The crystal is connected to the SOSCI and SOSCO pins.

- External Clock (EC): External clock signal up to 64 MHz. The external clock signal is directly applied to SOSCI pin.

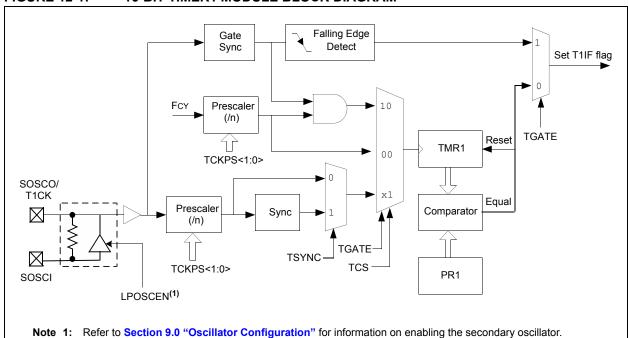

#### 12.0 TIMER1

Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source.

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- · Timer mode

- · Gated Timer mode

- · Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

TABLE 12-1: TIMER MODE SETTINGS

| Mode                 | TCS | TGATE | TSYNC |

|----------------------|-----|-------|-------|

| Timer                | 0   | 0     | X     |

| Gated timer          | 0   | 1     | X     |

| Synchronous counter  | 1   | Х     | 1     |

| Asynchronous counter | 1   | Х     | 0     |

FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

## 18.1 UART Helpful Tips

- In multi-node direct-connect UART networks, UART receive inputs react to complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

**Note:** In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

#### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- · Development Tools

# REGISTER 19-19: CiFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

| R/W-0       | R/W-0 | R/W-0       | R/W-0 | R/W-0       | R/W-0 | R/W-0       | R/W-0 |

|-------------|-------|-------------|-------|-------------|-------|-------------|-------|

| F15MSK<1:0> |       | F14MSK<1:0> |       | F13MSK<1:0> |       | F12MSK<1:0> |       |

| bit 15      |       |             |       |             |       |             | bit 8 |

| R/W-0       | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  |

|-------------|-------|-------|--------|-------|--------|-------|--------|

| F11MSK<1:0> |       | F10MS | K<1:0> | F9MS  | K<1:0> | F8MSI | <<1:0> |

| bit 7       |       |       |        |       |        |       | bit 0  |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                                                     |                    |  |  |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                                               | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

| bit 15-14 | F15MSK<1:0>: Mask Source for Filter 15 bit                            |

|-----------|-----------------------------------------------------------------------|

|           | 11 = No mask                                                          |

|           | 10 = Acceptance Mask 2 registers contain mask                         |

|           | 01 = Acceptance Mask 1 registers contain mask                         |

|           | 00 = Acceptance Mask 0 registers contain mask                         |

| bit 13-12 | F14MSK<1:0>: Mask Source for Filter 14 bit (same values as bit 15-14) |

| bit 11-10 | F13MSK<1:0>: Mask Source for Filter 13 bit (same values as bit 15-14) |

| bit 9-8   | F12MSK<1:0>: Mask Source for Filter 12 bit (same values as bit 15-14) |

| bit 7-6   | F11MSK<1:0>: Mask Source for Filter 11 bit (same values as bit 15-14) |

| bit 5-4   | F10MSK<1:0>: Mask Source for Filter 10 bit (same values as bit 15-14) |

| bit 3-2   | F9MSK<1:0>: Mask Source for Filter 9 bit (same values as bit 15-14)   |

| bit 1-0   | F8MSK<1:0>: Mask Source for Filter 8 bit (same values as bit 15-14)   |

# REGISTER 19-20: CIRXMnSID: ECAN™ ACCEPTANCE FILTER MASK STANDARD IDENTIFIER REGISTER n (n = 0-2)

| R/W-x        | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| SID10        | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |  |  |

| bit 15 bit 8 |       |       |       |       |       |       |       |  |  |

| R/W-x       | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |  |  |

|-------------|-------|-------|-----|-------|-----|-------|-------|--|--|

| SID2        | SID1  | SID0  | _   | MIDE  | _   | EID17 | EID16 |  |  |

| bit 7 bit ( |       |       |     |       |     |       |       |  |  |

Legend:C = Writable bit, but only '0' can be written to clear the bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Include bit SIDx in filter comparison

0 = Bit SIDx is don't care in filter comparison

bit 4 **Unimplemented:** Read as '0'

bit 3 MIDE: Identifier Receive Mode bit

1 = Match only message types (standard or extended address) that correspond to EXIDE bit in filter

0 = Match either standard or extended address message if filters match

(i.e., if (Filter SID) = (Message SID) or if (Filter SID/EID) = (Message SID/EID))

bit 2 Unimplemented: Read as '0'

bit 1-0 **EID<17:16>:** Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

# REGISTER 19-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK EXTENDED IDENTIFIER REGISTER n (n = 0-2)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| EID7        | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |  |  |

| bit 7 bit 0 |       |       |       |       |       |       |       |  |  |

Legend:C = Writable bit, but only '0' can be written to clear the bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

Note:

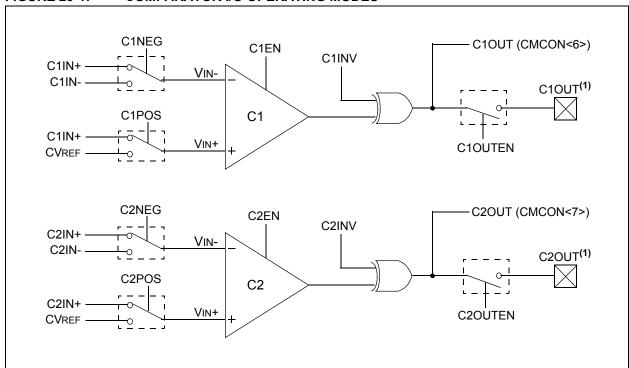

## 23.0 COMPARATOR MODULE

Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304. the dsPIC33FJ64GPX02/X04, dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Comparator" (DS70212) "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Comparator module provides a set of dual input comparators. The inputs to the comparator can be configured to use any one of the four pin inputs (C1IN+, C1IN-, C2IN+ and C2IN-) as well as the Comparator Voltage Reference Input (CVREF).

This peripheral contains output functions that may need to be configured by the peripheral pin select feature. For more information, see Section 11.6 "Peripheral Pin Select".

## FIGURE 23-1: COMPARATOR I/O OPERATING MODES

Note 1: This peripheral's outputs must be assigned to an available RPn pin before use. Refer to Section 11.6 "Peripheral Pin Select" for more information.

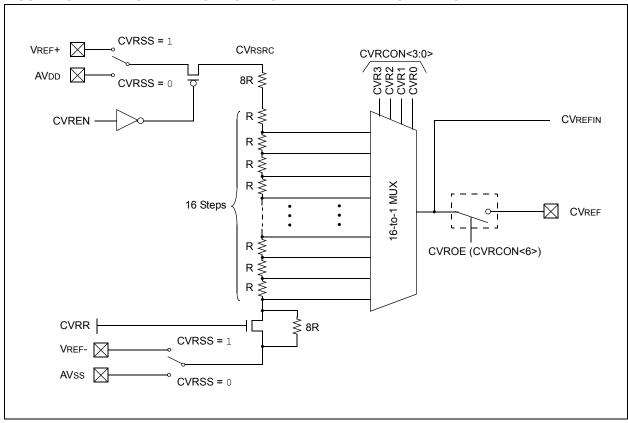

## 23.3 Comparator Voltage Reference

# 23.3.1 CONFIGURING THE COMPARATOR VOLTAGE REFERENCE

The voltage reference module is controlled through the CVRCON register (Register 23-2). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR3:CVR0), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

FIGURE 23-2: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 27.0 SPECIAL FEATURES

# Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- · Flexible configuration

- · Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming™ (ICSP™)

- · In-Circuit emulation

## 27.1 Configuration Bits

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25. "Device Configuration"** (DS70194), in the "dsPIC33F/PIC24H Family Reference Manual" for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 27-2.

Note that address 0xF80000 is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using table reads and table writes.

The Device Configuration register map is shown in Table 27-1.

TABLE 27-1: DEVICE CONFIGURATION REGISTER MAP

| Address  | Name               | Bit 7      | Bit 6               | Bit 5   | Bit 4        | Bit 3    | Bit 2             | Bit 1 | Bit 0   |  |

|----------|--------------------|------------|---------------------|---------|--------------|----------|-------------------|-------|---------|--|

| 0xF80000 | FBS                | RBS<       | :1:0>               | _       | _            |          | BSS<2:0>          |       | BWRP    |  |

| 0xF80002 | FSS <sup>(1)</sup> | RSS<       | :1:0>               | _       | _            |          | SSS<2:0>          |       | SWRP    |  |

| 0xF80004 | FGS                | _          | _                   | _       | _            | _        | GSS<1             | :0>   | GWRP    |  |

| 0xF80006 | FOSCSEL            | IESO —     |                     | _       | _            |          | FNOSC<2:0>        |       |         |  |

| 0xF80008 | FOSC               | FCKSM<1:0> |                     | IOL1WAY | _            | _        | OSCIOFNC POSCMD<1 |       | 1D<1:0> |  |

| 0xF8000A | FWDT               | FWDTEN     | WINDIS              | _       | WDTPRE       |          | WDTPOST<3:0>      |       |         |  |

| 0xF8000C | FPOR               |            | Reserved            | (2)     | ALTI2C       | _        | FPWRT<2:0>        |       | •       |  |

| 0xF8000E | FICD               | Reserv     | ved <sup>(3)</sup>  | JTAGEN  | _            | _        | _                 | ICS<  | :1:0>   |  |

| 0xF80010 | FUID0              |            |                     |         | User Unit ID | Byte 0   |                   |       |         |  |

| 0xF80012 | FUID1              |            | User Unit ID Byte 1 |         |              |          |                   |       |         |  |

| 0xF80014 | FUID2              |            | User Unit ID Byte 2 |         |              |          |                   |       |         |  |

| 0xF80016 | FUID3              |            |                     |         | User Unit ID | ) Byte 3 |                   |       |         |  |

**Legend:** — = unimplemented bit, read as '0'.

Note 1: This Configuration register is not available and reads as 0xFF on dsPIC33FJ32GP302/304 devices.

- 2: These bits are reserved and always read as '1'.

- 3: These bits are reserved for use by development tools and must be programmed as '1'.

| TABLE 30-17: PLL CLOCK TIMING SPECIFICATIONS (V | $V_{DD} = 3.0V \text{ TO } 3.6V)$ |

|-------------------------------------------------|-----------------------------------|

|-------------------------------------------------|-----------------------------------|

| AC CHA                       | AC CHARACTERISTICS |                                                                     |     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                    |     |       |                             |  |  |

|------------------------------|--------------------|---------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------------|--|--|

| Param No. Symbol Characteris |                    |                                                                     | tic | Min                                                                                                                                                                                                                                              | Typ <sup>(1)</sup> | Max | Units | Conditions                  |  |  |

| OS50                         | FPLLI              | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |     | 0.8                                                                                                                                                                                                                                              |                    | 8   | MHz   | ECPLL, HSPLL, XTPLL modes   |  |  |

| OS51                         | Fsys               | On-Chip VCO System<br>Frequency                                     |     | 100                                                                                                                                                                                                                                              | _                  | 200 | MHz   | _                           |  |  |

| OS52                         | TLOCK              | PLL Start-up Time (Lock Time)                                       |     | 0.9                                                                                                                                                                                                                                              | 1.5                | 3.1 | mS    | _                           |  |  |

| OS53                         | DCLK               | CLKO Stability (Jitter) <sup>(2)</sup>                              |     | -3                                                                                                                                                                                                                                               | 0.5                | 3   | %     | Measured over 100 ms period |  |  |

- **Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral\ Clock\ Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral\ Bit\ Rate\ Clock}}}$$

For example: Fosc = 32 MHz, DCLK = 3%, SPI bit rate clock, (i.e., SCK) is 2 MHz.

SPI SCK Jitter =

$$\left[\frac{DCLK}{\sqrt{\left(\frac{32\ MHz}{2\ MHz}\right)}}\right] = \left[\frac{3\%}{\sqrt{16}}\right] = \left[\frac{3\%}{4}\right] = 0.75\%$$

#### TABLE 30-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHARACTERISTICS |                                                   |    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |    |   |                     |       |  |  |  |

|--------------------|---------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|---------------------|-------|--|--|--|

| Param<br>No.       | Characteristic   Min   Tvn   Max   Units          |    |                                                                                                                                                                                                                                                   |    |   |                     | tions |  |  |  |

|                    | Internal FRC Accuracy @ 7.3728 MHz <sup>(1)</sup> |    |                                                                                                                                                                                                                                                   |    |   |                     |       |  |  |  |

| F20a               | FRC                                               | -2 | _                                                                                                                                                                                                                                                 | +2 | % | -40°C ≤ TA ≤ +85°C  |       |  |  |  |

| F20b               | FRC                                               | -5 | _                                                                                                                                                                                                                                                 | +5 | % | -40°C ≤ TA ≤ +125°C |       |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

#### **TABLE 30-19: INTERNAL RC ACCURACY**

| •• •• •• •• •• •• •• •• •• •• •• •• |                                  |                                                                                                                                                                                                                                                  |    |     |   |                     |  |  |  |  |  |

|-------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|---|---------------------|--|--|--|--|--|

| AC CH                               | ARACTERISTICS                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |    |     |   |                     |  |  |  |  |  |

| Param<br>No.                        | Characteristic                   | c Min Typ Max Units Conditions                                                                                                                                                                                                                   |    |     |   |                     |  |  |  |  |  |

|                                     | LPRC @ 32.768 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                  |    |     |   |                     |  |  |  |  |  |

| F21a                                | LPRC                             | -20                                                                                                                                                                                                                                              | ±6 | +20 | % | -40°C ≤ TA ≤ +85°C  |  |  |  |  |  |

| F21b                                | LPRC                             | -30                                                                                                                                                                                                                                              |    | +30 | % | -40°C ≤ TA ≤ +125°C |  |  |  |  |  |

Note 1: Change of LPRC frequency as VDD changes.

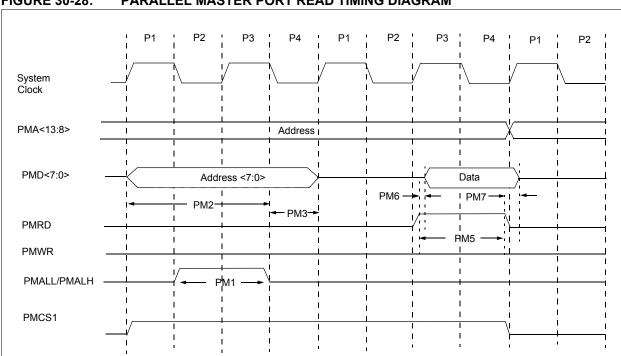

FIGURE 30-28: PARALLEL MASTER PORT READ TIMING DIAGRAM

TABLE 30-52: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHA       | ARACTERISTICS                                                  | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |          |      |       |            |  |  |

|--------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|------------|--|--|

| Param<br>No. | Characteristic                                                 | Min.                                                                                                                                                                                                                                                | Тур      | Max. | Units | Conditions |  |  |

| PM1          | PMALL/PMALH Pulse-Width                                        | _                                                                                                                                                                                                                                                   | 0.5 Tcy  | _    | ns    | _          |  |  |

| PM2          | Address Out Valid to PMALL/PMALH Invalid (address setup time)  | _                                                                                                                                                                                                                                                   | 0.75 Tcy | _    | ns    | _          |  |  |

| РМ3          | PMALL/PMALH Invalid to Address Out Invalid (address hold time) | _                                                                                                                                                                                                                                                   | 0.25 TcY | _    | ns    | _          |  |  |

| PM5          | PMRD Pulse-Width                                               | _                                                                                                                                                                                                                                                   | 0.5 Tcy  | _    | ns    | _          |  |  |

| PM6          | PMRD or PMENB Active to Data In Valid (data setup time)        | 150                                                                                                                                                                                                                                                 | _        | _    | ns    | _          |  |  |

| PM7          | PMRD or PMENB Inactive to Data In Invalid (data hold time)     |                                                                                                                                                                                                                                                     | _        | 5    | ns    | _          |  |  |

# TABLE 31-17: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+150°C for High Temperature |     |     |     |       |            |  |  |

|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|--|

| Param<br>No.          | Symbol | Characteristic                                                                                                                      | Min | Тур | Max | Units | Conditions |  |  |

| Clock Parameters      |        |                                                                                                                                     |     |     |     |       |            |  |  |

| HAD50                 | TAD    | ADC Clock Period <sup>(1)</sup>                                                                                                     | 147 | _   | _   | ns    | _          |  |  |

| Conversion Rate       |        |                                                                                                                                     |     |     |     |       |            |  |  |

| HAD56                 | FCNV   | Throughput Rate <sup>(1)</sup>                                                                                                      | _   | _   | 400 | Ksps  | _          |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

# TABLE 31-18: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+150°C for High Temperature |     |     |     |       |            |  |  |

|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|--|

| Param<br>No.          | Symbol | Characteristic                                                                                                                      | Min | Тур | Max | Units | Conditions |  |  |

| Clock Parameters      |        |                                                                                                                                     |     |     |     |       |            |  |  |

| HAD50                 | TAD    | ADC Clock Period <sup>(1)</sup>                                                                                                     | 104 | _   | _   | ns    | _          |  |  |

| Conversion Rate       |        |                                                                                                                                     |     |     |     |       |            |  |  |

|                       | FCNV   | Throughput Rate <sup>(1)</sup>                                                                                                      |     |     | 800 | Ksps  | •          |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.