Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp304t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

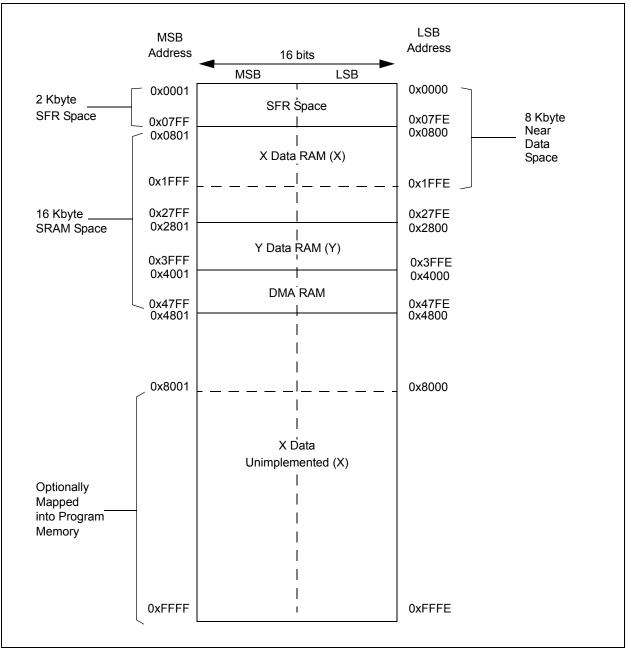

#### FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/ 804 DEVICES WITH 16 KB RAM

| REGISTER     | R /-13: IEC3: | INTERRUPT                         | ENABLE C       | UNIROL RE        | GISTER 3         |                 |       |

|--------------|---------------|-----------------------------------|----------------|------------------|------------------|-----------------|-------|

| U-0          | R/W-0         | R/W-0                             | R/W-0          | R/W-0            | U-0              | U-0             | U-0   |

| _            | RTCIE         | DMA5IE                            | DCIIE          | DCIEIE           | —                | —               | _     |

| bit 15       |               |                                   |                |                  |                  |                 | bit 8 |

|              |               |                                   |                |                  |                  |                 |       |

| U-0          | U-0           | U-0                               | U-0            | U-0              | U-0              | U-0             | U-0   |

| —            | —             | _                                 | —              | _                | —                | —               | —     |

| bit 7        |               |                                   |                |                  |                  |                 | bit C |

|              |               |                                   |                |                  |                  |                 |       |

| Legend:      |               |                                   |                |                  |                  |                 |       |

| R = Readal   | ble bit       | W = Writable                      | bit            | U = Unimpler     | mented bit, reac | l as '0'        |       |

| -n = Value a | at POR        | '1' = Bit is set                  |                | '0' = Bit is cle | ared             | x = Bit is unkn | own   |

|              |               |                                   |                |                  |                  |                 |       |

| bit 15       | Unimplemen    | ted: Read as '                    | 0'             |                  |                  |                 |       |

| bit 14       | RTCIE: Real-  | Time Clock and                    | d Calendar In  | terrupt Enable   | bit              |                 |       |

|              |               | request enable                    |                |                  |                  |                 |       |

|              | 0 = Interrupt | request not ena                   | abled          |                  |                  |                 |       |

| bit 13       | DMA5IE: DM    | A Channel 5 D                     | ata Transfer ( | Complete Interi  | rupt Enable bit  |                 |       |

|              | •             | request enable<br>request not ena |                |                  |                  |                 |       |

| bit 12       | DCIIE: DCI E  | vent Interrupt E                  | Enable bit     |                  |                  |                 |       |

|              |               |                                   |                |                  |                  |                 |       |

# REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

|        | Done. Doi Event interrupt Enable bit   |

|--------|----------------------------------------|

|        | 1 = Interrupt request enabled          |

|        | 0 = Interrupt request not enabled      |

| bit 11 | DCIEIE: DCI Error Interrupt Enable bit |

|        |                                        |

```

1 = Interrupt request enabled

```

- 0 = Interrupt request not enabled

- bit 10-0 Unimplemented: Read as '0'

| U-0          | R/W-1              | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|--------------|--------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| 0-0          | R/W-1              |                                          | R/W-U          | 0-0               | R/W-1           |                 | R/W-U |

| <br>bit 15   |                    | T1IP<2:0>                                |                | —                 |                 | OC1IP<2:0>      | bi    |

| 511 15       |                    |                                          |                |                   |                 |                 | DI    |

| U-0          | R/W-1              | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

| _            |                    | IC1IP<2:0>                               |                |                   |                 | INT0IP<2:0>     |       |

| bit 7        |                    |                                          |                |                   |                 |                 | bi    |

| Legend:      |                    |                                          |                |                   |                 |                 |       |

| R = Readab   | le bit             | W = Writable                             | bit            | U = Unimple       | mented bit, rea | ad as '0'       |       |

| -n = Value a |                    | '1' = Bit is set                         |                | '0' = Bit is cle  |                 | x = Bit is unkn | own   |

|              |                    |                                          |                |                   |                 |                 |       |

| bit 15       | Unimplem           | ented: Read as '                         | )'             |                   |                 |                 |       |

| bit 14-12    | T1IP<2:0>:         | Timer1 Interrupt                         | Priority bits  |                   |                 |                 |       |

|              | 111 = Inter        | rupt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              |                    | rupt is priority 1                       |                |                   |                 |                 |       |

|              |                    | rupt source is dis                       |                |                   |                 |                 |       |

| bit 11       | -                  | ented: Read as '                         |                |                   |                 |                 |       |

| bit 10-8     |                    | >: Output Compa                          |                | -                 | rity bits       |                 |       |

|              | 111 = Inter<br>•   | rupt is priority 7 (I                    | nignest priori | ty interrupt)     |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              |                    | rupt is priority 1<br>rupt source is dis | abled          |                   |                 |                 |       |

| bit 7        |                    | ented: Read as '                         |                |                   |                 |                 |       |

| bit 6-4      | •                  | : Input Capture C                        |                | errunt Priority h | nits            |                 |       |

|              |                    | rupt is priority 7 (I                    |                |                   |                 |                 |       |

|              | •                  |                                          | 0 1            | , ,               |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •<br>001 = Inter   | rupt is priority 1                       |                |                   |                 |                 |       |

|              |                    | rupt source is dis                       | abled          |                   |                 |                 |       |

| bit 3        | Unimplem           | ented: Read as '                         | )'             |                   |                 |                 |       |

| bit 2-0      | INT0IP<2:0         | >: External Interr                       | upt 0 Priority | / bits            |                 |                 |       |

|              | 111 = Inter        | rupt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              |                    | rupt is priority 1                       |                |                   |                 |                 |       |

|              | 000 <b>= Inter</b> | rupt source is dis                       | abled          |                   |                 |                 |       |

DS70292G-page 110

| U-0                       | U-0                                                                                                                                                                | U-0                                                                                                                                                                                                                       | U-0                                                                                        | U-0                                              | R/W-1            | R/W-0           | R/W-0 |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|-----------------|-------|

|                           | _                                                                                                                                                                  | _                                                                                                                                                                                                                         |                                                                                            | _                                                |                  | C1TXIP<2:0>(1)  |       |

| bit 15                    |                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                            |                                                  |                  |                 | bit   |

|                           |                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                            |                                                  |                  |                 |       |

| U-0                       | R/W-1                                                                                                                                                              | R/W-0                                                                                                                                                                                                                     | R/W-0                                                                                      | U-0                                              | R/W-1            | R/W-0           | R/W-0 |

| —                         |                                                                                                                                                                    | DMA7IP<2:0>                                                                                                                                                                                                               |                                                                                            | —                                                |                  | DMA6IP<2:0>     |       |

| bit 7                     |                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                            |                                                  |                  |                 | bit   |

| Legend:                   |                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                            |                                                  |                  |                 |       |

| R = Readab                | ole bit                                                                                                                                                            | W = Writable                                                                                                                                                                                                              | bit                                                                                        | U = Unimpler                                     | mented bit, rea  | ad as '0'       |       |

| -n = Value a              | at POR                                                                                                                                                             | '1' = Bit is set                                                                                                                                                                                                          |                                                                                            | '0' = Bit is cle                                 | ared             | x = Bit is unkn | own   |

| L:4 7 44                  |                                                                                                                                                                    | nted: Deed ee (                                                                                                                                                                                                           | ~'                                                                                         |                                                  |                  |                 |       |

| bit 15-11                 | •                                                                                                                                                                  | nted: Read as '                                                                                                                                                                                                           |                                                                                            |                                                  | (4)              |                 |       |

| bit 10-8                  |                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                            | autor of laterations                             |                  |                 |       |

| 011 10-0                  |                                                                                                                                                                    | >: ECAN1 Trans                                                                                                                                                                                                            |                                                                                            |                                                  | Priority bits    |                 |       |

| DIL 10-0                  |                                                                                                                                                                    | upt is priority 7 (l                                                                                                                                                                                                      |                                                                                            |                                                  | Priority bits    |                 |       |

| bit 10-0                  |                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                            |                                                  | Priority dits."  |                 |       |

| Dit 10-0                  |                                                                                                                                                                    |                                                                                                                                                                                                                           |                                                                                            |                                                  | Priority bits    |                 |       |

| Dit 10-0                  | 111 = Intern<br>•<br>•                                                                                                                                             |                                                                                                                                                                                                                           |                                                                                            |                                                  | Priority bits."  |                 |       |

| DIL 10-0                  | 111 = Intern<br>•<br>•<br>•<br>•<br>•                                                                                                                              | upt is priority 7 (l                                                                                                                                                                                                      | highest priorit                                                                            |                                                  |                  |                 |       |

| bit 7                     | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                        | upt is priority 7 (l<br>upt is priority 1                                                                                                                                                                                 | highest priorif<br>abled                                                                   |                                                  |                  |                 |       |

|                           | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                        | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis                                                                                                                                                            | highest priorif<br>abled                                                                   | ty interrupt)                                    |                  | rity bits       |       |

| bit 7                     | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0                                                                                  | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br>inted: Read as '(                                                                                                                                       | highest priorit<br>abled<br>o'<br>el 7 Data Tra                                            | ty interrupt)<br>nsfer Complete                  |                  | rity bits       |       |

| bit 7                     | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0                                                                                  | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br>ented: Read as '(<br>0>: DMA Channe                                                                                                                     | highest priorit<br>abled<br>o'<br>el 7 Data Tra                                            | ty interrupt)<br>nsfer Complete                  |                  | rity bits       |       |

| bit 7                     | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0                                                                                  | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br>ented: Read as '(<br>0>: DMA Channe                                                                                                                     | highest priorit<br>abled<br>o'<br>el 7 Data Tra                                            | ty interrupt)<br>nsfer Complete                  |                  | rity bits       |       |

| bit 7                     | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern                                                                            | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br>ented: Read as 'd<br>0>: DMA Chann<br>upt is priority 7 (l                                                                                              | highest priorit<br>abled<br>o'<br>el 7 Data Tra                                            | ty interrupt)<br>nsfer Complete                  |                  | rity bits       |       |

| bit 7                     | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:0<br>111 = Intern<br>001 = Intern                                                            | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>inted:</b> Read as 'ú<br><b>0&gt;:</b> DMA Chann<br>upt is priority 7 (l<br>upt is priority 1                                                        | abled<br><sub>D</sub> '<br>el 7 Data Tra<br>highest priorit                                | ty interrupt)<br>nsfer Complete                  |                  | rity bits       |       |

| bit 7<br>bit 6-4          | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern                                            | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>inted:</b> Read as '(<br><b>0&gt;:</b> DMA Chann<br>upt is priority 7 (l<br>upt is priority 1<br>upt source is dis                                   | abled<br>o <sup>,</sup><br>el 7 Data Tra<br>highest priorit                                | ty interrupt)<br>nsfer Complete                  |                  | rity bits       |       |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme                               | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br>ented: Read as 'd<br>0>: DMA Channe<br>upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br>ented: Read as 'd                              | abled<br><sup>D'</sup><br>el 7 Data Tra<br>highest priorit<br>abled                        | ty interrupt)<br>nsfer Complete<br>ty interrupt) | e Interrupt Prio |                 |       |

| bit 7<br>bit 6-4          | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>Unimpleme<br>DMA6IP<2:(                                 | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>inted:</b> Read as '(<br><b>0&gt;:</b> DMA Chann<br>upt is priority 7 (l<br>upt source is dis<br><b>inted:</b> Read as '(<br><b>0&gt;:</b> DMA Chann | abled<br><sup>D'</sup><br>el 7 Data Tra<br>highest priorit<br>abled<br>D'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | e Interrupt Prio |                 |       |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>Unimpleme<br>DMA6IP<2:(                                 | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br>ented: Read as 'd<br>0>: DMA Channe<br>upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br>ented: Read as 'd                              | abled<br><sup>D'</sup><br>el 7 Data Tra<br>highest priorit<br>abled<br>D'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | e Interrupt Prio |                 |       |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>Unimpleme<br>DMA6IP<2:(                                 | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>inted:</b> Read as '(<br><b>0&gt;:</b> DMA Chann<br>upt is priority 7 (l<br>upt source is dis<br><b>inted:</b> Read as '(<br><b>0&gt;:</b> DMA Chann | abled<br><sup>D'</sup><br>el 7 Data Tra<br>highest priorit<br>abled<br>D'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | e Interrupt Prio |                 |       |

| bit 7<br>bit 6-4<br>bit 3 | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA7IP<2:(<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>DMA6IP<2:(<br>111 = Intern | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>inted:</b> Read as '(<br><b>0&gt;:</b> DMA Chann<br>upt is priority 7 (l<br>upt source is dis<br><b>inted:</b> Read as '(<br><b>0&gt;:</b> DMA Chann | abled<br><sup>D'</sup><br>el 7 Data Tra<br>highest priorit<br>abled<br>D'<br>el 6 Data Tra | ty interrupt)<br>nsfer Complete<br>ty interrupt) | e Interrupt Prio |                 |       |

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

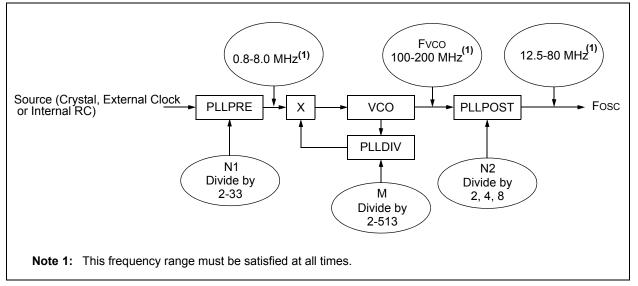

#### 9.1.4 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M,' by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2.' This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS. For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by:

#### EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \bullet \left(\frac{M}{N1 \bullet N2}\right)$$

For example, suppose a 10 MHz crystal is being used with the selected oscillator mode of XT with PLL.

- If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

#### EQUATION 9-3: XT WITH PLL MODE EXAMPLE

$$FCY = \frac{FOSC}{2} = \frac{1}{2} \left( \frac{10000000 \bullet 32}{2 \bullet 2} \right) = 40MIPS$$

#### FIGURE 9-2: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 PLL BLOCK DIAGRAM

| REGISTERS     | 9-5: ACLI                    |                                         | ARY CONT     | ROL REGIST       | ER               |                 |       |

|---------------|------------------------------|-----------------------------------------|--------------|------------------|------------------|-----------------|-------|

| U-0           | U-0                          | R/W-0                                   | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| _             | _                            | SELACLK                                 | AOSCI        | MD<1:0>          | A                | PSTSCLR<2:0>    | >     |

| bit 15        |                              |                                         |              |                  |                  |                 | bit 8 |

| R/W-0         | U-0                          | U-0                                     | U-0          | U-0              | U-0              | U-0             | U-0   |

| ASRCSEL       | 0-0                          | 0-0                                     | 0-0          | 0-0              | 0-0              | 0-0             | 0-0   |

| bit 7         | _                            | —                                       |              |                  |                  | —               | bit   |

|               |                              |                                         |              |                  |                  |                 | DIL   |

| Legend:       |                              |                                         |              |                  |                  |                 |       |

| R = Readable  | e bit                        | W = Writable I                          | oit          | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at | POR                          | '1' = Bit is set                        |              | '0' = Bit is cle | ared             | x = Bit is unkn | iown  |

|               |                              |                                         |              |                  |                  |                 |       |

| bit 15-14     | Unimpleme                    | ented: Read as '0                       | )'           |                  |                  |                 |       |

| bit 13        | SELACLK:                     | Select Auxiliary                        | Clock Source | for Auxiliary C  | lock Divider     |                 |       |

|               | •                            | y Oscillators prov<br>put (Fosc) provid |              |                  | •                |                 |       |

| bit 12-11     |                              | 1:0>: Auxiliary Os                      |              |                  |                  | Difficien       |       |

|               |                              | ternal Clock Mod                        |              |                  |                  |                 |       |

|               | 10 = XT Os                   | cillator Mode Sel                       | ect          |                  |                  |                 |       |

|               |                              | cillator Mode Sel                       |              |                  |                  |                 |       |

|               |                              | ry Oscillator Disa                      |              | <b>D</b>         |                  |                 |       |

| bit 10-8      |                              | R<2:0>: Auxiliary                       | Clock Output | Divider          |                  |                 |       |

|               | 111 = divide<br>110 = divide |                                         |              |                  |                  |                 |       |

|               | 101 = divide                 | •                                       |              |                  |                  |                 |       |

|               | 100 <b>= divide</b>          | •                                       |              |                  |                  |                 |       |

|               | 011 = divide                 |                                         |              |                  |                  |                 |       |

|               | 010 = divide                 | •                                       |              |                  |                  |                 |       |

|               | 001 = divide                 | ed by 64<br>ed by 256 (defaul           | t)           |                  |                  |                 |       |

| bit 7         |                              | Select Reference                        | ,            | e for Auxiliary  | Clock            |                 |       |

| ~             |                              | Oscillator is the                       |              | •                | 0.001            |                 |       |

|               |                              | y Oscillator is the                     |              |                  |                  |                 |       |

|               | -                            |                                         |              |                  |                  |                 |       |

# REGISTER 9-5: ACLKCON: AUXILIARY CONTROL REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

Unimplemented: Read as '0'

bit 6-0

#### 11.9 Peripheral Pin Select Registers

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 family of devices implement 33 registers for remappable peripheral configuration:

- 16 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR11 and PRINR18-RPINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

| Note: | Inpu | t and Output  | t Re  | gister | valu | es can | only  |

|-------|------|---------------|-------|--------|------|--------|-------|

|       | be   | changed       | if    | the    | IOI  | _OCK   | bit   |

|       | (OS  | CCON<6>)      | is    | set    | to   | '0'.   | See   |

|       | Sec  | tion 11.6.3.1 |       | "Cont  | rol  | Reg    | ister |

|       | Loc  | k" for a spec | cific | comm   | and  | seque  | nce.  |

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | —   |       |       | INT1R<4:0> |       |       |

| bit 15 |     |     | •     |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 Unimplemented: Read as '0 | Inimplemented: Read as '0' |

|-------------------------------------|----------------------------|

|-------------------------------------|----------------------------|

```

bit 12-8

INT1R<4:0>: Assign External Interrupt 1 (INTR1) to the corresponding RPn pin

1111 = Input tied to Vss

11001 = Input tied to RP25

•

•

00001 = Input tied to RP1

00000 = Input tied to RP0

bit 7-0

Unimplemented: Read as '0'

```

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| U-0                | U-0                                                  | U-0                                                                    | R/W-1         | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

|--------------------|------------------------------------------------------|------------------------------------------------------------------------|---------------|-----------------------------|------------------|-----------------|-------|

| —                  |                                                      | _                                                                      |               |                             | U1CTSR<4:0       | >               |       |

| bit 15             |                                                      |                                                                        |               |                             |                  |                 | bit 8 |

|                    |                                                      |                                                                        | <b>D</b> 44/4 |                             |                  | D 44/4          |       |

| U-0                | U-0                                                  | U-0                                                                    | R/W-1         | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

| -:+ 7              | _                                                    | —                                                                      |               |                             | U1RXR<4:0>       | •               | h:+ 0 |

| bit 7              |                                                      |                                                                        |               |                             |                  |                 | bit C |

| Legend:            |                                                      |                                                                        |               |                             |                  |                 |       |

| R = Readab         | le bit                                               | W = Writable                                                           | oit           | U = Unimplen                | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                                | '1' = Bit is set                                                       |               | '0' = Bit is clea           | ared             | x = Bit is unkr | nown  |

| bit 15-13          | Unimpleme                                            | nted: Read as '                                                        | )'            |                             |                  |                 |       |

| bit 12-8           | -                                                    | 0>: Assign UAR                                                         |               | end $(\overline{U1CTS})$ to | the correspo     | ndina RPn nin   |       |

|                    |                                                      | ut tied to Vss                                                         |               |                             |                  | ionig i i i più |       |

|                    |                                                      | ut tied to RP25                                                        |               |                             |                  |                 |       |

|                    | •                                                    |                                                                        |               |                             |                  |                 |       |

|                    | •                                                    |                                                                        |               |                             |                  |                 |       |

|                    |                                                      |                                                                        |               |                             |                  |                 |       |

|                    | •                                                    |                                                                        |               |                             |                  |                 |       |

|                    |                                                      | ut tied to RP1<br>ut tied to RP0                                       |               |                             |                  |                 |       |

| oit 7-5            | 00000 <b>= Inp</b>                                   |                                                                        | )'            |                             |                  |                 |       |

|                    | 00000 = Inp<br>Unimpleme                             | ut tied to RP0                                                         |               | 1RX) to the cor             | responding RF    | n pin           |       |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(                                     |               | 1RX) to the cor             | responding RF    | n pin           |       |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss |               | 1RX) to the cor             | responding RF    | 'n pin          |       |

| bit 7-5<br>bit 4-0 | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss |               | 1RX) to the cor             | responding RF    | 'n pin          |       |

### REGISTER 11-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

00001 = Input tied to RP1 00000 = Input tied to RP0

| U-0          | U-0                 | U-0                                                    | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |

|--------------|---------------------|--------------------------------------------------------|-------|------------------|-----------------|-----------------|-------|--|--|--|

| _            |                     | _                                                      |       |                  | U2CTSR<4:0>     |                 |       |  |  |  |

| bit 15       |                     |                                                        |       |                  |                 |                 | bit 8 |  |  |  |

|              |                     |                                                        |       |                  |                 |                 |       |  |  |  |

| U-0          | U-0                 | U-0                                                    | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |

| —            | —                   | —                                                      |       |                  | U2RXR<4:0       | >               |       |  |  |  |

| bit 7        |                     |                                                        |       |                  |                 |                 | bit C |  |  |  |

|              |                     |                                                        |       |                  |                 |                 |       |  |  |  |

| Legend:      | la hit              |                                                        | .:+   | II – Unimplor    | nanted hit rea  | d aa '0'        |       |  |  |  |

| R = Readab   |                     | W = Writable t                                         | אנ    |                  | nented bit, rea |                 |       |  |  |  |

| -n = Value a | t POR               | '1' = Bit is set                                       |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |  |  |  |

| bit 12-8     | 11111 <b>= In</b> p | :0>: Assign UAR<br>out tied to Vss<br>out tied to RP25 |       | - ( , -          |                 | 5 F             |       |  |  |  |

|              | •                   |                                                        |       |                  |                 |                 |       |  |  |  |

|              | •                   | but tied to RP1<br>but tied to RP0                     |       |                  |                 |                 |       |  |  |  |

| bit 7-5      | 00000 <b>= Inp</b>  |                                                        | ,     |                  |                 |                 |       |  |  |  |

| -n = Value at POR '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |       |                                    |           | nown  |       |  |

|------------------------------------|-----|-----------------------------------------|-------|------------------------------------|-----------|-------|-------|--|

| R = Readable I                     | oit | W = Writable                            | bit   | U = Unimplemented bit, read as '0' |           |       |       |  |

| Legend:                            |     |                                         |       |                                    |           |       |       |  |

|                                    |     |                                         |       |                                    |           |       |       |  |

| bit 7                              |     |                                         |       |                                    |           |       | bit   |  |

| —                                  | _   | —                                       |       |                                    | RP24R<4:0 | >     |       |  |

| U-0                                | U-0 | U-0                                     | R/W-0 | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |

|                                    |     |                                         |       |                                    |           |       |       |  |

| bit 15                             |     |                                         |       |                                    |           |       | bit   |  |

|                                    | —   |                                         |       |                                    | RP25R<4:0 | >     |       |  |

| U-0                                | U-0 | U-0                                     | R/W-0 | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |

# REGISTER 11-29: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 **RP25R<4:0>:** Peripheral Output Function is Assigned to RP25 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 **RP24R<4:0>:** Peripheral Output Function is Assigned to RP24 Output Pin bits (see Table 11-2 for peripheral function numbers)

Note 1: This register is implemented in 44-pin devices only.

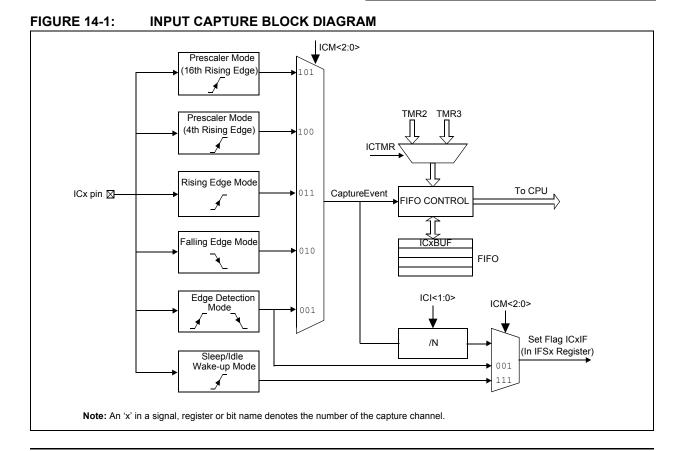

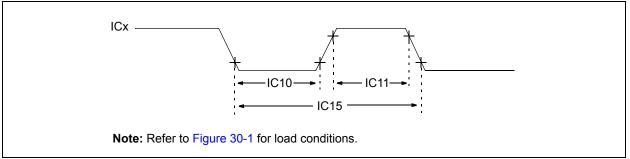

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices support up to four input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- 1. Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- 2. Capture timer value on every edge (rising and falling)

- 3. Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select one of two 16bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Use of input capture to provide additional sources of external interrupts

- Note: Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to '1' (ICI<1:0> = 00)

### 18.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

```

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en532311

```

#### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 23.2 Comparator Control Register

| R/W-0        | U-0                                                                                                           | R/W-0                                                   | R/W-0        | R/W-0              | R/W-0           | R/W-0                  | R/W-0                  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------|--------------------|-----------------|------------------------|------------------------|--|--|--|

| CMIDL        | _                                                                                                             | C2EVT                                                   | C1EVT        | C2EN               | C1EN            | C2OUTEN <sup>(1)</sup> | C1OUTEN <sup>(2)</sup> |  |  |  |

| bit 15       |                                                                                                               |                                                         |              | 1                  |                 |                        | bit 8                  |  |  |  |

| R-0          | R-0                                                                                                           | R/W-0                                                   | R/W-0        | R/W-0              | R/W-0           | R/W-0                  | R/W-0                  |  |  |  |

| C2OUT        | C10UT                                                                                                         | C2INV                                                   | C1INV        | C2NEG              | C2POS           | C1NEG                  | C1POS                  |  |  |  |

| bit 7        | 01001                                                                                                         | 021111                                                  | Onite        | OZINEO             | 021 00          | Onles                  | bit (                  |  |  |  |

|              |                                                                                                               |                                                         |              |                    |                 |                        |                        |  |  |  |

| Legend:      |                                                                                                               |                                                         |              |                    |                 |                        |                        |  |  |  |

| R = Readab   | le bit                                                                                                        | W = Writable                                            | bit          | U = Unimplem       | nented bit, rea | ad as '0'              |                        |  |  |  |

| -n = Value a | t POR                                                                                                         | '1' = Bit is set                                        |              | '0' = Bit is clea  | ared            | x = Bit is unkr        | iown                   |  |  |  |

| bit 15       | 1 = When de                                                                                                   | in Idle Mode b<br>evice enters Idle<br>e normal modul   | e mode, modu |                    | nerate interrup | ots. Module is stil    | ll enabled.            |  |  |  |

| bit 14       | Unimplemer                                                                                                    | nted: Read as '                                         | 0'           |                    |                 |                        |                        |  |  |  |

| bit 13       | C2EVT: Com                                                                                                    | parator 2 Even                                          | t bit        |                    |                 |                        |                        |  |  |  |

|              |                                                                                                               | ator output chai<br>ator output did i                   |              | ates               |                 |                        |                        |  |  |  |

| bit 12       |                                                                                                               | parator 1 Even                                          |              |                    |                 |                        |                        |  |  |  |

|              | <ul> <li>1 = Comparator output changed states</li> <li>0 = Comparator output did not change states</li> </ul> |                                                         |              |                    |                 |                        |                        |  |  |  |

| bit 11       | 1 = Compara                                                                                                   | parator 2 Enable<br>ator is enabled<br>ator is disabled | e bit        |                    |                 |                        |                        |  |  |  |

| bit 10       | C1EN: Comp                                                                                                    | parator 1 Enable                                        | e bit        |                    |                 |                        |                        |  |  |  |

|              | <ul> <li>1 = Comparator is enabled</li> <li>0 = Comparator is disabled</li> </ul>                             |                                                         |              |                    |                 |                        |                        |  |  |  |

| bit 9        | C2OUTEN: (                                                                                                    | Comparator 2 C                                          | utput Enable | bit <sup>(1)</sup> |                 |                        |                        |  |  |  |

|              |                                                                                                               | ator output is dr<br>ator output is no                  |              |                    |                 |                        |                        |  |  |  |

| bit 8        |                                                                                                               | Comparator 1 C                                          | •            |                    |                 |                        |                        |  |  |  |

|              |                                                                                                               | ator output is dr<br>ator output is no                  |              |                    |                 |                        |                        |  |  |  |

| bit 7        | C2OUT: Con                                                                                                    | nparator 2 Outp                                         | ut bit       |                    |                 |                        |                        |  |  |  |

|              | When C2INV = 0:                                                                                               |                                                         |              |                    |                 |                        |                        |  |  |  |

|              | 1 = C2 VIN+ > C2 VIN- 0 = C2 VIN+ < C2 VIN-                                                                   |                                                         |              |                    |                 |                        |                        |  |  |  |

|              |                                                                                                               |                                                         |              |                    |                 |                        |                        |  |  |  |

|              | When C2INV                                                                                                    | ′ = 1:                                                  |              |                    |                 |                        |                        |  |  |  |

|              | When C2INV<br>0 = C2 VIN+<br>1 = C2 VIN+                                                                      | > C2 VIN-                                               |              |                    |                 |                        |                        |  |  |  |

## REGISTER 23-1: CMCON: COMPARATOR CONTROL REGISTER

- **Note 1:** If C2OUTEN = 1, the C2OUT peripheral output must be configured to an available RPx pin. See **Section 11.6 "Peripheral Pin Select"** for more information.

- 2: If C1OUTEN = 1, the C1OUT peripheral output must be configured to an available RPx pin. See Section 11.6 "Peripheral Pin Select" for more information.

NOTES:

| REGISTER      | 26-2: PMM                                                                               | ODE: PARALI                                                                      | EL PORT M                                           | ODE REGIS                                                 | STER                                                                                                 |                          |                      |

|---------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------|----------------------|

| R-0           | R/W-0                                                                                   | R/W-0                                                                            | R/W-0                                               | R/W-0                                                     | R/W-0                                                                                                | R/W-0                    | R/W-0                |

| BUSY          | IRQI                                                                                    | M<1:0>                                                                           | INCM                                                | <1:0>                                                     | MODE16                                                                                               | MODE                     | <1:0>                |

| bit 15        | ·                                                                                       |                                                                                  |                                                     |                                                           | •                                                                                                    |                          | bit 8                |

| R/W-0         | R/W-0                                                                                   | R/W-0                                                                            | R/W-0                                               | R/W-0                                                     | R/W-0                                                                                                | R/W-0                    | R/W-0                |

| WAITE         | 3<1:0> <sup>(1)</sup>                                                                   |                                                                                  | WAITI                                               | M<3:0>                                                    |                                                                                                      | WAITE<                   | <1:0> <sup>(1)</sup> |

| bit 7         |                                                                                         |                                                                                  |                                                     |                                                           |                                                                                                      |                          | bit                  |

| Legend:       |                                                                                         |                                                                                  |                                                     |                                                           |                                                                                                      |                          |                      |

| R = Readable  | e bit                                                                                   | W = Writable                                                                     | bit                                                 | U = Unimple                                               | mented bit, read                                                                                     | as '0'                   |                      |

| -n = Value at | POR                                                                                     | '1' = Bit is set                                                                 |                                                     | '0' = Bit is cle                                          | eared                                                                                                | x = Bit is unkn          | own                  |

| bit 15        | BUSY: Busy                                                                              | bit (Master mod                                                                  | le only)                                            |                                                           |                                                                                                      |                          |                      |

|               |                                                                                         | usy (not useful v                                                                |                                                     | essor stall is a                                          | ctive)                                                                                               |                          |                      |

| bit 14-13     |                                                                                         | Interrupt Reque                                                                  | est Mode hits                                       |                                                           |                                                                                                      |                          |                      |

|               | 11 = Interrup<br>or on a<br>10 = No inte<br>01 = Interrup                               | ot generated who                                                                 | en Read Buffe<br>eration when I<br>processor sta    | PMA<1:0> = 1                                              | Write Buffer 3 is v<br>11 (Addressable<br>le                                                         |                          |                      |

| bit 12-11     | INCM<1:0>:                                                                              | Increment Mod                                                                    | e bits                                              |                                                           |                                                                                                      |                          |                      |

|               | 10 = Decrem<br>01 = Increme                                                             | ad and write but<br>nent ADDR<10:0<br>ent ADDR<10:0<br>ement or decrer           | )> by 1 every ı<br>> by 1 every re                  | read/write cyclead/write cycle                            |                                                                                                      | /)                       |                      |

| bit 10        | MODE16: 8-                                                                              | bit/16-bit Mode                                                                  | bit                                                 |                                                           |                                                                                                      |                          |                      |

|               |                                                                                         |                                                                                  |                                                     |                                                           | o the data registe<br>the data register                                                              |                          |                      |

| bit 9-8       | 11 = Master<br>10 = Master<br>01 = Enhanc                                               | mode 2 (PMCS<br>ced PSP, control                                                 | 1, PMRD/PMV<br>1, PMRD <u>, PMV</u><br>signals (PMR | VR, PMENB,<br>WR <u>, PMBE, P</u><br>D, PM <u>WR, P</u> M | PMBE, PMA <x:0<br><u>PMA<x:< u="">0&gt; and P<br/>MCS1, PMD&lt;7:0<br/>PMWR, PMCS</x:<></u></x:0<br> | MD<7:0>)<br>> and PMA<1: | 0>)                  |