Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp202-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33F/PIC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ64GP804 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

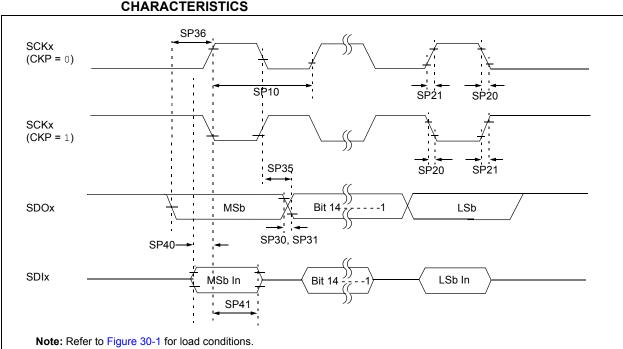

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

- Section 30. "I/O Ports with Peripheral Pin Select (PPS)" (DS70190)

- Section 32. "Interrupts (Part III)" (DS70214)

- Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211)

- Section 34. "Comparator" (DS70212)

- Section 35. "Parallel Master Port (PMP)" (DS70299)

- Section 36. "Programmable Cyclic Redundancy Check (CRC)" (DS70298)

- Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301)

- Section 38. "Direct Memory Access (DMA) (Part III)" (DS70215)

- Section 39. "Oscillator (Part III)" (DS70216)

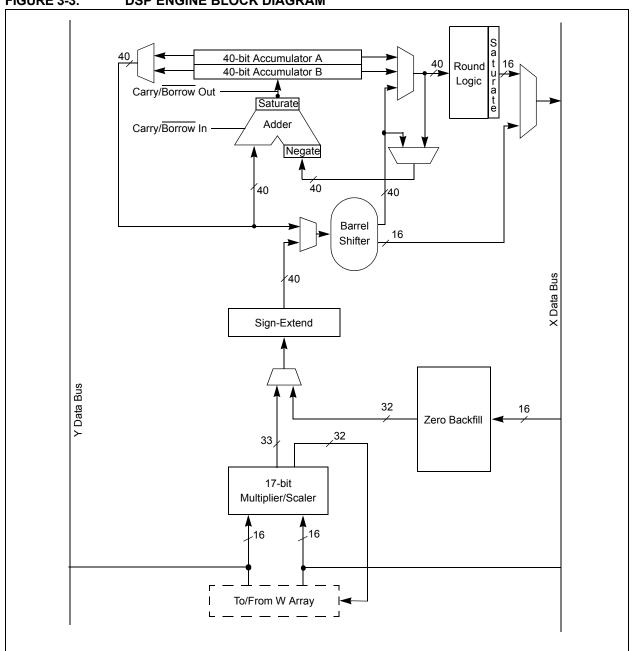

# FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

# TABLE 4-16: DMA REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3       | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-----------|------|--------|-----------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-------------|-------|-------|--------|---------------|

| DMA0CON   | 0380 | CHEN   | SIZE      | DIR    | HALF   | NULLW  |        | _     | —     | _        |       | AMOD  | E<1:0> | —           | _     | MODE  | <1:0>  | 0000          |

| DMA0REQ   | 0382 | FORCE  | _         |        |        | _      |        |       | —     |          |       |       | I      | IRQSEL<6:0> | >     |       |        | 0000          |

| DMA0STA   | 0384 |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA0STB   | 0386 |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA0PAD   | 0388 |        |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA0CNT   | 038A | _      | _         |        |        | _      |        |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA1CON   | 038C | CHEN   | SIZE      | DIR    | HALF   | NULLW  |        |       | —     |          |       | AMOD  | E<1:0> | —           |       | MODE  | =<1:0> | 0000          |

| DMA1REQ   | 038E | FORCE  | _         |        |        | _      |        |       | —     |          |       |       | I      | IRQSEL<6:0> | >     |       |        | 0000          |

| DMA1STA   | 0390 |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA1STB   | 0392 |        | STB<15:0> |        |        |        |        |       |       |          |       | 0000  |        |             |       |       |        |               |

| DMA1PAD   | 0394 |        | PAD<15:0> |        |        |        |        |       |       |          |       | 0000  |        |             |       |       |        |               |

| DMA1CNT   | 0396 | _      | Ι         | _      | _      | _      | _      |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA2CON   | 0398 | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | —           | —     | MODE  | <1:0>  | 0000          |

| DMA2REQ   | 039A | FORCE  | _         | _      | _      | _      | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA2STA   | 039C |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA2STB   | 039E |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA2PAD   | 03A0 |        |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA2CNT   | 03A2 | _      | Ι         | _      | _      | _      | _      |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA3CON   | 03A4 | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      | _     | _     | _        | _     | AMOD  | E<1:0> | _           | _     | MODE  | <1:0>  | 0000          |

| DMA3REQ   | 03A6 | FORCE  | Ι         | _      | _      | _      | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA3STA   | 03A8 |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA3STB   | 03AA |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA3PAD   | 03AC |        |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA3CNT   | 03AE | _      | Ι         | _      | _      | _      | _      |       |       |          |       | CN    | <9:0>  |             |       |       |        | 0000          |

| DMA4CON   | 03B0 | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | —           | _     | MODE  | <1:0>  | 0000          |

| DMA4REQ   | 03B2 | FORCE  | Ι         | _      | _      | _      | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA4STA   | 03B4 |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA4STB   | 03B6 |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA4PAD   | 03B8 |        |           |        |        |        |        |       | P     | AD<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA4CNT   | 03BA | _      | _         | _      | _      | _      | _      |       |       |          |       | CN    | [<9:0> |             |       |       |        | 0000          |

| DMA5CON   | 03BC | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      | —     | _     | —        | —     | AMOD  | E<1:0> | —           | _     | MODE  | <1:0>  | 0000          |

| DMA5REQ   | 03BE | FORCE  | _         | —      | _      |        | _      | _     | _     | _        |       |       | I      | IRQSEL<6:0  | >     |       |        | 0000          |

| DMA5STA   | 03C0 | ľ      |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |             |       |       |        | 0000          |

| DMA5STB   | 03C2 |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |             |       |       |        | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 6.2 Reset Control Registers

|                 | R/W-0                                             | U-0                                   | U-0           | U-0              | U-0              | R/W-0           | R/W-0         |  |  |  |  |

|-----------------|---------------------------------------------------|---------------------------------------|---------------|------------------|------------------|-----------------|---------------|--|--|--|--|

| TRAPR           | IOPUWR                                            | —                                     | _             | _                | _                | СМ              | VREGS         |  |  |  |  |

| bit 15          |                                                   |                                       |               |                  |                  |                 | bit 8         |  |  |  |  |

|                 |                                                   |                                       |               |                  |                  |                 |               |  |  |  |  |

| R/W-0           | R/W-0                                             | R/W-0                                 | R/W-0         | R/W-0            | R/W-0            | R/W-1           | R/W-1         |  |  |  |  |

| EXTR            | SWR                                               | SWDTEN <sup>(2)</sup>                 | WDTO          | SLEEP            | IDLE             | BOR             | POR           |  |  |  |  |

| bit 7           |                                                   |                                       |               |                  |                  |                 | bit 0         |  |  |  |  |

| Legend:         |                                                   |                                       |               |                  |                  |                 |               |  |  |  |  |

| R = Readable b  | nit                                               | W = Writable b                        | vit           | II = I Inimpler  | mented bit, read | 1 as 'O'        |               |  |  |  |  |

| -n = Value at P |                                                   | '1' = Bit is set                      | Л             | '0' = Bit is cle |                  | x = Bit is unki | nwn           |  |  |  |  |

|                 |                                                   |                                       |               |                  |                  |                 | IOWIT         |  |  |  |  |

| bit 15          | TRAPR: Trap                                       | Reset Flag bit                        |               |                  |                  |                 |               |  |  |  |  |

|                 | •                                                 | onflict Reset has                     | s occurred    |                  |                  |                 |               |  |  |  |  |

|                 |                                                   | onflict Reset has                     |               | d                |                  |                 |               |  |  |  |  |

| bit 14          | IOPUWR: Ille                                      | gal Opcode or l                       | Jninitialized | W Access Rese    | et Flag bit      |                 |               |  |  |  |  |

|                 |                                                   | I opcode detec                        |               | gal address m    | ode or uninitial | ized W registe  | er used as ar |  |  |  |  |

|                 |                                                   | Pointer caused                        |               |                  |                  |                 |               |  |  |  |  |

| h# 40 40        | •                                                 | l opcode or unin                      |               | leset has not o  | ccurrea          |                 |               |  |  |  |  |

| bit 13-10       | -                                                 | ted: Read as '0                       |               |                  |                  |                 |               |  |  |  |  |

| bit 9           | 0                                                 | ation Mismatch<br>ration mismatch     | •             | ocurred          |                  |                 |               |  |  |  |  |

|                 |                                                   | ration mismatch                       |               |                  |                  |                 |               |  |  |  |  |

| bit 8           | VREGS: Voltage Regulator Standby During Sleep bit |                                       |               |                  |                  |                 |               |  |  |  |  |

|                 | 1 = Voltage r                                     | egulator is activ                     | e during Slee | ep               |                  |                 |               |  |  |  |  |

|                 | 0 = Voltage r                                     | egulator goes ir                      | nto Standby r | node during Sl   | еер              |                 |               |  |  |  |  |

| bit 7           |                                                   | XTR: External Reset (MCLR) Pin bit    |               |                  |                  |                 |               |  |  |  |  |

|                 |                                                   | Clear (pin) Res                       |               |                  |                  |                 |               |  |  |  |  |

| <b>h</b> # C    |                                                   | Clear (pin) Res                       |               |                  |                  |                 |               |  |  |  |  |

| bit 6           |                                                   | re Reset (Instru<br>instruction has l | , .           |                  |                  |                 |               |  |  |  |  |

|                 |                                                   | instruction has                       |               |                  |                  |                 |               |  |  |  |  |

| bit 5           |                                                   | oftware Enable/[                      |               |                  |                  |                 |               |  |  |  |  |

|                 | 1 = WDT is e                                      |                                       |               |                  |                  |                 |               |  |  |  |  |

|                 | 0 = WDT is di                                     | isabled                               |               |                  |                  |                 |               |  |  |  |  |

| bit 4           | WDTO: Watc                                        | hdog Timer Tim                        | e-out Flag bi | t                |                  |                 |               |  |  |  |  |

|                 |                                                   | e-out has occurr                      |               |                  |                  |                 |               |  |  |  |  |

|                 |                                                   | e-out has not oc                      |               |                  |                  |                 |               |  |  |  |  |

| bit 3           |                                                   | e-up from Sleep                       | -             |                  |                  |                 |               |  |  |  |  |

|                 |                                                   | as been in Sleep<br>as not been in S  |               |                  |                  |                 |               |  |  |  |  |

| bit 2           |                                                   | up from Idle Flag                     |               |                  |                  |                 |               |  |  |  |  |

|                 |                                                   |                                       | 9 51          |                  |                  |                 |               |  |  |  |  |

|                 | = Device wa                                       | as in Idle mode                       |               |                  |                  |                 |               |  |  |  |  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| U-0                              | R/W-0                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                | U-0                                                                                                                                                         | U-0                 | U-0                   | U-0                               | U-0     |  |  |  |  |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------------------|---------|--|--|--|--|--|--|--|

|                                  | DMA4IE                                                                                                                                                                                                                             | PMPIE                                                                                                                                                                                                                |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

| <br>oit 15                       | DIVIAHIL                                                                                                                                                                                                                           |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   | bit     |  |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   | DIL     |  |  |  |  |  |  |  |

| U-0                              | U-0                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                  | R/W-0                                                                                                                                                       | R/W-0               | R/W-0                 | R/W-0                             | R/W-0   |  |  |  |  |  |  |  |

| _                                |                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                    | DMA3IE                                                                                                                                                      | C1IE <sup>(1)</sup> | C1RXIE <sup>(1)</sup> | SPI2IE                            | SPI2EIE |  |  |  |  |  |  |  |

| bit 7                            |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   | bit     |  |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

| Legend:                          |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

| R = Readab                       |                                                                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                         |                                                                                                                                                             | •                   | nented bit, read      |                                   |         |  |  |  |  |  |  |  |

| -n = Value a                     | it POR                                                                                                                                                                                                                             | '1' = Bit is se                                                                                                                                                                                                      | t                                                                                                                                                           | '0' = Bit is cle    | ared                  | x = Bit is unkr                   | nown    |  |  |  |  |  |  |  |

| L:4 / F                          |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

| bit 15                           | -                                                                                                                                                                                                                                  | ted: Read as                                                                                                                                                                                                         |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

| bit 14                           | DMA4IE: DMA Channel 4 Data Transfer Complete Interrupt Enable bit                                                                                                                                                                  |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

|                                  | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                                                                                                                                                 |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

|                                  | •                                                                                                                                                                                                                                  | •                                                                                                                                                                                                                    |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

| bit 13                           | PMPIE: Parallel Master Port Interrupt Enable bit                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

|                                  | 1 = Interrupt request enabled                                                                                                                                                                                                      |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

|                                  |                                                                                                                                                                                                                                    | •                                                                                                                                                                                                                    | abled                                                                                                                                                       |                     |                       | 0 = Interrupt request not enabled |         |  |  |  |  |  |  |  |

|                                  | Unimplemented: Read as '0'                                                                                                                                                                                                         |                                                                                                                                                                                                                      |                                                                                                                                                             |                     |                       |                                   |         |  |  |  |  |  |  |  |

| bit 12-5                         | Unimplemen                                                                                                                                                                                                                         | ted: Read as                                                                                                                                                                                                         | ʻ0 <b>'</b>                                                                                                                                                 |                     |                       |                                   |         |  |  |  |  |  |  |  |

| bit 12-5<br>bit 4                | •                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      | '0'<br>Data Transfer C                                                                                                                                      | complete Interr     | upt Enable bit        |                                   |         |  |  |  |  |  |  |  |

|                                  | DMA3IE: DM                                                                                                                                                                                                                         |                                                                                                                                                                                                                      | ata Transfer C                                                                                                                                              | complete Interr     | upt Enable bit        |                                   |         |  |  |  |  |  |  |  |

|                                  | <b>DMA3IE:</b> DM<br>1 = Interrupt                                                                                                                                                                                                 | IA Channel 3 E                                                                                                                                                                                                       | oata Transfer C<br>d                                                                                                                                        | Complete Interr     | upt Enable bit        |                                   |         |  |  |  |  |  |  |  |

| bit 4                            | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt                                                                                                                                                                                | IA Channel 3 E<br>request enable<br>request has er                                                                                                                                                                   | oata Transfer C<br>d                                                                                                                                        |                     | upt Enable bit        |                                   |         |  |  |  |  |  |  |  |

| bit 4                            | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt<br><b>C1IE:</b> ECAN                                                                                                                                                           | IA Channel 3 E<br>request enable<br>request has er                                                                                                                                                                   | Data Transfer C<br>ed<br>habled<br>pt Enable bit <sup>(1)</sup>                                                                                             |                     | rupt Enable bit       |                                   |         |  |  |  |  |  |  |  |

| bit 4                            | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt<br><b>C1IE:</b> ECAN<br>1 = Interrupt                                                                                                                                          | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru                                                                                                                                                | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed                                                                                       |                     | rupt Enable bit       |                                   |         |  |  |  |  |  |  |  |

|                                  | <b>DMA3IE:</b> DM<br>1 = Interrupt<br>0 = Interrupt<br><b>C1IE:</b> ECAN<br>1 = Interrupt<br>0 = Interrupt                                                                                                                         | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en                                                                                                            | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed                                                                                       | )                   |                       |                                   |         |  |  |  |  |  |  |  |

| bit 4                            | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: ECA                                                                                                                        | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en                                                                                                            | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte                                                           | )                   |                       |                                   |         |  |  |  |  |  |  |  |

| bit 4                            | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: ECA<br>1 = Interrupt                                                                                                       | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E                                                                                           | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte                                                           | )                   |                       |                                   |         |  |  |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2          | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt                                                                   | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable                                                                         | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled                                            | )                   |                       |                                   |         |  |  |  |  |  |  |  |

| bit 4                            | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: EC/<br>1 = Interrupt<br>0 = Interrupt<br>SPI2IE: SPI2                                                                      | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en                                                       | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled<br>bit Enable bit                          | )                   |                       |                                   |         |  |  |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2          | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: EC/<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en                                                       | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled<br>ot Enable bit<br>ed                     | )                   |                       |                                   |         |  |  |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2<br>bit 1 | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>C1IE: ECAN<br>1 = Interrupt<br>0 = Interrupt<br>C1RXIE: ECA<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>0 = Interrupt                  | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en<br>2 Event Interrup<br>request enable                 | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>ed<br>abled<br>ot Enable bit<br>ed<br>abled            | )                   |                       |                                   |         |  |  |  |  |  |  |  |

| bit 4<br>bit 3<br>bit 2          | DMA3IE: DM<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>0 = Interrupt<br>SPI2IE: SPI2<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>0 = Interrupt              | IA Channel 3 E<br>request enable<br>request has er<br>1 Event Interru<br>request enable<br>request not en<br>AN1 Receive E<br>request enable<br>request not en<br>Event Interrup<br>request enable<br>request not en | Data Transfer C<br>ed<br>labled<br>pt Enable bit <sup>(1)</sup><br>ed<br>abled<br>Data Ready Inte<br>abled<br>ot Enable bit<br>ed<br>abled<br>pt Enable bit | )                   |                       |                                   |         |  |  |  |  |  |  |  |

#### 7 4 2 ---

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

| U-0                    | R/W-1                                                        | R/W-0                                   | R/W-0          | U-0              | R/W-1            | R/W-0            | R/W-0   |  |  |  |  |  |  |

|------------------------|--------------------------------------------------------------|-----------------------------------------|----------------|------------------|------------------|------------------|---------|--|--|--|--|--|--|

| _                      |                                                              | T4IP<2:0>                               |                | —                |                  | OC4IP<2:0>       |         |  |  |  |  |  |  |

| bit 15                 |                                                              |                                         |                |                  |                  |                  | bit     |  |  |  |  |  |  |

| U-0                    | R/W-1                                                        | R/W-0                                   | R/W-0          | U-0              | R/W-1            | R/W-0            | R/W-0   |  |  |  |  |  |  |

|                        | N/W-1                                                        | OC3IP<2:0>                              | N/W-0          |                  | N/W-1            | DMA2IP<2:0>      | N/ VV-U |  |  |  |  |  |  |

| bit 7                  |                                                              |                                         |                |                  |                  |                  | bit (   |  |  |  |  |  |  |

| Logondi                |                                                              |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

| Legend:<br>R = Readabl | le bit                                                       | W = Writable t                          | oit            | U = Unimple      | mented bit, rea  | ad as '0'        |         |  |  |  |  |  |  |

| -n = Value at          |                                                              | '1' = Bit is set                        |                | '0' = Bit is cle |                  | x = Bit is unkno | own     |  |  |  |  |  |  |

|                        |                                                              |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

| bit 15                 | Unimpleme                                                    | ented: Read as '0                       | )'             |                  |                  |                  |         |  |  |  |  |  |  |

| bit 14-12              | T4IP<2:0>: Timer4 Interrupt Priority bits                    |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | 111 = Interr                                                 | upt is priority 7 (h                    | nighest priori | ity interrupt)   |                  |                  |         |  |  |  |  |  |  |

|                        | •                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | •                                                            | •                                       |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | 001 = Interrupt is priority 1                                |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | 000 <b>= Interr</b>                                          | upt source is disa                      | abled          |                  |                  |                  |         |  |  |  |  |  |  |

| bit 11                 | Unimpleme                                                    | ented: Read as '0                       | )'             |                  |                  |                  |         |  |  |  |  |  |  |

| bit 10-8               | OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | 111 = Interr                                                 | rupt is priority 7 (h                   | nighest priori | ity interrupt)   |                  |                  |         |  |  |  |  |  |  |

|                        | •                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | •                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        |                                                              | upt is priority 1                       |                |                  |                  |                  |         |  |  |  |  |  |  |

| L:1 7                  |                                                              | upt source is disa                      |                |                  |                  |                  |         |  |  |  |  |  |  |

| bit 7                  | -                                                            | ented: Read as '0                       |                |                  |                  |                  |         |  |  |  |  |  |  |

| bit 6-4                |                                                              | : Output Compa<br>upt is priority 7 (h  |                |                  | ity bits         |                  |         |  |  |  |  |  |  |

|                        | •                                                            | upt is phonity 7 (i                     | lighest priori | ity interrupt)   |                  |                  |         |  |  |  |  |  |  |

|                        | •                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | •                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        |                                                              | upt is priority 1<br>upt source is disa | abled          |                  |                  |                  |         |  |  |  |  |  |  |

| bit 3                  |                                                              | ented: Read as '0                       |                |                  |                  |                  |         |  |  |  |  |  |  |

| bit 2-0                | -                                                            | 0>: DMA Channe                          |                | unsfer Complete  | e Interrupt Prio | ritv bits        |         |  |  |  |  |  |  |

|                        |                                                              | rupt is priority 7 (h                   |                |                  |                  | ,                |         |  |  |  |  |  |  |

|                        | •                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | •                                                            |                                         |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        | •<br>001 = Interr                                            | upt is priority 1                       |                |                  |                  |                  |         |  |  |  |  |  |  |

|                        |                                                              | upt source is disa                      |                |                  |                  |                  |         |  |  |  |  |  |  |

#### DECISTED 7-21. IDCA- INTERDURT DRIOPITY CONTROL DECISTER A

NOTES:

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| U-0                | U-0                                                  | U-0                                                                                                      | R/W-1         | R/W-1           | R/W-1            | R/W-1           | R/W-1 |  |  |  |  |  |

|--------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------|-----------------|------------------|-----------------|-------|--|--|--|--|--|

| —                  |                                                      | _                                                                                                        |               |                 | U1CTSR<4:0       | >               |       |  |  |  |  |  |

| bit 15             |                                                      |                                                                                                          |               |                 |                  |                 | bit 8 |  |  |  |  |  |

|                    |                                                      |                                                                                                          | <b>D</b> 44/4 |                 |                  | D 44/4          |       |  |  |  |  |  |

| U-0                | U-0                                                  | U-0                                                                                                      | R/W-1         | R/W-1           | R/W-1            | R/W-1           | R/W-1 |  |  |  |  |  |

| -:+ 7              | _                                                    | —                                                                                                        |               |                 | U1RXR<4:0>       | •               | h:+ 0 |  |  |  |  |  |

| bit 7              |                                                      |                                                                                                          |               |                 |                  |                 | bit C |  |  |  |  |  |

| Legend:            |                                                      |                                                                                                          |               |                 |                  |                 |       |  |  |  |  |  |

| R = Readab         | le bit                                               | W = Writable                                                                                             | oit           | U = Unimplen    | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value a       | t POR                                                | '1' = Bit is set                                                                                         | •             |                 |                  | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15-13          | Unimpleme                                            | nted: Read as '                                                                                          | )'            |                 |                  |                 |       |  |  |  |  |  |

| bit 12-8           | -                                                    | <b>U1CTSR&lt;4:0&gt;:</b> Assign UART1 Clear to Send ( $\overline{U1CTS}$ ) to the corresponding RPn pin |               |                 |                  |                 |       |  |  |  |  |  |

|                    |                                                      | 11111 = Input tied to Vss                                                                                |               |                 |                  |                 |       |  |  |  |  |  |

|                    |                                                      | ut tied to RP25                                                                                          |               |                 |                  |                 |       |  |  |  |  |  |

|                    | •                                                    |                                                                                                          |               |                 |                  |                 |       |  |  |  |  |  |

|                    | •                                                    |                                                                                                          |               |                 |                  |                 |       |  |  |  |  |  |

|                    |                                                      |                                                                                                          |               |                 |                  |                 |       |  |  |  |  |  |

|                    | •                                                    |                                                                                                          |               |                 |                  |                 |       |  |  |  |  |  |

|                    |                                                      | ut tied to RP1<br>ut tied to RP0                                                                         |               |                 |                  |                 |       |  |  |  |  |  |

| oit 7-5            | 00000 <b>= Inp</b>                                   |                                                                                                          | )'            |                 |                  |                 |       |  |  |  |  |  |

|                    | 00000 = Inp<br>Unimpleme                             | ut tied to RP0                                                                                           |               | 1RX) to the cor | responding RF    | n pin           |       |  |  |  |  |  |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(                                                                       |               | 1RX) to the cor | responding RF    | n pin           |       |  |  |  |  |  |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss                                   |               | 1RX) to the cor | responding RF    | 'n pin          |       |  |  |  |  |  |

| bit 7-5<br>bit 4-0 | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss                                   |               | 1RX) to the cor | responding RF    | 'n pin          |       |  |  |  |  |  |

# REGISTER 11-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

00001 = Input tied to RP1 00000 = Input tied to RP0

# 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                          |

|       | Devices.aspx?dDocName=en532311                                                                                 |

## 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# BUFFER 19-7: ECAN™ MESSAGE BUFFER WORD 6

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x                              | R/W-x           | R/W-x              | R/W-x |  |  |

|------------------------------------|-------|-------|------------------|------------------------------------|-----------------|--------------------|-------|--|--|

|                                    |       |       | Ву               | rte 7                              |                 |                    |       |  |  |

| bit 15                             |       |       |                  |                                    |                 |                    | bit 8 |  |  |

|                                    |       |       |                  |                                    |                 |                    |       |  |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x                              | R/W-x           | R/W-x              | R/W-x |  |  |

|                                    |       |       | Ву               | rte 6                              |                 |                    |       |  |  |

| bit 7                              |       |       |                  |                                    |                 |                    | bit 0 |  |  |

| Legend:                            |       |       |                  |                                    |                 |                    |       |  |  |

| R = Readable bit W = Writable bit  |       |       |                  | U = Unimplemented bit, read as '0' |                 |                    |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared                               | x = Bit is unkr | x = Bit is unknown |       |  |  |

bit 15-8 Byte 7<15:8>: ECAN™ Message Byte 7

bit 7-0 Byte 6<7:0>: ECAN Message Byte 6

### BUFFER 19-8: ECAN™ MESSAGE BUFFER WORD 7

| U-0                                | U-0 | U-0            | R/W-x                                   | R/W-x        | R/W-x            | R/W-x    | R/W-x |  |  |  |

|------------------------------------|-----|----------------|-----------------------------------------|--------------|------------------|----------|-------|--|--|--|

| _                                  | _   | _              | FILHIT<4:0> <sup>(1)</sup>              |              |                  |          |       |  |  |  |

| bit 15                             |     |                |                                         |              |                  |          | bit 8 |  |  |  |

|                                    |     |                |                                         |              |                  |          |       |  |  |  |

| U-0                                | U-0 | U-0            | U-0                                     | U-0          | U-0              | U-0      | U-0   |  |  |  |

| —                                  | —   |                | —                                       |              | —                | _        | —     |  |  |  |

| bit 7                              |     |                |                                         |              |                  |          | bit 0 |  |  |  |

| Legend:                            |     |                |                                         |              |                  |          |       |  |  |  |

| R = Readable b                     | bit | W = Writable I | oit                                     | U = Unimpler | mented bit, read | d as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set |     |                | '0' = Bit is cleared x = Bit is unknown |              |                  |          |       |  |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits<sup>(1)</sup>

Encodes number of filter that resulted in writing this buffer.

bit 7-0 Unimplemented: Read as '0'

Note 1: These bits are only written by the module for receive buffers, and are unused for transmit buffers.

| REGISTER   | R 21-3: AD1C0                     | ON3: ADC1 C                                                |                 | EGISTER 3            |                 |                 |       |  |  |  |  |  |

|------------|-----------------------------------|------------------------------------------------------------|-----------------|----------------------|-----------------|-----------------|-------|--|--|--|--|--|

| R/W-0      | U-0                               | U-0                                                        | R/W-0           | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

| ADRC       |                                   |                                                            |                 |                      | SAMC<4:0>(      | 1)              |       |  |  |  |  |  |

| bit 15     |                                   |                                                            |                 |                      |                 |                 | bit   |  |  |  |  |  |

| R/W-0      | R/W-0                             | R/W-0                                                      | R/W-0           | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|            |                                   |                                                            | ADCS<           | :7:0> <sup>(2)</sup> |                 |                 |       |  |  |  |  |  |

| bit 7      |                                   |                                                            |                 |                      |                 |                 | bit   |  |  |  |  |  |

| Legend:    |                                   |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

| R = Reada  | ble bit                           | W = Writable b                                             | oit             | U = Unimpler         | nented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value | n = Value at POR '1' = Bit is set |                                                            |                 | '0' = Bit is cle     | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15     |                                   | Conversion Clo                                             | ck Source bit   |                      |                 |                 |       |  |  |  |  |  |

|            | 1 = ADC inter<br>0 = Clock der    | nal RC clock<br>ived from syste                            | m clock         |                      |                 |                 |       |  |  |  |  |  |

| bit 14-13  |                                   | ted: Read as '0                                            |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 12-8   |                                   | SAMC<4:0>: Auto Sample Time bits <sup>(1)</sup>            |                 |                      |                 |                 |       |  |  |  |  |  |

| 511 12 0   | 11111 = <b>31</b> T               | -                                                          |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | 00001 <b>= 1 T</b> A              |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

| h:+ 7 0    |                                   | 00000 = 0 TAD                                              |                 |                      |                 |                 |       |  |  |  |  |  |

| bit 7-0    |                                   | ADCS<7:0>: ADC Conversion Clock Select bits <sup>(2)</sup> |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 | 11111111 = Reserved                                        |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | 01000000 =                        | Reserved                                                   |                 |                      |                 |                 |       |  |  |  |  |  |

|            |                                   | TCY · (ADCS<7                                              | 7:0> + 1) = 64  | • Tcy = Tad          |                 |                 |       |  |  |  |  |  |

|            | •                                 | - (                                                        | , -             |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | •                                 |                                                            |                 |                      |                 |                 |       |  |  |  |  |  |

|            | 00000010 =                        | TCY · (ADCS<7                                              | 7:0> + 1) = 3 · | TCY = TAD            |                 |                 |       |  |  |  |  |  |

|            |                                   | Тсү · (ADCS<7<br>Тсү · (ADCS<7                             |                 |                      |                 |                 |       |  |  |  |  |  |

| Note 1:    | This bit only used i              | f AD1CON1<7:                                               | 5> (SSRC<2:     | <b>0&gt;) =</b> 111. |                 |                 |       |  |  |  |  |  |

|            | This bit is not used              |                                                            |                 | ,                    |                 |                 |       |  |  |  |  |  |

#### 40010

# 23.1 Comparator Resources

Many useful resources related to Comparators are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en532311                                        |

#### 23.1.1 KEY RESOURCES

- Section 34. "Comparator" (DS70212)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# **REGISTER 24-10:** ALRMVAL (WHEN ALRMPTR<1:0> = 00): ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0     | R/W-x | R/W-x       | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x |  |

|---------|-------|-------------|-------|-------------|-------|-------|-------|--|

| —       |       | MINTEN<2:0> |       | MINONE<3:0> |       |       |       |  |