#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp202-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | This bit is used for signed arithmetic (two's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                 |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                 |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                |

- Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

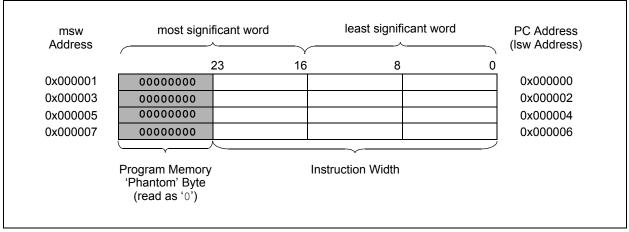

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table**".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|-----------------|-------|------------------|-------|--------------|-----------------|----------|-------|

|                 |       |                  | PAD   | <15:8>       |                 |          |       |

| bit 15          |       |                  |       |              |                 |          | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                 |       |                  | PAD   | )<7:0>       |                 |          |       |

| bit 7           |       |                  |       |              |                 |          | bit 0 |

| Legend:         |       |                  |       |              |                 |          |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler | nented bit, rea | d as '0' |       |

| -n = Value at P |       | '1' = Bit is set | •     |              |                 | nown     |       |

# **REGISTER 8-5:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0   | U-0   | U-0   | U-0                 | U-0   | R/W-0 | R/W-0           |

|--------|-------|-------|-------|---------------------|-------|-------|-----------------|

| _      | —     | _     | —     | _                   | _     | CNT<  | 9:8> <b>(2)</b> |

| bit 15 |       |       |       |                     |       |       | bit 8           |

|        |       |       |       |                     |       |       |                 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0           |

|        |       |       | CNT<  | 7:0> <sup>(2)</sup> |       |       |                 |

| bit 7  |       |       |       |                     |       |       | bit 0           |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

| REGISTER     | R 9-3: PLLFE | BD: PLL FEE      | DBACK DIV                           | ISOR REGIS    | STER "           |                |           |  |  |

|--------------|--------------|------------------|-------------------------------------|---------------|------------------|----------------|-----------|--|--|

| U-0          | U-0          | U-0              | U-0                                 | U-0           | U-0              | U-0            | R/W-0     |  |  |

|              | —            | _                | _                                   | —             | —                | _              | PLLDIV<8> |  |  |

| bit 15       |              |                  |                                     |               |                  |                | bit 8     |  |  |

| R/W-0        | D/M/ O       |                  |                                     | R/W-0         | R/W-0            | R/W-0          |           |  |  |

| R/W-U        | R/W-0        | R/W-1            | R/W-1                               |               | R/W-U            | R/W-U          | R/W-0     |  |  |

|              |              |                  | PLLD                                | IV<7:0>       |                  |                |           |  |  |

| bit 7        |              |                  |                                     |               |                  |                | bit C     |  |  |

|              |              |                  |                                     |               |                  |                |           |  |  |

| Legend:      |              |                  |                                     |               |                  |                |           |  |  |

| R = Readab   | ole bit      | W = Writable     | bit                                 | U = Unimpler  | mented bit, read | l as '0'       |           |  |  |

| -n = Value a | at POR       | '1' = Bit is set | t '0' = Bit is cleared x = Bit is u |               |                  | x = Bit is unl | known     |  |  |

|              |              |                  |                                     |               |                  |                |           |  |  |

| bit 15-9     | Unimplemen   | ted: Read as '   | 0'                                  |               |                  |                |           |  |  |

| bit 8-0      | PLLDIV<8:0>  | >: PLL Feedba    | ck Divisor bits                     | (also denoted | as 'M', PLL mu   | ltiplier)      |           |  |  |

|              | 111111111    | = 513            |                                     |               |                  |                |           |  |  |

|              | •            |                  |                                     |               |                  |                |           |  |  |

|              | •            |                  |                                     |               |                  |                |           |  |  |

|              | •            |                  |                                     |               |                  |                |           |  |  |

|              | 000110000=   | = 50 (default)   |                                     |               |                  |                |           |  |  |

|              | •            |                  |                                     |               |                  |                |           |  |  |

|              | •            |                  |                                     |               |                  |                |           |  |  |

|              | •            |                  |                                     |               |                  |                |           |  |  |

|              | 000000010 =  |                  |                                     |               |                  |                |           |  |  |

#### REGISTER 9-3-PLLEBD PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

00000001 = 3 000000000 = 2

Note 1: This register is reset only on a Power-on Reset (POR).

| REGISTERS     | 9-5: ACLI                    |                                         | ARY CONT     | ROL REGIST       | ER               |                 |       |

|---------------|------------------------------|-----------------------------------------|--------------|------------------|------------------|-----------------|-------|

| U-0           | U-0                          | R/W-0                                   | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| _             | _                            | SELACLK                                 | AOSC         | MD<1:0>          | A                | PSTSCLR<2:0>    | >     |

| bit 15        |                              |                                         |              |                  |                  |                 | bit 8 |

| R/W-0         | U-0                          | U-0                                     | U-0          | U-0              | U-0              | U-0             | U-0   |

| ASRCSEL       | 0-0                          | 0-0                                     | 0-0          | 0-0              | 0-0              | 0-0             | 0-0   |

| bit 7         | _                            | —                                       |              |                  |                  | —               | bit   |

|               |                              |                                         |              |                  |                  |                 | DIL   |

| Legend:       |                              |                                         |              |                  |                  |                 |       |

| R = Readable  | e bit                        | W = Writable I                          | oit          | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at | POR                          | '1' = Bit is set                        |              | '0' = Bit is cle | ared             | x = Bit is unkn | iown  |

|               |                              |                                         |              |                  |                  |                 |       |

| bit 15-14     | Unimpleme                    | ented: Read as '0                       | )'           |                  |                  |                 |       |

| bit 13        | SELACLK:                     | Select Auxiliary                        | Clock Source | for Auxiliary C  | lock Divider     |                 |       |

|               | •                            | y Oscillators prov<br>put (Fosc) provid |              |                  | •                |                 |       |

| bit 12-11     |                              | 1:0>: Auxiliary Os                      |              |                  |                  | Difficien       |       |

|               |                              | ternal Clock Mod                        |              |                  |                  |                 |       |

|               | 10 = XT Os                   | cillator Mode Sel                       | ect          |                  |                  |                 |       |

|               |                              | cillator Mode Sel                       |              |                  |                  |                 |       |

|               |                              | ry Oscillator Disa                      |              | <b>D</b>         |                  |                 |       |

| bit 10-8      |                              | R<2:0>: Auxiliary                       | Clock Output | Divider          |                  |                 |       |

|               | 111 = divide<br>110 = divide |                                         |              |                  |                  |                 |       |

|               | 101 = divide                 | •                                       |              |                  |                  |                 |       |

|               | 100 <b>= divide</b>          | •                                       |              |                  |                  |                 |       |

|               | 011 = divide                 |                                         |              |                  |                  |                 |       |

|               | 010 = divide                 | •                                       |              |                  |                  |                 |       |

|               | 001 = divide                 | ed by 64<br>ed by 256 (defaul           | t)           |                  |                  |                 |       |

| bit 7         |                              | Select Reference                        | ,            | e for Auxiliary  | Clock            |                 |       |

| ~             |                              | Oscillator is the                       |              | •                | 0.001            |                 |       |

|               |                              | y Oscillator is the                     |              |                  |                  |                 |       |

|               | -                            |                                         |              |                  |                  |                 |       |

# REGISTER 9-5: ACLKCON: AUXILIARY CONTROL REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

Unimplemented: Read as '0'

bit 6-0

# 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 devices can manage power consumption in four ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- · Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 10.1 Clock Frequency and Clock Switching

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 9.0 "Oscillator Configuration".

## 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake up.

# 10.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode PWRSAV #IDLE MODE ; Put the device into IDLE mode

| -n = Value at POR '1' = Bit is set |     |                                        | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |       |

|------------------------------------|-----|----------------------------------------|------------------|-------|-----------------|-------|-------|

| R = Readable bit W = Writable b    |     | bit U = Unimplemented bit, read as '0' |                  |       |                 |       |       |

| Legend:                            |     |                                        |                  |       |                 |       |       |

|                                    |     |                                        |                  |       |                 |       |       |

| bit 7                              |     |                                        |                  |       |                 |       | bit   |

| —                                  | _   | —                                      |                  |       | RP24R<4:0       | >     |       |

| U-0                                | U-0 | U-0                                    | R/W-0            | R/W-0 | R/W-0           | R/W-0 | R/W-0 |

|                                    |     |                                        |                  |       |                 |       |       |

| bit 15                             |     |                                        |                  |       |                 |       | bit   |

|                                    | —   |                                        |                  |       | RP25R<4:0       | >     |       |

| U-0                                | U-0 | U-0                                    | R/W-0            | R/W-0 | R/W-0           | R/W-0 | R/W-0 |

# REGISTER 11-29: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 **RP25R<4:0>:** Peripheral Output Function is Assigned to RP25 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 **RP24R<4:0>:** Peripheral Output Function is Assigned to RP24 Output Pin bits (see Table 11-2 for peripheral function numbers)

Note 1: This register is implemented in 44-pin devices only.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER 1   | EGISTER 19-24: CIRXOVF1: ECAN III RECEIVE BUFFER OVERFLOW REGISTER 1 |                |                   |                |                    |        |        |  |

|--------------|----------------------------------------------------------------------|----------------|-------------------|----------------|--------------------|--------|--------|--|

| R/C-0        | R/C-0                                                                | R/C-0          | R/C-0             | R/C-0          | R/C-0              | R/C-0  | R/C-0  |  |

| RXOVF15      | RXOVF14                                                              | RXOVF13        | RXOVF12           | RXOVF11        | RXOVF10            | RXOVF9 | RXOVF8 |  |

| bit 15       |                                                                      |                |                   |                |                    |        | bit 8  |  |

|              |                                                                      |                |                   |                |                    |        |        |  |

| R/C-0        | R/C-0                                                                | R/C-0          | R/C-0             | R/C-0          | R/C-0              | R/C-0  | R/C-0  |  |

| RXOVF7       | RXOVF6                                                               | RXOVF5         | RXOVF4            | RXOVF3         | RXOVF2             | RXOVF1 | RXOVF0 |  |

| bit 7        |                                                                      |                |                   |                |                    |        | bit 0  |  |

|              |                                                                      |                |                   |                |                    |        |        |  |

| Legend:      |                                                                      | C = Writable b | oit, but only '0' | can be writter | n to clear the bit |        |        |  |

| R = Readable | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                |                   |                |                    |        |        |  |

'0' = Bit is cleared

x = Bit is unknown

# DECIOTED 40.04. CODVOVE4. FOANIM DECENCE DUFFED OVEDELOW DECIOTED 4

bit 15-0

-n = Value at POR

RXOVF<15:0>: Receive Buffer n Overflow bits

'1' = Bit is set

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition

# REGISTER 19-25: CIRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-0

RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition

# REGISTER 20-3: DCICON3: DCI CONTROL REGISTER 3

| U-0                                | U-0   | U-0   | U-0                                     | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|------------------------------------|-------|-------|-----------------------------------------|------------------------------------|-------|--------|-------|--|

| _                                  | _     | _     | _                                       |                                    | BCG   | <11:8> |       |  |

| bit 15                             |       |       |                                         |                                    |       |        | bit 8 |  |

| [                                  |       |       |                                         |                                    |       |        |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    |       |       | BCC                                     | 6<7:0>                             |       |        |       |  |

| bit 7                              |       |       |                                         |                                    |       |        | bit 0 |  |

|                                    |       |       |                                         |                                    |       |        |       |  |

| Legend:                            |       |       |                                         |                                    |       |        |       |  |

| R = Readable bit W = Writable bit  |       |       | bit                                     | U = Unimplemented bit, read as '0' |       |        |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |        |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 BCG<11:0>: DCI Bit Clock Generator Control bits

# 21.6 ADC Control Registers

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0     | R/W-0  |  |

|--------|-----------|--------|---------|--------|-------|-----------|--------|--|

| ADON   | —         | ADSIDL | ADDMABM |        | AD12B | FORM<1:0> |        |  |

| bit 15 |           |        |         |        |       |           | bit 8  |  |

|        |           |        |         |        |       |           |        |  |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0     | R/C-0  |  |

|        |           |        |         |        |       | HC,HS     | HC, HS |  |

|        | SSRC<2:0> |        | —       | SIMSAM | ASAM  | SAMP      | DONE   |  |

# REGISTER 21-1: AD1CON1: ADC1 CONTROL REGISTER 1

| L :1  | - |

|-------|---|

| T III |   |

| DIL   |   |

| Legend: HC = Cleared by hardware   |  | HS = Set by hardware               | C = Clear only bit |  |  |

|------------------------------------|--|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit  |  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR (1' = Bit is set |  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15  | ADON: ADC Operating Mode bit<br>1 = ADC module is operating                                                                                                                                                                                                                                                                                                                                               |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = ADC is off                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 13  | <ul> <li>ADSIDL: Stop in Idle Mode bit</li> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                                                                              |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = DMA buffers are written in the order of conversion. The module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer</li> <li>0 = DMA buffers are written in Scatter/Gather mode. The module provides a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 10  | AD12B: 10-bit or 12-bit Operation Mode bit                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = 12-bit, 1-channel ADC operation</li> <li>0 = 10-bit, 4-channel ADC operation</li> </ul>                                                                                                                                                                                                                                                                                                      |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                                                                                                                                                                                                                        |

|         | For 10-bit operation:<br>11 = Signed fractional (Dout = sddd dddd dd00 0000, where s =.NOT.d<9>)<br>10 = Fractional (Dout = dddd dddd dd00 0000)<br>01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                                                                    |

|         | For 12-bit operation:                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)                                                                                                                                                                                                                                                                                                                                 |

|         | 10 = Fractional (Douт = dddd dddd dddd 0000)<br>01 = Signed Integer (Douт = ssss sddd dddd dddd, where s = .NOT.d<11>)                                                                                                                                                                                                                                                                                    |

|         | 00 = Integer (Dout = 0000  ddd  dddd  dddd)                                                                                                                                                                                                                                                                                                                                                               |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>111 = Internal counter ends sampling and starts conversion (auto-convert)</li> <li>110 = Reserved</li> <li>101 = Reserved</li> </ul>                                                                                                                                                                                                                                                             |

|         | 100 = GP timer (Timer5 for ADC1) compare ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                              |

|         | 011 = Reserved<br>010 = GP timer (Timer3 for ADC1) compare ends sampling and starts conversion                                                                                                                                                                                                                                                                                                            |

|         | 001 = Active transition on INT0 pin ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                   |

|         | 000 = Clearing sample bit ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                             |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                           |

bit 0

# 24.3 RTCC Registers

|                      | U-0                                                                                                                                                                                   | R/W-0                        | R-0            | R-0                    | R/W-0           | R/W-0            | R/W-0         |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|------------------------|-----------------|------------------|---------------|--|--|--|

| RTCEN <sup>(2)</sup> | _                                                                                                                                                                                     | RTCWREN                      | RTCSYNC        | HALFSEC <sup>(3)</sup> | RTCOE           | RTCPT            | R<1:0>        |  |  |  |

| bit 15               |                                                                                                                                                                                       |                              |                |                        |                 |                  | bit           |  |  |  |

| R/W-0                | R/W-0                                                                                                                                                                                 | R/W-0                        | R/W-0          | R/W-0                  | R/W-0           | R/W-0            | R/W-0         |  |  |  |

|                      |                                                                                                                                                                                       |                              | CAL            | <7:0>                  |                 |                  |               |  |  |  |

| bit 7                |                                                                                                                                                                                       |                              |                |                        |                 |                  | bit           |  |  |  |

| Legend:              |                                                                                                                                                                                       |                              |                |                        |                 |                  |               |  |  |  |

| R = Readable         | bit                                                                                                                                                                                   | W = Writable                 | bit            | U = Unimpleme          | ented bit, read | as '0'           |               |  |  |  |

| -n = Value at F      | POR                                                                                                                                                                                   | '1' = Bit is set             |                | '0' = Bit is clear     | red             | x = Bit is unkn  | own           |  |  |  |

| bit 15               |                                                                                                                                                                                       | CC Enable bit <sup>(2)</sup> |                |                        |                 |                  |               |  |  |  |

|                      |                                                                                                                                                                                       | odule is enable              |                |                        |                 |                  |               |  |  |  |

|                      |                                                                                                                                                                                       | odule is disable             |                |                        |                 |                  |               |  |  |  |

| bit 14               | Unimplemer                                                                                                                                                                            | ted: Read as '               | )'             |                        |                 |                  |               |  |  |  |

| bit 13               | RTCWREN:                                                                                                                                                                              | RTCC Value Re                | egisters Write | Enable bit             |                 |                  |               |  |  |  |

|                      | 1 = RTCVAL                                                                                                                                                                            | H and RTCVAL                 | L registers ca | n be written to b      | y the user      |                  |               |  |  |  |

|                      | 0 = RTCVAL                                                                                                                                                                            | H and RTCVAL                 | L registers ar | e locked out fror      | n being writter | n to by the user |               |  |  |  |

| bit 12               | RTCSYNC: RTCC Value Registers Read Synchronization bit                                                                                                                                |                              |                |                        |                 |                  |               |  |  |  |

|                      | 1 = RTCVALH, RTCVALL and ALCFGRPT registers can change while reading due to a rollover ripple                                                                                         |                              |                |                        |                 |                  |               |  |  |  |

|                      | resulting in an invalid data read. If the register is read twice and results in the same data, the data<br>can be assumed to be valid.                                                |                              |                |                        |                 |                  |               |  |  |  |

|                      |                                                                                                                                                                                       |                              |                | registers can be       | read without of | concern over a   | rollover ripp |  |  |  |

| bit 11               |                                                                                                                                                                                       | alf-Second Sta               |                | C                      |                 |                  |               |  |  |  |

|                      | 1 = Second half period of a second                                                                                                                                                    |                              |                |                        |                 |                  |               |  |  |  |

|                      | 0 = First half                                                                                                                                                                        | period of a sec              | ond            |                        |                 |                  |               |  |  |  |

| bit 10               | RTCOE: RTCC Output Enable bit                                                                                                                                                         |                              |                |                        |                 |                  |               |  |  |  |

|                      | <ul> <li>1 = RTCC output enabled</li> <li>0 = RTCC output disabled</li> </ul>                                                                                                         |                              |                |                        |                 |                  |               |  |  |  |

| L:1 0 0              |                                                                                                                                                                                       | •                            |                | - dave Dainstan bita   |                 |                  |               |  |  |  |

| bit 9-8              | RTCPTR<1:0>: RTCC Value Register Window Pointer bits                                                                                                                                  |                              |                |                        |                 |                  |               |  |  |  |

|                      | Points to the corresponding RTCC Value registers when reading RTCVALH and RTCVALL registers the RTCPTR<1:0> value decrements on every read or write of RTCVALH until it reaches '00'. |                              |                |                        |                 |                  |               |  |  |  |

|                      | RTCVAL<15:                                                                                                                                                                            |                              |                | 2                      |                 |                  |               |  |  |  |

|                      | 00 <b>= MINUTE</b>                                                                                                                                                                    |                              |                |                        |                 |                  |               |  |  |  |

|                      | 01 = WEEKD<br>10 = MONTH                                                                                                                                                              |                              |                |                        |                 |                  |               |  |  |  |

|                      | 11 = Reserve                                                                                                                                                                          |                              |                |                        |                 |                  |               |  |  |  |

|                      | RTCVAL<7:0                                                                                                                                                                            |                              |                |                        |                 |                  |               |  |  |  |

|                      | 00 = SECON                                                                                                                                                                            |                              |                |                        |                 |                  |               |  |  |  |

|                      |                                                                                                                                                                                       |                              |                |                        |                 |                  |               |  |  |  |

|                      | 01 = HOURS<br>10 = DAY                                                                                                                                                                | 5                            |                |                        |                 |                  |               |  |  |  |

# REGISTER 24-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

**2:** A write to the RTCEN bit is only allowed when RTCWREN = 1.

3: This bit is read-only. It is cleared to '0' on a write to the lower half of the MINSEC register.

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0                     | U-0    |

|-----------------|-----|------------------|-----|-----------------------------------------|-----|-------------------------|--------|

| —               | —   | —                | _   | —                                       | —   | —                       | —      |

| bit 15          |     |                  |     |                                         |     |                         |        |

|                 |     |                  |     |                                         |     |                         |        |

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | R/W-0                   | R/W-0  |

|                 | —   | —                | _   | —                                       | —   | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7           |     |                  |     |                                         |     |                         | bit 0  |

|                 |     |                  |     |                                         |     |                         |        |

| Legend:         |     |                  |     |                                         |     |                         |        |

| R = Readable I  | bit | W = Writable     | bit | U = Unimplemented bit, read as '0'      |     |                         |        |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |                         |        |

bit 15-2 Unimplemented: Read as '0'

| bit 1 | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup>                                                                      |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | <ul> <li>1 = RTCC seconds clock is selected for the RTCC pin</li> <li>0 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |  |  |  |  |  |

| bit 0 | PMPTTL: PMP Module TTL Input Buffer Select bit                                                                                     |  |  |  |  |  |

|       | 1 = PMP module uses TTL input buffers                                                                                              |  |  |  |  |  |

|       | 0 = PMP module uses Schmitt Trigger input buffers                                                                                  |  |  |  |  |  |

|       |                                                                                                                                    |  |  |  |  |  |

Note 1: To enable the actual RTCC output, the RTCOE bit (RCFGCAL<10>) needs to be set.

## 25.5 Programmable CRC Registers

#### **CRCCON: CRC CONTROL REGISTER** REGISTER 25-1: R/W-0 U-0 U-0 R-0 R-0 R-0 R-0 R-0 CSIDL VWORD<4:0> \_ bit 15 bit 8 R/W-0 R-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 CRCFUL CRCMPT CRCGO PLEN<3:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-14 Unimplemented: Read as '0' bit 13 CSIDL: CRC Stop in Idle Mode bit 1 = Discontinue module operation when device enters Idle mode 0 = Continue module operation in Idle mode bit 12-8 VWORD<4:0>: Pointer Value bits Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<3:0> is greater than 7, or 16 when PLEN<3:0> is less than or equal to 7. bit 7 **CRCFUL:** FIFO Full bit 1 = FIFO is full 0 = FIFO is not full bit 6 **CRCMPT:** FIFO Empty bit 1 = FIFO is empty 0 = FIFO is not empty bit 5 Unimplemented: Read as '0' bit 4 CRCGO: Start CRC bit 1 = Start CRC serial shifter 0 = Turn off CRC serial shifter after FIFO is empty bit 3-0 PLEN<3:0>: Polynomial Length bits Denotes the length of the polynomial to be generated minus 1.

# 29.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 29.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP)<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| DC CHARACTERISTICS              |                           |     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |           |  |  |

|---------------------------------|---------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-----------|--|--|

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup>    | Max | Units                                                                                                                                                                                                                                                                                 | Conditions |        |           |  |  |

| Operating Cur                   | rent (IDD) <sup>(1)</sup> |     | •                                                                                                                                                                                                                                                                                     |            |        |           |  |  |

| DC20d                           | 18                        | 21  | mA                                                                                                                                                                                                                                                                                    | -40°C      |        |           |  |  |

| DC20a                           | 18                        | 22  | mA                                                                                                                                                                                                                                                                                    | +25°C      | 3.3V   | 10 MIPS   |  |  |

| DC20b                           | 18                        | 22  | mA                                                                                                                                                                                                                                                                                    | +85°C      | - 3.3V | 10 101195 |  |  |

| DC20c                           | 18                        | 25  | mA                                                                                                                                                                                                                                                                                    | +125°C     |        |           |  |  |

| DC21d                           | 30                        | 35  | mA                                                                                                                                                                                                                                                                                    | -40°C      |        |           |  |  |

| DC21a                           | 30                        | 34  | mA                                                                                                                                                                                                                                                                                    | +25°C      | 3.3V   | 16 MIPS   |  |  |

| DC21b                           | 30                        | 34  | mA                                                                                                                                                                                                                                                                                    | +85°C      | - 3.3V | TO IVITES |  |  |

| DC21c                           | 30                        | 36  | mA                                                                                                                                                                                                                                                                                    | +125°C     |        |           |  |  |

| DC22d                           | 34                        | 42  | mA                                                                                                                                                                                                                                                                                    | -40°C      |        |           |  |  |

| DC22a                           | 34                        | 41  | mA                                                                                                                                                                                                                                                                                    | +25°C      | 3.3V   | 20 MIPS   |  |  |

| DC22b                           | 34                        | 42  | mA                                                                                                                                                                                                                                                                                    | +85°C      | 3.3V   | 20 MIPS   |  |  |

| DC22c                           | 35                        | 44  | mA                                                                                                                                                                                                                                                                                    | +125°C     |        |           |  |  |

| DC23d                           | 49                        | 58  | mA                                                                                                                                                                                                                                                                                    | -40°C      |        |           |  |  |

| DC23a                           | 49                        | 57  | mA                                                                                                                                                                                                                                                                                    | +25°C      | 2.21/  |           |  |  |

| DC23b                           | 49                        | 57  | mA                                                                                                                                                                                                                                                                                    | +85°C      | - 3.3V | 30 MIPS   |  |  |

| DC23c                           | 49                        | 60  | mA                                                                                                                                                                                                                                                                                    | +125°C     | 7      |           |  |  |

| DC24d                           | 63                        | 75  | mA                                                                                                                                                                                                                                                                                    | -40°C      |        |           |  |  |

| DC24a                           | 63                        | 74  | mA                                                                                                                                                                                                                                                                                    | +25°C      | 2.21/  |           |  |  |

| DC24b                           | 63                        | 74  | mA                                                                                                                                                                                                                                                                                    | +85°C      | - 3.3V | 40 MIPS   |  |  |

| DC24c                           | 63                        | 76  | mA                                                                                                                                                                                                                                                                                    | +125°C     | 1      |           |  |  |

#### TABLE 30-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode, no PLL until 10 MIPS, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational