### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp202-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 28-Pin QFN-S<sup>(2)</sup> Pins are up to 5V tolerant AN10/DAC1LP/RTCC/RP14<sup>(1)</sup>/CN12/PMWR/RB14 AN9/DAC1LN/RP15(1)/CN11/PMCS1/RB15 AN0/VREF+/CN2/RA0 AN1/NREF-/CN3/RA1 MCLR AVDD AVSS 27 [ 26 [ 25 [ 28 24 [ 23 [ 22 [ PGED1/AN2/C2IN-/RP0<sup>(1)</sup>/CN4/RB0 1 AN11/DAC1RN/RP13<sup>(1)</sup>/CN13/PMRD/RB13 21 PGEC1/AN3/C2IN+/RP1(1)/CN5/RB1 2 AN12/DAC1RP/RP12<sup>(1)</sup>/CN14/PMD0/RB12 20 AN4/C1IN-/RP2<sup>(1)</sup>/CN6/RB2 PGEC2/TMS/RP11<sup>(1)</sup>/CN15/PMD1/RB11 3 dsPIC33FJ64GP802 19 PGED2/TDI/RP10<sup>(1)</sup>/CN16/PMD2/RB10 AN5/C1IN+/RP3(1)/CN7/RB3 4 dsPIC33FJ128GP802 18 Vss 5 VCAP 17 OSC1/CLKI/CN30/RA2 6 16 Vss TDO/SDA1/RP9(1)/CN21/PMD3/RB9 OSC2/CLKO/CN29/PMA0/RA3 7 15 9 2 33 4 PGEC3/ASCL1/RP6<sup>(1)</sup>/CN24/PMD6/RB6 INT0/RP7<sup>(1)</sup>/CN23/PMD5/RB7 PGED3/ASDA1/RP5<sup>(1)</sup>/CN27/PMD7/RB5 TCK/SCL1/RP8<sup>(1)</sup>/CN22/PMD4/RB8 SOSCI/RP4<sup>(1)</sup>/CN1/PMBE/RB4 VDD SOSCO/T1CK/CN0/PMA1/RA4 The RPx pins can be used by any remappable peripheral. See Table 1 in this section for the list of available peripherals. Note 1: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 2:

### Pin Diagrams (Continued)

# TABLE 4-19: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1(FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/804) (CONTINUED)

| File Name  | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8 | Bit 7                         | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|--------|-----------|--------|--------|--------|--------|----------|-------|-------------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11EID | 046E |        |           |        | EID<   | 15:8>  |        |          |       | EID<7:0>                      |          |       |       |       |       |       |       | XXXX          |

| C1RXF12SID | 0470 |        |           |        | SID<   | 10:3>  |        |          |       |                               | SID<2:0> |       | —     | EXIDE |       | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472 |        | EID<15:8> |        |        |        |        | EID<7:0> |       |                               |          |       |       |       |       | XXXX  |       |               |

| C1RXF13SID | 0474 |        | SID<10:3> |        |        |        |        |          |       |                               | SID<2:0> |       | —     | EXIDE | —     | EID<1 | 7:16> | XXXX          |

| C1RXF13EID | 0476 |        |           |        | EID<   | 15:8>  |        |          |       | EID<7:0>                      |          |       |       |       |       |       | XXXX  |               |

| C1RXF14SID | 0478 |        |           |        | SID<   | 10:3>  |        |          |       | SID<2:0> — EXIDE — EID<17:16> |          |       |       |       |       | 7:16> | XXXX  |               |

| C1RXF14EID | 047A |        | EID<15:8> |        |        |        |        |          |       |                               |          |       | EID<  | 7:0>  |       |       |       | XXXX          |

| C1RXF15SID | 047C |        | SID<10:3> |        |        |        |        |          |       | SID<2:0>                      |          | —     | EXIDE | —     | EID<1 | 7:16> | XXXX  |               |

| C1RXF15EID | 047E |        | EID<15:8> |        |        |        |        |          |       |                               |          | EID<  | 7:0>  |       |       |       | XXXX  |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-20: DCI REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13                          | Bit 12 | Bit 11                          | Bit 10                                                       | Bit 9    | Bit 8       | Bit 7      | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   |         | Reset Sta | ate     |

|----------|-------|--------|--------|---------------------------------|--------|---------------------------------|--------------------------------------------------------------|----------|-------------|------------|--------|-------|-------|-------|-------|---------|---------|---------|-----------|---------|

| DCICON1  | 0280  | DCIEN  | —      | DCISIDL                         | —      | DLOOP                           | CSCKD                                                        | CSCKE    | COFSD       | UNFM       | CSDOM  | DJST  | —     | —     | _     | COFSM1  | COFSM0  | 0000    | 0000 00   | 00 0000 |

| DCICON2  | 0282  | _      | _      |                                 | _      | BLEN1                           | BLEN0                                                        |          |             | COFSC      | G<3:0> |       |       |       | V     | /S<3:0> | •       | 0000    | 0000 00   | 00 0000 |

| DCICON3  | 0284  | —      | —      | _                               | —      |                                 |                                                              |          |             |            | BCG<11 | :0>   |       |       |       |         |         | 0000    | 0000 00   | 00 0000 |

| DCISTAT  | 0286  | —      | —      | _                               | —      | SLOT3                           | SLOT2                                                        | SLOT1    | SLOT0       | —          | —      | _     | _     | ROV   | RFUL  | TUNF    | TMPTY   | 0000    | 0000 00   | 00 0000 |

| TSCON    | 0288  | TSE15  | TSE14  | TSE13                           | TSE12  | TSE11                           | TSE10                                                        | TSE9     | TSE8        | TSE7       | TSE6   | TSE5  | TSE4  | TSE3  | TSE2  | TSE1    | TSE0    | 0000    | 0000 00   | 00 0000 |

| RSCON    | 028C  | RSE15  | RSE14  | RSE13                           | RSE12  | RSE11                           | SE11 RSE10 RSE9 RSE8 RSE7 RSE6 RSE5 RSE4 RSE3 RSE2 RSE1 RSE0 |          |             |            |        |       |       |       |       | 0000    | 0000 00 | 00 0000 |           |         |

| RXBUF0   | 0290  |        |        |                                 |        | Receive Buffer 0 Data Register  |                                                              |          |             |            |        |       |       |       |       | 0000    | 0000 00 | 00 0000 |           |         |

| RXBUF1   | 0292  |        |        |                                 |        |                                 |                                                              | Receive  | Buffer 1 Da | ata Regist | er     |       |       |       |       |         |         | 0000    | 0000 00   | 00 0000 |

| RXBUF2   | 0294  |        |        |                                 |        |                                 |                                                              | Receive  | Buffer 2 Da | ata Regist | er     |       |       |       |       |         |         | 0000    | 0000 00   | 00 0000 |

| RXBUF3   | 0296  |        |        |                                 |        |                                 |                                                              | Receive  | Buffer 3 Da | ata Regist | er     |       |       |       |       |         |         | 0000    | 0000 00   | 00 0000 |

| TXBUF0   | 0298  |        |        |                                 |        |                                 |                                                              | Transmit | Buffer 0 Da | ata Regis  | ter    |       |       |       |       |         |         | 0000    | 0000 00   | 00 0000 |

| TXBUF1   | 029A  |        |        |                                 |        | Transmit Buffer 1 Data Register |                                                              |          |             |            |        |       |       |       |       |         | 0000    | 0000 00 | 00 0000   |         |

| TXBUF2   | 029C  |        |        |                                 |        |                                 | Transmit Buffer 2 Data Register                              |          |             |            |        |       |       |       |       |         |         | 0000    | 0000 00   | 00 0000 |

| TXBUF3   | 029E  |        |        | Transmit Buffer 3 Data Register |        |                                 |                                                              |          |             |            |        |       |       |       | 0000  | 0000 00 | 00 0000 |         |           |         |

Legend: — = unimplemented, read as '0'.

### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to <sup>(0010)</sup> to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

# EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | ;                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA[15:0] pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | ;                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

| EGISTER 7      | -10: IEC0:      | INTERRUPT                        | ENABLE CO      | ONTROL REC        | GISTER 0         |                 |        |

|----------------|-----------------|----------------------------------|----------------|-------------------|------------------|-----------------|--------|

| U-0            | R/W-0           | R/W-0                            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| _              | DMA1IE          | AD1IE                            | U1TXIE         | U1RXIE            | SPI1IE           | SPI1EIE         | T3IE   |

| it 15          |                 |                                  |                |                   |                  |                 | bi     |

| R/W-0          | R/W-0           | R/W-0                            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IE           | OC2IE           | IC2IE                            | DMA0IE         | T1IE              | OC1IE            | IC1IE           | INTOIE |

| oit 7          |                 |                                  |                |                   |                  |                 | b      |

| egend:         |                 |                                  |                |                   |                  |                 |        |

| R = Readable   | bit             | W = Writable                     | bit            | U = Unimplem      | nented bit, read | d as '0'        |        |

| n = Value at F | POR             | '1' = Bit is set                 | t              | '0' = Bit is clea |                  | x = Bit is unkn | own    |

|                |                 |                                  |                |                   |                  |                 |        |

| it 15          | Unimplemen      | ted: Read as                     | 0'             |                   |                  |                 |        |

| oit 14         | DMA1IE: DM      | A Channel 1 D                    | ata Transfer C | Complete Interru  | upt Enable bit   |                 |        |

|                |                 | request enable                   |                |                   |                  |                 |        |

|                | -               | request not en                   |                |                   |                  |                 |        |

| oit 13         |                 |                                  | •              | rupt Enable bit   |                  |                 |        |

|                |                 | request enable<br>request not en |                |                   |                  |                 |        |

| it 12          | •               | RT1 Transmitte                   |                | able bit          |                  |                 |        |

| 1, 12          |                 | request enable                   | -              |                   |                  |                 |        |

|                |                 | request not en                   |                |                   |                  |                 |        |

| oit 11         | U1RXIE: UAF     | RT1 Receiver I                   | nterrupt Enabl | e bit             |                  |                 |        |

|                |                 | request enable                   |                |                   |                  |                 |        |

|                |                 | request not en                   |                |                   |                  |                 |        |

| oit 10         |                 | Event Interrup                   |                |                   |                  |                 |        |

|                |                 | request enable<br>request not en |                |                   |                  |                 |        |

| oit 9          | -               | 1 Error Interru                  |                |                   |                  |                 |        |

|                | 1 = Interrupt r | request enable                   | d              |                   |                  |                 |        |

| ÷ 0            | •               | request not en                   |                |                   |                  |                 |        |

| oit 8          |                 | Interrupt Enab<br>request enable |                |                   |                  |                 |        |

|                | •               | request enable                   |                |                   |                  |                 |        |

| oit 7          | •               | Interrupt Enab                   |                |                   |                  |                 |        |

|                | 1 = Interrupt r | request enable                   | d              |                   |                  |                 |        |

|                | •               | request not en                   |                |                   |                  |                 |        |

| oit 6          | -               | ut Compare Cl                    |                | upt Enable bit    |                  |                 |        |

|                |                 | request enable<br>request not en |                |                   |                  |                 |        |

| oit 5          | •               | Capture Chann                    |                | Enable bit        |                  |                 |        |

|                | •               | request enable                   | •              |                   |                  |                 |        |

|                |                 | request not en                   |                |                   |                  |                 |        |

| oit 4          | DMA0IE: DM      | A Channel 0 D                    | ata Transfer C | Complete Interru  | upt Enable bit   |                 |        |

|                |                 | request enable                   |                |                   |                  |                 |        |

|                | •               | request not en                   |                |                   |                  |                 |        |

| oit 3          | T1IE: Timer1    | Interrupt Enab                   | ole bit        |                   |                  |                 |        |

|                | a 1             | request enable                   |                |                   |                  |                 |        |

### ----

| R/W-0                   | R/W-0                              | U-0                              | U-0             | U-0                      | U-0              | U-0             | U-0   |

|-------------------------|------------------------------------|----------------------------------|-----------------|--------------------------|------------------|-----------------|-------|

| DAC1LIE <sup>(2)</sup>  | DAC1RIE <sup>(2)</sup>             | _                                | —               | —                        | —                | —               |       |

| bit 15                  |                                    |                                  |                 |                          |                  |                 | bit   |

|                         |                                    |                                  |                 |                          |                  |                 |       |

| U-0                     | R/W-0                              | R/W-0                            | R/W-0           | R/W-0                    | R/W-0            | R/W-0           | U-0   |

| —                       | C1TXIE <sup>(1)</sup>              | DMA7IE                           | DMA6IE          | CRCIE                    | U2EIE            | U1EIE           | —     |

| bit 7                   |                                    |                                  |                 |                          |                  |                 | bit   |

| Lowandi                 |                                    |                                  |                 |                          |                  |                 |       |

| Legend:<br>R = Readable | , hit                              | \\/ = \\/ritabla                 | hit             | II – Unimplor            | monted hit read  |                 |       |

| -n = Value at           |                                    | W = Writable<br>'1' = Bit is set |                 | '0' = Bit is cle         | mented bit, read | x = Bit is unkn | 0.000 |

|                         | FUR                                |                                  | L               |                          | aleu             |                 |       |

| bit 15                  | DAC1LIE: DA                        | C Left Channe                    | el Interrupt En | able bit <sup>(2)</sup>  |                  |                 |       |

|                         | 1 = Interrupt r                    |                                  |                 |                          |                  |                 |       |

|                         | 0 = Interrupt r                    | •                                |                 |                          |                  |                 |       |

| bit 14                  | DAC1RIE: DA                        |                                  |                 | nable bit <sup>(2)</sup> |                  |                 |       |

|                         | 1 = Interrupt r                    | •                                |                 |                          |                  |                 |       |

| bit 13-7                | 0 = Interrupt r<br>Unimplement     | •                                |                 |                          |                  |                 |       |

| bit 6                   | •                                  |                                  |                 | nterrupt Enable          | o hit(1)         |                 |       |

|                         | 1 = Interrupt r                    |                                  | •               | nterrupt Enable          |                  |                 |       |

|                         |                                    | equest not occ                   |                 |                          |                  |                 |       |

| bit 5                   | DMA7IE: DM                         | A Channel 7 D                    | ata Transfer C  | Complete Interr          | upt Enable bit   |                 |       |

|                         |                                    | equest enable                    |                 |                          |                  |                 |       |

|                         | -                                  | equest not en                    |                 |                          |                  |                 |       |

| bit 4                   |                                    |                                  |                 | Complete Interr          | upt Enable bit   |                 |       |

|                         | 1 = Interrupt r<br>0 = Interrupt r | equest enable                    |                 |                          |                  |                 |       |

| bit 3                   | CRCIE: CRC                         | •                                |                 | oit                      |                  |                 |       |

| DIL 3                   | 1 = Interrupt r                    |                                  | •               | JIL                      |                  |                 |       |

|                         | 0 = Interrupt r                    |                                  |                 |                          |                  |                 |       |

| bit 2                   | U2EIE: UART                        | 2 Error Interru                  | pt Enable bit   |                          |                  |                 |       |

|                         | 1 = Interrupt r                    | equest enable                    | d               |                          |                  |                 |       |

|                         | 0 = Interrupt r                    | equest not en                    | abled           |                          |                  |                 |       |

| bit 1                   | U1EIE: UART                        |                                  | -               |                          |                  |                 |       |

|                         | 1 = Interrupt r<br>0 = Interrupt r | equest enable                    |                 |                          |                  |                 |       |

|                         |                                    |                                  |                 |                          |                  |                 |       |

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

2: Interrupts are disabled on devices without Audio DAC modules.

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 38. "Direct Memory Access (DMA) (Part III)" (DS70215) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer), and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association         | DMAxREQ Register<br>IRQSEL<6:0> Bits | DMAxPAD Register<br>Values to Read from<br>Peripheral | DMAxPAD Register<br>Values to Write to<br>Peripheral |

|---------------------------------------|--------------------------------------|-------------------------------------------------------|------------------------------------------------------|

| INT0 – External Interrupt 0           | 0000000                              | —                                                     | —                                                    |

| IC1 – Input Capture 1                 | 000001                               | 0x0140 (IC1BUF)                                       | —                                                    |

| OC1 – Output Compare 1 Data           | 0000010                              | —                                                     | 0x0182 (OC1R)                                        |

| OC1 – Output Compare 1 Secondary Data | 0000010                              | —                                                     | 0x0180 (OC1RS)                                       |

| IC2 – Input Capture 2                 | 0000101                              | 0x0144 (IC2BUF)                                       | —                                                    |

| OC2 – Output Compare 2 Data           | 0000110                              | —                                                     | 0x0188 (OC2R)                                        |

| OC2 – Output Compare 2 Secondary Data | 0000110                              | —                                                     | 0x0186 (OC2RS)                                       |

| TMR2 – Timer2                         | 0000111                              | —                                                     | —                                                    |

| TMR3 – Timer3                         | 0001000                              | —                                                     | —                                                    |

| SPI1 – Transfer Done                  | 0001010                              | 0x0248 (SPI1BUF)                                      | 0x0248 (SPI1BUF)                                     |

| UART1RX – UART1 Receiver              | 0001011                              | 0x0226 (U1RXREG)                                      | —                                                    |

| UART1TX – UART1 Transmitter           | 0001100                              | —                                                     | 0x0224 (U1TXREG)                                     |

| ADC1 – ADC1 convert done              | 0001101                              | 0x0300 (ADC1BUF0)                                     | —                                                    |

| UART2RX – UART2 Receiver              | 0011110                              | 0x0236 (U2RXREG)                                      | —                                                    |

| UART2TX – UART2 Transmitter           | 0011111                              | —                                                     | 0x0234 (U2TXREG)                                     |

| SPI2 – Transfer Done                  | 0100001                              | 0x0268 (SPI2BUF)                                      | 0x0268 (SPI2BUF)                                     |

| ECAN1 – RX Data Ready                 | 0100010                              | 0x0440 (C1RXD)                                        | —                                                    |

| PMP – Master Data Transfer            | 0101101                              | 0x0608 (PMDIN1)                                       | 0x0608 (PMDIN1)                                      |

| ECAN1 – TX Data Request               | 1000110                              | —                                                     | 0x0442 (C1TXD)                                       |

| DCI – Codec Transfer Done             | 0111100                              | 0x0290 (RXBUF0)                                       | 0x0298 (TXBUF0)                                      |

| DAC1 – Right Data Output              | 1001110                              | —                                                     | 0x03F6 (DAC1RDAT)                                    |

| DAC2 – Left Data Output               | 1001111                              | —                                                     | 0x03F8 (DAC1LDAT)                                    |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

### 11.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

### 11.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Note: MPLAB<sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: \_\_builtin\_write\_OSCCONL(value) \_\_builtin\_write\_OSCCONH(value) See MPLAB Help for more information.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

### 11.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset is triggered.

### 11.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY configuration bit (FOSC<5>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

NOTES:

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as $I^2C$ slave)                                                                                                                                                                      |

|       | 1 = Read – indicates data transfer is output from slave<br>0 = Write – indicates data transfer is input to slave<br>Hardware set or clear after reception of $I^2C$ device address byte.                                                     |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

# $dsPIC33FJ32GP302/304,\, dsPIC33FJ64GPX02/X04,\, AND\, dsPIC33FJ128GPX02/X04$

| U-0          | U-0                                                                                         | R-0                                                                          | R-0              | R-0              | R-0            | R-0             | R-0   |

|--------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|------------------|----------------|-----------------|-------|

| _            |                                                                                             |                                                                              |                  | FBF              | P<5:0>         |                 |       |

| bit 15       |                                                                                             |                                                                              |                  |                  |                |                 | bit 8 |

| U-0          | U-0                                                                                         | R-0                                                                          | R-0              | R-0              | R-0            | R-0             | R-0   |

| _            | —                                                                                           |                                                                              |                  | FNR              | B<5:0>         |                 |       |

| bit 7        |                                                                                             |                                                                              |                  |                  |                |                 | bit ( |

| Legend:      |                                                                                             | C = Writable b                                                               | oit, but only '0 | ' can be writter | n to clear the | bit             |       |

| R = Readab   | le bit                                                                                      | W = Writable                                                                 | bit              | U = Unimpler     | mented bit, re | ad as '0'       |       |

| -n = Value a | t POR                                                                                       | '1' = Bit is set                                                             |                  | '0' = Bit is cle | ared           | x = Bit is unki | nown  |

| bit 7-6      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | RB30 buffer<br>IRB1 buffer<br>IRB0 buffer<br>ented: Read as '0               | o <b>'</b>       |                  |                |                 |       |

| bit 5-0      | 011111 =  <br>011110 =  <br>•                                                               | >: FIFO Next Rea<br>RB31 buffer<br>RB30 buffer<br>IRB1 buffer<br>IRB1 buffer | id Buffer Poin   | ter bits         |                |                 |       |

| REGISTER     | R 19-20: CiRXI<br>REGIS | /InSID: ECAN<br>STER n (n = (                             |                  | ANCE FILTE       | R MASK STA         | ANDARD IDEI     | NTIFIER         |

|--------------|-------------------------|-----------------------------------------------------------|------------------|------------------|--------------------|-----------------|-----------------|

| R/W-x        | R/W-x                   | R/W-x                                                     | R/W-x            | R/W-x            | R/W-x              | R/W-x           | R/W-x           |

| SID10        | SID9                    | SID8                                                      | SID7             | SID6             | SID5               | SID4            | SID3            |

| bit 15       |                         |                                                           |                  |                  |                    |                 | bit             |

| R/W-x        | R/W-x                   | R/W-x                                                     | U-0              | R/W-x            | U-0                | R/W-x           | R/W-x           |

| SID2         | SID1                    | SID0                                                      | _                | MIDE             | _                  | EID17           | EID16           |

| bit 7        |                         |                                                           |                  |                  |                    |                 | bit             |

| Legend:      |                         | C = Writable                                              | bit, but only '0 | ' can be writter | n to clear the bi  | it              |                 |

| R = Readab   | ole bit                 | W = Writable                                              | bit              | U = Unimpler     | mented bit, rea    | d as '0'        |                 |

| -n = Value a | at POR                  | '1' = Bit is set                                          |                  | '0' = Bit is cle | ared               | x = Bit is unkr | nown            |

| bit 15-5     | 1 = Include b           | Standard Identii<br>it SIDx in filter<br>is don't care in | comparison       | son              |                    |                 |                 |

| bit 4        | Unimplemer              | nted: Read as '                                           | 0'               |                  |                    |                 |                 |

| bit 3        | MIDE: Identif           | ier Receive Mo                                            | ode bit          |                  |                    |                 |                 |

|              | 0 = Match eit           | ly message typ<br>her standard o<br>ilter SID) = (Me      | r extended ad    | dress message    | e if filters match |                 | DE bit in filte |

|              |                         |                                                           |                  |                  |                    |                 |                 |

- bit 2 Unimplemented: Read as '0'

- bit 1-0 EID<17:16>: Extended Identifier bits

- 1 = Include bit EIDx in filter comparison

- 0 = Bit EIDx is don't care in filter comparison

# REGISTER 19-21: CIRXMnEID: ECAN<sup>™</sup> ACCEPTANCE FILTER MASK EXTENDED IDENTIFIER REGISTER n (n = 0-2)

|        |       | •     | •     |       |       |       |       |

|--------|-------|-------|-------|-------|-------|-------|-------|

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           | C = Writable bit, but only '0 | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |

|-------------------|-------------------------------|----------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit              | W = Writable bit U = Unimplemented bit, read as '0'            |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

# REGISTER 19-22: CiRXFUL1: ECAN™ RECEIVE BUFFER FULL REGISTER 1

|                                                                        |         | -       |         |         |         |        |        |

|------------------------------------------------------------------------|---------|---------|---------|---------|---------|--------|--------|

| R/C-0                                                                  | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL15                                                                | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15                                                                 |         |         |         |         |         |        | bit 8  |

|                                                                        |         |         |         |         |         |        |        |

| R/C-0                                                                  | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL7                                                                 | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1 | RXFUL0 |

| bit 7                                                                  |         |         |         |         |         |        | bit 0  |

|                                                                        |         |         |         |         |         |        |        |

| Legend: C = Writable bit, but only '0' can be written to clear the bit |         |         |         |         |         |        |        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'   |         |         |         |         |         |        |        |

|                                                                        |         |         |         |         |         |        |        |

'0' = Bit is cleared

x = Bit is unknown

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

'1' = Bit is set

0 = Buffer is empty

-n = Value at POR

### REGISTER 19-23: CIRXFUL2: ECAN™ RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                                    |                    |  |  |

|-------------------|----------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty

# REGISTER 20-3: DCICON3: DCI CONTROL REGISTER 3

| U-0                               | U-0   | U-0              | U-0                                | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-----------------------------------------|-------|--------|-------|

| _                                 |       | _                | _                                  |                                         | BCG   | <11:8> |       |

| bit 15                            |       | ·                |                                    |                                         |       |        | bit 8 |

| [                                 |       |                  |                                    |                                         |       |        |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|                                   |       |                  | BCC                                | 6<7:0>                                  |       |        |       |

| bit 7                             |       |                  |                                    |                                         |       |        | bit 0 |

|                                   |       |                  |                                    |                                         |       |        |       |

| Legend:                           |       |                  |                                    |                                         |       |        |       |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0' |                                         |       |        |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknown |       |        |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 BCG<11:0>: DCI Bit Clock Generator Control bits

# 21.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

# 21.5 ADC Resources

Many useful resources related to ADC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

### 21.5.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

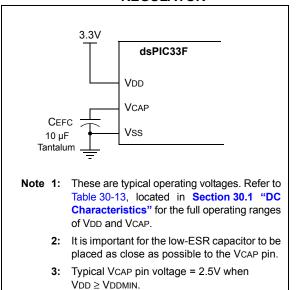

### 27.2 On-Chip Voltage Regulator

All of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 Ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-13 located in Section 30.1 "DC Characteristics".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20 µs for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

### 27.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

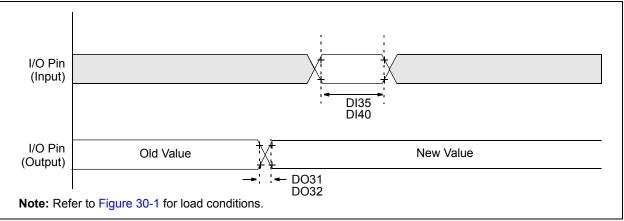

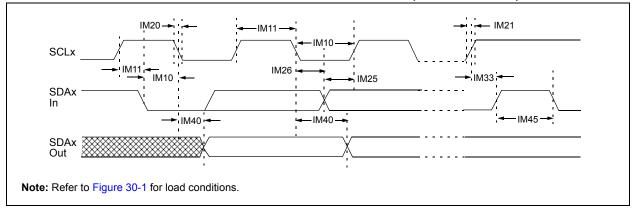

### FIGURE 30-3: CLKO AND I/O TIMING CHARACTERISTICS

### TABLE 30-20: I/O TIMING REQUIREMENTS

|              |        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |     |                    |     |       |            |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|--------------------|-----|-------|------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                                                                                       |            | Min | Typ <sup>(1)</sup> | Мах | Units | Conditions |

| DO31         | TioR   | Port Output Rise Tim                                                                                                                                                                                 | e          |     | 10                 | 25  | ns    | _          |

| DO32         | TIOF   | Port Output Fall Time                                                                                                                                                                                | 9          | —   | 10                 | 25  | ns    | —          |

| DI35         | TINP   | INTx Pin High or Low Time (input)                                                                                                                                                                    |            | 20  | _                  | _   | ns    | _          |

| DI40         | Trbp   | CNx High or Low Tim                                                                                                                                                                                  | ne (input) | 2   | _                  |     | TCY   |            |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

| АС СНА       | RACTERIST             | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |     |                    |     |       |                                  |

|--------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|----------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                            | Min | Тур <sup>(2)</sup> | Max | Units | Conditions                       |

| SP10         | TscP                  | Maximum SCK Frequency                                                                                                                                                                    | —   | _                  | 15  | MHz   | See Note 3                       |

| SP20         | TscF                  | SCKx Output Fall Time                                                                                                                                                                    | _   | —                  | _   | ns    | See parameter DO32<br>and Note 4 |

| SP21         | TscR                  | SCKx Output Rise Time                                                                                                                                                                    | —   | —                  |     | ns    | See parameter DO31 and Note 4    |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                                                                                                                                               | _   | —                  | _   | ns    | See parameter DO32 and Note 4    |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                                                                                                                                               | _   | —                  | _   | ns    | See parameter DO31 and Note 4    |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                                | —   | 6                  | 20  | ns    | _                                |

| SP36         | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                                                             | 30  | —                  | _   | ns    | —                                |

### TABLE 30-29: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# 33.0 PACKAGING INFORMATION

28-Lead SPDIP

28-Lead SOIC

28-Lead QFN-S

44-Lead QFN

44-Lead TQFP

Example

Example

Example

Example

Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |  |  |

|--------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Note:  |                                           |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |