Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp202-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.4 Special MCU Features

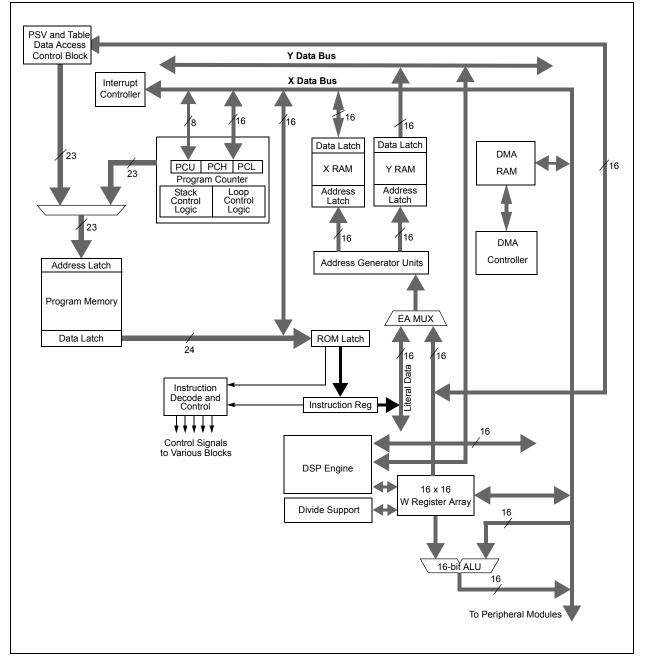

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

#### FIGURE 3-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 CPU CORE BLOCK DIAGRAM

#### TABLE 4-2:CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ128GP202/802, dsPIC33FJ64GP202/802 AND dsPIC33FJ32GP302

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|--------|-------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | _      | _     | —       | CN7IE   | CN6IE   | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE   | 0000          |

| CNEN2       | 0062        |         | CN30IE  | CN29IE  | -       | CN27IE  |        | —     | CN24IE  | CN23IE  | CN22IE  | CN21IE  | —      | _      | _      | -      | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE |        | _     | -       | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE |         | CN27PUE | _      | _     | CN24PUE | CN23PUE | CN22PUE | CN21PUE | —      |        |        | _      | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ128GP204/804, dsPIC33FJ64GP204/804 AND dsPIC33FJ32GP304

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE   | CN8IE   | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | —       | CN30IE  | CN29IE  | CN28IE  | CN27IE  | CN26IE  | CN25IE  | CN24IE  | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE  | CN8PUE  | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE | CN28PUE | CN27PUE | CN26PUE | CN25PUE | CN24PUE | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 8-3: | DMAxSTA: DMA CHANNEL x RAM START ADDRESS REGISTER A <sup>(1)</sup> |

|---------------|--------------------------------------------------------------------|

|---------------|--------------------------------------------------------------------|

| R/W-0                              | R/W-0                             | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |  |  |  |

|------------------------------------|-----------------------------------|-------|-------|-----------------------------------------|------------------------------------|-------|-------|--|--|--|--|

|                                    |                                   |       | STA   | <15:8>                                  |                                    |       |       |  |  |  |  |

| bit 15                             |                                   |       |       |                                         |                                    |       | bit 8 |  |  |  |  |

|                                    |                                   |       |       |                                         |                                    |       |       |  |  |  |  |

| R/W-0                              | R/W-0                             | R/W-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |  |  |  |

|                                    |                                   |       | STA   | <7:0>                                   |                                    |       |       |  |  |  |  |

| bit 7                              |                                   |       |       |                                         |                                    |       | bit 0 |  |  |  |  |

|                                    |                                   |       |       |                                         |                                    |       |       |  |  |  |  |

| Legend:                            |                                   |       |       |                                         |                                    |       |       |  |  |  |  |

| R = Readable                       | R = Readable bit W = Writable bit |       |       |                                         | U = Unimplemented bit, read as '0' |       |       |  |  |  |  |

| -n = Value at POR '1' = Bit is set |                                   |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |  |  |  |  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

**Note 1:** A read of this address register returns the current contents of the DMA RAM Address register, not the contents written to STA<15:0>. If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS REGISTER B<sup>(1)</sup>

| R/W-0                         | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|-------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                               |       |                  | STB   | <15:8>                             |       |                    |       |  |

| bit 15                        |       |                  |       |                                    |       |                    | bit 8 |  |

| R/W-0                         | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|                               |       |                  | STE   | 3<7:0>                             |       |                    |       |  |

| bit 7                         |       |                  |       |                                    |       |                    | bit 0 |  |

| Legend:                       |       |                  |       |                                    |       |                    |       |  |

| R = Readable bit W = Writable |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR             |       | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unknown |       |  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

**Note 1:** A read of this address register returns the current contents of the DMA RAM Address register, not the contents written to STB<15:0>. If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

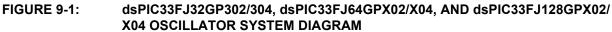

#### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304 dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 39. "Oscillator (Part III)" (DS70216) of the "dsPIC33F/ PIC24H Family Reference Manual". which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase-Locked Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Non-volatile Configuration bits for main oscillator selection

- · An auxiliary crystal oscillator for Audio DAC

A simplified diagram of the oscillator system is shown in Figure 9-1.

| TABLE 9-1. CONFIGURATION                         | BIT VALUES FOR C  |             | ·          |             |

|--------------------------------------------------|-------------------|-------------|------------|-------------|

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Note |

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | XX          | 111        | 1, 2        |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | XX          | 110        | 1           |

| Low-Power RC Oscillator (LPRC)                   | Internal          | XX          | 101        | 1           |

| Secondary (Timer1) Oscillator (SOSC)             | Secondary         | XX          | 100        | 1           |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | -           |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -           |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1           |

| Primary Oscillator (HS)                          | Primary           | 10          | 010        | _           |

| Primary Oscillator (XT)                          | Primary           | 01          | 010        | -           |

| Primary Oscillator (EC)                          | Primary           | 00          | 010        | 1           |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal          | XX          | 001        | 1           |

| Fast RC Oscillator (FRC)                         | Internal          | XX          | 000        | 1           |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 9.2 Oscillator Resources

Many useful resources related to the Oscillator are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

#### 9.2.1 KEY RESOURCES

- Section 39. "Oscillator (Part III)" (DS70216)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |              |                                  |               |                  |                 |                 |       |  |  |  |  |  |

|-------------------------------------------------------------------|--------------|----------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| U-0                                                               | U-0          | U-0                              | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|                                                                   | _            | —                                |               | —                | CMPMD           | RTCCMD          | PMPMD |  |  |  |  |  |

| bit 15                                                            |              |                                  |               |                  |                 |                 | bit 8 |  |  |  |  |  |

| R/W-0                                                             | R/W-0        | U-0                              | U-0           | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |

| CRCMD                                                             | DAC1MD       |                                  |               |                  |                 |                 | _     |  |  |  |  |  |

| bit 7                                                             | Briomi       |                                  |               |                  |                 |                 | bit ( |  |  |  |  |  |

|                                                                   |              |                                  |               |                  |                 |                 |       |  |  |  |  |  |

| Legend:                                                           |              |                                  |               |                  |                 |                 |       |  |  |  |  |  |

| R = Readab                                                        | le bit       | W = Writable b                   | bit           | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a                                                      | t POR        | '1' = Bit is set                 |               | '0' = Bit is cle | eared           | x = Bit is unkn | iown  |  |  |  |  |  |

|                                                                   |              |                                  |               |                  |                 |                 |       |  |  |  |  |  |

| bit 15-11                                                         | Unimplemen   | ted: Read as '0                  | ,             |                  |                 |                 |       |  |  |  |  |  |

| bit 10                                                            | CMPMD: Con   | mparator Module                  | e Disable bit |                  |                 |                 |       |  |  |  |  |  |

|                                                                   |              | tor module is dis                |               |                  |                 |                 |       |  |  |  |  |  |

|                                                                   | 0 = Comparat | tor module is er                 | abled         |                  |                 |                 |       |  |  |  |  |  |

| bit 9                                                             |              | RTCCMD: RTCC Module Disable bit  |               |                  |                 |                 |       |  |  |  |  |  |

|                                                                   |              | dule is disabled                 |               |                  |                 |                 |       |  |  |  |  |  |

| 1.11.0                                                            |              | dule is enabled                  |               |                  |                 |                 |       |  |  |  |  |  |

| bit 8                                                             |              | P Module Disab                   | ie dit        |                  |                 |                 |       |  |  |  |  |  |

|                                                                   |              | lule is disabled lule is enabled |               |                  |                 |                 |       |  |  |  |  |  |

| bit 7                                                             |              | C Module Disab                   | le bit        |                  |                 |                 |       |  |  |  |  |  |

|                                                                   |              | lule is disabled                 |               |                  |                 |                 |       |  |  |  |  |  |

|                                                                   | 0 = CRC mod  | lule is enabled                  |               |                  |                 |                 |       |  |  |  |  |  |

| bit 6                                                             | DAC1MD: DA   | AC1 Module Dis                   | able bit      |                  |                 |                 |       |  |  |  |  |  |

|                                                                   | 1 = DAC1 mo  | dule is disabled                 | ł             |                  |                 |                 |       |  |  |  |  |  |

|                                                                   | 0 = DAC1 mo  | dule is enabled                  |               |                  |                 |                 |       |  |  |  |  |  |

| bit 5-0                                                           | Unimplemen   | ted: Read as '0                  | ,             |                  |                 |                 |       |  |  |  |  |  |

|                                                                   |              |                                  |               |                  |                 |                 |       |  |  |  |  |  |

#### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to **"Pin Diagrams"** for the available pins and their functionality.

#### 11.3 Configuring Analog Port Pins

The AD1PCFGL and TRIS registers control the operation of the Analog-to-Digital (ADC) port pins. The port pins that are to function as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP, as shown in Example 11-1.

#### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-ofstates even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-ofstate.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

# MOV0xFF00, W0; Configure PORTB<15:8> as inputsMOVW0, TRISBB; and PORTB<7:0> as outputsNOP; Delay 1 cyclebtssPORTB, #13; Next Instruction

PORT WRITE/READ EXAMPLE

EXAMPLE 11-1:

| U-0                               | 11.0             |              |                                         |                               |                                                                               |                                                                                      |  |  |  |

|-----------------------------------|------------------|--------------|-----------------------------------------|-------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

|                                   | U-0              | U-0          | U-0                                     | U-0                           | U-0                                                                           | U-0                                                                                  |  |  |  |

| _                                 | —                | _            | —                                       | —                             | _                                                                             | _                                                                                    |  |  |  |

|                                   |                  |              |                                         |                               |                                                                               | bit 8                                                                                |  |  |  |

|                                   |                  |              |                                         |                               |                                                                               |                                                                                      |  |  |  |

| U-0                               | U-0              | R/W-1        | R/W-1                                   | R/W-1                         | R/W-1                                                                         | R/W-1                                                                                |  |  |  |

| _                                 | —                |              |                                         | INT2R<4:0>                    |                                                                               |                                                                                      |  |  |  |

|                                   |                  |              |                                         |                               |                                                                               | bit 0                                                                                |  |  |  |

|                                   |                  |              |                                         |                               |                                                                               |                                                                                      |  |  |  |

|                                   |                  |              |                                         |                               |                                                                               |                                                                                      |  |  |  |

| R = Readable bit W = Writable bit |                  |              | t U = Unimplemented bit, read as '0'    |                               |                                                                               |                                                                                      |  |  |  |

| 1                                 | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknown |                               |                                                                               |                                                                                      |  |  |  |

|                                   | _                | W = Writable | W = Writable bit                        | W = Writable bit U = Unimpler | —     —     INT2R<4:0>       W = Writable bit     U = Unimplemented bit, read | —     —     INT2R<4:0>       W = Writable bit     U = Unimplemented bit, read as '0' |  |  |  |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 INT2R<4:0>: Assign External Interrupt 2 (INTR2) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

.

00001 = Input tied to RP1 00000 = Input tied to RP0 NOTES:

#### 18.3 UART Control Registers

#### REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0    | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|----------|-------|

| UARTEN <sup>(1)</sup> | —   | USIDL | IREN <sup>(2)</sup> | RTSMD | —   | UEN<1:0> |       |

| bit 15                |     |       |                     |       |     |          | bit 8 |

| R/W-0 HC | R/W-0  | R/W-0 HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|--------|----------|--------|-------|-------|-------|-------|

| WAKE     | LPBACK | ABAUD    | URXINV | BRGH  | PDSEL | <1:0> | STSEL |

| bit 7    |        |          |        |       |       |       | bit 0 |

| Legend:           | HC = Hardware cleared |                             |                    |

|-------------------|-----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | <ul> <li>UARTEN: UARTx Enable bit<sup>(1)</sup></li> <li>1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN&lt;1:0&gt;</li> <li>0 = UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption minimal</li> </ul>                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 13  | USIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                           |

| bit 12  | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = IrDA<sup>®</sup> encoder and decoder enabled</li> <li>0 = IrDA<sup>®</sup> encoder and decoder disabled</li> </ul>                                                                                                                                                                                                                                                                 |

| bit 11  | <b>RTSMD:</b> Mode Selection for UxRTS Pin bit                                                                                                                                                                                                                                                                                                                                                  |

|         | 1 = <u>UxRTS</u> pin in Simplex mode<br>0 = UxRTS pin in Flow Control mode                                                                                                                                                                                                                                                                                                                      |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 9-8 | UEN<1:0>: UARTx Enable bits                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>11 = UxTX, UxRX and BCLK pins are enabled and used; UxCTS pin controlled by port latches</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches</li> <li>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by port latches</li> </ul> |

| bit 7   | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = UARTx continues to sample the UxRX pin; interrupt generated on falling edge; bit cleared<br/>in hardware on following rising edge</li> <li>0 = No wake-up enabled</li> </ul>                                                                                                                                                                                                       |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                                                                                                                                                                                                                                                          |

|         | 1 = Enable Loopback mode<br>0 = Loopback mode is disabled                                                                                                                                                                                                                                                                                                                                       |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul>                                                                                                                                                           |

| Note 1: | Refer to <b>Section 17. "UART"</b> (DS70188) in the <i>"dsPIC33F/PIC24H Family Reference Manual"</i> for information on enabling the UART module for receive or transmit operation.                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                                                                                                                                                                                                                 |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

| U-0                   | U-0                            | U-0                                | R-0              | R-0               | R-0                | R-0             | R-0  |

|-----------------------|--------------------------------|------------------------------------|------------------|-------------------|--------------------|-----------------|------|

| _                     | _                              |                                    |                  |                   | FILHIT<4:0>        |                 |      |

| it 15                 |                                |                                    |                  |                   |                    |                 | bit  |

| U-0                   | R-1                            | R-0                                | R-0              | R-0               | R-0                | R-0             | R-0  |

| _                     |                                |                                    |                  | ICODE<6:0>        |                    |                 |      |

| pit 7                 |                                |                                    |                  |                   |                    |                 | bit  |

| _egend:               |                                | C = Writable                       | bit, but only '0 | )' can be writter | n to clear the bit |                 |      |

| R = Readable          | e bit                          | W = Writable                       | -                |                   | mented bit, read   |                 |      |

| n = Value at          | POR                            | '1' = Bit is set                   | '1' = Bit is set |                   | ared               | x = Bit is unkr | nown |

|                       |                                |                                    |                  |                   |                    |                 |      |

| oit 15-13<br>oit 12-8 | -                              | ted: Read as '<br>Filter Hit Num   |                  |                   |                    |                 |      |

|                       | 10000-1111                     |                                    |                  |                   |                    |                 |      |

|                       | 01111 <b>= Filte</b>           |                                    |                  |                   |                    |                 |      |

|                       | •                              |                                    |                  |                   |                    |                 |      |

|                       | •                              |                                    |                  |                   |                    |                 |      |

|                       | •                              |                                    |                  |                   |                    |                 |      |

|                       | 00001 = Filte<br>00000 = Filte |                                    |                  |                   |                    |                 |      |

| oit 7                 | Unimplemen                     | ted: Read as '                     | 0'               |                   |                    |                 |      |

| oit 6-0               | ICODE<6:0>:                    | Interrupt Flag                     | Code bits        |                   |                    |                 |      |

|                       |                                | 11111 = Rese                       |                  |                   |                    |                 |      |

|                       |                                | IFO almost full<br>eceiver overflo |                  |                   |                    |                 |      |

|                       |                                | /ake-up interru                    |                  |                   |                    |                 |      |

|                       | 1000001 <b>= E</b>             |                                    |                  |                   |                    |                 |      |

|                       | 1000000 <b>= N</b>             | o interrupt                        |                  |                   |                    |                 |      |

|                       | •                              |                                    |                  |                   |                    |                 |      |

|                       | •                              |                                    |                  |                   |                    |                 |      |

|                       |                                | 11111 = Rese                       |                  |                   |                    |                 |      |

|                       | 0001111 <b>= R</b>             | B15 buffer Inte                    | errupt           |                   |                    |                 |      |

|                       | •                              |                                    |                  |                   |                    |                 |      |

|                       | •                              |                                    |                  |                   |                    |                 |      |

|                       | 0001001 <b>= R</b>             | B9 buffer inter                    | rupt             |                   |                    |                 |      |

|                       | 0001000 <b>= R</b>             | B8 buffer inter                    | rupt             |                   |                    |                 |      |

|                       |                                | RB7 buffer inte                    |                  |                   |                    |                 |      |

|                       |                                | RB6 buffer inte<br>RB5 buffer inte |                  |                   |                    |                 |      |

|                       |                                | RB4 buffer inte                    |                  |                   |                    |                 |      |

|                       |                                | RB3 buffer inte                    |                  |                   |                    |                 |      |

|                       | 0000010 = 1                    | RB2 buffer inte                    | TUDI             |                   |                    |                 |      |

|                       |                                | RB1 buffer inte                    |                  |                   |                    |                 |      |

| U-0           | U-0                                                                                     | U-0                                  | U-0              | U-0               | U-0                | U-0             | U-0   |  |

|---------------|-----------------------------------------------------------------------------------------|--------------------------------------|------------------|-------------------|--------------------|-----------------|-------|--|

| _             | _                                                                                       | _                                    | _                | —                 | _                  | _               | _     |  |

| bit 15        |                                                                                         |                                      |                  |                   |                    |                 | bit 8 |  |

|               |                                                                                         |                                      |                  |                   |                    |                 |       |  |

| R/W-0         | R/W-0                                                                                   | R/W-0                                | U-0              | R/W-0             | R/W-0              | R/W-0           | R/W-0 |  |

| IVRIE         | WAKIE                                                                                   | ERRIE                                |                  | FIFOIE            | RBOVIE             | RBIE            | TBIE  |  |

| bit 7         |                                                                                         |                                      |                  |                   |                    |                 | bit ( |  |

| Legend:       |                                                                                         | C = Writable b                       | oit. but only '( | )' can be writter | n to clear the bit |                 |       |  |

| R = Readabl   | e bit                                                                                   | W = Writable                         |                  |                   | mented bit, read   |                 |       |  |

| -n = Value at |                                                                                         | '1' = Bit is set                     |                  | '0' = Bit is cle  |                    | x = Bit is unkr | iown  |  |

|               |                                                                                         |                                      |                  |                   |                    |                 |       |  |

| bit 15-8      | Unimplemer                                                                              | nted: Read as '                      | )'               |                   |                    |                 |       |  |

| bit 7         | IVRIE: Invalio                                                                          | d Message Rec                        | eived Interru    | pt Enable bit     |                    |                 |       |  |

|               |                                                                                         | Request Enable                       |                  |                   |                    |                 |       |  |

|               |                                                                                         | Request not en                       |                  |                   |                    |                 |       |  |

| bit 6         |                                                                                         | Wake-up Activi                       |                  | lag bit           |                    |                 |       |  |

|               |                                                                                         | Request Enable                       |                  |                   |                    |                 |       |  |

| L:1 F         |                                                                                         | Request not en                       |                  |                   |                    |                 |       |  |

| bit 5         |                                                                                         | Interrupt Enab                       |                  |                   |                    |                 |       |  |

|               |                                                                                         | Request Enable<br>Request not en     |                  |                   |                    |                 |       |  |

| bit 4         | -                                                                                       |                                      |                  |                   |                    |                 |       |  |

|               | -                                                                                       | nted: Read as '(                     |                  | a hit             |                    |                 |       |  |

| bit 3         |                                                                                         | D Almost Full Inf<br>Request Enable  |                  | ebit              |                    |                 |       |  |

|               |                                                                                         | Request not en                       |                  |                   |                    |                 |       |  |

| bit 2         | -                                                                                       | -                                    |                  | nable bit         |                    |                 |       |  |

|               | <b>RBOVIE:</b> RX Buffer Overflow Interrupt Enable bit<br>1 = Interrupt Request Enabled |                                      |                  |                   |                    |                 |       |  |

|               | 0 = Interrupt Request not enabled                                                       |                                      |                  |                   |                    |                 |       |  |

| bit 1         | RBIE: RX Bu                                                                             | RBIE: RX Buffer Interrupt Enable bit |                  |                   |                    |                 |       |  |

|               |                                                                                         | 1 = Interrupt Request Enabled        |                  |                   |                    |                 |       |  |

|               |                                                                                         | Request not en                       |                  |                   |                    |                 |       |  |

| bit 0         |                                                                                         | ffer Interrupt En                    |                  |                   |                    |                 |       |  |

|               | 1 = Interrupt Request Enabled                                                           |                                      |                  |                   |                    |                 |       |  |

|               | 0 = Interrupt Request not enabled                                                       |                                      |                  |                   |                    |                 |       |  |

#### 21.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices have up to 13 ADC input channels.

The AD12B bit (AD1CON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

#### 21.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 13 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported

Depending on the particular device pinout, the ADC can have up to 13 analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs can be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration depends on the specific device.

Block diagrams of the ADC module are shown in Figure 21-1 and Figure 21-2.

#### 21.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (AD1PCFGH<15:0> or AD1PCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (AD1CON3<7:0>)

- d) Determine how many S/H channels are used (AD1CON2<9:8> and AD1PCFGH<15:0> or AD1PCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>)

- f) Select how conversion results are presented in the buffer (AD1CON1<9:8>)

- g) Turn on ADC module (AD1CON1<15>)

- 2. Configure ADC interrupt (if required):

- a) Clear the AD1IF bit

- b) Select ADC interrupt priority

#### 21.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. ADC1 can trigger a DMA data transfer. If ADC1 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF bit gets set as a result of an ADC1 sample conversion sequence.

The SMPI<3:0> bits (AD1CON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (AD1CON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module provides an address to the DMA channel that is the same as the address used for the non-DMA standalone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module provides a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

| U-0                                                                  | U-0   | U-0   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|------------------------------------|-------|-------|-------|-------|

| _                                                                    | _     | —     | CSS12                              | CSS11 | CSS10 | CSS9  | CSS8  |

| bit 15                                                               |       |       |                                    |       |       | -     | bit 8 |

|                                                                      |       |       |                                    |       |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CSS7                                                                 | CSS6  | CSS5  | CSS4                               | CSS3  | CSS2  | CSS1  | CSS0  |

| bit 7                                                                |       | ·     |                                    |       |       | -     | bit 0 |

|                                                                      |       |       |                                    |       |       |       |       |

| Legend:                                                              |       |       |                                    |       |       |       |       |

| R = Readable bit W = Writable bit                                    |       | oit   | U = Unimplemented bit, read as '0' |       |       |       |       |

| n = Value at POR (1' = Bit is set 0' = Bit is cleared x = Bit is unk |       |       | nown                               |       |       |       |       |

#### REGISTER 21-7: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-12 Unimplemented: Read as '0'

bit 11-0 CSS<11:0>: ADC Input Scan Selection bits

1 = Select ANx for input scan

0 = Skip ANx for input scan

**Note 1:** On devices without 13 analog inputs, all AD1CSSL bits can be selected by the user application. However, inputs selected for scan without a corresponding input on device converts VREFL.

**2:** CSSx = ANx, where x = 0 through 12.

#### **REGISTER 21-8:** AD1PCFGL: ADC1 PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup>

| U-0     | U-0   | U-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|---------|-------|-------|--------|--------|--------|-------|-------|

| _       | —     | —     | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 15  |       |       |        |        |        |       | bit 8 |

|         |       |       |        |        |        |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| PCFG7   | PCFG6 | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1 | PCFG0 |

| bit 7   |       |       |        |        |        |       | bit 0 |

|         |       |       |        |        |        |       |       |

| Legend: |       |       |        |        |        |       |       |

| <b>L</b> ogona.   |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12-0 PCFG<12:0>: ADC Port Configuration Control bits

- 1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

## **Note 1:** On devices without 13 analog inputs, all PCFG bits are R/W by user software. However, the PCFG bits are ignored on ports without a corresponding input on device.

- **2:** PCFGx = ANx, where x = 0 through 12.

- **3:** PCFGx bits have no effect if ADC module is disabled by setting ADxMD bit in the PMDx Register. In this case all port pins multiplexed with ANx will be in Digital mode.

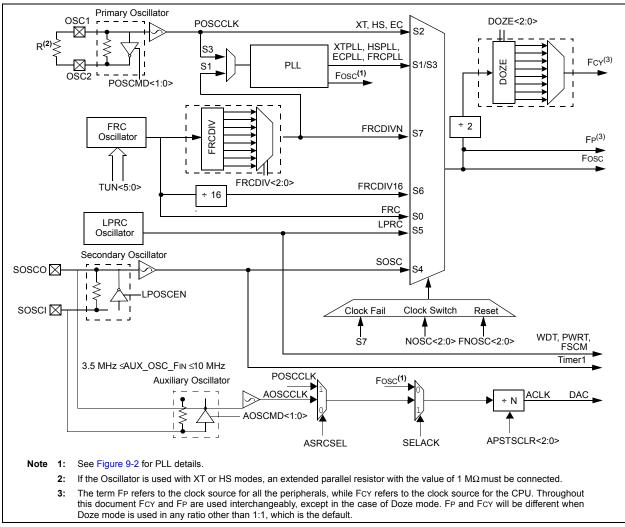

#### FIGURE 30-5: TIMER1, 2, 3 AND 4 EXTERNAL CLOCK TIMING CHARACTERISTICS

## TABLE 30-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

|              |           |                                                                        |                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq T_A \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq T_A \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                               |     |                  |       |                                          |

|--------------|-----------|------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|------------------|-------|------------------------------------------|

| Param<br>No. | Symbol    | Charact                                                                | eristic                     |                                                                                                                                                                                                                                                                                           | Min                                           | Тур | Мах              | Units | Conditions                               |

| TA10         | ТтхН      | TxCK High Time                                                         | Synchro<br>no prese         |                                                                                                                                                                                                                                                                                           | Тсү + 20                                      |     |                  | ns    | Must also meet parameter TA15.           |

|              |           |                                                                        | Synchro<br>with pre         |                                                                                                                                                                                                                                                                                           | (Tcy + 20)/N                                  |     |                  | ns    | N = prescale<br>value                    |

|              |           |                                                                        | Asynchr                     | onous                                                                                                                                                                                                                                                                                     | 20                                            |     | —                | ns    | (1, 8, 64, 256)                          |

| TA11         |           |                                                                        | Synchro<br>no prese         |                                                                                                                                                                                                                                                                                           | (Tcy + 20)                                    |     | —                | ns    | Must also meet parameter TA15.           |

|              |           |                                                                        | Synchronous, with prescaler |                                                                                                                                                                                                                                                                                           | (Tcy + 20)/N                                  | _   | —                | ns    | N = prescale<br>value                    |

|              |           |                                                                        | Asynchr                     | onous                                                                                                                                                                                                                                                                                     | 20                                            | _   | _                | ns    | (1, 8, 64, 256)                          |

| TA15         | ΤτχΡ      | TxCK Input<br>Period                                                   | Synchro<br>no prese         |                                                                                                                                                                                                                                                                                           | 2 Tcy + 40                                    | _   | —                | ns    | —                                        |

|              |           |                                                                        | Synchro<br>with pre         |                                                                                                                                                                                                                                                                                           | Greater of:<br>40 ns or<br>(2 TCY + 40)/<br>N | _   | _                | _     | N = prescale<br>value<br>(1, 8, 64, 256) |

|              |           |                                                                        | Asynchr                     | onous                                                                                                                                                                                                                                                                                     | 40                                            | _   | _                | ns    | —                                        |

| OS60         | Ft1       | SOSCI/T1CK Osc<br>frequency Range<br>enabled by setting<br>(T1CON<1>)) | (oscillator                 |                                                                                                                                                                                                                                                                                           | DC                                            |     | 50               | kHz   | —                                        |

| TA20         | TCKEXTMRL | Delay from Extern<br>Edge to Timer Inc                                 |                             | Clock                                                                                                                                                                                                                                                                                     | 0.75 Tcy +<br>40                              |     | 1.75 Tcy +<br>40 | _     |                                          |

Note 1: Timer1 is a Type A.

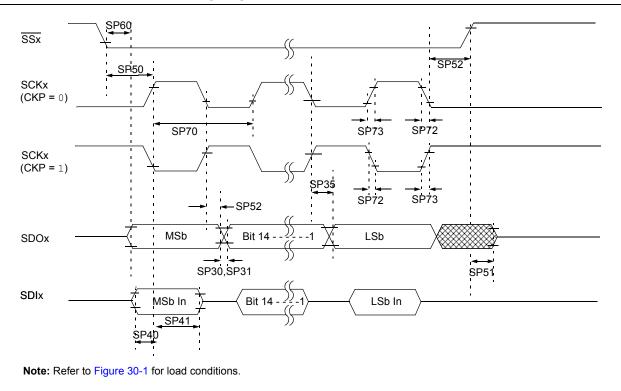

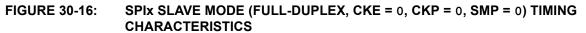

## FIGURE 30-14: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS |                                                                                                                |                                                                                                                             | <b>Standar</b><br>(unless<br>Operatir | <b>∷ 3.0V to 3.6V</b><br>≤TA ≤+150°C for High<br>rature |      |                                                |                                                     |

|--------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------|------|------------------------------------------------|-----------------------------------------------------|

| Param.             | Symbol                                                                                                         | Characteristic                                                                                                              | Min.                                  | Тур.                                                    | Max. | Units                                          | Conditions                                          |

|                    |                                                                                                                | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - RA2, RA7-<br>RA10, RB10, RB11, RB7, RB4,<br>RC3-RC9                |                                       | _                                                       | 0.4  | V                                              | lo∟ ≤1.8 mA, VDD = 3.3V<br>See <b>Note 1</b>        |

| DO10               | Vol                                                                                                            | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - RA0, RA1,<br>RB0-RB3, RB5, RB6, RB8, RB9,<br>RB12-RB15, RC0-RC2    | _                                     | _                                                       | 0.4  | v                                              | IoL ≤3.6 mA, VDD = 3.3V<br>See <b>Note 1</b>        |

|                    |                                                                                                                | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - RA3, RA4                                                           | _                                     | _                                                       | 0.4  | V                                              | Io∟ ⊴6 mA, VDD = 3.3V<br>See <b>Note 1</b>          |

| DO20 Vон           | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,<br>RB11, RC3-RC9 | 2.4                                                                                                                         | _                                     | _                                                       | V    | lo∟ ≥ -1.8 mA, Vod = 3.3V<br>See <b>Note 1</b> |                                                     |

|                    | Vон                                                                                                            | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA0,<br>RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2 | 2.4                                   | _                                                       | _    | v                                              | lo∟ ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>        |

|                    |                                                                                                                | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - RA4,<br>RA3                                                     | 2.4                                   | _                                                       | _    | V                                              | IoL ≥ -6 mA, VDD <b>=</b> 3.3V<br>See <b>Note 1</b> |

|                    |                                                                                                                | Output High Voltage                                                                                                         | 1.5                                   | _                                                       | _    |                                                | IOH ≥ -1.9 mA, VDD = 3.3V<br>See <b>Note 1</b>      |

|                    |                                                                                                                | 2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,<br>RB11, RC3-RC9                                                  | 2.0                                   | —                                                       | _    | V                                              | Іон ≥ -1.85 mA, Vod = 3.3V<br>See <b>Note 1</b>     |

|                    |                                                                                                                | ,                                                                                                                           | 3.0                                   | —                                                       | _    |                                                | IOH ≥ -1.4 mA, VDD = 3.3V<br>See <b>Note 1</b>      |

|                    |                                                                                                                | Output High Voltage<br>4x Source Driver Pins - RA0,                                                                         | 1.5                                   | _                                                       | _    |                                                | Іон ≥ -3.9 mA, VDD = 3.3V<br>See <b>Note 1</b>      |

| DO20A              | Vон1                                                                                                           | RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2                                                                     | 2.0                                   | _                                                       |      | V                                              | IOH ≥ -3.7 mA, VDD = 3.3V<br>See <b>Note 1</b>      |