Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Detalls                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp202-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.5 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532311              |

### 3.5.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0             | U-0                            | U-0                                    | R/W-0                             | R/W-0                        | R-0             | R-0              | R-0         |

|-----------------|--------------------------------|----------------------------------------|-----------------------------------|------------------------------|-----------------|------------------|-------------|

| _               | _                              |                                        | US                                | EDT <sup>(1)</sup>           |                 | DL<2:0>          |             |

| pit 15          |                                | ·                                      |                                   |                              |                 |                  | bit 8       |

| R/W-0           | D/M/ O                         |                                        | R/W-0                             |                              |                 | R/W-0            |             |

| SATA            | R/W-0<br>SATB                  | R/W-1<br>SATDW                         | ACCSAT                            | R/C-0<br>IPL3 <sup>(2)</sup> | R/W-0<br>PSV    | R/W-0            | R/W-0<br>IF |

| bit 7           | SAID                           | SAIDW                                  | ACCSAT                            | IFL3' /                      | F3V             | RND              | bit         |

| Legend:         |                                | C = Clear on                           | y bit                             |                              |                 |                  |             |

| R = Readable    | e bit                          | W = Writable                           | bit                               | -n = Value at                | -               | '1' = Bit is set |             |

| 0' = Bit is cle | ared                           | ʻx = Bit is unk                        | nown                              | U = Unimplen                 | nented bit, rea | ad as '0'        |             |

| bit 15-13       | Unimplemer                     | nted: Read as                          | 0'                                |                              |                 |                  |             |

| bit 12          | •                              | Itiply Unsigned                        |                                   | ol bit                       |                 |                  |             |

|                 |                                | ine multiplies a                       | -                                 |                              |                 |                  |             |

|                 | •                              | ine multiplies a                       | •                                 |                              |                 |                  |             |

| bit 11          | EDT: Early D                   | O Loop Termina                         | ation Control b                   | it <sup>(1)</sup>            |                 |                  |             |

|                 | 1 = Terminate<br>0 = No effect | e executing DO                         | loop at end of                    | current loop ite             | eration         |                  |             |

| bit 10-8        | DL<2:0>: DO                    | Loop Nesting                           | Level Status bi                   | its                          |                 |                  |             |

|                 | 111 <b>= 7</b> do <b>k</b>     | oops active                            |                                   |                              |                 |                  |             |

|                 | •                              |                                        |                                   |                              |                 |                  |             |

|                 | •<br>001 = 1 DO lo             | oon active                             |                                   |                              |                 |                  |             |

|                 | 000 = 0 DO lo                  | •                                      |                                   |                              |                 |                  |             |

| bit 7           | SATA: ACCA                     | Saturation En                          | able bit                          |                              |                 |                  |             |

|                 |                                | ator A saturatio<br>ator A saturatio   |                                   |                              |                 |                  |             |

| bit 6           | SATB: ACCE                     | 3 Saturation En                        | able bit                          |                              |                 |                  |             |

|                 |                                | ator B saturatio<br>ator B saturatio   |                                   |                              |                 |                  |             |

| bit 5           | SATDW: Dat                     | a Space Write                          | from DSP Eng                      | ine Saturation               | Enable bit      |                  |             |

|                 |                                | ce write satura<br>ce write satura     |                                   |                              |                 |                  |             |

| bit 4           | ACCSAT: Ac                     | cumulator Satu                         | ration Mode S                     | elect bit                    |                 |                  |             |

|                 |                                | iration (super s<br>iration (normal    |                                   |                              |                 |                  |             |

| bit 3           |                                | nterrupt Priority                      |                                   |                              |                 |                  |             |

|                 |                                | rrupt priority le<br>rrupt priority le | 0                                 |                              |                 |                  |             |

| bit 2           | PSV: Program                   | m Space Visibil                        | ity in Data Spa                   | ice Enable bit               |                 |                  |             |

|                 |                                | space visible in                       |                                   |                              |                 |                  |             |

| L:1 1           | •                              | space not visit                        | •                                 | ce                           |                 |                  |             |

| bit 1           |                                | ing Mode Sele                          |                                   | d                            |                 |                  |             |

|                 | 0 = Unbiased                   | conventional) ro<br>d (convergent)     | rounding enab                     | led                          |                 |                  |             |

| bit 0           | -                              | Fractional Mu                          | -                                 |                              |                 |                  |             |

|                 | 1 = Integer m                  | node enabled for                       | or DSP multiply<br>d for DSP mult |                              |                 |                  |             |

**Note 1:** This bit is always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

### TABLE 4-2:CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ128GP202/802, dsPIC33FJ64GP202/802 AND dsPIC33FJ32GP302

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|--------|-------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | _      | _     | _       | CN7IE   | CN6IE   | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE   | 0000          |

| CNEN2       | 0062        |         | CN30IE  | CN29IE  | -       | CN27IE  |        | —     | CN24IE  | CN23IE  | CN22IE  | CN21IE  | —      | _      | _      | -      | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE |        | _     | -       | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE |         | CN27PUE | _      | _     | CN24PUE | CN23PUE | CN22PUE | CN21PUE | —      |        |        | _      | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ128GP204/804, dsPIC33FJ64GP204/804 AND dsPIC33FJ32GP304

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE   | CN8IE   | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | CN30IE  | CN29IE  | CN28IE  | CN27IE  | CN26IE  | CN25IE  | CN24IE  | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE  | CN8PUE  | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE | CN28PUE | CN27PUE | CN26PUE | CN25PUE | CN24PUE | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| <b>REGISTER 5-2</b> | : NVM | KEY: NONVOLA     | TILE ME | MORY KEY RI       | EGISTER         |                 |       |

|---------------------|-------|------------------|---------|-------------------|-----------------|-----------------|-------|

| U-0                 | U-0   | U-0              | U-0     | U-0               | U-0             | U-0             | U-0   |

| —                   | _     | —                | —       | —                 | —               | —               | —     |

| bit 15              |       |                  |         |                   |                 |                 | bit 8 |

| W-0                 | W-0   | W-0              | W-0     | W-0               | W-0             | W-0             | W-0   |

|                     |       |                  | NVM     | (EY<7:0>          |                 |                 |       |

| bit 7               |       |                  |         |                   |                 |                 | bit 0 |

| Legend:             |       |                  |         |                   |                 |                 |       |

| R = Readable bi     | t     | W = Writable bi  | it      | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at PC    | R     | '1' = Bit is set |         | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register (write-only) bits

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 38. "Direct Memory Access (DMA) (Part III)" (DS70215) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer), and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association         | DMAxREQ Register<br>IRQSEL<6:0> Bits | DMAxPAD Register<br>Values to Read from<br>Peripheral | DMAxPAD Register<br>Values to Write to<br>Peripheral |

|---------------------------------------|--------------------------------------|-------------------------------------------------------|------------------------------------------------------|

| INT0 – External Interrupt 0           | 0000000                              | —                                                     | —                                                    |

| IC1 – Input Capture 1                 | 000001                               | 0x0140 (IC1BUF)                                       | —                                                    |

| OC1 – Output Compare 1 Data           | 0000010                              | —                                                     | 0x0182 (OC1R)                                        |

| OC1 – Output Compare 1 Secondary Data | 0000010                              | —                                                     | 0x0180 (OC1RS)                                       |

| IC2 – Input Capture 2                 | 0000101                              | 0x0144 (IC2BUF)                                       | —                                                    |

| OC2 – Output Compare 2 Data           | 0000110                              | —                                                     | 0x0188 (OC2R)                                        |

| OC2 – Output Compare 2 Secondary Data | 0000110                              | —                                                     | 0x0186 (OC2RS)                                       |

| TMR2 – Timer2                         | 0000111                              | —                                                     | —                                                    |

| TMR3 – Timer3                         | 0001000                              | —                                                     | —                                                    |

| SPI1 – Transfer Done                  | 0001010                              | 0x0248 (SPI1BUF)                                      | 0x0248 (SPI1BUF)                                     |

| UART1RX – UART1 Receiver              | 0001011                              | 0x0226 (U1RXREG)                                      | —                                                    |

| UART1TX – UART1 Transmitter           | 0001100                              | —                                                     | 0x0224 (U1TXREG)                                     |

| ADC1 – ADC1 convert done              | 0001101                              | 0x0300 (ADC1BUF0)                                     | —                                                    |

| UART2RX – UART2 Receiver              | 0011110                              | 0x0236 (U2RXREG)                                      | —                                                    |

| UART2TX – UART2 Transmitter           | 0011111                              | —                                                     | 0x0234 (U2TXREG)                                     |

| SPI2 – Transfer Done                  | 0100001                              | 0x0268 (SPI2BUF)                                      | 0x0268 (SPI2BUF)                                     |

| ECAN1 – RX Data Ready                 | 0100010                              | 0x0440 (C1RXD)                                        | —                                                    |

| PMP – Master Data Transfer            | 0101101                              | 0x0608 (PMDIN1)                                       | 0x0608 (PMDIN1)                                      |

| ECAN1 – TX Data Request               | 1000110                              | —                                                     | 0x0442 (C1TXD)                                       |

| DCI – Codec Transfer Done             | 0111100                              | 0x0290 (RXBUF0)                                       | 0x0298 (TXBUF0)                                      |

| DAC1 – Right Data Output              | 1001110                              | —                                                     | 0x03F6 (DAC1RDAT)                                    |

| DAC2 – Left Data Output               | 1001111                              | —                                                     | 0x03F8 (DAC1LDAT)                                    |

## TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

| REGISTER      | 9-2: CLKD                  | DIV: CLOCK DI       | VISOR RE           | GISTER <sup>(2)</sup> |                 |                    |           |

|---------------|----------------------------|---------------------|--------------------|-----------------------|-----------------|--------------------|-----------|

| R/W-0         | R/W-0                      | R/W-1               | R/W-1              | R/W-0                 | R/W-0           | R/W-0              | R/W-0     |

| ROI           |                            | DOZE<2:0>           |                    | DOZEN <sup>(1)</sup>  |                 | FRCDIV<2:0>        |           |

| bit 15        |                            |                     |                    |                       |                 |                    | bit 8     |

| R/W-0         | R/W-1                      | U-0                 | R/W-0              | R/W-0                 | R/W-0           | R/W-0              | R/W-0     |

| PLLPC         | ST<1:0>                    | —                   |                    |                       | PLLPRE<4:0      | >                  |           |

| bit 7         |                            |                     |                    |                       |                 |                    | bit C     |

| Legend:       |                            | v = Value set f     | rom Configu        | ration bits on P      | OR              |                    |           |

| R = Readable  | a bit                      | W = Writable b      | -                  |                       | nented bit, rea | d as '0'           |           |

| -n = Value at |                            | '1' = Bit is set    | Л                  | '0' = Bit is cle      |                 |                    |           |

|               | PUR                        | I = DILIS SEL       |                    |                       | areu            | x = Bit is unki    | IOWII     |

| bit 15        | ROI: Recove                | er on Interrupt bit |                    |                       |                 |                    |           |

|               |                            | ts clears the DO    |                    | the processor c       | lock/periphera  | l clock ratio is s | et to 1:1 |

|               |                            | ts have no effect   |                    |                       |                 |                    |           |

| bit 14-12     | DOZE<2:0>                  | Processor Cloc      | k Reduction        | Select bits           |                 |                    |           |

|               | 111 = Fcy/1                | 28                  |                    |                       |                 |                    |           |

|               | 110 = Fcy/6                |                     |                    |                       |                 |                    |           |

|               | 101 = Fcy/3                |                     |                    |                       |                 |                    |           |

|               | 100 = Fcy/1<br>011 = Fcy/8 |                     |                    |                       |                 |                    |           |

|               | 010 = Fcy/4                |                     |                    |                       |                 |                    |           |

|               | 001 = Fcy/2                |                     |                    |                       |                 |                    |           |

|               | 000 = Fcy/1                |                     |                    |                       |                 |                    |           |

| bit 11        | DOZEN: Doz                 | ze Mode Enable      | bit <sup>(1)</sup> |                       |                 |                    |           |

|               |                            | 2:0> field specifie |                    |                       | ipheral clocks  | and the process    | or clocks |

| bit 10-8      |                            | >: Internal Fast    |                    |                       | S               |                    |           |

|               | 111 <b>= FRC (</b>         | divide by 256       |                    |                       |                 |                    |           |

|               | 110 <b>= FRC d</b>         |                     |                    |                       |                 |                    |           |

|               | 101 <b>= FRC d</b>         |                     |                    |                       |                 |                    |           |

|               | 100 <b>= FRC</b> (         |                     |                    |                       |                 |                    |           |

|               | 011 = FRC o<br>010 = FRC o |                     |                    |                       |                 |                    |           |

|               | 010 = FRC (<br>001 = FRC ( | -                   |                    |                       |                 |                    |           |

|               |                            | divide by 1 (defai  | ult)               |                       |                 |                    |           |

| bit 7-6       |                            | I:0>: PLL VCO C     | -                  | er Select bits (al    | so denoted as   | 'N2', PLL posts    | caler)    |

|               | 11 = Output/               |                     |                    |                       |                 | , .                | ,         |

|               | 10 = Reserv                |                     |                    |                       |                 |                    |           |

|               | 01 = Output/               |                     |                    |                       |                 |                    |           |

|               | 00 = Output/               | 2                   |                    |                       |                 |                    |           |

| bit 5         | Unimpleme                  | nted: Read as '0    | ,                  |                       |                 |                    |           |

| bit 4-0       | PLLPRE<4:                  | 0>: PLL Phase D     | etector Inpu       | ıt Divider bits (a    | lso denoted as  | s 'N1', PLL pres   | caler)    |

|               | 11111 <b>= Inp</b>         | ut/33               |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | •                          |                     |                    |                       |                 |                    |           |

|               | 00000 <b>= Inp</b>         | ut/2 (default)      |                    |                       |                 |                    |           |

|               | 00001 = Inp                |                     |                    |                       |                 |                    |           |

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

**Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

2: This register is reset only on a Power-on Reset (POR).

### 11.9 Peripheral Pin Select Registers

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 family of devices implement 33 registers for remappable peripheral configuration:

- 16 Input Remappable Peripheral Registers:

- RPINR0-RPINR1, RPINR3-RPINR4, RPINR7, RPINR10-RPINR11 and PRINR18-RPINR26

- 13 Output Remappable Peripheral Registers:

- RPOR0-RPOR12

| Note: | Inpu | t and Output  | t Re  | gister | valu | es can | only  |

|-------|------|---------------|-------|--------|------|--------|-------|

|       | be   | changed       | if    | the    | IOI  | _OCK   | bit   |

|       | (OS  | CCON<6>)      | is    | set    | to   | '0'.   | See   |

|       | Sec  | tion 11.6.3.1 |       | "Cont  | rol  | Reg    | ister |

|       | Loc  | k" for a spec | cific | comm   | and  | seque  | nce.  |

### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | _   | —   |       |       | INT1R<4:0> |       |       |

| bit 15 |     |     | •     |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 Unimplemented: Read as '0 | Inimplemented: Read as '0' |

|-------------------------------------|----------------------------|

|-------------------------------------|----------------------------|

```

bit 12-8

INT1R<4:0>: Assign External Interrupt 1 (INTR1) to the corresponding RPn pin

1111 = Input tied to Vss

11001 = Input tied to RP25

•

•

00001 = Input tied to RP1

00000 = Input tied to RP0

bit 7-0

Unimplemented: Read as '0'

```

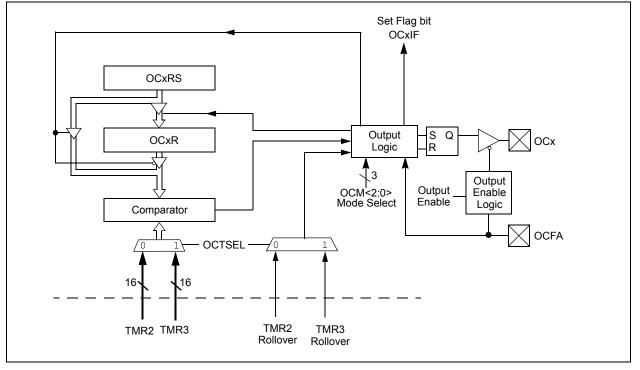

# 15.0 OUTPUT COMPARE

- This data sheet summarizes the features Note 1: of the dsPIC33FJ32GP302/304. dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault protection

- PWM mode with Fault protection

# FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

| R/W-0         | U-0                                                                                                                           | R/W-0                                    | R/W-1 HC                                           | R/W-0                        | R/W-0             | R/W-0                       | R/W-0      |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------|------------------------------|-------------------|-----------------------------|------------|--|--|--|

| I2CEN         | _                                                                                                                             | I2CSIDL                                  | SCLREL                                             | IPMIEN                       | A10M              | DISSLW                      | SMEN       |  |  |  |

| bit 15        |                                                                                                                               |                                          |                                                    |                              |                   | ·                           | bit 8      |  |  |  |

| R/W-0         | R/W-0                                                                                                                         | R/W-0                                    | R/W-0 HC                                           | R/W-0 HC                     | R/W-0 HC          | R/W-0 HC                    | R/W-0 HC   |  |  |  |

| GCEN          | STREN                                                                                                                         | ACKDT                                    | ACKEN                                              | RCEN                         | PEN               | RSEN                        | SEN        |  |  |  |

| bit 7         | SITCEN                                                                                                                        | ACRET                                    | ACKEN                                              | ROEN                         | I LIN             | ROLIN                       | bit (      |  |  |  |

|               |                                                                                                                               |                                          |                                                    | 1                            |                   |                             |            |  |  |  |

| Legend:       |                                                                                                                               | •                                        | mented bit, read                                   |                              |                   |                             |            |  |  |  |

| R = Readable  |                                                                                                                               | W = Writable                             |                                                    | HS = Set in h                |                   | HC = Cleared                |            |  |  |  |

| -n = Value at | POR                                                                                                                           | '1' = Bit is se                          | t                                                  | '0' = Bit is cle             | ared              | x = Bit is unkr             | IOWN       |  |  |  |

| bit 15        | <b>12CEN:</b> 12Cx                                                                                                            | Enable bit                               |                                                    |                              |                   |                             |            |  |  |  |

|               |                                                                                                                               |                                          | le and configure<br>ile. All l <sup>2</sup> C™ pir |                              |                   | as serial port pir<br>tions | าร         |  |  |  |

| bit 14        | Unimplemer                                                                                                                    | ted: Read as                             | ʻ0 <b>'</b>                                        |                              |                   |                             |            |  |  |  |

| bit 13        | I2CSIDL: Sto                                                                                                                  | p in Idle Mode                           | bit                                                |                              |                   |                             |            |  |  |  |

|               |                                                                                                                               |                                          | eration when de<br>tion in Idle mod                |                              | n Idle mode       |                             |            |  |  |  |

| bit 12        | <b>SCLREL:</b> SCLx Release Control bit (when operating as $I^2C$ slave)                                                      |                                          |                                                    |                              |                   |                             |            |  |  |  |

|               | 1 = Release SCLx clock<br>0 = Hold SCLx clock low (clock stretch)                                                             |                                          |                                                    |                              |                   |                             |            |  |  |  |

|               | If STREN = 1:<br>Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear |                                          |                                                    |                              |                   |                             |            |  |  |  |

|               | at beginning of slave transmission. Hardware clear at end of slave reception.                                                 |                                          |                                                    |                              |                   |                             |            |  |  |  |

|               | If STREN = 0                                                                                                                  |                                          |                                                    |                              |                   |                             |            |  |  |  |

|               | Bit is R/S (i.e transmission.                                                                                                 |                                          | only write '1' to                                  | o release cloc               | k). Hardware cl   | ear at beginning            | g of slave |  |  |  |

| bit 11        | IPMIEN: Inte                                                                                                                  | lligent Peripher                         | ral Managemer                                      | nt Interface (IP             | MI) Enable bit    |                             |            |  |  |  |

|               | 1 = IPMI mod<br>0 = IPMI mod                                                                                                  |                                          | all addresses A                                    | cknowledged                  |                   |                             |            |  |  |  |

| bit 10        | A10M: 10-bit                                                                                                                  | Slave Address                            | s bit                                              |                              |                   |                             |            |  |  |  |

|               |                                                                                                                               | ) is a 10-bit slav<br>) is a 7-bit slave |                                                    |                              |                   |                             |            |  |  |  |

| bit 9         | DISSLW: Dis                                                                                                                   | able Slew Rate                           | e Control bit                                      |                              |                   |                             |            |  |  |  |

|               |                                                                                                                               | control disable<br>control enable        |                                                    |                              |                   |                             |            |  |  |  |

| bit 8         | SMEN: SMB                                                                                                                     | us Input Levels                          | s bit                                              |                              |                   |                             |            |  |  |  |

|               |                                                                                                                               | O pin threshold<br>MBus input th         | ls compliant wi<br>resholds                        | th SMBus spe                 | cification        |                             |            |  |  |  |

| bit 7         |                                                                                                                               |                                          | e bit (when ope                                    | rating as I <sup>2</sup> C s | slave)            |                             |            |  |  |  |

|               | 1 = Enable in<br>(module i                                                                                                    |                                          | general call ac                                    | •                            | ,                 | RSR                         |            |  |  |  |

| bit 6         |                                                                                                                               |                                          | h Enable bit (wi                                   | hon operating                | $ac l^2 C alove)$ |                             |            |  |  |  |

|               | SINCH SUL                                                                                                                     |                                          | i Litable bit (Wi                                  | nen operating                | as i U Slave)     |                             |            |  |  |  |

|               | Llood in achi                                                                                                                 | unction with SC                          |                                                    |                              |                   |                             |            |  |  |  |

# REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as $I^2C$ slave)                                                                                                                                                                      |

|       | 1 = Read – indicates data transfer is output from slave<br>0 = Write – indicates data transfer is input to slave<br>Hardware set or clear after reception of $I^2C$ device address byte.                                                     |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

|                                                                            | n (n =                                                                                                                                                                                                                                                                                                                                                                                                             | 0-15)                                               |                  |                  |                   |                |                |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|------------------|-------------------|----------------|----------------|

| R/W-x                                                                      | R/W-x                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-x                                               | R/W-x            | R/W-x            | R/W-x             | R/W-x          | R/W-x          |

| SID10                                                                      | SID9                                                                                                                                                                                                                                                                                                                                                                                                               | SID8                                                | SID7             | SID6             | SID5              | SID4           | SID3           |

| bit 15                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                  |                  |                   |                | bit 8          |

| DAA                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                  |                  |                   |                |                |

| R/W-x<br>SID2                                                              | R/W-x<br>SID1                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-x<br>SID0                                       | U-0              | R/W-x<br>EXIDE   | U-0               | R/W-x<br>EID17 | R/W-x<br>EID16 |

| bit 7                                                                      | 5101                                                                                                                                                                                                                                                                                                                                                                                                               | SIDU                                                | _                | EXIDE            |                   |                | bit 0          |

|                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                  |                  |                   |                | bit 0          |

| Legend:                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    | C = Writable b                                      | oit, but only 'C | )' can be writte | n to clear the bi | t              |                |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as           |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                  |                  | d as '0'          |                |                |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |                  |                  |                   | nown           |                |

| bit 15-5<br>bit 4<br>bit 3                                                 | SID<10:0>: Standard Identifier bits <ol> <li>Message address bit SIDx must be '1' to match filter</li> <li>Message address bit SIDx must be '0' to match filter</li> <li>Mimplemented: Read as '0'</li> <li>EXIDE: Extended Identifier Enable bit</li> <li>If MIDE = 1:</li> <li>Match only messages with extended identifier addresses</li> <li>Match only messages with standard identifier addresses</li> </ol> |                                                     |                  |                  |                   |                |                |

| bit 2<br>bit 1-0                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                  | E bit.<br>I <b>ted:</b> Read as 'i<br>Extended Iden |                  |                  |                   |                |                |

1 = Message address bit EIDx must be '1' to match filter 0 = Message address bit EIDx must be '0' to match filter

### REGISTER 19-16: CIRXFnSID: ECAN<sup>™</sup> ACCEPTANCE FILTER STANDARD IDENTIFIER REGISTER n (n = 0-15)

#### 21.6 **ADC Control Registers**

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0 | R/W-0  |

|--------|-----------|--------|---------|--------|-------|-------|--------|

| ADON   | -         | ADSIDL | ADDMABM | _      | AD12B | FORM  | 1<1:0> |

| bit 15 |           |        |         |        |       |       | bit 8  |

|        |           |        |         |        |       |       |        |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0 | R/C-0  |

|        |           |        |         |        |       | HC,HS | HC, HS |

|        | SSRC<2:0> |        | _       | SIMSAM | ASAM  | SAMP  | DONE   |

| bit 7  |           |        |         |        |       |       | bit 0  |

# REGISTER 21-1: AD1CON1: ADC1 CONTROL REGISTER 1

| L :1  | - |

|-------|---|

| T III |   |

| DIL   |   |

| Legend:           | HC = Cleared by hardware | HS = Set by hardware       | C = Clear only bit |

|-------------------|--------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | ADON: ADC Operating Mode bit<br>1 = ADC module is operating                                                                                                                                                                                                                                                                                                                                               |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = ADC is off                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 13  | <ul> <li>ADSIDL: Stop in Idle Mode bit</li> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                                                                              |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = DMA buffers are written in the order of conversion. The module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer</li> <li>0 = DMA buffers are written in Scatter/Gather mode. The module provides a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 10  | AD12B: 10-bit or 12-bit Operation Mode bit                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = 12-bit, 1-channel ADC operation</li> <li>0 = 10-bit, 4-channel ADC operation</li> </ul>                                                                                                                                                                                                                                                                                                      |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                                                                                                                                                                                                                        |

|         | For 10-bit operation:<br>11 = Signed fractional (Dout = sddd dddd dd00 0000, where s =.NOT.d<9>)<br>10 = Fractional (Dout = dddd dddd dd00 0000)<br>01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                                                                    |

|         | For 12-bit operation:                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)                                                                                                                                                                                                                                                                                                                                 |

|         | 10 = Fractional (Douт = dddd dddd dddd 0000)<br>01 = Signed Integer (Douт = ssss sddd dddd dddd, where s = .NOT.d<11>)                                                                                                                                                                                                                                                                                    |

|         | 00 = Integer (Dout = 0000  ddd  dddd  dddd)                                                                                                                                                                                                                                                                                                                                                               |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>111 = Internal counter ends sampling and starts conversion (auto-convert)</li> <li>110 = Reserved</li> <li>101 = Reserved</li> </ul>                                                                                                                                                                                                                                                             |

|         | 100 = GP timer (Timer5 for ADC1) compare ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                              |

|         | 011 = Reserved<br>010 = GP timer (Timer3 for ADC1) compare ends sampling and starts conversion                                                                                                                                                                                                                                                                                                            |

|         | 001 = Active transition on INT0 pin ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                   |

|         | 000 = Clearing sample bit ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                             |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                           |

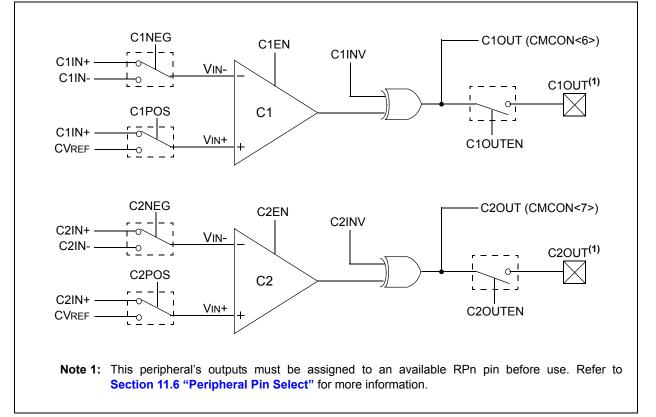

# 23.0 COMPARATOR MODULE

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304. of the dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Comparator" (DS70212) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Comparator module provides a set of dual input comparators. The inputs to the comparator can be configured to use any one of the four pin inputs (C1IN+, C1IN-, C2IN+ and C2IN-) as well as the Comparator Voltage Reference Input (CVREF).

Note: This peripheral contains output functions that may need to be configured by the peripheral pin select feature. For more information, see Section 11.6 "Peripheral Pin Select".

## FIGURE 23-1: COMPARATOR I/O OPERATING MODES

NOTES:

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax       | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------|-----------------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc                   | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                      | ADD   | f                     | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG                | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn             | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd              | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd           | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc        | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC  | f                     | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG                | WREG = f + WREG + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn             | Wd = lit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd              | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd           | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f                     | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | f,WREG                | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | #lit10,Wn             | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd              | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd           | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |

| 4                  | ASR                  | ASR   | f                     | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR   | f,WREG                | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd                 | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR   | Wb,Wns,Wnd            | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd          | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4               | Bit Clear f                              | 1             | 1              | None                     |

|                    |                      | BCLR  | Ws,#bit4              | Bit Clear Ws                             | 1             | 1              | None                     |

| 6                  | BRA                  | BRA   | C,Expr                | Branch if Carry                          | 1             | 1 (2)          | None                     |

| -                  |                      | BRA   | GE, Expr              | Branch if greater than or equal          | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GEU, Expr             | Branch if unsigned greater than or equal | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GT, Expr              | Branch if greater than                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | GTU, Expr             | Branch if unsigned greater than          | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LE, Expr              | Branch if less than or equal             | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LEU, Expr             | Branch if unsigned less than or equal    | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LT,Expr               | Branch if less than                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | LTU, Expr             | Branch if unsigned less than             | 1             | 1 (2)          | None                     |

|                    |                      | BRA   |                       | Branch if Negative                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | N, Expr               | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NC, Expr              | Branch if Not Negative                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NN, Expr<br>NOV, Expr | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |

|                    |                      |       |                       | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | NZ,Expr               | Branch if Accumulator A overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OA, Expr              | Branch if Accumulator B overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA   | OB, Expr              | Branch if Overflow                       | 1             |                | None                     |

|                    |                      | BRA   | OV, Expr              |                                          |               | 1 (2)          | None                     |

|                    |                      | BRA   | SA, Expr              | Branch if Accumulator A saturated        | 1             | 1 (2)          |                          |