#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Decalis                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp202t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Pin Diagrams (Continued)

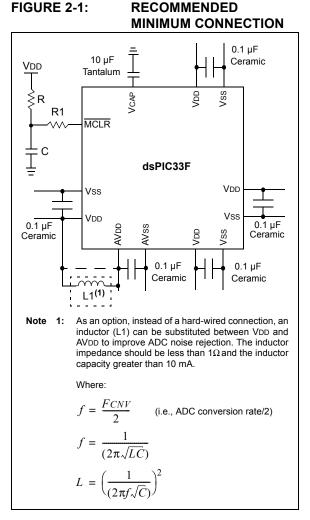

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

#### 2.3 **CPU Logic Filter Capacitor Connection (VCAP)**

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7 µF and 10 µF, preferably surface mount connected within one-eights inch of the VCAP pin connected to ground. The type can be ceramic or tantalum. Refer to Section 30.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-guarter inch (6 mm). Refer to Section 27.2 "On-Chip Voltage Regulator" for details.

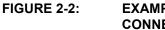

#### Master Clear (MCLR) Pin 2.4

The MCLR pin provides for two specific device functions:

- Device Reset

- · Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### **EXAMPLE OF MCLR PIN** CONNECTIONS

VIH and VIL specifications are met.

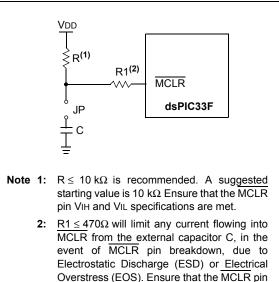

#### 3.4 Special MCU Features

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

#### FIGURE 3-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 CPU CORE BLOCK DIAGRAM

#### 4.0 MEMORY ORGANIZATION

| Note: | This data sheet summarizes the features |

|-------|-----------------------------------------|

|       | of the dsPIC33FJ32GP302/304,            |

|       | dsPIC33FJ64GPX02/X04, and               |

|       | dsPIC33FJ128GPX02/X04 families of       |

|       | devices. It is not intended to be a     |

|       | comprehensive reference source. To      |

|       | complement the information in this data |

|       | sheet, refer to Section 4. "Program     |

|       | Memory" (DS70203) of the "dsPIC33F/     |

|       | PIC24H Family Reference Manual", which  |

|       | is available from the Microchip website |

|       | (www.microchip.com).                    |

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

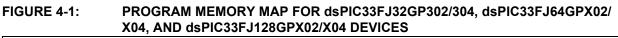

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory map for the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices is shown in Figure 4-1.

|          | GOTO Instruction                                     | GOTO Instruction                                                       | GOTO Instruction                                     | 0x000000                         |

|----------|------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|----------------------------------|

| T        | Reset Address                                        | Reset Address                                                          | Reset Address                                        | 0x000000<br>0x000002             |

|          | Interrupt Vector Table                               | Interrupt Vector Table                                                 | Interrupt Vector Table                               | 0x000004                         |

|          | Reserved                                             | Reserved                                                               | Reserved                                             | 0x0000FE<br>0x000100             |

|          | Alternate Vector Table                               | Alternate Vector Table                                                 | Alternate Vector Table                               | 0x000104<br>0x0001FE             |

| obacc    | User Program<br>Flash Memory<br>(11264 instructions) | User Program<br>– – – – Flash Memory – – – – .<br>(22016 instructions) |                                                      | 0x000200<br>0x0057FE<br>0x005800 |

|          |                                                      |                                                                        | User Program<br>Flash Memory<br>(44032 instructions) | 0x00ABFE<br>0x00AC00             |

|          | Unimplemented                                        |                                                                        |                                                      |                                  |

|          | (Read '0's)                                          | Unimplemented                                                          |                                                      | 0x0157FE                         |

|          |                                                      | (Read '0's)                                                            |                                                      | 0x015800                         |

|          |                                                      |                                                                        | Unimplemented                                        |                                  |

|          |                                                      |                                                                        | (Read '0's)                                          |                                  |

|          |                                                      |                                                                        | (                                                    |                                  |

|          | <b>├</b> ─── <b>├</b>                                | ++                                                                     |                                                      | 0x7FFFFE<br>0x800000             |

|          | Reserved                                             | Reserved                                                               | Reserved                                             |                                  |

|          |                                                      |                                                                        |                                                      | 0xF7FFFE                         |

| ,        | Device Configuration<br>Registers                    | Device Configuration<br>Registers                                      | Device Configuration<br>Registers                    | 0xF80000<br>0xF80017             |

|          |                                                      |                                                                        |                                                      | 0xF80017<br>0xF80018             |

|          | Reserved                                             | Reserved                                                               | Reserved                                             |                                  |

| )        | DEVID (2)                                            |                                                                        | DEVID (2)                                            | 0xFEFFFE<br>0xFF0000             |

|          |                                                      |                                                                        |                                                      | 0xFF0002                         |

| <u> </u> | Reserved                                             | Reserved                                                               | Reserved                                             | 0xFFFFFE                         |

#### 5.2 RTSP Operation

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 30-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

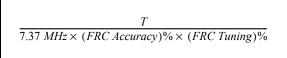

The programming time depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the formula in Equation 5-1 to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 30-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 \ ms$$

The maximum row write time is equal to Equation 5-3.

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

#### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY (Register 5-2) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

#### 5.5 Flash Resources

Many useful resources related to Flash memory are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | product page using the link above, enter    |  |  |  |  |  |

|       | this URL in your browser:                   |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/       |  |  |  |  |  |

|       | Devices.aspx?dDocName=en532311              |  |  |  |  |  |

#### 5.5.1 KEY RESOURCES

- Section 5. "Flash Programming" (DS70191)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 |                                                                                                                                                              |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------|-----------------|-----------------|-------|--|--|--|

| R/W-0                                               | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                | R/W-0           | R/W-0                      | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| NSTDIS                                              | OVAERR                                                                                                                                                       | OVBERR                                                                                                                               | COVAERR         | COVBERR                    | OVATE           | OVBTE           | COVTE |  |  |  |

| bit 15                                              |                                                                                                                                                              |                                                                                                                                      |                 |                            |                 |                 | bit   |  |  |  |

|                                                     |                                                                                                                                                              |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

| R/W-0                                               | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                | R/W-0           | R/W-0                      | R/W-0           | R/W-0           | U-0   |  |  |  |

| SFTACERR                                            | DIV0ERR                                                                                                                                                      | DMACERR                                                                                                                              | MATHERR         | ADDRERR                    | STKERR          | OSCFAIL         | —     |  |  |  |

| bit 7                                               |                                                                                                                                                              |                                                                                                                                      |                 |                            |                 |                 | bit ( |  |  |  |

| Legend:                                             |                                                                                                                                                              |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

| R = Readable                                        | e bit                                                                                                                                                        | W = Writable                                                                                                                         | bit             | U = Unimplem               | ented bit, read | d as '0'        |       |  |  |  |

| -n = Value at                                       |                                                                                                                                                              | '1' = Bit is set                                                                                                                     |                 | '0' = Bit is clea          |                 | x = Bit is unkn | own   |  |  |  |

|                                                     |                                                                                                                                                              |                                                                                                                                      |                 | 0 21110 0100               |                 |                 |       |  |  |  |

| bit 15                                              | NSTDIS: Inte                                                                                                                                                 | rrupt Nesting D                                                                                                                      | isable bit      |                            |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              | nesting is disat                                                                                                                     |                 |                            |                 |                 |       |  |  |  |

|                                                     | •                                                                                                                                                            | nesting is enab                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

| bit 14                                              |                                                                                                                                                              | cumulator A O                                                                                                                        | •               | •                          |                 |                 |       |  |  |  |

|                                                     | •                                                                                                                                                            | caused by ove<br>not caused by                                                                                                       |                 |                            |                 |                 |       |  |  |  |

| bit 13                                              | -                                                                                                                                                            | cumulator B O                                                                                                                        |                 |                            |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              | caused by ove                                                                                                                        | •               | •                          |                 |                 |       |  |  |  |

|                                                     | •                                                                                                                                                            | not caused by                                                                                                                        |                 |                            |                 |                 |       |  |  |  |

| bit 12                                              |                                                                                                                                                              |                                                                                                                                      | -               | Overflow Trap F            | -               |                 |       |  |  |  |

|                                                     | <ul> <li>1 = Trap was caused by catastrophic overflow of Accumulator A</li> <li>0 = Trap was not caused by catastrophic overflow of Accumulator A</li> </ul> |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

| bit 11                                              | -                                                                                                                                                            | -                                                                                                                                    | -               |                            |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              | <b>COVBERR:</b> Accumulator B Catastrophic Overflow Trap Flag bit<br>1 = Trap was caused by catastrophic overflow of Accumulator B   |                 |                            |                 |                 |       |  |  |  |

|                                                     | •                                                                                                                                                            | •                                                                                                                                    | •               | overflow of Accu           |                 |                 |       |  |  |  |

| bit 10                                              |                                                                                                                                                              | umulator A Ove                                                                                                                       | •               | able bit                   |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              | 1 = Trap overflow of Accumulator A                                                                                                   |                 |                            |                 |                 |       |  |  |  |

| hit 0                                               | 0 = Trap disa                                                                                                                                                |                                                                                                                                      | offow Trop En   | abla hit                   |                 |                 |       |  |  |  |

| bit 9                                               |                                                                                                                                                              | <b>OVBTE:</b> Accumulator B Overflow Trap Enable bit<br>1 = Trap overflow of Accumulator B                                           |                 |                            |                 |                 |       |  |  |  |

|                                                     | 0 = Trap disa                                                                                                                                                |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

| bit 8                                               | COVTE: Cata                                                                                                                                                  | astrophic Overf                                                                                                                      | low Trap Enat   | ole bit                    |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              |                                                                                                                                      | erflow of Accur | mulator A or B e           | enabled         |                 |       |  |  |  |

|                                                     | 0 = Trap disa                                                                                                                                                |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

| bit 7                                               |                                                                                                                                                              | Shift Accumula                                                                                                                       |                 | is bit<br>Ilid accumulator | chift           |                 |       |  |  |  |

|                                                     |                                                                                                                                                              |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

| bit 6                                               | DIV0ERR: Ar                                                                                                                                                  | <ul> <li>0 = Math error trap was not caused by an invalid accumulator shift</li> <li>DIV0ERR: Arithmetic Error Status bit</li> </ul> |                 |                            |                 |                 |       |  |  |  |

|                                                     | 1 = Math error trap was caused by a divide by zero                                                                                                           |                                                                                                                                      |                 |                            |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              | or trap was not                                                                                                                      | -               | -                          |                 |                 |       |  |  |  |

| bit 5                                               |                                                                                                                                                              | DMA Controller<br>troller error trap                                                                                                 |                 |                            |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              | troller error trap                                                                                                                   |                 |                            |                 |                 |       |  |  |  |

| bit 4                                               |                                                                                                                                                              | Arithmetic Error                                                                                                                     |                 |                            |                 |                 |       |  |  |  |

|                                                     |                                                                                                                                                              | or trap has occu                                                                                                                     |                 |                            |                 |                 |       |  |  |  |

|                                                     | 0 = Math erro                                                                                                                                                | or trap has not o                                                                                                                    | occurred        |                            |                 |                 |       |  |  |  |

| REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3 |                                    |                  |                |                                      |                 |     |       |  |  |

|------------------------------------------------------|------------------------------------|------------------|----------------|--------------------------------------|-----------------|-----|-------|--|--|

| U-0                                                  | R/W-0                              | R/W-0            | R/W-0          | R/W-0                                | U-0             | U-0 | U-0   |  |  |

| _                                                    | RTCIF                              | DMA5IF           | DCIIF          | DCIEIF                               | —               | —   | _     |  |  |

| bit 15                                               |                                    |                  |                |                                      |                 |     | bit 8 |  |  |

|                                                      |                                    |                  |                |                                      |                 |     |       |  |  |

| U-0                                                  | U-0                                | U-0              | U-0            | U-0                                  | U-0             | U-0 | U-0   |  |  |

|                                                      |                                    |                  | _              |                                      |                 |     |       |  |  |

| bit 7                                                |                                    |                  |                |                                      |                 |     | bit C |  |  |

|                                                      |                                    |                  |                |                                      |                 |     |       |  |  |

| Legend:                                              |                                    |                  |                |                                      |                 |     |       |  |  |

| R = Readabl                                          | le bit                             | W = Writable     | bit            | U = Unimplemented bit, read as '0'   |                 |     |       |  |  |

| -n = Value at                                        | t POR                              | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unkr |                 |     | nown  |  |  |

|                                                      |                                    |                  |                |                                      |                 |     |       |  |  |

| bit 15                                               | Unimplemen                         | ted: Read as '   | 0'             |                                      |                 |     |       |  |  |

| bit 14                                               | RTCIF: Real-                       | Time Clock and   | d Calendar In  | terrupt Flag Sta                     | atus bit        |     |       |  |  |

|                                                      | 1 = Interrupt request has occurred |                  |                |                                      |                 |     |       |  |  |

|                                                      | 0 = Interrupt i                    | equest has not   | occurred       |                                      |                 |     |       |  |  |

| bit 13                                               | DMA5IF: DM                         | A Channel 5 Da   | ata Transfer C | Complete Interr                      | upt Flag Status | bit |       |  |  |

|                                                      |                                    | equest has occ   |                |                                      |                 |     |       |  |  |

|                                                      | 0 = Interrupt i                    | equest has not   | cocurred       |                                      |                 |     |       |  |  |

# REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

**DCIIF:** DCI Event Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

DCIEIF: DCI Error Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

Unimplemented: Read as '0'

bit 12

bit 11

bit 10-0

| R/W-0                  | R/W-0                                                                                                               | U-0              | U-0              | U-0              | U-0              | U-0             | U-0   |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|-----------------|-------|--|--|--|

| DAC1LIF <sup>(2)</sup> | DAC1RIF <sup>(2)</sup>                                                                                              | 00               |                  |                  | 00               |                 |       |  |  |  |

| bit 15                 | DACTRIE                                                                                                             | _                | —                | _                |                  |                 |       |  |  |  |

|                        |                                                                                                                     |                  |                  |                  |                  |                 | bit   |  |  |  |

| U-0                    | R/W-0                                                                                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | U-0   |  |  |  |

| _                      | C1TXIF <sup>(1)</sup>                                                                                               | DMA7IF           | DMA6IF           | CRCIF            | U2EIF            | U1EIF           | _     |  |  |  |

| bit 7                  |                                                                                                                     |                  |                  |                  |                  |                 | bit   |  |  |  |

| Legend:                |                                                                                                                     |                  |                  |                  |                  |                 |       |  |  |  |

| R = Readable           | hit                                                                                                                 | M = M/ritoblo    | hit              | LI – Unimplon    | montod bit rook  |                 |       |  |  |  |

|                        |                                                                                                                     | W = Writable     |                  | •                | nented bit, read |                 | 0.475 |  |  |  |

| -n = Value at F        | POR                                                                                                                 | '1' = Bit is set | [                | '0' = Bit is cle | ared             | x = Bit is unkn | own   |  |  |  |

| bit 15                 | DAC1LIF: DA                                                                                                         | C Left Chann     | el Interrunt Fla | a Status hit(2)  |                  |                 |       |  |  |  |

| Sit TO                 | 1 = Interrupt r                                                                                                     |                  | •                | g clatac bit     |                  |                 |       |  |  |  |

|                        | 0 = Interrupt r                                                                                                     |                  |                  |                  |                  |                 |       |  |  |  |

| bit 14                 | <b>DAC1RIF:</b> DAC Right Channel Interrupt Flag Status bit <sup>(2)</sup>                                          |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 1 = Interrupt request has occurred                                                                                  |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 0 = Interrupt r                                                                                                     | equest has no    | t occurred       |                  |                  |                 |       |  |  |  |

| bit 13-7               | Unimplement                                                                                                         | ed: Read as      | 0'               |                  |                  |                 |       |  |  |  |

| bit 6                  | C1TXIF: ECAN1 Transmit Data Request Interrupt Flag Status bit <sup>(1)</sup>                                        |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 1 = Interrupt request has occurred                                                                                  |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 0 = Interrupt request has not occurred                                                                              |                  |                  |                  |                  |                 |       |  |  |  |

| bit 5                  | DMA7IF: DMA Channel 7 Data Transfer Complete Interrupt Flag Status bit                                              |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 1 = Interrupt request has occurred                                                                                  |                  |                  |                  |                  |                 |       |  |  |  |

| bit 4                  | 0 = Interrupt request has not occurred                                                                              |                  |                  |                  |                  |                 |       |  |  |  |

| 511 4                  | <b>DMA6IF:</b> DMA Channel 6 Data Transfer Complete Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 0 = Interrupt request has occurred                                                                                  |                  |                  |                  |                  |                 |       |  |  |  |

| bit 3                  | CRCIF: CRC Generator Interrupt Flag Status bit                                                                      |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 1 = Interrupt request has occurred                                                                                  |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 0 = Interrupt request has not occurred                                                                              |                  |                  |                  |                  |                 |       |  |  |  |

| bit 2                  | U2EIF: UART2 Error Interrupt Flag Status bit                                                                        |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 1 = Interrupt request has occurred                                                                                  |                  |                  |                  |                  |                 |       |  |  |  |

|                        | 0 = Interrupt request has not occurred                                                                              |                  |                  |                  |                  |                 |       |  |  |  |

| bit 1                  | U1EIF: UART                                                                                                         |                  |                  | bit              |                  |                 |       |  |  |  |

|                        | 1 = Interrupt r<br>0 = Interrupt r                                                                                  |                  |                  |                  |                  |                 |       |  |  |  |

| hit O                  | •                                                                                                                   | •                |                  |                  |                  |                 |       |  |  |  |

| bit 0                  | Unimplement                                                                                                         | eu: Read as      | U                |                  |                  |                 |       |  |  |  |

#### -<u>\_\_\_\_</u>

Note 1: Interrupts are disabled on devices without ECAN<sup>™</sup> modules.

2: Interrupts are disabled on devices without Audio DAC modules.

### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- bit 3 CF: Clock Fail Detect bit (read/clear by application)

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2 Unimplemented: Read as '0'

- bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 39. "Oscillator (Part III)"** (DS70216) in the *"dsPIC33F/PIC24H Family Reference Manual"* (available from the Microchip website) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

#### 11.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 11.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Note: MPLAB<sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: \_\_builtin\_write\_OSCCONL(value) \_\_builtin\_write\_OSCCONH(value) See MPLAB Help for more information.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 11.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset is triggered.

#### 11.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY configuration bit (FOSC<5>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER 11-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4 |                                                         |                                                                                           |       |                  |                 |                 |           |  |  |

|---------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|------------------|-----------------|-----------------|-----------|--|--|

| U-0                                                           | U-0                                                     | U-0                                                                                       | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1     |  |  |

| _                                                             |                                                         |                                                                                           |       |                  | T5CKR<4:0       | >               |           |  |  |

| bit 15                                                        |                                                         |                                                                                           |       |                  |                 |                 | bit       |  |  |

|                                                               |                                                         |                                                                                           |       |                  |                 |                 |           |  |  |

| U-0                                                           | U-0                                                     | U-0                                                                                       | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1     |  |  |

| _                                                             | —                                                       | —                                                                                         |       |                  | T4CKR<4:0       | >               |           |  |  |

| bit 7                                                         |                                                         |                                                                                           |       |                  |                 |                 | bit       |  |  |

| Legend:                                                       |                                                         |                                                                                           |       |                  |                 |                 |           |  |  |

| R = Readabl                                                   | le bit                                                  | W = Writable I                                                                            | oit   | U = Unimpler     | mented bit, rea | ad as '0'       |           |  |  |

| -n = Value at                                                 | t POR                                                   | '1' = Bit is set                                                                          |       | '0' = Bit is cle | ared            | x = Bit is unkı | s unknown |  |  |

|                                                               | 11001 = Inpl                                            | ut tied to RP25                                                                           |       |                  |                 |                 |           |  |  |

|                                                               |                                                         | ut tied to RP1<br>ut tied to RP0                                                          |       |                  |                 |                 |           |  |  |

| bit 7-5                                                       | Unimplemer                                              | nted: Read as 'o                                                                          | )'    |                  |                 |                 |           |  |  |

| bit 4-0                                                       | T4CKR<4:0>                                              | <b>T4CKR&lt;4:0&gt;:</b> Assign Timer4 External Clock (T4CK) to the corresponding RPn pin |       |                  |                 |                 |           |  |  |

|                                                               | 11111 = Input tied to Vss<br>11001 = Input tied to RP25 |                                                                                           |       |                  |                 |                 |           |  |  |

|                                                               | •                                                       |                                                                                           |       |                  |                 |                 |           |  |  |

|                                                               | •                                                       |                                                                                           |       |                  |                 |                 |           |  |  |

|                                                               | •                                                       |                                                                                           |       |                  |                 |                 |           |  |  |

|                                                               |                                                         | ut tied to RP1<br>ut tied to RP0                                                          |       |                  |                 |                 |           |  |  |

### REGISTER 11-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

#### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

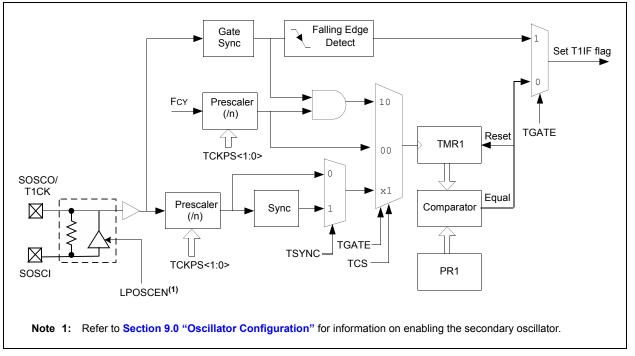

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source.

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

#### TABLE 12-1: TIMER MODE SETTINGS

| Mode                 | TCS | TGATE | TSYNC |

|----------------------|-----|-------|-------|

| Timer                | 0   | 0     | Х     |

| Gated timer          | 0   | 1     | х     |

| Synchronous counter  | 1   | х     | 1     |

| Asynchronous counter | 1   | х     | 0     |

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

# 16.3 SPI Control Registers

## REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0                                 | U-0                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                              | U-0                                                                                           | U-0                       | U-0              | U-0             | U-0           |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|------------------|-----------------|---------------|

| SPIEN                                 |                                                                                                                                                                                                                                                                                                                                                                      | SPISIDL                                                                                                                                                                            | _                                                                                             | —                         |                  | _               | _             |

| bit 15                                |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                    |                                                                                               |                           |                  |                 | bit 8         |

| U-0                                   | R/C-0                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                | U-0                                                                                           | U-0                       |                  |                 |               |

| 0-0                                   | SPIROV                                                                                                                                                                                                                                                                                                                                                               | 0-0                                                                                                                                                                                | 0-0                                                                                           | 0-0                       | U-0              | R-0             | R-0<br>SPIRBF |

| <br>bit 7                             | SPIROV                                                                                                                                                                                                                                                                                                                                                               | —                                                                                                                                                                                  |                                                                                               | —                         |                  | SPITBF          | bit (         |

|                                       |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                    |                                                                                               |                           |                  |                 |               |

| Legend:                               |                                                                                                                                                                                                                                                                                                                                                                      | C = Clearable                                                                                                                                                                      | bit                                                                                           |                           |                  |                 |               |

| R = Readab                            |                                                                                                                                                                                                                                                                                                                                                                      | W = Writable                                                                                                                                                                       | bit                                                                                           | •                         | mented bit, read | l as '0'        |               |

| -n = Value a                          | t POR                                                                                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                                   |                                                                                               | '0' = Bit is cle          | ared             | x = Bit is unkr | nown          |

| bit 14<br>bit 13<br>bit 12-7<br>bit 6 | SPISIDL: Sto<br>1 = Discontinue<br>0 = Continue<br>Unimplemen<br>SPIROV: Rec<br>1 = A new by<br>previous                                                                                                                                                                                                                                                             | module<br>ted: Read as '(<br>p in Idle Mode<br>ue module operati<br>module operati<br>ted: Read as '(<br>ceive Overflow I<br>/te/word is com<br>data in the SPI<br>low has occurre | bit<br>ration when de<br>on in Idle mod<br>o'<br>Flag bit<br>pletely receive<br>xBUF register | de<br>ed and discard      |                  | oftware has not | read the      |

| bit 5-2                               |                                                                                                                                                                                                                                                                                                                                                                      | ted: Read as '                                                                                                                                                                     |                                                                                               |                           |                  |                 |               |

| bit 1                                 | •                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |                                                                                               | bit                       |                  |                 |               |

|                                       | <ul> <li>SPITBF: SPIx Transmit Buffer Full Status bit</li> <li>1 = Transmit not yet started, SPIxTXB is full</li> <li>0 = Transmit started, SPIxTXB is empty</li> <li>Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.</li> <li>Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul> |                                                                                                                                                                                    |                                                                                               |                           |                  |                 |               |

| bit 0                                 | 1 = Receive o<br>0 = Receive is<br>Automatically                                                                                                                                                                                                                                                                                                                     | x Receive Buffe<br>complete, SPIxI<br>s not complete,<br>set in hardward<br>cleared in hard                                                                                        | RXB is full<br>SPIxRXB is e<br>e when SPIx t                                                  | empty<br>rransfers data t |                  |                 | ί <b>Β</b> .  |

| U-0                                                           | U-0   | U-0             | U-0   | U-0                                | U-0   | R/W-0 | R/W-0 |

|---------------------------------------------------------------|-------|-----------------|-------|------------------------------------|-------|-------|-------|

| —                                                             | —     | —               | _     | —                                  | —     | AMSK9 | AMSK8 |

| bit 15                                                        |       |                 |       |                                    |       |       | bit 8 |

|                                                               |       |                 |       |                                    |       |       |       |

| R/W-0                                                         | R/W-0 | R/W-0           | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

| AMSK7                                                         | AMSK6 | AMSK5           | AMSK4 | AMSK3                              | AMSK2 | AMSK1 | AMSK0 |

| bit 7                                                         |       |                 |       |                                    |       |       | bit 0 |

|                                                               |       |                 |       |                                    |       |       |       |