Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp204-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.8.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

## 3.8.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 and 31 for right shifts, and between bit positions 0 and 16 for left shifts.

| TABLE       | 4-4:        | INTERRUPT CONTROLLER REGISTER MAP |                        |            |         |         |        |            |                     |          |                       |             |         |                     |                       |            | -             |               |

|-------------|-------------|-----------------------------------|------------------------|------------|---------|---------|--------|------------|---------------------|----------|-----------------------|-------------|---------|---------------------|-----------------------|------------|---------------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15                            | Bit 14                 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8               | Bit 7    | Bit 6                 | Bit 5       | Bit 4   | Bit 3               | Bit 2                 | Bit 1      | Bit 0         | All<br>Resets |

| INTCON1     | 0080        | NSTDIS                            | OVAERR                 | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE               | SFTACERR | DIV0ERR               | DMACERR     | MATHERR | ADDRERR             | STKERR                | OSCFAIL    | —             | 0000          |

| INTCON2     | 0082        | ALTIVT                            | DISI                   | _          | _       | _       |        | _          |                     | _        | _                     | _           | _       | _                   | INT2EP                | INT1EP     | INT0EP        | 0000          |

| IFS0        | 0084        | —                                 | DMA1IF                 | AD1IF      | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | T3IF                | T2IF     | OC2IF                 | IC2IF       | DMA0IF  | T1IF                | OC1IF                 | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS1        | 0086        | U2TXIF                            | U2RXIF                 | INT2IF     | T5IF    | T4IF    | OC4IF  | OC3IF      | DMA2IF              | IC8IF    | IC7IF                 | _           | INT1IF  | CNIF                | CMIF                  | MI2C1IF    | SI2C1IF       | 0000          |

| IFS2        | 0088        | _                                 | DMA4IF                 | PMPIF      | _       | _       | _      | _          | _                   | _        | _                     | _           | DMA3IF  | C1IF <sup>(1)</sup> | C1RXIF <sup>(1)</sup> | SPI2IF     | SPI2EIF       | 0000          |

| IFS3        | 008A        | _                                 | RTCIF                  | DMA5IF     | DCIIF   | DCIEIF  | -      | —          |                     | —        |                       | _           | _       |                     | _                     | _          |               | 0000          |

| IFS4        | 008C        | DAC1LIF <sup>(2)</sup>            | DAC1RIF <sup>(2)</sup> | —          | —       | _       | -      | —          |                     | —        | C1TXIF <sup>(1)</sup> | DMA7IF      | DMA6IF  | CRCIF               | U2EIF                 | U1EIF      |               | 0000          |

| IEC0        | 0094        | _                                 | DMA1IE                 | AD1IE      | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | T3IE                | T2IE     | OC2IE                 | IC2IE       | DMA0IE  | T1IE                | OC1IE                 | IC1IE      | INT0IE        | 0000          |

| IEC1        | 0096        | U2TXIE                            | U2RXIE                 | INT2IE     | T5IE    | T4IE    | OC4IE  | OC3IE      | DMA2IE              | IC8IE    | IC7IE                 | _           | INT1IE  | CNIE                | CMIE                  | MI2C1IE    | SI2C1IE       | 0000          |

| IEC2        | 0098        | _                                 | DMA4IE                 | PMPIE      | —       | _       | -      | —          |                     | —        |                       | _           | DMA3IE  | C1IE <sup>(1)</sup> | C1RXIE <sup>(1)</sup> | SPI2IE     | SPI2EIE       | 0000          |

| IEC3        | 009A        | _                                 | RTCIE                  | DMA5IE     | DCIIE   | DCIEIE  | -      | —          |                     | —        |                       | _           | _       |                     | _                     | _          |               | 0000          |

| IEC4        | 009C        | DAC1LIE <sup>(2)</sup>            | DAC1RIE <sup>(2)</sup> | —          | —       | _       | -      | —          |                     | —        | C1TXIE <sup>(1)</sup> | DMA7IE      | DMA6IE  | CRCIE               | U2EIE                 | U1EIE      |               | 0000          |

| IPC0        | 00A4        | _                                 | -                      | T1IP<2:0>  |         | _       | (      | DC1IP<2:0  | >                   | —        |                       | IC1IP<2:0>  |         |                     | IN                    | T0IP<2:0>  |               | 4444          |

| IPC1        | 00A6        | _                                 | -                      | T2IP<2:0>  |         | _       | (      | DC2IP<2:0  | >                   | —        |                       | IC2IP<2:0>  |         |                     | DN                    | MA0IP<2:0  | >             | 4444          |

| IPC2        | 00A8        | _                                 | U                      | 1RXIP<2:0  | >       | _       | 95     | SPI1IP<2:0 | >                   | —        |                       | SPI1EIP<2:0 | >       |                     | ٦                     | T3IP<2:0>  |               | 4444          |

| IPC3        | 00AA        | _                                 |                        | —          | —       | _       | D      | MA1IP<2:0  | )>                  | —        |                       | AD1IP<2:0>  |         |                     | U                     | 1TXIP<2:0> | >             | 0444          |

| IPC4        | 00AC        | —                                 | (                      | CNIP<2:0>  |         | —       |        | CMIP<2:0>  | •                   | —        | I                     | WI2C1IP<2:0 | >       | -                   | SI                    | 2C1IP<2:0  | >             | 4444          |

| IPC5        | 00AE        | —                                 | l.                     | C8IP<2:0>  |         | —       |        | IC7IP<2:0> | •                   | —        | -                     | —           | _       | -                   | IN                    | NT1IP<2:0> |               | 4404          |

| IPC6        | 00B0        | —                                 |                        | T4IP<2:0>  |         | —       | (      | DC4IP<2:0  | >                   | —        |                       | OC3IP<2:0>  |         | -                   | DN                    | MA2IP<2:0  | >             | 4444          |

| IPC7        | 00B2        | _                                 | U                      | 2TXIP<2:0  | >       | _       | U      | 2RXIP<2:0  | )>                  | —        |                       | INT2IP<2:0> | •       |                     | ٦                     | T5IP<2:0>  |               | 4444          |

| IPC8        | 00B4        | —                                 | С                      | 1IP<2:0>(1 | )       | —       | C1     | RXIP<2:0   | <sub>&gt;</sub> (1) | —        |                       | SPI2IP<2:0> | •       | -                   | SF                    | PI2EIP<2:0 | >             | 4444          |

| IPC9        | 00B6        | —                                 | —                      | —          | —       | —       | _      | —          | -                   | —        | -                     | —           | _       | -                   | DN                    | MA3IP<2:0  | >             | 0004          |

| IPC11       | 00BA        | —                                 | —                      | —          | —       | —       | D      | MA4IP<2:0  | )>                  | —        |                       | PMPIP<2:0>  | •       | -                   | —                     | —          | _             | 0440          |

| IPC14       | 00C0        | —                                 | D                      | CIEIP<2:0  | >       | —       | _      | —          | -                   | —        | -                     | —           | _       | -                   | —                     | —          | _             | 4000          |

| IPC15       | 00C2        | —                                 | —                      | —          | —       | —       | I      | RTCIP<2:0  | >                   | —        |                       | DMA5IP<2:0  | >       | -                   | D                     | CIIP<2:0>  |               | 0444          |

| IPC16       | 00C4        | —                                 | С                      | RCIP<2:0   | >       | _       | I      | J2EIP<2:0  | >                   | —        |                       | U1EIP<2:0>  |         | _                   | —                     | _          | —             | 4440          |

| IPC17       | 00C6        | —                                 | _                      | _          | —       | _       | C      | TXIP<2:0   | (1)                 | —        |                       | DMA7IP<2:0  | >       | _                   | DN                    | MA6IP<2:0  | >             | 0444          |

| IPC19       | 00CA        | —                                 | DAG                    | C1LIP<2:0  | >(2)    | _       | DA     | C1RIP<2:0  | >(2)                | —        | _                     | _           | _       | _                   | —                     | _          | —             | 4400          |

| INTTREG     | 00E0        | _                                 |                        | _          | —       |         | ILR<3  | :0>>       |                     | —        |                       |             | VEC     | CNUM<6:0>           |                       |            |               | 4444          |

#### TABLE 4-4. INTERRUPT CONTROLLER REGISTER MAP

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

Interrupts disabled on devices without ECAN™ modules. Interrupts disabled on devices without Audio DAC modules. 2:

## TABLE 4-7: OUTPUT COMPARE REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|-------------------------------------|--------|--------|--------|--------|-------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| OC1RS    | 0180        |        |                                     |        |        |        |        | Ou    | tput Compar | e 1 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC1R     | 0182        |        |                                     |        |        |        |        |       | Output Co   | mpare 1 Re  | egister      |       |       |        |       |          |       | XXXX          |

| OC1CON   | 0184        | _      | _                                   | OCSIDL | _      | _      | _      | _     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        | Output Compare 2 Secondary Register |        |        |        |        |       |             |             |              |       | XXXX  |        |       |          |       |               |

| OC2R     | 0188        |        | Output Compare 2 Register           |        |        |        |        |       |             |             |              |       |       | XXXX   |       |          |       |               |

| OC2CON   | 018A        | _      | _                                   | OCSIDL | _      | _      | _      | _     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |                                     |        |        |        |        | Ou    | tput Compar | e 3 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC3R     | 018E        |        |                                     |        |        |        |        |       | Output Co   | mpare 3 Re  | egister      |       |       |        |       |          |       | XXXX          |

| OC3CON   | 0190        | _      | _                                   | OCSIDL | _      | _      | _      | _     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        |                                     |        |        |        |        | Ou    | tput Compar | e 4 Seconda | ary Register |       |       |        |       |          |       | XXXX          |

| OC4R     | 0194        |        | Output Compare 4 Register           |        |        |        |        |       |             |             |              |       |       | XXXX   |       |          |       |               |

| OC4CON   | 0196        | _      | OCSIDL OCFLT OCTSEL OCM<2:0>        |        |        |        |        |       |             |             |              |       |       | 0000   |       |          |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-8: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                 | Bit 7                        | Bit 6 | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-----------------------|------------------------------|-------|-------|----------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | -       | -      | _      | -      | —      | _                     | - Receive Register           |       |       |          |          |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | -                     |                              |       |       | Transmit | Register |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |                       | Baud Rate Generator Register |       |       |          |          |       |       | 0000  |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                  | GCEN                         | STREN | ACKDT | ACKEN    | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT |         | _      | _      | BCL    | GCSTAT | ADD10                 | IWCOL                        | I2COV | D_A   | Р        | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      |         | _      | _      |        |        |                       | Address Register             |       |       |          |          |       |       | 0000  |               |

| I2C1MSK  | 020C        | _       | _      | _       | -      | _      | -      |        | Address Mask Register |                              |       |       |          |          |       | 0000  |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-9: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                        | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                           | Bit 6 | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|-------------------------------|--------|----------|--------|--------|--------|-------|-------|-------------------------------------------------|-------|-------|------------|--------------|-------|-------|-------|---------------|

| U1MODE   | 0220        | UARTEN                        | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0  | WAKE LPBACK ABAUD URXINV BRGH PDSEL<1:0> STSEL  |       |       |            |              |       |       | 0000  |               |

| U1STA    | 0222        | UTXISEL1                      | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | T URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |       |       |            |              |       |       |       | 0110          |

| U1TXREG  | 0224        | _                             | _      | _        | _      | _      | —      | _     | UTX8  |                                                 |       | U     | ART Transm | nit Register |       |       |       | XXXX          |

| U1RXREG  | 0226        | _                             | _      | _        | _      | _      | _      | _     | URX8  | UART Received Register                          |       |       |            |              |       |       |       |               |

| U1BRG    | 0228        | Baud Rate Generator Prescaler |        |          |        |        |        |       |       |                                                 |       |       |            | 0000         |       |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

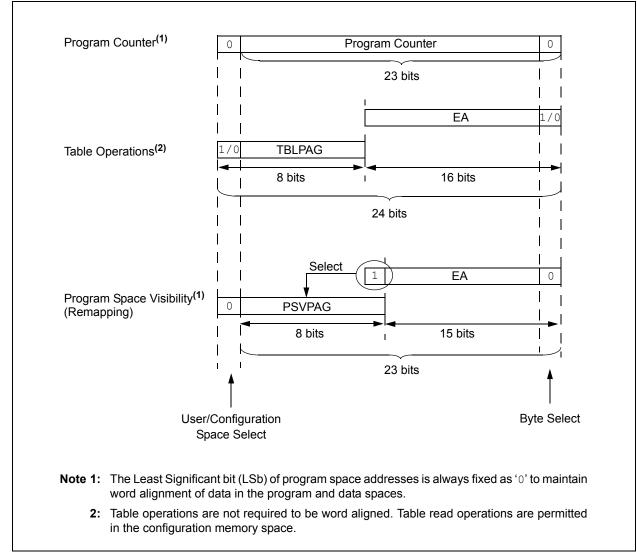

## 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 architecture uses a 24 bit wide program space and a 16 bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## 4.8.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-39 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

## TABLE 4-39: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        | Program Space Address        |           |                     |               |       |  |  |  |  |  |

|--------------------------|---------------|------------------------------|-----------|---------------------|---------------|-------|--|--|--|--|--|

| Access Type              | Space         | <23>                         | <22:16>   | <15>                | <14:1>        | <0>   |  |  |  |  |  |

| Instruction Access       | User          | 0                            |           | PC<22:1>            |               | 0     |  |  |  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                     |               |       |  |  |  |  |  |

| TBLRD/TBLWT              | User          | TB                           | LPAG<7:0> |                     | Data EA<15:0> |       |  |  |  |  |  |

| (Byte/Word Read/Write)   |               | 0                            | XXX XXXX  | XXXX XXXX XXXX XXXX |               |       |  |  |  |  |  |

|                          | Configuration | TB                           | LPAG<7:0> | Data EA<15:0>       |               |       |  |  |  |  |  |

|                          |               | 1                            | XXX XXXX  | XXXX X              | XXX XXXX XXXX |       |  |  |  |  |  |

| Program Space Visibility | User          | 0                            | PSVPAG<7  | <7:0> Data EA<      |               | 0>(1) |  |  |  |  |  |

| (Block Remap/Read)       | 0             | XXXX XXXX                    | ĸ         | XXX XXXX XXXX XXXX  |               |       |  |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

## 4.8.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 0x8000 and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

**Note:** PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop allows the instruction using PSV to access data, to execute in a single cycle.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER      | 7-4: INTC                                                                                                                               | ON2: INTERR                                                     | UPT CONT   | ROL REGIST       | ER 2             |                 |        |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------|------------------|------------------|-----------------|--------|--|--|--|

| R/W-0         | R-0                                                                                                                                     | U-0                                                             | U-0        | U-0              | U-0              | U-0             | U-0    |  |  |  |

| ALTIVT        | DISI                                                                                                                                    | —                                                               |            | —                | _                | _               | —      |  |  |  |

| bit 15        |                                                                                                                                         |                                                                 |            |                  |                  |                 | bit 8  |  |  |  |

| U-0           | U-0                                                                                                                                     | U-0                                                             | U-0        | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| _             | -                                                                                                                                       |                                                                 | -          | -                | INT2EP           | INT1EP          | INT0EP |  |  |  |

| bit 7         |                                                                                                                                         |                                                                 |            |                  |                  |                 | bit 0  |  |  |  |

| Legend:       |                                                                                                                                         |                                                                 |            |                  |                  |                 |        |  |  |  |

| R = Readabl   | e bit                                                                                                                                   | W = Writable                                                    | bit        | U = Unimplei     | mented bit, read | l as '0'        |        |  |  |  |

| -n = Value at | POR                                                                                                                                     | '1' = Bit is set                                                |            | '0' = Bit is cle |                  | x = Bit is unkr | nown   |  |  |  |

| bit 15        | 1 = Use alte                                                                                                                            | able Alternate In<br>ernate vector tabl<br>ndard (default) v    | e          | r Table bit      |                  |                 |        |  |  |  |

| bit 14        | 1 = DISI in                                                                                                                             | Instruction Status<br>struction is active<br>struction is not a | 9          |                  |                  |                 |        |  |  |  |

| bit 13-3      | Unimpleme                                                                                                                               | ented: Read as '                                                | 0'         |                  |                  |                 |        |  |  |  |

| bit 2         | INT2EP: E>                                                                                                                              | ternal Interrupt 2                                              | Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |

|               |                                                                                                                                         | t on negative edg<br>t on positive edg                          |            |                  |                  |                 |        |  |  |  |

| bit 1         | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                                                 |            |                  |                  |                 |        |  |  |  |

## REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

bit 0 INT0EP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge 0 = Interrupt on positive edge

© 2007-2012 Microchip Technology Inc.

## 8.3 DMA Control Registers

#### R/W-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 U-0 U-0 CHEN SIZE DIR HALF NULLW bit 15 bit 8 U-0 U-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 AMODE<1:0> MODE<1:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15 CHEN: Channel Enable bit 1 = Channel enabled 0 = Channel disabled bit 14 SIZE: Data Transfer Size bit 1 = Byte 0 = Word bit 13 DIR: Transfer Direction bit (source/destination bus select) 1 = Read from DMA RAM address, write to peripheral address 0 = Read from peripheral address, write to DMA RAM address HALF: Early Block Transfer Complete Interrupt Select bit bit 12 1 = Initiate block transfer complete interrupt when half of the data has been moved 0 = Initiate block transfer complete interrupt when all of the data has been moved bit 11 NULLW: Null Data Peripheral Write Mode Select bit 1 = Null data write to peripheral in addition to DMA RAM write (DIR bit must also be clear) 0 = Normal operation bit 10-6 Unimplemented: Read as '0' bit 5-4 AMODE<1:0>: DMA Channel Operating Mode Select bits 11 = Reserved (acts as Peripheral Indirect Addressing mode) 10 = Peripheral Indirect Addressing mode 01 = Register Indirect without Post-Increment mode 00 = Register Indirect with Post-Increment mode bit 3-2 Unimplemented: Read as '0' bit 1-0 MODE<1:0>: DMA Channel Operating Mode Select bits 11 = One-Shot, Ping-Pong modes enabled (one block transfer from/to each DMA RAM buffer) 10 = Continuous, Ping-Pong modes enabled 01 = One-Shot, Ping-Pong modes disabled 00 = Continuous, Ping-Pong modes disabled

## REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| R-0               | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0              | R-0   |

|-------------------|-----|------------------|------|----------------------|-------------|------------------|-------|

|                   |     |                  | DSAI | DR<15:8>             |             |                  |       |

| bit 15            |     |                  |      |                      |             |                  | bit 8 |

|                   |     |                  |      |                      |             |                  |       |

| R-0               | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0              | R-0   |

|                   |     |                  | DSA  | DR<7:0>              |             |                  |       |

| bit 7             |     |                  |      |                      |             |                  | bit 0 |

|                   |     |                  |      |                      |             |                  |       |

| Legend:           |     |                  |      |                      |             |                  |       |

| R = Readable bit  |     | W = Writable bit |      | U = Unimplement      | ted bit, re | ad as '0'        |       |

| -n = Value at POR |     | '1' = Bit is set |      | '0' = Bit is cleared | ł           | x = Bit is unkno | own   |

## REGISTER 8-9: DSADR: MOST RECENT DMA RAM ADDRESS

bit 15-0 DSADR<15:0>: Most Recent DMA RAM Address Accessed by DMA Controller bits

#### 9.3 Oscillator Control Registers

#### U-0 R/W-y R/W-y U-0 R-0 R-0 R-0 R/W-y COSC<2:0> NOSC<2:0>(2) bit 15 bit 8 R/W-0 R/W-0 R-0 U-0 R/C-0 U-0 R/W-0 R/W-0 CLKLOCK IOLOCK LOCK CF LPOSCEN OSWEN bit 7 bit 0 y = Value set from Configuration bits on POR Legend: C = Clear only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 COSC<2:0>: Current Oscillator Selection bits (read-only) 111 = Fast RC oscillator (FRC) with Divide-by-n 110 = Fast RC oscillator (FRC) with Divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Secondary oscillator (SOSC) 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primarv oscillator (XT, HS, EC) 001 = Fast RC Oscillator (FRC) with divide-by-N and PLL (FRCDIVN + PLL) 000 = Fast RC oscillator (FRC) Unimplemented: Read as '0' bit 11 bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup> 111 = Fast RC oscillator (FRC) with Divide-by-n 110 = Fast RC oscillator (FRC) with Divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Secondary oscillator (SOSC) 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC Oscillator (FRC) with divide-by-N and PLL (FRCDIVN + PLL) 000 = Fast RC oscillator (FRC) CLKLOCK: Clock Lock Enable bit bit 7 If clock switching is enabled and FSCM is disabled, FCKSM<1:0>(FOSC<7:6>) = 0b01 1 = Clock switching is disabled, system clock source is locked 0 = Clock switching is enabled, system clock source can be modified by clock switching bit 6 IOLOCK: Peripheral Pin Select Lock bit 1 = Peripherial pin select is locked, write to peripheral pin select registers not allowed 0 = Peripherial pin select is not locked, write to peripheral pin select registers allowed bit 5 LOCK: PLL Lock Status bit (read-only) 1 = Indicates that PLL is in lock, or PLL start-up timer is satisfied 0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled bit 4 Unimplemented: Read as '0' Note 1: Writes to this register require an unlock sequence. Refer to Section 39. "Oscillator (Part III)" (DS70216) in the "dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip website) for details. Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. 2: This applies to clock switches in either direction. In these instances, the application must switch to FRC

OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> **REGISTER 9-1:**

- mode as a transition clock source between the two PLL modes.

- 3: This register is reset only on a Power-on Reset (POR).

| TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTIO |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Input Name              | Function Name | Register | Configuration<br>Bits |

|-------------------------|---------------|----------|-----------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>            |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>            |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<4:0>            |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<4:0>            |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7         | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8         | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>            |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| UART2 Receive           | U2RX          | RPINR19  | U2RXR<4:0>            |

| UART2 Clear To Send     | U2CTS         | RPINR19  | U2CTSR<4:0>           |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI1 Clock Input        | SCK1          | RPINR20  | SCK1R<4:0>            |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0>             |

| SPI2 Data Input         | SDI2          | RPINR22  | SDI2R<4:0>            |

| SPI2 Clock Input        | SCK2          | RPINR22  | SCK2R<4:0>            |

| SPI2 Slave Select Input | SS2           | RPINR23  | SS2R<4:0>             |

| DCI Serial Data Input   | CSDI          | RPINR24  | CSDIR<4:0>            |

| DCI Serial Clock Input  | CSCK          | RPINR24  | CSCKR<4:0>            |

| DCI Frame Sync Input    | COFS          | RPINR25  | COFSR<4:0>            |

| ECAN1 Receive           | CIRX          | RPINR26  | CIRXR<4:0>            |

Note 1: Unless otherwise noted, all inputs use Schmitt input buffers.

## **19.6 ECAN Message Buffers**

ECAN Message Buffers are part of DMA RAM Memory. They are not ECAN special function registers. The user application must directly write into the DMA RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

## BUFFER 19-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | _   | SID10 | SID9  | SID8  | SID7  | SID6  |

| bit 15 |     |     |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID5  | SID4  | SID3  | SID2  | SID1  | SID0  | SRR   | IDE   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                    |

|-----------|-----------------------------------------------|

| bit 12-2  | SID<10:0>: Standard Identifier bits           |

| bit 1     | SRR: Substitute Remote Request bit            |

|           | 1 = Message will request remote transmission  |

|           | 0 = Normal message                            |

| bit 0     | IDE: Extended Identifier bit                  |

|           | 1 = Message will transmit extended identifier |

|           | 0 = Message will transmit standard identifier |

## BUFFER 19-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0    | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      | —   | _   | —   | EID17 | EID16 | EID15 | EID14 |

| bit 15 |     |     |     |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID13 | EID12 | EID11 | EID10 | EID9  | EID8  | EID7  | EID6  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

#### 20.3 **DCI Control Registers**

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 DCIEN DCISIDL DLOOP CSCKD CSCKE COFSD \_\_\_ \_\_\_\_ bit 15 Г 11\_0 11\_0

#### DCICON1: DCI CONTROL REGISTER 1 REGISTER 20-1:

| R/W-0                                                              | R/W-0                          | R/W-0                                  | U-0            | U-0               | U-0              | R/W-0             | R/W-0       |

|--------------------------------------------------------------------|--------------------------------|----------------------------------------|----------------|-------------------|------------------|-------------------|-------------|

| UNFM                                                               | CSDOM                          | DJST                                   | —              | _                 | _                | COFSI             | M<1:0>      |

| bit 7                                                              |                                | -                                      |                |                   |                  | -                 | bit         |

|                                                                    |                                |                                        |                |                   |                  |                   |             |

| Legend:                                                            |                                |                                        |                |                   |                  |                   |             |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                |                                        |                |                   |                  |                   |             |

| -n = Value at                                                      | POR                            | '1' = Bit is set                       |                | '0' = Bit is cle  | ared             | x = Bit is unkr   | nown        |

|                                                                    |                                |                                        |                |                   |                  |                   |             |

| bit 15                                                             | -                              | Module Enable                          | bit            |                   |                  |                   |             |

|                                                                    | 1 = Module is<br>0 = Module is |                                        |                |                   |                  |                   |             |

| bit 14                                                             | Unimplemer                     | nted: Read as '                        | 0'             |                   |                  |                   |             |

| bit 13                                                             | DCISIDL: DO                    | CI Stop in Idle C                      | ontrol bit     |                   |                  |                   |             |

|                                                                    |                                | vill halt in CPU I                     |                |                   |                  |                   |             |

|                                                                    |                                | vill continue to c                     | -              | 'U Idle mode      |                  |                   |             |

| bit 12                                                             | -                              | nted: Read as '                        |                |                   |                  |                   |             |

| bit 11                                                             | 0                              | ital Loopback N                        |                |                   |                  |                   |             |

|                                                                    |                                | oopback mode i<br>oopback mode i       |                | SDI and CSDO      | pins internally  | connected.        |             |

| bit 10                                                             | CSCKD: Sar                     | nple Clock Dire                        | ction Control  | bit               |                  |                   |             |

|                                                                    | •                              | n is an input wh                       |                |                   |                  |                   |             |

|                                                                    | 0 = CSCK pi                    | n is an output w                       | hen DCI moo    | dule is enabled   |                  |                   |             |

| bit 9                                                              |                                | nple Clock Edge                        |                |                   |                  |                   |             |

|                                                                    |                                | inges on serial o<br>inges on serial o |                |                   |                  |                   |             |

| bit 8                                                              | COFSD: Fra                     | me Synchroniza                         | ation Directio | n Control bit     |                  |                   |             |

|                                                                    |                                | n is an input wh<br>n is an output w   |                |                   |                  |                   |             |

| bit 7                                                              | -                              | erflow Mode bit                        |                |                   |                  |                   |             |

|                                                                    |                                | last value writte                      |                |                   | n a transmit un  | derflow           |             |

| bit 6                                                              | CSDOM: Set                     | rial Data Output                       | Mode bit       |                   |                  |                   |             |

|                                                                    |                                | n will be tri-state                    |                | abled transmit t  | ime slots        |                   |             |

|                                                                    |                                | n drives '0's du                       |                |                   |                  |                   |             |

| bit 5                                                              | DJST: DCI D                    | ata Justification                      | Control bit    |                   |                  |                   |             |

|                                                                    |                                | nsmission/recep                        | otion is begur | n during the san  | ne serial clock  | cycle as the frai | me          |

|                                                                    |                                | nization pulse                         |                |                   |                  |                   |             |

| <b>h</b> #4.0                                                      |                                | nsmission/recep                        | -              | n one serial cloc | ск сусіе апег та | ame synchroniz    | ation pulse |

| bit 4-2                                                            | -                              | nted: Read as '                        |                |                   |                  |                   |             |

| bit 1-0                                                            |                                | >: Frame Sync                          | IVIODE DITS    |                   |                  |                   |             |

|                                                                    |                                | C-Link mode                            |                |                   |                  |                   |             |

|                                                                    |                                | me Sync mode                           |                |                   |                  |                   |             |

|                                                                    |                                | hannel Frame S                         | ync mode       |                   |                  |                   |             |

bit 8

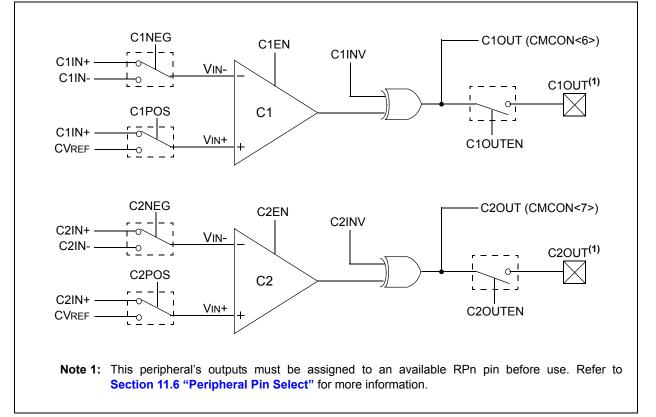

## 23.0 COMPARATOR MODULE

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304. of the dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Comparator" (DS70212) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Comparator module provides a set of dual input comparators. The inputs to the comparator can be configured to use any one of the four pin inputs (C1IN+, C1IN-, C2IN+ and C2IN-) as well as the Comparator Voltage Reference Input (CVREF).

Note: This peripheral contains output functions that may need to be configured by the peripheral pin select feature. For more information, see Section 11.6 "Peripheral Pin Select".

## FIGURE 23-1: COMPARATOR I/O OPERATING MODES

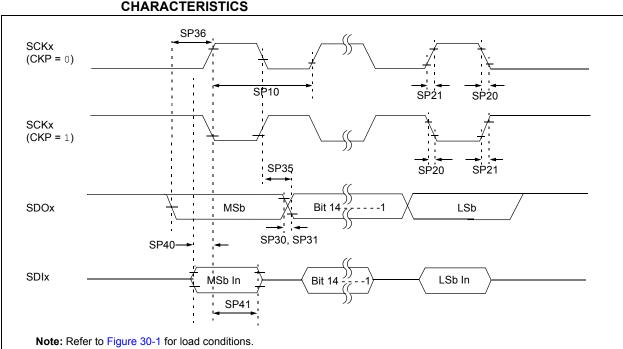

# FIGURE 30-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

|              |                       |                                               | (unless c                                   | <b>Operatin</b><br>otherwise<br>g temperat | <b>stated)</b><br>ture -40 | °C ≤Ta ≤+ | <b>/ to 3.6V</b><br>85°C for Industrial<br>125°C for Extended |  |

|--------------|-----------------------|-----------------------------------------------|---------------------------------------------|--------------------------------------------|----------------------------|-----------|---------------------------------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min Typ <sup>(2)</sup> Max Units Conditions |                                            |                            |           |                                                               |  |

| SP10         | TscP                  | Maximum SCK Frequency                         | _                                           | _                                          | 9                          | MHz       | See Note 3                                                    |  |

| SP20         | TscF                  | SCKx Output Fall Time                         | —                                           | —                                          | _                          | ns        | See parameter DO32 and Note 4                                 |  |

| SP21         | TscR                  | SCKx Output Rise Time                         | —                                           | —                                          | _                          | ns        | See parameter DO31 and Note 4                                 |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | —                                           | —                                          | _                          | ns        | See parameter DO32 and Note 4                                 |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | —                                           | —                                          | _                          | ns        | See parameter DO31 and Note 4                                 |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | —                                           | 6                                          | 20                         | ns        | _                                                             |  |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                          | —                                          | —                          | ns        | _                                                             |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                          | —                                          | _                          | ns        | _                                                             |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                          | —                                          |                            | ns        | —                                                             |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

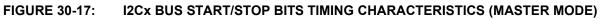

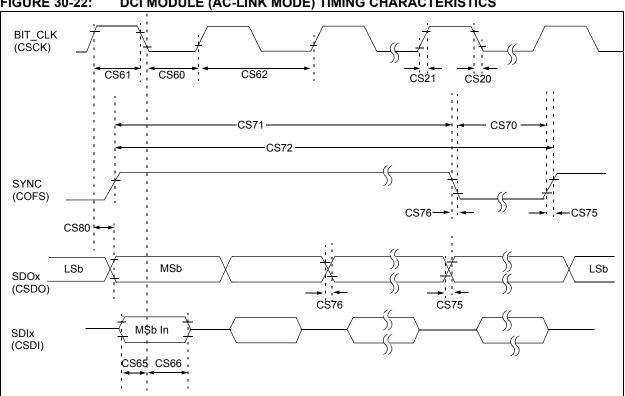

**FIGURE 30-22:** DCI MODULE (AC-LINK MODE) TIMING CHARACTERISTICS

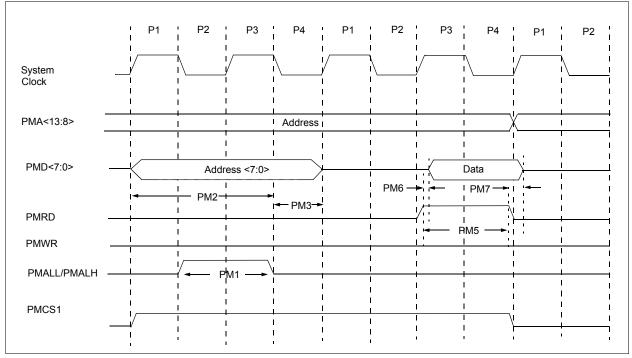

## FIGURE 30-28: PARALLEL MASTER PORT READ TIMING DIAGRAM

## TABLE 30-52: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                                                | Standard C<br>(unless oth<br>Operating te | erwise stat | ,    |       |            |

|--------------------|----------------------------------------------------------------|-------------------------------------------|-------------|------|-------|------------|

| Param<br>No.       | Characteristic                                                 | Min.                                      | Тур         | Max. | Units | Conditions |

| PM1                | PMALL/PMALH Pulse-Width                                        | —                                         | 0.5 TCY     | _    | ns    | _          |

| PM2                | Address Out Valid to PMALL/PMALH Invalid (address setup time)  | —                                         | 0.75 TCY    | _    | ns    | —          |

| PM3                | PMALL/PMALH Invalid to Address Out Invalid (address hold time) | —                                         | 0.25 TCY    | _    | ns    | —          |

| PM5                | PMRD Pulse-Width                                               | _                                         | 0.5 TCY     | _    | ns    | —          |

| PM6                | PMRD or PMENB Active to Data In Valid (data setup time)        | 150                                       | —           | _    | ns    | —          |

| PM7                | PMRD or PMENB Inactive to Data In Invalid (data hold time)     | —                                         | —           | 5    | ns    | —          |

NOTES:

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| Listen All Messages                               | . 230 |

|---------------------------------------------------|-------|

| Listen Only                                       | . 230 |

| Loopback                                          |       |

| Normal Operation                                  |       |

| Modulo Addressing                                 | 63    |

| Applicability                                     | 64    |

| Operation Example                                 | 63    |

| Start and End Address                             | 63    |

| W Address Register Selection                      | 63    |

| MPLAB ASM30 Assembler, Linker, Librarian          | . 334 |

| MPLAB Integrated Development Environment Software | . 333 |

| MPLAB PM3 Device Programmer                       | . 336 |

| MPLAB REAL ICE In-Circuit Emulator System         | . 335 |

| MPLINK Object Linker/MPLIB Object Librarian       | . 334 |

## Ν

| NVM Module   |    |

|--------------|----|

| Register Map | 60 |

| 0            |    |

| 0                        |  |

|--------------------------|--|

| Open-Drain Configuration |  |

| Output Compare           |  |

## Ρ

| Packaging                                   | 407      |

|---------------------------------------------|----------|

| Marking                                     |          |

| Peripheral Module Disable (PMD)             |          |

| Pinout I/O Descriptions (table)             |          |

| PMD Module                                  |          |

| Register Map                                | 60       |

| PORTA                                       |          |

| Register Map                                | 58 59    |

| PORTB                                       | . 50, 55 |

| Register Map                                | 59       |

| Power-on Reset (POR)                        |          |

| Power-Saving Features                       |          |

| Clock Frequency and Switching               |          |

|                                             |          |

| Program Address Space                       |          |

| Construction                                |          |

| Data Access from Program Memory Using       |          |

| Program Space Visibility                    | 69       |

| Data Access from Program Memory Using       |          |

| Table Instructions                          |          |

| Data Access from, Address Generation        |          |

| Memory Map                                  | 35       |

| Table Read Instructions                     |          |

| TBLRDH                                      | 68       |

| TBLRDL                                      | 68       |

| Visibility Operation                        | 69       |

| Program Memory                              |          |

| Interrupt Vector                            |          |

| Organization                                | 36       |

| Reset Vector                                |          |

| 5                                           |          |

| R                                           |          |

| Reader Response                             | 432      |

| Register Map                                |          |

| CRC                                         | 58       |

| Dual Comparator                             | 58       |

| Parallel Master/Slave Port                  |          |

| Real-Time Clock and Calendar                |          |

| Registers                                   |          |

| AD1CHS0 (ADC1 Input Channel 0 Select        | 274      |

| AD1CHS123 (ADC1 Input Channel 1, 2, 3 Selec |          |

| AD1CON1 (ADC1 Control 1)                    |          |

| AD1CON2 (ADC1 Control 2)                    |          |

| AD1CON2 (ADC1 Control 2)                    |          |

|                                             | Zíl      |

| AD1CON4 (ADC1 Control 4)                                                                                                  |                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD1CSSL (ADC1 Input Scan Select Low)                                                                                      |                                                                                                                                                                                                                              |

| AD1PCFGL (ADC1 Port Configuration Low)                                                                                    | 275                                                                                                                                                                                                                          |

| CiBUFPNT1 (ECAN Filter 0-3 Buffer Pointer)                                                                                | 241                                                                                                                                                                                                                          |

| CiBUFPNT2 (ECAN Filter 4-7 Buffer Pointer)                                                                                |                                                                                                                                                                                                                              |

| CiBUFPNT3 (ECAN Filter 8-11 Buffer Pointer)                                                                               |                                                                                                                                                                                                                              |

| CiBUFPNT4 (ECAN Filter 12-15 Buffer Pointer)                                                                              |                                                                                                                                                                                                                              |

| CiCFG1 (ECAN Baud Rate Configuration 1)                                                                                   |                                                                                                                                                                                                                              |

|                                                                                                                           |                                                                                                                                                                                                                              |

| CiCFG2 (ECAN Baud Rate Configuration 2)                                                                                   |                                                                                                                                                                                                                              |

| CiCTRL1 (ECAN Control 1)                                                                                                  |                                                                                                                                                                                                                              |

| CiCTRL2 (ECAN Control 2)                                                                                                  |                                                                                                                                                                                                                              |

| CiEC (ECAN Transmit/Receive Error Count)                                                                                  |                                                                                                                                                                                                                              |

| CiFCTRL (ECAN FIFO Control)                                                                                               | 235                                                                                                                                                                                                                          |

| CiFEN1 (ECAN Acceptance Filter Enable)                                                                                    | 241                                                                                                                                                                                                                          |

| CiFIFO (ECAN FIFO Status)                                                                                                 | 236                                                                                                                                                                                                                          |

| CiFMSKSEL1 (ECAN Filter 7-0 Mask Selection)                                                                               |                                                                                                                                                                                                                              |

| 246                                                                                                                       | 240,                                                                                                                                                                                                                         |

|                                                                                                                           | 000                                                                                                                                                                                                                          |

| CilNTE (ECAN Interrupt Enable)                                                                                            |                                                                                                                                                                                                                              |

| CiINTF (ECAN Interrupt Flag)                                                                                              | 237                                                                                                                                                                                                                          |

| CiRXFnEID (ECAN Acceptance Filter n                                                                                       |                                                                                                                                                                                                                              |

| Extended Identifier)                                                                                                      | 245                                                                                                                                                                                                                          |

| CiRXFnSID (ECAN Acceptance Filter n                                                                                       |                                                                                                                                                                                                                              |

| Standard Identifier)                                                                                                      | 244                                                                                                                                                                                                                          |

| CiRXFUL1 (ECAN Receive Buffer Full 1)                                                                                     | 248                                                                                                                                                                                                                          |

| CiRXFUL2 (ECAN Receive Buffer Full 2)                                                                                     |                                                                                                                                                                                                                              |

| CiRXMnEID (ECAN Acceptance Filter Mask n                                                                                  | 240                                                                                                                                                                                                                          |

| Extended Identifier)                                                                                                      | 247                                                                                                                                                                                                                          |