Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp204-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

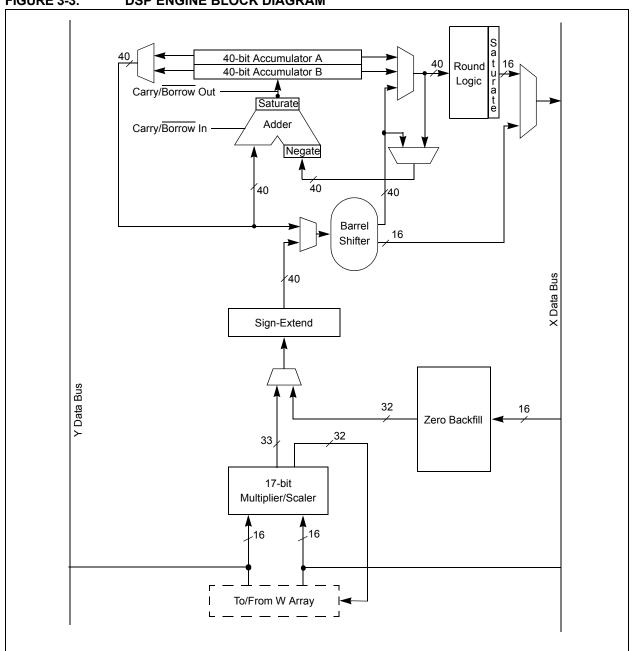

#### FIGURE 3-3: DSP ENGINE BLOCK DIAGRAM

| TABLE 4     | 4-5:        | TIMEF      | R REGIS           | TER MA                 | ٨P          |               |             |              |              |                |              |       |        |       |       |       |       |               |

|-------------|-------------|------------|-------------------|------------------------|-------------|---------------|-------------|--------------|--------------|----------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15     | Bit 14            | Bit 13                 | Bit 12      | Bit 11        | Bit 10      | Bit 9        | Bit 8        | Bit 7          | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |            |                   |                        |             |               |             |              | Timer1       | Register       |              |       |        |       |       |       |       | 0000          |

| PR1         | 0102        |            |                   |                        |             |               |             |              | Period F     | Register 1     |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON        | _                 | TSIDL                  | _           | _             | _           | _            | —            | —              | TGATE        | TCKP  | S<1:0> |       | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106        |            |                   |                        |             |               |             |              | Timer2       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |            |                   |                        |             |               | Tin         | ner3 Holding | Register (fo | r 32-bit timeı | operations o | only) |        |       |       |       |       | XXXX          |

| TMR3        | 010A        |            |                   |                        |             |               |             |              | Timer3       | Register       |              |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |            |                   | Period Register 2 FFFF |             |               |             |              |              |                |              |       |        |       | FFFF  |       |       |               |

| PR3         | 010E        |            |                   |                        |             |               |             |              | Period F     | Register 3     |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON        | _                 | TSIDL                  | _           | _             | _           | _            | _            | _              | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112        | TON        |                   | TSIDL                  |             |               |             | _            | —            | —              | TGATE        | TCKP  | S<1:0> | —     | _     | TCS   | —     | 0000          |

| TMR4        | 0114        |            |                   |                        |             |               |             |              | Timer4       | Register       |              |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        |            |                   |                        |             |               | Tin         | ner5 Holding | Register (fo | r 32-bit timeı | operations o | only) |        |       |       |       |       | XXXX          |

| TMR5        | 0118        |            |                   |                        |             |               |             |              | Timer5       | Register       |              |       |        |       |       |       |       | 0000          |

| PR4         | 011A        |            |                   |                        |             |               |             |              | Period F     | Register 4     |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C        |            | Period Register 5 |                        |             |               |             |              |              |                |              |       | FFFF   |       |       |       |       |               |

| T4CON       | 011E        | TON        |                   | TSIDL                  |             |               |             | _            | _            | -              | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON        |                   | TSIDL                  |             |               |             | _            | _            | -              | TGATE        | TCKP  | S<1:0> | —     | —     | TCS   | _     | 0000          |

| Legend:     | x = un      | known valu | e on Reset,       | — = unimp              | lemented, r | ead as '0'. F | Reset value | s are showr  | in hexadeo   | cimal.         |              |       |        |       |       |       |       |               |

#### TABLE 4-6: INPUT CAPTURE REGISTER MAP

|             |             |                         | •/                       |        |        | · •••• |        |       |            |              |       |       |       |       |       |          |       |               |

|-------------|-------------|-------------------------|--------------------------|--------|--------|--------|--------|-------|------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15                  | Bit 14                   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF      | 0140        |                         |                          |        |        |        |        |       | Input 1 Ca | pture Regist | er    |       |       |       |       |          |       | XXXX          |

| IC1CON      | 0142        | —                       |                          | ICSIDL | —      |        | -      |       |            | ICTMR        | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF      | 0144        |                         | Input 2 Capture Register |        |        |        |        |       |            |              |       |       |       |       |       | XXXX     |       |               |

| IC2CON      | 0146        | —                       |                          |        |        |        |        |       |            |              |       |       |       |       |       |          | 0000  |               |

| IC7BUF      | 0158        |                         |                          |        |        |        |        |       | Input 7 Ca | pture Regist | er    |       |       |       |       |          |       | XXXX          |

| IC7CON      | 015A        |                         |                          |        |        |        |        |       |            |              |       |       | 0000  |       |       |          |       |               |

| IC8BUF      | 015C        | Input 8Capture Register |                          |        |        |        |        |       |            |              |       |       | XXXX  |       |       |          |       |               |

| IC8CON      | 015E        | —                       |                          | ICSIDL | —      |        | _      |       |            | ICTMR        | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

|             |             |                         |                          |        |        |        |        |       |            |              |       |       |       |       |       |          |       |               |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | Addr | Bit 15 | Bit 14  | Bit 13 | Bit 12  | Bit 11              | Bit 10    | Bit 9       | Bit 8   | Bit 7       | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|---------|--------|---------|---------------------|-----------|-------------|---------|-------------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |         |        |         |                     |           |             | ADC Da  | ta Buffer 0 |           |       |       |        |          |          |         | XXXX          |

| AD1CON1   | 0320 | ADON   | —       | ADSIDL | ADDMABM | _                   | AD12B     | FOR         | M<1:0>  | :           | SSRC<2:0> |       | _     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | CFG<2:0 | >      | _       | _                   | CSCNA     | CHP         |         |             |           |       |       |        | ALTS     | 0000     |         |               |

| AD1CON3   | 0324 | ADRC   | —       | _      |         | SAMC<4:0> ADCS<7:0> |           |             |         |             |           |       | 0000  |        |          |          |         |               |

| AD1CHS123 | 0326 | _      | _       | _      | _       | —                   | CH123N    | IB<1:0>     | CH123SB | _           | _         | _     | _     | _      | CH123N   | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _       | _      |         | C                   | H0SB<4:0> | <b>&gt;</b> |         | CH0NA       | —         | —     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      | _       | _      | PCFG12  | PCFG11              | PCFG10    | PCFG9       | _       | _           | —         | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _       | _      | CSS12   | CSS11               | CSS10     | CSS9        | _       | _           | _         | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 |        | _       |        | _       | _                   | _         | _           | _       |             | _         | _     |       | _      | [        | DMABL<2: | 0>      | 0000          |

#### TABLE 4-13: ADC1 REGISTER MAP FOR dsPIC33FJ64GP202/802, dsPIC33FJ128GP202/802 AND dsPIC33FJ32GP302

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

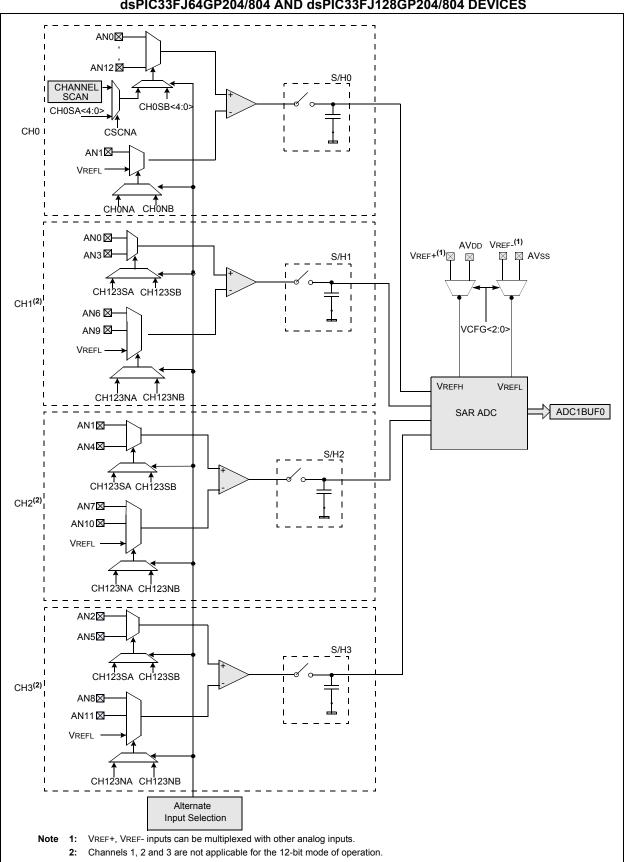

#### TABLE 4-14: ADC1 REGISTER MAP FOR dsPIC33FJ64GP204/804, dsPIC33FJ128GP204/804 AND dsPIC33FJ32GP304

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8   | Bit 7        | Bit 6     | Bit 5 | Bit 4 | Bit 3   | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|---------|--------|-----------|---------|---------|--------------|-----------|-------|-------|---------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |          |        |         |        |           |         | ADC Da  | ata Buffer 0 |           |       |       |         |          |          |         | XXXX          |

| AD1CON1   | 0320 | ADON   |          | ADSIDL | ADDMABM |        | AD12B     | FOR     | M<1:0>  | :            | SSRC<2:0> |       | —     | SIMSAM  | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | 'CFG<2:0 | >      | _       |        | CSCNA     | CHP     | S<1:0>  | BUFS         | —         |       | SMP   | <3:0>   |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   |          |        |         | S      | AMC<4:0>  |         |         |              |           |       | ADCS  | \$<7:0> |          |          |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _       | _      | CH123N    | NB<1:0> | CH123SB | _            | _         | _     | _     | _       | CH123N   | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |         | С      | H0SB<4:0> | >       |         | CH0NA        | _         | _     |       | С       | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      |          |        | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8   | PCFG7        | PCFG6     | PCFG5 | PCFG4 | PCFG3   | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      |          |        | CSS12   | CSS11  | CSS10     | CSS9    | CSS8    | CSS7         | CSS6      | CSS5  | CSS4  | CSS3    | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |          |        | _       | —      |           |         | —       | _            | —         | —     | —     | —       | [        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: DAC1 REGISTER MAP FOR dsPIC33FJ128GP802/804 AND dsPIC33FJ64GP802/804

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14             | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7    | Bit 6 | Bit 5  | Bit 4 | Bit 3      | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------------------|---------|--------|--------|--------|-------|--------|----------|-------|--------|-------|------------|--------|-------|--------|---------------|

| DAC1CON  | 03F0        | DACEN  | —                  | DACSIDL | AMPON  | —      | _      | —     | FORM   | —        |       |        | D     | ACFDIV<6:( | )>     |       |        | 0000          |

| DAC1STAT | 03F2        | LOEN   | —                  | LMVOEN  | _      | _      | LITYPE | LFULL | LEMPTY | ROEN     | -     | RMVOEN | _     | _          | RITYPE | RFULL | REMPTY | 0000          |

| DAC1DFLT | 03F4        |        |                    |         |        |        |        |       | DAC1DF | LT<15:0> |       |        |       |            |        |       |        | 0000          |

| DAC1RDAT | 03F6        |        | DAC1RDAT<15:0> 0   |         |        |        |        |       |        |          |       |        |       | 0000       |        |       |        |               |

| DAC1LDAT | 03F8        |        | DAC1LDAT<15:0> 000 |         |        |        |        |       |        |          |       |        |       | 0000       |        |       |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.6 Flash Control Registers

#### R/SO-0(1) R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> U-0 U-0 U-0 U-0 U-0 WR WREN WRERR bit 15 bit 8 R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> U-0 U-0 U-0 NVMOP<3:0>(2) ERASE bit 7 bit 0 Leaend: SO = Settable only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown WR: Write Control bit bit 15 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is cleared by hardware once operation is complete 0 = Program or erase operation is complete and inactive bit 14 WREN: Write Enable bit 1 = Enable Flash program/erase operations 0 = Inhibit Flash program/erase operations bit 13 WRERR: Write Sequence Error Flag bit 1 = An improper program or erase sequence attempt or termination has occurred (bit is set automatically on any set attempt of the WR bit) 0 = The program or erase operation completed normally bit 12-7 Unimplemented: Read as '0' bit 6 ERASE: Erase/Program Enable bit 1 = Perform the erase operation specified by NVMOP<3:0> on the next WR command 0 = Perform the program operation specified by NVMOP<3:0> on the next WR command bit 5-4 Unimplemented: Read as '0' NVMOP<3:0>: NVM Operation Select bits<sup>(2)</sup> bit 3-0 If ERASE = 1: 1111 = Memory bulk erase operation 1110 = Reserved 1101 = Erase General Segment 1100 = Erase Secure Segment 1011 = Reserved 0011 = No operation 0010 = Memory page erase operation 0001 = No operation 0000 = Erase a single Configuration register byte If ERASE = 0: 1111 = No operation 1110 = Reserved 1101 = No operation 1100 = No operation 1011 = Reserved 0011 = Memory word program operation 0010 = No operation 0001 = Memory row program operation 0000 = Program a single Configuration register byte Note 1: These bits can only be reset on POR.

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

2: All other combinations of NVMOP<3:0> are unimplemented.

| U-0          | R/W-1              | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|--------------|--------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| 0-0          | R/W-1              |                                          | R/W-U          | 0-0               | R/W-1           |                 | R/W-U |

| <br>bit 15   |                    | T1IP<2:0>                                |                | —                 |                 | OC1IP<2:0>      | bi    |

| 511 15       |                    |                                          |                |                   |                 |                 | DI    |

| U-0          | R/W-1              | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

| _            |                    | IC1IP<2:0>                               |                |                   |                 | INT0IP<2:0>     |       |

| bit 7        |                    |                                          |                |                   |                 |                 | bi    |

| Legend:      |                    |                                          |                |                   |                 |                 |       |

| R = Readab   | le bit             | W = Writable                             | bit            | U = Unimple       | mented bit, rea | ad as '0'       |       |

| -n = Value a |                    | '1' = Bit is set                         |                | '0' = Bit is cle  |                 | x = Bit is unkn | own   |

|              |                    |                                          |                |                   |                 |                 |       |

| bit 15       | Unimplem           | ented: Read as '                         | )'             |                   |                 |                 |       |

| bit 14-12    | T1IP<2:0>:         | Timer1 Interrupt                         | Priority bits  |                   |                 |                 |       |

|              | 111 = Inter        | rupt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              |                    | rupt is priority 1                       |                |                   |                 |                 |       |

|              |                    | rupt source is dis                       |                |                   |                 |                 |       |

| bit 11       | -                  | ented: Read as '                         |                |                   |                 |                 |       |

| bit 10-8     |                    | >: Output Compa                          |                | -                 | rity bits       |                 |       |

|              | 111 = Inter<br>•   | rupt is priority 7 (I                    | nignest priori | ty interrupt)     |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              |                    | rupt is priority 1<br>rupt source is dis | abled          |                   |                 |                 |       |

| bit 7        |                    | ented: Read as '                         |                |                   |                 |                 |       |

| bit 6-4      | •                  | : Input Capture C                        |                | errunt Priority h | nits            |                 |       |

|              |                    | rupt is priority 7 (I                    |                |                   |                 |                 |       |

|              | •                  |                                          | 0 1            | , ,               |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •<br>001 = Inter   | rupt is priority 1                       |                |                   |                 |                 |       |

|              |                    | rupt source is dis                       | abled          |                   |                 |                 |       |

| bit 3        | Unimplem           | ented: Read as '                         | )'             |                   |                 |                 |       |

| bit 2-0      | INT0IP<2:0         | >: External Interr                       | upt 0 Priority | / bits            |                 |                 |       |

|              | 111 = Inter        | rupt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              | •                  |                                          |                |                   |                 |                 |       |

|              |                    | rupt is priority 1                       |                |                   |                 |                 |       |

|              | 000 <b>= Inter</b> | rupt source is dis                       | abled          |                   |                 |                 |       |

DS70292G-page 110

| U-0              | U-0                            | U-0                                   | U-0             | U-0               | R/W-1            | R/W-0           | R/W-0   |

|------------------|--------------------------------|---------------------------------------|-----------------|-------------------|------------------|-----------------|---------|

| _                | _                              | —                                     | _               | —                 |                  | DMA4IP<2:0>     |         |

| bit 15           |                                |                                       |                 |                   |                  |                 | bit 8   |

|                  |                                | <b>D</b> 444 0                        |                 |                   |                  |                 |         |

| U-0              | R/W-1                          | R/W-0                                 | R/W-0           | U-0               | U-0              | U-0             | U-0     |

|                  |                                | PMPIP<2:0>                            |                 | —                 |                  |                 | — hit ( |

| bit 7            |                                |                                       |                 |                   |                  |                 | bit C   |

| Legend:          |                                |                                       |                 |                   |                  |                 |         |

| R = Readab       | le bit                         | W = Writable                          | bit             | U = Unimplen      | nented bit, read | 1 as '0'        |         |

| -n = Value a     | t POR                          | '1' = Bit is set                      |                 | '0' = Bit is clea |                  | x = Bit is unkr | own     |

|                  |                                |                                       |                 |                   |                  |                 |         |

| bit 15-11        | Unimpleme                      | ented: Read as '                      | 0'              |                   |                  |                 |         |

| bit 10-8         | DMA4IP<2:                      | 0>: DMA Chann                         | el 4 Data Tra   | nsfer Complete    | Interrupt Priori | ty bits         |         |

|                  | 111 = Interr                   | upt is priority 7 (                   | highest priori  | ty interrupt)     |                  |                 |         |

|                  | •                              |                                       |                 |                   |                  |                 |         |

|                  | •                              |                                       |                 |                   |                  |                 |         |

|                  | 001 = Interr                   | upt is priority 1                     |                 |                   |                  |                 |         |

|                  |                                | upt source is dis                     | abled           |                   |                  |                 |         |

|                  |                                |                                       |                 |                   |                  |                 |         |

| bit 7            | Unimpleme                      | ented: Read as '                      | 0'              |                   |                  |                 |         |

|                  | •                              | ented: Read as '<br>>: Parallel Maste |                 | pt Priority bits  |                  |                 |         |

|                  | PMPIP<2:0                      |                                       | er Port Interru |                   |                  |                 |         |

|                  | PMPIP<2:0                      | >: Parallel Maste                     | er Port Interru |                   |                  |                 |         |

|                  | PMPIP<2:0                      | >: Parallel Maste                     | er Port Interru |                   |                  |                 |         |

| bit 7<br>bit 6-4 | PMPIP<2:0<br>111 = Interr<br>• | >: Parallel Maste                     | er Port Interru |                   |                  |                 |         |

###

bit 3-0 Unimplemented: Read as '0'

| REGISTER 7      | 7-31: INTTR       | EG: INTERR                             | UPT CONTI     | ROL AND STA       | ATUS REGI       | STER            |       |

|-----------------|-------------------|----------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| U-0             | U-0               | U-0                                    | U-0           | R-0               | R-0             | R-0             | R-0   |

| _               | —                 | —                                      | _             |                   | ILF             | <3:0>           |       |

| bit 15          |                   |                                        |               |                   |                 |                 | bit 8 |

| U-0             | R-0               | R-0                                    | R-0           | R-0               | R-0             | R-0             | R-0   |

| _               |                   |                                        |               | VECNUM<6:0        | >               |                 |       |

| bit 7           |                   |                                        |               |                   |                 |                 | bit C |

|                 |                   |                                        |               |                   |                 |                 |       |

| Legend:         |                   |                                        |               |                   |                 |                 |       |

| R = Readable    | e bit             | W = Writable                           | bit           | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at I | POR               | '1' = Bit is set                       |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-12       | Unimplomon        | ted: Read as '                         | <b>`</b>      |                   |                 |                 |       |

|                 | -                 |                                        |               | -1                |                 |                 |       |

| bit 11-8        |                   | w CPU Interru                          | -             | el bits           |                 |                 |       |

|                 | 1111 <b>= CPU</b> | Interrupt Priorit                      | y Level is 15 |                   |                 |                 |       |

|                 | •                 |                                        |               |                   |                 |                 |       |

|                 | •                 |                                        |               |                   |                 |                 |       |

|                 |                   | Interrupt Priorit<br>Interrupt Priorit |               |                   |                 |                 |       |

| bit 7           |                   | •                                      | •             |                   |                 |                 |       |

|                 | Unimplemen        | ted: Read as '                         | 0.            |                   |                 |                 |       |

0111111 = Interrupt Vector pending is number 135

0000001 = Interrupt Vector pending is number 9 0000000 = Interrupt Vector pending is number 8

•

#### 10.5 Power-Saving Resources

Many useful resources related to Power-Saving are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en532311              |

#### 10.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- · Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

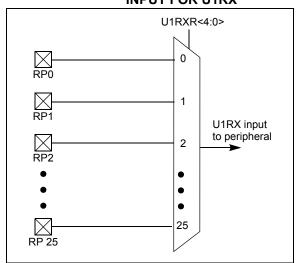

#### 11.6 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 11.6.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 26 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 11.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 11.6.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it is mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-16). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 11-2 illustrates remappable pin selection for U1RX input.

#### FIGURE 11-2: REMAPPABLE MUX INPUT FOR U1RX

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| U-0                | U-0                                                  | U-0                                                                    | R/W-1         | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

|--------------------|------------------------------------------------------|------------------------------------------------------------------------|---------------|-----------------------------|------------------|-----------------|-------|

| —                  |                                                      | _                                                                      |               |                             | U1CTSR<4:0       | >               |       |

| bit 15             |                                                      |                                                                        |               |                             |                  |                 | bit 8 |

|                    |                                                      |                                                                        | <b>D</b> 44/4 |                             |                  | D 44/4          |       |

| U-0                | U-0                                                  | U-0                                                                    | R/W-1         | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

| -:+ 7              | _                                                    | —                                                                      |               |                             | U1RXR<4:0>       | •               | h:+ 0 |

| bit 7              |                                                      |                                                                        |               |                             |                  |                 | bit C |

| Legend:            |                                                      |                                                                        |               |                             |                  |                 |       |

| R = Readab         | le bit                                               | W = Writable                                                           | oit           | U = Unimplen                | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                                | '1' = Bit is set                                                       |               | '0' = Bit is clea           | ared             | x = Bit is unkr | nown  |

| bit 15-13          | Unimpleme                                            | nted: Read as '                                                        | )'            |                             |                  |                 |       |

| bit 12-8           | -                                                    | 0>: Assign UAR                                                         |               | end $(\overline{11000})$ to | the correspo     | ndina RPn nin   |       |

|                    |                                                      | ut tied to Vss                                                         |               |                             |                  | ionig i i i più |       |

|                    |                                                      | ut tied to RP25                                                        |               |                             |                  |                 |       |

|                    | •                                                    |                                                                        |               |                             |                  |                 |       |

|                    | •                                                    |                                                                        |               |                             |                  |                 |       |

|                    |                                                      |                                                                        |               |                             |                  |                 |       |

|                    | •                                                    |                                                                        |               |                             |                  |                 |       |

|                    |                                                      | ut tied to RP1<br>ut tied to RP0                                       |               |                             |                  |                 |       |

| oit 7-5            | 00000 <b>= Inp</b>                                   |                                                                        | )'            |                             |                  |                 |       |

|                    | 00000 = Inp<br>Unimpleme                             | ut tied to RP0                                                         |               | 1RX) to the cor             | responding RF    | n pin           |       |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(                                     |               | 1RX) to the cor             | responding RF    | n pin           |       |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss |               | 1RX) to the cor             | responding RF    | 'n pin          |       |

| bit 7-5<br>bit 4-0 | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss |               | 1RX) to the cor             | responding RF    | 'n pin          |       |

#### REGISTER 11-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

00001 = Input tied to RP1 00000 = Input tied to RP0

## 14.2 Input Capture Registers

# **REGISTER 14-1:** ICxCON: INPUT CAPTURE x CONTROL REGISTER (x = 1, 2, 7 OR 8)

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | —   | —   |     |     | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0    | R/W-0 |

|-------|-------|-------|---------|---------|-------|----------|-------|

| ICTMR | ICI<  | 1:0>  | ICOV    | ICBNE   |       | ICM<2:0> |       |

| bit 7 |       |       |         |         |       |          | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 1 = Input capture module halts in CPU Idle mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 0 = Input capture module continues to operate in CPU Idle mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 00 = Interrupt on every capture event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 1 = Input capture overflow occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | 0 = No input capture overflow occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br/>(Rising edge detect only, all other control bits are not applicable.)</li> <li>110 = Unused (module disabled)</li> <li>101 = Capture mode, every 16th rising edge</li> <li>100 = Capture mode, every 4th rising edge</li> <li>011 = Capture mode, every rising edge</li> <li>010 = Capture mode, every falling edge</li> <li>010 = Capture mode, every falling edge</li> <li>001 = Capture mode, every edge (rising and falling)</li> </ul> |

|           | (ICI<1:0> bits do not control interrupt generation for this mode.)<br>000 = Input capture module turned off                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BUFFER 19-3                                                       | B: ECAN                                                                                      | I™ MESSAGE          | BUFFER \         | NORD 2          |                  |          |       |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------|------------------|-----------------|------------------|----------|-------|

| R/W-x                                                             | R/W-x                                                                                        | R/W-x               | R/W-x            | R/W-x           | R/W-x            | R/W-x    | R/W-x |

| EID5                                                              | EID4                                                                                         | EID3                | EID2             | EID1            | EID0             | RTR      | RB1   |

| bit 15                                                            |                                                                                              |                     |                  |                 |                  |          | bit 8 |

| U-0                                                               | U-0                                                                                          | U-0                 | R/W-x            | R/W-x           | R/W-x            | R/W-x    | R/W-x |

| —                                                                 | —                                                                                            | —                   | RB0              | DLC3            | DLC2             | DLC1     | DLC0  |

| bit 7                                                             |                                                                                              |                     |                  |                 |                  |          | bit 0 |

| Legend:                                                           | h:t                                                                                          | M - Mritabla        |                  |                 | mented bit, read | d aa '0' |       |

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |                                                                                              |                     | '0' = Bit is cle | x = Bit is unkr | Iown             |          |       |

| bit 15-10                                                         | <b>EID&lt;5:0&gt;:</b> E                                                                     | xtended Identifie   | er bits          |                 |                  |          |       |

| bit 9                                                             | RTR: Remote Transmission Request bit                                                         |                     |                  |                 |                  |          |       |

|                                                                   | <ul> <li>1 = Message will request remote transmission</li> <li>0 = Normal message</li> </ul> |                     |                  |                 |                  |          |       |

| hit Q                                                             | DB1. Docor                                                                                   | PP4: Depended Pit 1 |                  |                 |                  |          |       |

| bit 8   | RB1: Reserved Bit 1                             |

|---------|-------------------------------------------------|

|         | User must set this bit to '0' per CAN protocol. |

| bit 7-5 | Unimplemented: Read as '0'                      |

| bit 4   | RB0: Reserved Bit 0                             |

|         | User must set this bit to '0' per CAN protocol. |

| bit 3-0 | DLC<3:0>: Data Length Code bits                 |

#### BUFFER 19-4: ECAN™ MESSAGE BUFFER WORD 3

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|------------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                  |       |                  | B     | yte 1             |                 |                 |       |

| bit 15           |       |                  |       |                   |                 |                 | bit 8 |

|                  |       |                  |       |                   |                 |                 |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                  |       |                  | B     | yte 0             |                 |                 |       |

| bit 7            |       |                  |       |                   |                 |                 | bit 0 |

| Legend:          |       |                  |       |                   |                 |                 |       |

| R = Readable bit |       | W = Writable bi  | it    | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at PO | R     | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

Byte 1<15:8>: ECAN™ Message Byte 0 bit 15-8

bit 7-0 Byte 0<7:0>: ECAN Message Byte 1

#### 25.5 Programmable CRC Registers

#### **CRCCON: CRC CONTROL REGISTER** REGISTER 25-1: R/W-0 U-0 U-0 R-0 R-0 R-0 R-0 R-0 CSIDL VWORD<4:0> \_ bit 15 bit 8 R/W-0 R-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 CRCFUL CRCMPT CRCGO PLEN<3:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-14 Unimplemented: Read as '0' bit 13 CSIDL: CRC Stop in Idle Mode bit 1 = Discontinue module operation when device enters Idle mode 0 = Continue module operation in Idle mode bit 12-8 VWORD<4:0>: Pointer Value bits Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<3:0> is greater than 7, or 16 when PLEN<3:0> is less than or equal to 7. bit 7 **CRCFUL:** FIFO Full bit 1 = FIFO is full 0 = FIFO is not full bit 6 **CRCMPT:** FIFO Empty bit 1 = FIFO is empty 0 = FIFO is not empty bit 5 Unimplemented: Read as '0' bit 4 CRCGO: Start CRC bit 1 = Start CRC serial shifter 0 = Turn off CRC serial shifter after FIFO is empty bit 3-0 PLEN<3:0>: Polynomial Length bits Denotes the length of the polynomial to be generated minus 1.

Most instructions are a single word. Certain doubleword instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| TABLE 28-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS |

|-------------|-------------------------------------|

|-------------|-------------------------------------|

| #text<br>(text)<br>[text]<br>{}<br><n:m><br/>.b<br/>.d<br/>.S</n:m> | Means literal defined by "text"         Means "content of text"         Means "the location addressed by text"         Optional field or operation         Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select         Word mode selection (default) |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [text]<br>{}<br><n:m><br/>.b<br/>.d<br/>.S</n:m>                    | Means "the location addressed by text"         Optional field or operation         Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                               |

| {}<br><n:m><br/>.b<br/>.d<br/>.S</n:m>                              | Optional field or operation         Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                                                                              |

| <n:m><br/>.b<br/>.d<br/>.S</n:m>                                    | Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                                                                                                                  |

| .b<br>.d<br>.S                                                      | Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                                                                                                                                             |

| .d<br>.S                                                            | Double-Word mode selection       Shadow register select                                                                                                                                                                                                                                                           |

| .S                                                                  | Shadow register select                                                                                                                                                                                                                                                                                            |

|                                                                     | · ·                                                                                                                                                                                                                                                                                                               |

|                                                                     | Word mode selection (default)                                                                                                                                                                                                                                                                                     |

| .W                                                                  |                                                                                                                                                                                                                                                                                                                   |

| Acc                                                                 | One of two accumulators {A, B}                                                                                                                                                                                                                                                                                    |

| AWB                                                                 | Accumulator write back destination address register $\in$ {W13, [W13]+ = 2}                                                                                                                                                                                                                                       |

| bit4                                                                | 4-bit bit selection field (used in word addressed instructions) ∈ {015}                                                                                                                                                                                                                                           |

| C, DC, N, OV, Z                                                     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                                                                                                                                                                                                                                              |

| Expr                                                                | Absolute address, label or expression (resolved by the linker)                                                                                                                                                                                                                                                    |

| f                                                                   | File register address ∈ {0x00000x1FFF}                                                                                                                                                                                                                                                                            |

| lit1                                                                | 1-bit unsigned literal ∈ {0,1}                                                                                                                                                                                                                                                                                    |

| lit4                                                                | 4-bit unsigned literal ∈ {015}                                                                                                                                                                                                                                                                                    |

| lit5                                                                | 5-bit unsigned literal ∈ {031}                                                                                                                                                                                                                                                                                    |

| lit8                                                                | 8-bit unsigned literal ∈ {0255}                                                                                                                                                                                                                                                                                   |

| lit10                                                               | 10-bit unsigned literal $\in~\{0255\}$ for Byte mode, {0:1023} for Word mode                                                                                                                                                                                                                                      |

| lit14                                                               | 14-bit unsigned literal ∈ {016384}                                                                                                                                                                                                                                                                                |

| lit16                                                               | 16-bit unsigned literal ∈ {065535}                                                                                                                                                                                                                                                                                |

| lit23                                                               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                                                                                                                                                                                                                                             |

| None                                                                | Field does not require an entry, can be blank                                                                                                                                                                                                                                                                     |

| OA, OB, SA, SB                                                      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate                                                                                                                                                                                                                                       |

| PC                                                                  | Program Counter                                                                                                                                                                                                                                                                                                   |

| Slit10                                                              | 10-bit signed literal $\in$ {-512511}                                                                                                                                                                                                                                                                             |

| Slit16                                                              | 16-bit signed literal ∈ {-3276832767}                                                                                                                                                                                                                                                                             |

| Slit6                                                               | 6-bit signed literal $\in$ {-1616}                                                                                                                                                                                                                                                                                |

| Wb                                                                  | Base W register ∈ {W0W15}                                                                                                                                                                                                                                                                                         |

| Wd                                                                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                                                                                                                                                                                                                 |

| Wdo                                                                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                                                                                                                                                                                                              |

| Wm,Wn                                                               | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                                                                                       |