#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp204t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register</u>. The <u>C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.7.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

#### 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.8 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- · Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- · Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACC-SAT)

A block diagram of the DSP engine is shown in Figure 3-3.

# TABLE 3-1:DSP INSTRUCTIONSSUMMARY

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | A = A + x2              | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | A = x 2                 | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-37: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |

|-------|---------------------------------------------------------------------------------------|

|       | for the source and destination EA.                                                    |

|       | However, the 4-bit Wb (Register Offset)                                               |

|       | field is shared by both source and                                                    |

|       | destination (but typically only used by                                               |

|       | one).                                                                                 |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the data pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register                                | Indirect  | with    | Register  | Offset |  |  |  |

|-------|-----------------------------------------|-----------|---------|-----------|--------|--|--|--|

|       | Addressing mode is available only for W |           |         |           |        |  |  |  |

|       | (in X spac                              | ce) and W | /11 (in | Y space). |        |  |  |  |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Set up NVMCON for row programming open | rations                                 |

|------------------------------------------|-----------------------------------------|

| MOV #0x4001, W0                          | ;                                       |

| MOV W0, NVMCON                           | ; Initialize NVMCON                     |

| ; Set up a pointer to the first program  | memory location to be written           |

| ; program memory selected, and writes er | abled                                   |

| MOV #0x0000, W0                          | ;                                       |

| MOV W0, TBLPAG                           | ; Initialize PM Page Boundary SFR       |

| MOV #0x6000, W0                          | ; An example program memory address     |

| ; Perform the TBLWT instructions to writ | te the latches                          |

| ; Oth program word                       |                                         |

| MOV #LOW WORD 0, W2                      | ;                                       |

| MOV #HIGH_BYTE_0, W3                     | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

| ; 1st_program_word                       |                                         |

| MOV #LOW_WORD_1, W2                      | ;                                       |

| MOV #HIGH_BYTE_1, W3                     | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

| ; 2nd_program_word                       |                                         |

| MOV #LOW_WORD_2, W2                      | ;                                       |

| MOV #HIGH_BYTE_2, W3                     | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

| •                                        |                                         |

| •                                        |                                         |

| •                                        |                                         |

| ; 63rd_program_word                      |                                         |

| MOV #LOW_WORD_31, W2                     | ;                                       |

| MOV #HIGH_BYTE_31, W3                    | ;                                       |

| TBLWTL W2, [W0]                          | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                        | ; Write PM high byte into program latch |

|                                          |                                         |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | <pre>; Block all interrupts with priority &lt;7 ; for next 5 instructions</pre> |

|------|-------------|---------------------------------------------------------------------------------|

|      |             | ; for next 5 instructions                                                       |

| MOV  | #0x55, W0   |                                                                                 |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                              |

| MOV  | #0xAA, W1   | ;                                                                               |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                              |

| BSET | NVMCON, #WR | ; Start the erase sequence                                                      |

| NOP  |             | ; Insert two NOPs after the                                                     |

| NOP  |             | ; erase command is asserted                                                     |

|      |             |                                                                                 |

| U-0              | R/W-1                                                                          | R/W-0                                                                                                                             | R/W-0           | U-0                 | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|-----------------|-----------------|-------|--|--|--|--|

| —                |                                                                                | U2TXIP<2:0>                                                                                                                       |                 |                     |                 | U2RXIP<2:0>     |       |  |  |  |  |

| oit 15           |                                                                                |                                                                                                                                   |                 |                     | I               |                 | bi    |  |  |  |  |

|                  |                                                                                |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| U-0              | R/W-1                                                                          | R/W-0                                                                                                                             | R/W-0           | U-0                 | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

| _                |                                                                                | INT2IP<2:0>                                                                                                                       |                 |                     |                 | T5IP<2:0>       |       |  |  |  |  |

| bit 7            |                                                                                |                                                                                                                                   |                 |                     |                 |                 | bi    |  |  |  |  |

|                  |                                                                                |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| Legend:          |                                                                                |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| R = Readab       | le bit                                                                         | W = Writable                                                                                                                      |                 | U = Unimpler        | mented bit, rea | id as '0'       |       |  |  |  |  |

| -n = Value a     | t POR                                                                          | '1' = Bit is set                                                                                                                  |                 | '0' = Bit is cle    | ared            | x = Bit is unkn | iown  |  |  |  |  |

|                  |                                                                                |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| bit 15           | -                                                                              | nted: Read as '                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| bit 14-12        |                                                                                | <b>U2TXIP&lt;2:0&gt;:</b> UART2 Transmitter Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                 |                     |                 |                 |       |  |  |  |  |

|                  | •                                                                              | ipt is priority 7 (                                                                                                               | nignest priori  | ity interrupt)      |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled            |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| L:L 44           |                                                                                | -                                                                                                                                 |                 |                     |                 |                 |       |  |  |  |  |

| bit 11           | -                                                                              | nted: Read as '                                                                                                                   |                 | t Dui - uitu - hitu |                 |                 |       |  |  |  |  |

| bit 10-8         |                                                                                | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits                                                                               |                 |                     |                 |                 |       |  |  |  |  |

|                  | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul> |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | •                                                                              | •                                                                                                                                 |                 |                     |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled            |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| bit 7            |                                                                                | -                                                                                                                                 |                 |                     |                 |                 |       |  |  |  |  |

|                  | -                                                                              | nted: Read as '                                                                                                                   |                 | / hita              |                 |                 |       |  |  |  |  |

| bit 6-4          |                                                                                | : External Interi                                                                                                                 |                 |                     |                 |                 |       |  |  |  |  |

|                  | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul> |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled            |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| hit 2            |                                                                                | nted: Read as '                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| bit 3<br>bit 2-0 | -                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

| DIL 2-0          |                                                                                | Fimer5 Interrupt<br>.pt is priority 7 (                                                                                           | -               | ity interrunt)      |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   | ingriest priori | ity interrupt)      |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  | •                                                                              |                                                                                                                                   |                 |                     |                 |                 |       |  |  |  |  |

|                  |                                                                                | upt is priority 1                                                                                                                 | ablad           |                     |                 |                 |       |  |  |  |  |

|                  | 000 = mem                                                                      | pt source is dis                                                                                                                  | auleu           |                     |                 |                 |       |  |  |  |  |

| U-0         | U-0                                                                                              | U-0                                            | U-0             | R-1               | R-1              | R-1             | R-1   |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| _           | _                                                                                                | _                                              | _               |                   | LSTC             | H<3:0>          |       |  |  |  |  |

| oit 15      | ·                                                                                                |                                                |                 |                   |                  |                 | bit   |  |  |  |  |

|             |                                                                                                  |                                                |                 |                   |                  |                 |       |  |  |  |  |

| R-0         | R-0                                                                                              | R-0                                            | R-0             | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

| PPST7       | PPST6                                                                                            | PPST5                                          | PPST4           | PPST3             | PPST2            | PPST1           | PPST0 |  |  |  |  |

| pit 7       |                                                                                                  |                                                |                 |                   |                  |                 | bit   |  |  |  |  |

| _egend:     |                                                                                                  |                                                |                 |                   |                  |                 |       |  |  |  |  |

| R = Readab  | le bit                                                                                           | W = Writable                                   | bit             | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |  |

| n = Value a | t POR                                                                                            | '1' = Bit is se                                | t               | '0' = Bit is clea |                  | x = Bit is unki | nown  |  |  |  |  |

|             |                                                                                                  |                                                |                 |                   |                  |                 |       |  |  |  |  |

| bit 15-12   | Unimplemen                                                                                       |                                                |                 |                   |                  |                 |       |  |  |  |  |

| oit 11-8    |                                                                                                  |                                                | nannel Active I |                   |                  |                 |       |  |  |  |  |

|             | 1111 = No DI<br>1110-1000 =                                                                      |                                                | as occurred sir | ice system Res    | et               |                 |       |  |  |  |  |

|             |                                                                                                  |                                                | as by DMA Cł    | nannel 7          |                  |                 |       |  |  |  |  |

|             |                                                                                                  |                                                | as by DMA Ch    |                   |                  |                 |       |  |  |  |  |

|             |                                                                                                  |                                                | as by DMA Cl    |                   |                  |                 |       |  |  |  |  |

|             | 0100 = Last data transfer was by DMA Channel 4                                                   |                                                |                 |                   |                  |                 |       |  |  |  |  |

|             | 0011 = Last data transfer was by DMA Channel 3                                                   |                                                |                 |                   |                  |                 |       |  |  |  |  |

|             |                                                                                                  | 0010 = Last data transfer was by DMA Channel 2 |                 |                   |                  |                 |       |  |  |  |  |

|             | 0001 = Last data transfer was by DMA Channel 1<br>0000 = Last data transfer was by DMA Channel 0 |                                                |                 |                   |                  |                 |       |  |  |  |  |

| oit 7       | PPST7: Channel 7 Ping-Pong Mode Status Flag bit                                                  |                                                |                 |                   |                  |                 |       |  |  |  |  |

|             | 1 = DMA7STB register selected                                                                    |                                                |                 |                   |                  |                 |       |  |  |  |  |

|             | 0 = DMA7STA register selected                                                                    |                                                |                 |                   |                  |                 |       |  |  |  |  |

| oit 6       | PPST6: Chan                                                                                      | inel 6 Ping-Po                                 | ng Mode Statu   | is Flag bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA6STE<br>0 = DMA6STA                                                                       | U U                                            |                 |                   |                  |                 |       |  |  |  |  |

| bit 5       | PPST5: Chan                                                                                      | inel 5 Ping-Po                                 | ng Mode Statu   | is Flag bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA5STE                                                                                      | -                                              | -               | 0                 |                  |                 |       |  |  |  |  |

|             | 0 = DMA5STA                                                                                      |                                                |                 |                   |                  |                 |       |  |  |  |  |

| oit 4       | PPST4: Chan                                                                                      | inel 4 Ping-Po                                 | ng Mode Statu   | ıs Flag bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA4STB register selected                                                                    |                                                |                 |                   |                  |                 |       |  |  |  |  |

|             | 0 = DMA4STA register selected                                                                    |                                                |                 |                   |                  |                 |       |  |  |  |  |

| oit 3       |                                                                                                  | -                                              | ng Mode Statu   | is Flag bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA3STB register selected<br>0 = DMA3STA register selected                                   |                                                |                 |                   |                  |                 |       |  |  |  |  |

| oit 2       |                                                                                                  | -                                              | ng Mode Statu   | is Elag bit       |                  |                 |       |  |  |  |  |

|             |                                                                                                  | -                                              | -               | is Flag bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA2STB register selected<br>0 = DMA2STA register selected                                   |                                                |                 |                   |                  |                 |       |  |  |  |  |

| oit 1       |                                                                                                  | -                                              | ng Mode Statu   | ıs Flaq bit       |                  |                 |       |  |  |  |  |

|             | 1 = DMA1STE                                                                                      | -                                              | -               | ie i i i g i i i  |                  |                 |       |  |  |  |  |

|             | 0 = DMA1STA                                                                                      | -                                              |                 |                   |                  |                 |       |  |  |  |  |

| bit 0       |                                                                                                  | -                                              |                 | e Elaa bit        |                  |                 |       |  |  |  |  |

|             | PPST0: Channel 0 Ping-Pong Mode Status Flag bit                                                  |                                                |                 |                   |                  |                 |       |  |  |  |  |

| JILU        | 1 = DMA0STE                                                                                      | -                                              | -               | is Flag bit       |                  |                 |       |  |  |  |  |

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- bit 3 CF: Clock Fail Detect bit (read/clear by application)

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2 Unimplemented: Read as '0'

- bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 39. "Oscillator (Part III)"** (DS70216) in the *"dsPIC33F/PIC24H Family Reference Manual"* (available from the Microchip website) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

# 9.4 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

# 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 27.1 "Configuration Bits**" for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the status bits, LOCK (OSCCON<5>) and the CF (OSCCON<3>) are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 39. "Oscillator (Part III)" (DS70216) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

# 9.5 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

<sup>© 2007-2012</sup> Microchip Technology Inc.

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section "30. I/O Ports with Peripheral Pin Select" (DS70190) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

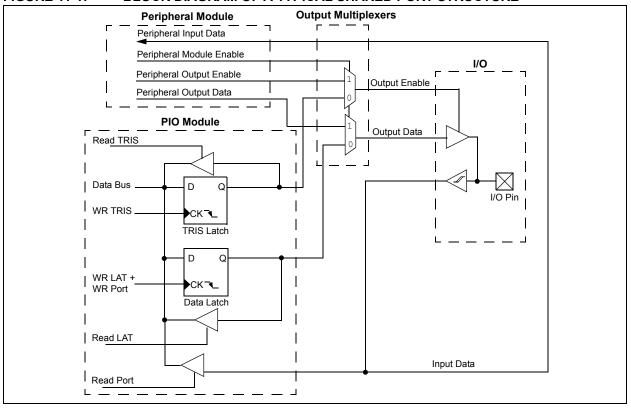

## 11.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2012 Microchip Technology Inc.

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| U-0                | U-0                                                  | U-0                                                                                                      | R/W-1         | R/W-1             | R/W-1            | R/W-1           | R/W-1 |  |  |  |

|--------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|

| —                  |                                                      | _                                                                                                        |               |                   | U1CTSR<4:0       | >               |       |  |  |  |

| bit 15             |                                                      |                                                                                                          |               |                   |                  |                 | bit 8 |  |  |  |

|                    |                                                      |                                                                                                          | <b>D</b> 44/4 |                   |                  | D 44/4          |       |  |  |  |

| U-0                | U-0                                                  | U-0                                                                                                      | R/W-1         | R/W-1             | R/W-1            | R/W-1           | R/W-1 |  |  |  |

| -:+ 7              | _                                                    | —                                                                                                        |               |                   | U1RXR<4:0>       | •               | h:+ 0 |  |  |  |

| bit 7              |                                                      |                                                                                                          |               |                   |                  |                 | bit C |  |  |  |

| Legend:            |                                                      |                                                                                                          |               |                   |                  |                 |       |  |  |  |

| R = Readab         | le bit                                               | W = Writable                                                                                             | oit           | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |

| -n = Value a       | t POR                                                | '1' = Bit is set                                                                                         |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |

| bit 15-13          | Unimpleme                                            | nted: Read as '                                                                                          | )'            |                   |                  |                 |       |  |  |  |

| bit 12-8           | -                                                    | <b>U1CTSR&lt;4:0&gt;:</b> Assign UART1 Clear to Send ( $\overline{U1CTS}$ ) to the corresponding RPn pin |               |                   |                  |                 |       |  |  |  |

|                    |                                                      | 11111 = Input tied to Vss                                                                                |               |                   |                  |                 |       |  |  |  |

|                    |                                                      | ut tied to RP25                                                                                          |               |                   |                  |                 |       |  |  |  |

|                    | •                                                    |                                                                                                          |               |                   |                  |                 |       |  |  |  |

|                    | •                                                    |                                                                                                          |               |                   |                  |                 |       |  |  |  |

|                    |                                                      |                                                                                                          |               |                   |                  |                 |       |  |  |  |

|                    | •                                                    |                                                                                                          |               |                   |                  |                 |       |  |  |  |

|                    |                                                      | ut tied to RP1<br>ut tied to RP0                                                                         |               |                   |                  |                 |       |  |  |  |

| oit 7-5            | 00000 <b>= Inp</b>                                   |                                                                                                          | )'            |                   |                  |                 |       |  |  |  |

|                    | 00000 = Inp<br>Unimpleme                             | ut tied to RP0                                                                                           |               | 1RX) to the cor   | responding RF    | n pin           |       |  |  |  |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(                                                                       |               | 1RX) to the cor   | responding RF    | n pin           |       |  |  |  |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss                                   |               | 1RX) to the cor   | responding RF    | 'n pin          |       |  |  |  |

| bit 7-5<br>bit 4-0 | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss                                   |               | 1RX) to the cor   | responding RF    | 'n pin          |       |  |  |  |

#### REGISTER 11-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

00001 = Input tied to RP1 00000 = Input tied to RP0

| U-0           | U-0                                                                | U-0                                                                | U-0              | U-0               | U-0                | U-0             | U-0                               |  |  |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------|--------------------------------------------------------------------|------------------|-------------------|--------------------|-----------------|-----------------------------------|--|--|--|--|--|--|--|--|--|

| _             | _                                                                  | _                                                                  | _                | —                 | _                  | _               | _                                 |  |  |  |  |  |  |  |  |  |

| bit 15        |                                                                    |                                                                    |                  |                   |                    |                 | bit 8                             |  |  |  |  |  |  |  |  |  |

|               |                                                                    |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                              | R/W-0                                                              | U-0              | R/W-0             | R/W-0              | R/W-0           | R/W-0                             |  |  |  |  |  |  |  |  |  |

| IVRIE         | WAKIE                                                              | ERRIE                                                              |                  | FIFOIE            | RBOVIE             | RBIE            | TBIE                              |  |  |  |  |  |  |  |  |  |

| bit 7         |                                                                    |                                                                    |                  |                   |                    |                 | bit (                             |  |  |  |  |  |  |  |  |  |

| Legend:       |                                                                    | C = Writable b                                                     | oit. but only '( | )' can be writter | n to clear the bit |                 |                                   |  |  |  |  |  |  |  |  |  |

| R = Readabl   | e bit                                                              | W = Writable                                                       |                  |                   | mented bit, read   |                 |                                   |  |  |  |  |  |  |  |  |  |

| -n = Value at |                                                                    | '1' = Bit is set                                                   |                  | '0' = Bit is cle  |                    | x = Bit is unkr | iown                              |  |  |  |  |  |  |  |  |  |

|               |                                                                    |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 15-8      | Unimplemer                                                         | nted: Read as '                                                    | )'               |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 7         | IVRIE: Invalio                                                     | d Message Rec                                                      | eived Interru    | pt Enable bit     |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               | 1 = Interrupt Request Enabled                                      |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               |                                                                    | Request not en                                                     |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| oit 6         |                                                                    | WAKIE: Bus Wake-up Activity Interrupt Flag bit                     |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               | 1 = Interrupt Request Enabled                                      |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| L:1 F         |                                                                    | 0 = Interrupt Request not enabled                                  |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 5         |                                                                    | ERRIE: Error Interrupt Enable bit                                  |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               |                                                                    | 1 = Interrupt Request Enabled<br>0 = Interrupt Request not enabled |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 4         | -                                                                  |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               | -                                                                  | nted: Read as '(                                                   |                  | a hit             |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 3         |                                                                    | ) Almost Full Inf<br>Request Enable                                |                  | ebit              |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               | 1 = Interrupt Request Enabled<br>0 = Interrupt Request not enabled |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 2         | <b>RBOVIE:</b> RX Buffer Overflow Interrupt Enable bit             |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               | 1 = Interrupt Request Enabled                                      |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               | 0 = Interrupt Request not enabled                                  |                                                                    |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 1         | RBIE: RX Bu                                                        | RBIE: RX Buffer Interrupt Enable bit                               |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               |                                                                    | Request Enable                                                     |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               |                                                                    | Request not en                                                     |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

| bit 0         |                                                                    | ffer Interrupt En                                                  |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               |                                                                    | Request Enable                                                     |                  |                   |                    |                 |                                   |  |  |  |  |  |  |  |  |  |

|               | 0 = interrupt                                                      | Request not en                                                     | apied            |                   |                    |                 | 0 = Interrupt Request not enabled |  |  |  |  |  |  |  |  |  |

| REGISTER 21     | -2: AD1C                                                                                                                                                                                     | ON2: ADC1      | CONTROL RE                                | GISTER 2         |                 |                 |               |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------|------------------|-----------------|-----------------|---------------|--|--|

| R/W-0           | R/W-0                                                                                                                                                                                        | R/W-0          | U-0                                       | U-0              | R/W-0           | R/W-0           | R/W-0         |  |  |

|                 | VCFG<2:0>                                                                                                                                                                                    |                | —                                         |                  | CSCNA           | CHPS            | 6<1:0>        |  |  |

| bit 15          |                                                                                                                                                                                              |                |                                           |                  |                 |                 | bit           |  |  |

| R-0             | U-0                                                                                                                                                                                          | R/W-0          | R/W-0                                     | R/W-0            | R/W-0           | R/W-0           | R/W-0         |  |  |

| BUFS            | — SMPI<3:0>                                                                                                                                                                                  |                | BUFM                                      | ALTS             |                 |                 |               |  |  |

| bit 7           |                                                                                                                                                                                              |                |                                           |                  |                 |                 | bit           |  |  |

| Legend:         |                                                                                                                                                                                              |                |                                           |                  |                 |                 |               |  |  |

| R = Readable b  | oit                                                                                                                                                                                          | W = Writab     | le bit                                    | U = Unimple      | mented bit, rea | id as '0'       |               |  |  |

| -n = Value at P | OR                                                                                                                                                                                           | '1' = Bit is s | set                                       | '0' = Bit is cle | eared           | x = Bit is unkr | nown          |  |  |

| bit 15-13       | VCFG<2:0>:                                                                                                                                                                                   | Converter Ve   | oltage Reference                          | Configuration    | bits            |                 |               |  |  |

|                 | A                                                                                                                                                                                            | DREF+          | ADREF-                                    |                  |                 |                 |               |  |  |

|                 | 000                                                                                                                                                                                          | Avdd           | Avss                                      |                  |                 |                 |               |  |  |

|                 | 001 Exte                                                                                                                                                                                     | rnal VREF+     | Avss                                      |                  |                 |                 |               |  |  |

|                 | 010                                                                                                                                                                                          | Avdd           | External VREF-                            | _                |                 |                 |               |  |  |

|                 |                                                                                                                                                                                              | rnal VREF+     | External VREF-                            | _                |                 |                 |               |  |  |

|                 | 1xx                                                                                                                                                                                          | Avdd           | Avss                                      |                  |                 |                 |               |  |  |

| bit 12-11       | Unimplemen                                                                                                                                                                                   | ted: Read a    | <b>s</b> '0'                              |                  |                 |                 |               |  |  |

| bit 10          | CSCNA: Scan Input Selections for CH0+ during Sample A bit                                                                                                                                    |                |                                           |                  |                 |                 |               |  |  |

|                 | <ul><li>1 = Scan inputs</li><li>0 = Do not scan inputs</li></ul>                                                                                                                             |                |                                           |                  |                 |                 |               |  |  |

| <b>h</b> # 0 0  |                                                                                                                                                                                              | •              |                                           |                  |                 |                 |               |  |  |

| bit 9-8         |                                                                                                                                                                                              |                | nnels Utilized bits <1:0> is: U-0, Un     |                  | Bood on (o)     |                 |               |  |  |

|                 |                                                                                                                                                                                              |                | CH2 and CH3                               | implementet      | i, Reau as 0    |                 |               |  |  |

|                 | 01 = Convert                                                                                                                                                                                 |                |                                           |                  |                 |                 |               |  |  |

|                 | 00 = Convert                                                                                                                                                                                 | s CH0          |                                           |                  |                 |                 |               |  |  |

| bit 7           |                                                                                                                                                                                              |                | it (only valid when                       |                  |                 |                 |               |  |  |

|                 | <ul> <li>1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7</li> <li>0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF</li> </ul> |                |                                           |                  |                 |                 |               |  |  |

| <b>h</b> # 0    |                                                                                                                                                                                              |                | -                                         | user snould a    | ccess data in u | X8-UXF          |               |  |  |