#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b; D/A 2x16b                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

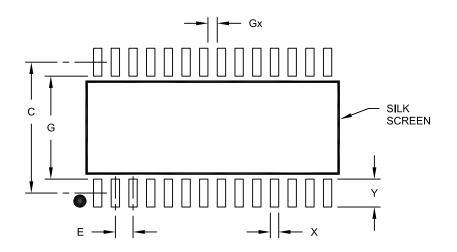

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp802-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304, the of dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

- VREF+/VREF- pins used when external voltage reference for ADC module is implemented

- Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### 3.4 Special MCU Features

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

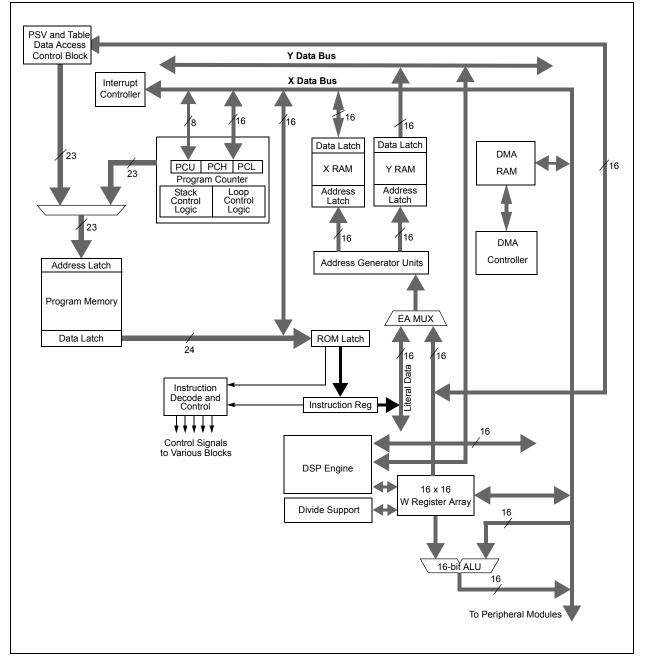

#### FIGURE 3-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 CPU CORE BLOCK DIAGRAM

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-37: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |

|-------|---------------------------------------------------------------------------------------|

|       | for the source and destination EA.                                                    |

|       | However, the 4-bit Wb (Register Offset)                                               |

|       | field is shared by both source and                                                    |

|       | destination (but typically only used by                                               |

|       | one).                                                                                 |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the data pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register   | Indirect  | with    | Register    | Offset |

|-------|------------|-----------|---------|-------------|--------|

|       | Addressir  | ng mode i | is ava  | ilable only | for W9 |

|       | (in X spac | ce) and W | /11 (in | Y space).   |        |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 5.6 Flash Control Registers

#### R/SO-0(1) R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> U-0 U-0 U-0 U-0 U-0 WR WREN WRERR bit 15 bit 8 R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> R/W-0<sup>(1)</sup> U-0 U-0 U-0 NVMOP<3:0>(2) ERASE bit 7 bit 0 Leaend: SO = Settable only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown WR: Write Control bit bit 15 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is cleared by hardware once operation is complete 0 = Program or erase operation is complete and inactive bit 14 WREN: Write Enable bit 1 = Enable Flash program/erase operations 0 = Inhibit Flash program/erase operations bit 13 WRERR: Write Sequence Error Flag bit 1 = An improper program or erase sequence attempt or termination has occurred (bit is set automatically on any set attempt of the WR bit) 0 = The program or erase operation completed normally bit 12-7 Unimplemented: Read as '0' bit 6 ERASE: Erase/Program Enable bit 1 = Perform the erase operation specified by NVMOP<3:0> on the next WR command 0 = Perform the program operation specified by NVMOP<3:0> on the next WR command bit 5-4 Unimplemented: Read as '0' NVMOP<3:0>: NVM Operation Select bits<sup>(2)</sup> bit 3-0 If ERASE = 1: 1111 = Memory bulk erase operation 1110 = Reserved 1101 = Erase General Segment 1100 = Erase Secure Segment 1011 = Reserved 0011 = No operation 0010 = Memory page erase operation 0001 = No operation 0000 = Erase a single Configuration register byte If ERASE = 0: 1111 = No operation 1110 = Reserved 1101 = No operation 1100 = No operation 1011 = Reserved 0011 = Memory word program operation 0010 = No operation 0001 = Memory row program operation 0000 = Program a single Configuration register byte Note 1: These bits can only be reset on POR.

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

2: All other combinations of NVMOP<3:0> are unimplemented.

| REGISTER      | 7-19: IPC4         |                       | PRIORITY        | CONTROL R        | EGISTER 4      |                 |       |

|---------------|--------------------|-----------------------|-----------------|------------------|----------------|-----------------|-------|

| U-0           | R/W-1              | R/W-0                 | R/W-0           | U-0              | R/W-1          | R/W-0           | R/W-0 |

|               |                    | CNIP<2:0>             |                 | <u> </u>         |                | CMIP<2:0>       |       |

| bit 15        |                    |                       |                 |                  |                |                 | bit   |

| U-0           | R/W-1              | R/W-0                 | R/W-0           | U-0              | R/W-1          | R/W-0           | R/W-0 |

| _             |                    | MI2C1IP<2:0>          |                 | _                |                | SI2C1IP<2:0>    |       |

| bit 7         |                    |                       |                 |                  |                |                 | bit   |

| Legend:       |                    |                       |                 |                  |                |                 |       |

| R = Readabl   | le bit             | W = Writable I        | oit             | U = Unimpler     | mented bit, re | ad as '0'       |       |

| -n = Value at |                    | '1' = Bit is set      |                 | '0' = Bit is cle |                | x = Bit is unkn | own   |

|               |                    |                       |                 |                  |                |                 | •     |

| bit 15        | Unimpleme          | ented: Read as '0     | )'              |                  |                |                 |       |

| bit 14-12     | CNIP<2:0>          | : Change Notifica     | tion Interrup   | t Priority bits  |                |                 |       |

|               |                    | rupt is priority 7 (ł | -               | -                |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               | •<br>001 = Inter   | rupt is priority 1    |                 |                  |                |                 |       |

|               |                    | rupt source is disa   | abled           |                  |                |                 |       |

| bit 11        | Unimpleme          | ented: Read as 'o     | )'              |                  |                |                 |       |

| bit 10-8      | CMIP<2:0>          | : Comparator Inte     | errupt Priority | y bits           |                |                 |       |

|               | 111 = Inter        | rupt is priority 7 (ł | nighest priori  | ty interrupt)    |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               |                    | rupt is priority 1    |                 |                  |                |                 |       |

|               |                    | rupt source is disa   |                 |                  |                |                 |       |

| bit 7         | -                  | ented: Read as '0     |                 |                  |                |                 |       |

| bit 6-4       |                    | :0>: I2C1 Master      |                 |                  | 3              |                 |       |

|               | 111 <b>= Inter</b> | rupt is priority 7 (I | nighest priori  | ty interrupt)    |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               |                    | rupt is priority 1    |                 |                  |                |                 |       |

|               |                    | rupt source is disa   |                 |                  |                |                 |       |

| bit 3         | -                  | ented: Read as '0     |                 |                  |                |                 |       |

| bit 2-0       |                    | :0>: I2C1 Slave E     |                 |                  |                |                 |       |

|               | 111 = Inter        | rupt is priority 7 (ł | nghest priori   | ty interrupt)    |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               | •                  |                       |                 |                  |                |                 |       |

|               |                    | rupt is priority 1    |                 |                  |                |                 |       |

|               | 000 <b>= Inter</b> | rupt source is disa   | abled           |                  |                |                 |       |

#### - ---.... ------

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER     | 7-30: IPC1                             | 9: INTERRUPT                                                                         | PRIORITY       | CONTROL          | REGISTER 19           | 1                         |       |

|--------------|----------------------------------------|--------------------------------------------------------------------------------------|----------------|------------------|-----------------------|---------------------------|-------|

| U-0          | R/W-1                                  | R/W-0                                                                                | R/W-0          | U-0              | R/W-0                 | R/W-0                     | R/W-0 |

| _            |                                        | DAC1LIP<2:0>(                                                                        | 1)             |                  | D                     | AC1RIP<2:0> <sup>(*</sup> | 1)    |

| bit 15       | ·                                      |                                                                                      |                |                  | •                     |                           | bit 8 |

| U-0          | U-0                                    | U-0                                                                                  | U-0            | U-0              | U-0                   | U-0                       | U-0   |

| _            | _                                      | _                                                                                    | _              | _                | _                     | _                         | _     |

| bit 7        | ·                                      | ·                                                                                    |                |                  | ·                     | •                         | bit ( |

| Legend:      |                                        |                                                                                      |                |                  |                       |                           |       |

| R = Readab   | le bit                                 | W = Writable                                                                         | bit            | U = Unimple      | mented bit, read      | l as '0'                  |       |

| -n = Value a | t POR                                  | '1' = Bit is set                                                                     |                | '0' = Bit is cle | eared                 | x = Bit is unkr           | nown  |

| bit 14-12    | 111 = Interr<br>•<br>•                 | 2:0>: DAC Left C<br>rupt is priority 7 (I                                            |                |                  |                       |                           |       |

|              |                                        | upt is priority if                                                                   | abled          |                  |                       |                           |       |

| bit 11       | Unimpleme                              | ented: Read as '                                                                     | 0'             |                  |                       |                           |       |

| bit 10-8     | 111 = Interr<br>•<br>•<br>001 = Interr | 2:0>: DAC Right<br>rupt is priority 7 (I<br>rupt is priority 1<br>rupt source is dis | highest priori |                  | us bit <sup>(1)</sup> |                           |       |

| bit 7-0      |                                        | ented: Read as '                                                                     |                |                  |                       |                           |       |

|              | -                                      |                                                                                      |                |                  |                       |                           |       |

#### REGISTER 7-30: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

**Note 1:** Interrupts are disabled on devices without Audio DAC modules.

NOTES:

#### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to **"Pin Diagrams"** for the available pins and their functionality.

#### 11.3 Configuring Analog Port Pins

The AD1PCFGL and TRIS registers control the operation of the Analog-to-Digital (ADC) port pins. The port pins that are to function as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP, as shown in Example 11-1.

#### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/ X04 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-ofstates even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-ofstate.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

# MOV0xFF00, W0; Configure PORTB<15:8> as inputsMOVW0, TRISBB; and PORTB<7:0> as outputsNOP; Delay 1 cyclebtssPORTB, #13; Next Instruction

PORT WRITE/READ EXAMPLE

EXAMPLE 11-1:

#### **19.4 ECAN Resources**

Many useful resources related to ECAN are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                          |

|       | Devices.aspx?dDocName=en532311                                                                                 |

#### 19.4.1 KEY RESOURCES

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER      | 19-15: CIDU               | FPN14: ECA                                 |                  |                                    | RPUINIER        | REGISTER        |       |  |  |

|---------------|---------------------------|--------------------------------------------|------------------|------------------------------------|-----------------|-----------------|-------|--|--|

| R/W-0         | R/W-0                     | R/W-0                                      | R/W-0            | R/W-0                              | R/W-0           | R/W-0           | R/W-0 |  |  |

|               | F15BP<3:0>                |                                            |                  | F15BP<3:0> F14BP<3:0>              |                 |                 |       |  |  |

| bit 15        |                           |                                            |                  |                                    |                 |                 | bit 8 |  |  |

| R/W-0         | R/W-0                     | R/W-0                                      | R/W-0            | R/W-0                              | R/W-0           | R/W-0           | R/W-0 |  |  |

|               | F13BP<3:0>                |                                            |                  |                                    | F12BI           | ><3:0>          |       |  |  |

| bit 7         |                           |                                            |                  |                                    |                 |                 | bit 0 |  |  |

|               |                           |                                            |                  |                                    |                 |                 |       |  |  |

| Legend:       |                           | C = Writable                               | bit, but only '0 | ' can be writter                   | to clear the bi | t               |       |  |  |

| R = Readabl   | able bit W = Writable bit |                                            |                  | U = Unimplemented bit, read as '0' |                 |                 |       |  |  |

| -n = Value at | at POR '1' = Bit is set   |                                            |                  | '0' = Bit is cle                   | ared            | x = Bit is unkr | nown  |  |  |

|               |                           |                                            |                  |                                    |                 |                 |       |  |  |

| bit 15-12     | F15BP<3:0                 | RX Buffer ma                               | sk for Filter 15 | 5                                  |                 |                 |       |  |  |

|               | 1111 = Filte              | er hits received in                        | n RX FIFO buf    | ffer                               |                 |                 |       |  |  |

|               | 1110 <b>= Filte</b>       | er hits received in                        | n RX Buffer 14   | ŀ                                  |                 |                 |       |  |  |

|               | •                         |                                            |                  |                                    |                 |                 |       |  |  |

|               | •                         |                                            |                  |                                    |                 |                 |       |  |  |

|               | •                         |                                            |                  |                                    |                 |                 |       |  |  |

|               | 0001                      | er hits received in<br>ar hits received in |                  |                                    |                 |                 |       |  |  |

| bit 11-8      | F14BP<3:0                 | >: RX Buffer ma                            | sk for Filter 14 | (same values                       | as bit 15-12)   |                 |       |  |  |

| bit 7-4       | F13BP<3:0                 | >: RX Buffer ma                            | sk for Filter 13 | (same values                       | as bit 15-12)   |                 |       |  |  |

|               |                           |                                            |                  |                                    |                 |                 |       |  |  |

#### REGISTER 19-15: CiBUFPNT4: ECAN™ FILTER 12-15 BUFFER POINTER REGISTER

bit 3-0 **F12BP<3:0>:** RX Buffer mask for Filter 12 (same values as bit 15-12)

| U-0          | U-0           | U-0               | U-0            | U-0              | U-0                             | U-0             | U-0   |

|--------------|---------------|-------------------|----------------|------------------|---------------------------------|-----------------|-------|

| —            |               |                   | —              | —                | _                               | _               | —     |

| bit 15       |               |                   |                |                  |                                 |                 | bit 8 |

|              |               |                   |                |                  |                                 |                 |       |

| R/W-0        | R/W-0         | R/W-0             | R/W-0          | R/W-0            | R/W-0                           | R/W-0           | R/W-0 |

| CVREN        | CVROE         | CVRR              | CVRSS          |                  | CVR                             | <3:0>           |       |

| bit 7        |               |                   |                |                  |                                 |                 | bit C |

|              |               |                   |                |                  |                                 |                 |       |

| Legend:      |               |                   |                |                  |                                 |                 |       |

| R = Readable | e bit         | W = Writable      | bit            | U = Unimpler     | nented bit, read                | l as '0'        |       |

| n = Value at | POR           | '1' = Bit is set  | t              | '0' = Bit is cle | ared                            | x = Bit is unkr | iown  |

|              |               |                   |                |                  |                                 |                 |       |

| bit 15-8     | Unimplemen    | ted: Read as '    | 0'             |                  |                                 |                 |       |

| oit 7        | CVREN: Com    | parator Voltag    | e Reference E  | Enable bit       |                                 |                 |       |

|              | 1 = CVREF cir | rcuit powered     | on             |                  |                                 |                 |       |

|              | 0 = CVREF cit | rcuit powered     | down           |                  |                                 |                 |       |

| oit 6        | CVROE: Corr   | parator VREF      | Output Enable  | e bit            |                                 |                 |       |

|              |               | oltage level is o |                |                  |                                 |                 |       |

|              | 0 = CVREF VC  | oltage level is o | disconnected f | from CVREF pin   | 1                               |                 |       |

| oit 5        | CVRR: Comp    | arator VREF R     | ange Selectio  | n bit            |                                 |                 |       |

|              |               | U U               |                |                  | VRSRC/24 step :<br>CVRSRC/32 st |                 |       |

| bit 4        | CVRSS: Com    | parator VREF      | Source Select  | ion bit          |                                 |                 |       |

|              |               |                   |                | C = VREF+ - VF   |                                 |                 |       |

|              | 0 = Compara   | tor reference s   | source CVRSR   | c = AVDD - AV    | SS                              |                 |       |

| hit 2 0      | OVD 42.05 . C |                   |                |                  | 0.0. <15 hite                   |                 |       |

#### REGISTER 23-2: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

bit 3-0 **CVR<3:0>:** Comparator VREF Value Selection  $0 \le CVR<3:0> \le 15$  bits  $\frac{When CVRR = 1:}{CVREF = (CVR<3:0>/24) \bullet (CVRSRC)}$ When CVRR = 0:

$\overline{CVREF} = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)$

| R/W-0              | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                                                                                                        | R/W-0                                                                        | R/W-0                                                | R/W-0                          | R/W-0              | R/W-0                  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|--------------------|------------------------|

| ALRMEN             | CHIME                                                                                                                                                        |                                                                                                                                                                                                                              | AMA                                                                          | SK<3:0>                                              |                                | ALRMP              | FR<1:0>                |

| bit 15             | •                                                                                                                                                            |                                                                                                                                                                                                                              |                                                                              |                                                      |                                |                    | bit 8                  |

| R/W-0              | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                                                                                                        | R/W-0                                                                        | R/W-0                                                | R/W-0                          | R/W-0              | R/W-0                  |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                              | ARP                                                                          | T<7:0>                                               |                                |                    |                        |

| bit 7              |                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                              |                                                      |                                |                    | bit (                  |

| Legend:            |                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                              |                                                      |                                |                    |                        |

| R = Readabl        | e bit                                                                                                                                                        | W = Writable                                                                                                                                                                                                                 | bit                                                                          | U = Unimplen                                         | nented bit, read               | l as '0'           |                        |

| -n = Value at      | POR                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                             | t                                                                            | '0' = Bit is clea                                    | ared                           | x = Bit is unkn    | iown                   |

| 6:4 <i>7</i>       |                                                                                                                                                              | Alere Freble bit                                                                                                                                                                                                             |                                                                              |                                                      |                                |                    |                        |

| bit 15             | 1 = Alarm<br>CHIM                                                                                                                                            | : Alarm Enable bit<br>n is enabled (clear<br>IE = 0)<br>n is disabled                                                                                                                                                        |                                                                              | ally after an ala                                    | rm event when                  | ever ARPT<7:0      | )> = 0x00 and          |

| bit 14             | CHIME: C                                                                                                                                                     | hime Enable bit                                                                                                                                                                                                              |                                                                              |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | e is enabled; ARP<br>e is disabled; ARF                                                                                                                                                                                      |                                                                              |                                                      |                                | 00 to 0xFF         |                        |

| bit 13-10          |                                                                                                                                                              | 3:0>: Alarm Mask                                                                                                                                                                                                             |                                                                              |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | eserved – do not u                                                                                                                                                                                                           | •                                                                            |                                                      |                                |                    |                        |

|                    | 101x <b>= R</b>                                                                                                                                              | eserved – do not ι                                                                                                                                                                                                           | lse                                                                          |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | nce a year (excep                                                                                                                                                                                                            | t when config                                                                | ured for Februa                                      | ry 29th, once e                | very 4 years)      |                        |

|                    |                                                                                                                                                              | nce a month                                                                                                                                                                                                                  |                                                                              |                                                      |                                |                    |                        |

|                    | 0111 = O<br>0110 = O                                                                                                                                         | nce a week                                                                                                                                                                                                                   |                                                                              |                                                      |                                |                    |                        |

|                    | 0110 <b>– O</b>                                                                                                                                              | •                                                                                                                                                                                                                            |                                                                              |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | very 10 minutes                                                                                                                                                                                                              |                                                                              |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | very minute                                                                                                                                                                                                                  |                                                                              |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | very 10 seconds                                                                                                                                                                                                              |                                                                              |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | very second                                                                                                                                                                                                                  |                                                                              |                                                      |                                |                    |                        |

|                    |                                                                                                                                                              | very half second                                                                                                                                                                                                             |                                                                              |                                                      |                                |                    |                        |

| 1.1.0.0            |                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                              |                                                      | L 10.                          |                    |                        |

| bit 9-8            |                                                                                                                                                              |                                                                                                                                                                                                                              | -                                                                            | Vindow Pointer                                       |                                |                    |                        |

| bit 9-8            | Points to t                                                                                                                                                  | he corresponding                                                                                                                                                                                                             | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM                                                                                                                                      | he corresponding /<br>PTR<1:0> value d                                                                                                                                                                                       | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u>                                                                                                                    | he corresponding /<br>PTR<1:0> value d<br><u>.&lt;15:8&gt;:</u>                                                                                                                                                              | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u>                                                                                                                    | he corresponding <i>,</i><br>PTR<1:0> value d<br><u>-&lt;15:8&gt;:</u><br>nplemented                                                                                                                                         | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u><br>11 = Unin<br>10 = ALR<br>01 = ALR                                                                               | he corresponding <i>,</i><br>PTR<1:0> value d<br><u>-&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD                                                                                                                         | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u><br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR                                                                   | he corresponding <i>,</i><br>PTR<1:0> value d<br><u>_&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN                                                                                                                 | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u><br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br><u>ALRMVAL</u>                                                 | he corresponding <i>J</i><br>PTR<1:0> value d<br><u>&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN<br><u>_&lt;7:0&gt;:</u>                                                                                          | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u><br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br><u>ALRMVAL</u><br>11 = Unin                                    | he corresponding <i>,</i><br>PTR<1:0> value d<br><u>-&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN<br><u>-&lt;7:0&gt;:</u><br>nplemented                                                                           | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u><br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br><u>ALRMVAL</u><br>11 = Unin<br>10 = ALR                        | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>-&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN<br><u>-&lt;7:0&gt;:</u><br>nplemented<br>MDAY                                                                   | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

| bit 9-8            | Points to t<br>the ALRM<br><u>ALRMVAL</u><br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br><u>ALRMVAL</u><br>11 = Unin                                    | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>-&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN<br><u>-&lt;7:0&gt;:</u><br>nplemented<br>MDAY<br>MHR                                                            | Alarm Value re                                                               | gisters when re                                      | ading ALRMVA                   |                    |                        |

|                    | Points to t<br>the ALRM<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR                                    | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>-&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN<br><u>-&lt;7:0&gt;:</u><br>nplemented<br>MDAY<br>MHR                                                            | Alarm Value re<br>ecrements on                                               | gisters when re<br>every read or w                   | ading ALRMVA                   |                    |                        |

|                    | Points to t<br>the ALRM<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>ALRMVAL<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>ARPT<7:              | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>-&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN<br><u>-&lt;7:0&gt;:</u><br>nplemented<br>MDAY<br>MHR<br>MSEC                                                    | Alarm Value re<br>ecrements on<br>Counter Value                              | gisters when re<br>every read or w                   | ading ALRMVA                   |                    |                        |

| bit 9-8<br>bit 7-0 | Points to t<br>the ALRM<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>ALRMVAL<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>ARPT<7:              | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>&lt;15:8&gt;:</u><br>1plemented<br>MMNTH<br>MWD<br>MMIN<br><u>&lt;7:0&gt;:</u><br>1plemented<br>MDAY<br>MHR<br>MSEC<br><b>0&gt;:</b> Alarm Repeat                        | Alarm Value re<br>ecrements on<br>Counter Value                              | gisters when re<br>every read or w                   | ading ALRMVA                   |                    |                        |

|                    | Points to t<br>the ALRM<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>ALRMVAL<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>ARPT<7:              | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>&lt;15:8&gt;:</u><br>1plemented<br>MMNTH<br>MWD<br>MMIN<br><u>&lt;7:0&gt;:</u><br>1plemented<br>MDAY<br>MHR<br>MSEC<br><b>0&gt;:</b> Alarm Repeat                        | Alarm Value re<br>ecrements on<br>Counter Value                              | gisters when re<br>every read or w                   | ading ALRMVA                   |                    |                        |

|                    | Points to t<br>the ALRM<br>ALRMVAL<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>11 = Unin<br>10 = ALR<br>00 = ALR<br>00 = ALR<br>ARPT<7:(<br>1111111) | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>&lt;15:8&gt;:</u><br>1plemented<br>MMNTH<br>MWD<br>MMIN<br><u>&lt;7:0&gt;:</u><br>1plemented<br>MDAY<br>MHR<br>MSEC<br><b>0&gt;:</b> Alarm Repeat                        | Alarm Value re<br>ecrements on<br>Counter Value<br>eat 255 more t            | gisters when re<br>every read or w                   | ading ALRMVA                   |                    |                        |

|                    | Points to t<br>the ALRM<br>ALRMVAL<br>11 = Unin<br>10 = ALR<br>01 = ALR<br>00 = ALR<br>ALRMVAL<br>11 = Unin<br>10 = ALR<br>00 = ALR<br>ARPT<7:(<br>1111111)  | he corresponding <i>i</i><br>PTR<1:0> value d<br><u>&lt;15:8&gt;:</u><br>nplemented<br>MMNTH<br>MWD<br>MMIN<br><u>&lt;7:0&gt;:</u><br>nplemented<br>MDAY<br>MHR<br>MSEC<br><b>0&gt;:</b> Alarm Repeat<br>1 = Alarm will repe | Alarm Value re<br>ecrements on<br>Counter Value<br>eat 255 more to<br>repeat | gisters when re<br>every read or w<br>e bits<br>imes | ading ALRMVA<br>rite of ALRMVA | ALH until it reach | nes '00 <sup>7</sup> . |

#### DECISTED 24 2 ALADM CONFIGURATION DECISTED ...

Most instructions are a single word. Certain doubleword instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| TABLE 28-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS |

|-------------|-------------------------------------|

|-------------|-------------------------------------|

| #text<br>(text)<br>[text]<br>{}<br><n:m><br/>.b<br/>.d<br/>.S</n:m> | Means literal defined by "text"         Means "content of text"         Means "the location addressed by text"         Optional field or operation         Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select         Word mode selection (default) |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [text]<br>{}<br><n:m><br/>.b<br/>.d<br/>.S</n:m>                    | Means "the location addressed by text"         Optional field or operation         Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                               |

| {}<br><n:m><br/>.b<br/>.d<br/>.S</n:m>                              | Optional field or operation         Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                                                                              |

| <n:m><br/>.b<br/>.d<br/>.S</n:m>                                    | Register bit field         Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                                                                                                                  |

| .b<br>.d<br>.S                                                      | Byte mode selection         Double-Word mode selection         Shadow register select                                                                                                                                                                                                                             |

| .d<br>.S                                                            | Double-Word mode selection       Shadow register select                                                                                                                                                                                                                                                           |

| .S                                                                  | Shadow register select                                                                                                                                                                                                                                                                                            |

|                                                                     | · ·                                                                                                                                                                                                                                                                                                               |

|                                                                     | Word mode selection (default)                                                                                                                                                                                                                                                                                     |

| .W                                                                  |                                                                                                                                                                                                                                                                                                                   |

| Acc                                                                 | One of two accumulators {A, B}                                                                                                                                                                                                                                                                                    |

| AWB                                                                 | Accumulator write back destination address register $\in$ {W13, [W13]+ = 2}                                                                                                                                                                                                                                       |

| bit4                                                                | 4-bit bit selection field (used in word addressed instructions) ∈ {015}                                                                                                                                                                                                                                           |

| C, DC, N, OV, Z                                                     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                                                                                                                                                                                                                                              |

| Expr                                                                | Absolute address, label or expression (resolved by the linker)                                                                                                                                                                                                                                                    |

| f                                                                   | File register address ∈ {0x00000x1FFF}                                                                                                                                                                                                                                                                            |

| lit1                                                                | 1-bit unsigned literal ∈ {0,1}                                                                                                                                                                                                                                                                                    |

| lit4                                                                | 4-bit unsigned literal ∈ {015}                                                                                                                                                                                                                                                                                    |

| lit5                                                                | 5-bit unsigned literal ∈ {031}                                                                                                                                                                                                                                                                                    |

| lit8                                                                | 8-bit unsigned literal ∈ {0255}                                                                                                                                                                                                                                                                                   |

| lit10                                                               | 10-bit unsigned literal $\in~\{0255\}$ for Byte mode, {0:1023} for Word mode                                                                                                                                                                                                                                      |

| lit14                                                               | 14-bit unsigned literal ∈ {016384}                                                                                                                                                                                                                                                                                |

| lit16                                                               | 16-bit unsigned literal ∈ {065535}                                                                                                                                                                                                                                                                                |

| lit23                                                               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                                                                                                                                                                                                                                             |

| None                                                                | Field does not require an entry, can be blank                                                                                                                                                                                                                                                                     |

| OA, OB, SA, SB                                                      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate                                                                                                                                                                                                                                       |

| PC                                                                  | Program Counter                                                                                                                                                                                                                                                                                                   |

| Slit10                                                              | 10-bit signed literal $\in$ {-512511}                                                                                                                                                                                                                                                                             |