Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b; D/A 2x16b                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp802-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Pin Diagrams (Continued)

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) DS51749

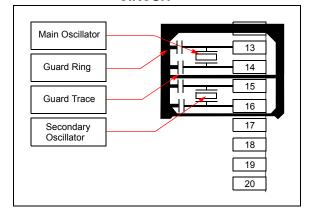

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3. Recommendations for crystals and ceramic resonators are provided in Table 2-1 and Table 2-2, respectively.

# FIGURE 2-3:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| Part<br>Number                               | Vendor   | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |  |  |

|----------------------------------------------|----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|--|--|

| ECS-40-20-4DN                                | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |  |  |

| ECS-80-18-4DN                                | ECS Inc. | 8 MHz  | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |  |  |

| ECS-100-18-4-DN                              | ECS Inc. | 10 MHz | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |  |  |

| ECS-200-20-4DN                               | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |  |  |

| ECS-40-20-5G3XDS-TR                          | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |  |  |

| ECS-80-20-5G3XDS-TR                          | ECS Inc. | 8 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |  |  |

| ECS-100-20-5G3XDS-TR                         | ECS Inc. | 10 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |  |  |

| ECS-200-20-5G3XDS-TR                         | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to 125°C           |  |  |

| NX3225SA 20MHZ AT-W                          | NDK      | 20 MHz | 8 pF         | 3.2 mm x 2.5 mm | ±50 ppm                | SM               | -40°C to 125°C           |  |  |

| Legend: TH = Through Hole SM = Surface Mount |          |        |              |                 |                        |                  |                          |  |  |

## TABLE 2-1: CRYSTAL RECOMMENDATIONS

## 3.6 CPU Control Registers

## REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0          | R-0                             | R/C-0                                | R/C-0             | R-0                    | R/C-0              | R -0              | R/W-0           |

|--------------|---------------------------------|--------------------------------------|-------------------|------------------------|--------------------|-------------------|-----------------|

| OA           | OB                              | SA <sup>(1)</sup>                    | SB <sup>(1)</sup> | OAB                    | SAB <sup>(4)</sup> | DA                | DC              |

| bit 15       |                                 |                                      |                   |                        |                    |                   | bit 8           |

|              | (2) (2)                         | (2)                                  |                   |                        |                    |                   |                 |

| R/W-0        |                                 | R/W-0 <sup>(3)</sup>                 | R-0               | R/W-0                  | R/W-0              | R/W-0             | R/W-0           |

|              | IPL<2:0> <sup>(2)</sup>         |                                      | RA                | N                      | OV                 | Z                 | С               |

| bit 7        |                                 |                                      |                   |                        |                    |                   | bit 0           |

| Legend:      |                                 |                                      |                   |                        |                    |                   |                 |

| C = Clear    | only bit                        | R = Readable                         | e bit             | U = Unimple            | mented bit, read   | l as '0'          |                 |

| S = Set o    | •                               | W = Writable                         | bit               | -n = Value at          |                    |                   |                 |

| '1' = Bit is | set                             | '0' = Bit is cle                     | ared              | x = Bit is unk         | nown               |                   |                 |

|              |                                 |                                      |                   |                        |                    |                   |                 |

| bit 15       | OA: Accumul                     | ator A Overflo                       | w Status bit      |                        |                    |                   |                 |

|              |                                 | ator A overflow                      |                   |                        |                    |                   |                 |

|              |                                 | ator A has not                       |                   |                        |                    |                   |                 |

| bit 14       |                                 | ator B Overflo<br>ator B overflow    |                   |                        |                    |                   |                 |

|              |                                 | ator B has not                       |                   |                        |                    |                   |                 |

| bit 13       | SA: Accumul                     | ator A Saturati                      | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                    |                   |                 |

|              |                                 |                                      |                   | en saturated at        | some time          |                   |                 |

|              |                                 | ator A is not sa                     |                   |                        |                    |                   |                 |

| bit 12       |                                 | ator B Saturati                      | -                 |                        |                    |                   |                 |

|              |                                 | ator B is satura<br>ator B is not sa |                   | en saturated at        | some time          |                   |                 |

| bit 11       | <b>0ab:</b> 0a    C             | B Combined A                         | Accumulator C     | verflow Status         | bit                |                   |                 |

|              |                                 | ators A or B ha<br>ccumulators A     |                   |                        |                    |                   |                 |

| bit 10       | <b>SAB:</b> SA    SI            | B Combined A                         | ccumulator (S     | ticky) Status bi       | t <sup>(4)</sup>   |                   |                 |

|              |                                 | ators A or B are                     |                   |                        | urated at some     | time in the pas   | t               |

| bit 9        | DA: DO Loop                     |                                      |                   |                        |                    |                   |                 |

|              | 1 = DO <b>loop ir</b>           |                                      |                   |                        |                    |                   |                 |

|              | 0 = DO loop n                   | ot in progress                       |                   |                        |                    |                   |                 |

| bit 8        | DC: MCU AL                      | U Half Carry/B                       | orrow bit         |                        |                    |                   |                 |

|              |                                 | ut from the 4th<br>sult occurred     | low-order bit (   | for byte-sized         | data) or 8th low-  | order bit (for wo | ord-sized data) |

|              | •                               | -out from the 4 he result occu       |                   | oit (for byte-siz      | ed data) or 8th    | low-order bit (1  | for word-sized  |

| Note 1:      | This bit can be rea             | d or cleared (r                      | not set).         |                        |                    |                   |                 |

| 2:           | The IPL<2:0> bits               |                                      |                   |                        |                    |                   |                 |

|              | Level. The value in IPL<3> = 1. | n parentheses                        | indicates the I   | PL if IPL<3> =         | 1. User interrup   | ots are disabled  | d when          |

| 3:           | The IPL<2:0> Stat               | us bits are rea                      | d only when th    | ne NSTDIS bit          | (INTCON1<15>       | )=1.              |                 |

| 4.           | This hit says has use           |                                      |                   | na this hit slos       |                    |                   |                 |

4: This bit can be read or cleared (not set). Clearing this bit clears SA and SB.

## 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

### 4.2.6 DMA RAM

Every dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 device contains up to 2 Kbytes of dual ported DMA RAM located at the end of Y data space, and is part of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

| Note: | DMA    | RAM     | can     | be    | used     | for | general  |

|-------|--------|---------|---------|-------|----------|-----|----------|

|       | purpo  | se data | a stora | age   | if the D | DMA | function |

|       | is not | require | ed in a | an ap | oplicati | on. |          |

## 4.3 Memory Resources

Many useful resources related to Memory Organization are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

## 4.3.1 KEY RESOURCES

- Section 2. "Program Memory" (DS70203)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 5.2 RTSP Operation

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 30-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

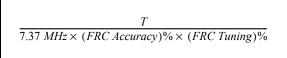

The programming time depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the formula in Equation 5-1 to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 30-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 \ ms$$

The maximum row write time is equal to Equation 5-3.

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

## 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY (Register 5-2) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

## 5.5 Flash Resources

Many useful resources related to Flash memory are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | product page using the link above, enter    |  |  |  |  |  |

|       | this URL in your browser:                   |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/       |  |  |  |  |  |

|       | Devices.aspx?dDocName=en532311              |  |  |  |  |  |

## 5.5.1 KEY RESOURCES

- Section 5. "Flash Programming" (DS70191)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

NOTES:

| U-0                | U-0                                                  | U-0                                                                    | R/W-1   | R/W-1                       | R/W-1            | R/W-1              | R/W-1 |  |

|--------------------|------------------------------------------------------|------------------------------------------------------------------------|---------|-----------------------------|------------------|--------------------|-------|--|

| —                  |                                                      | _                                                                      |         |                             | U1CTSR<4:0       | >                  |       |  |

| bit 15             |                                                      |                                                                        |         |                             |                  |                    | bit 8 |  |

|                    |                                                      |                                                                        | D 44/ 4 |                             |                  | D 44/4             |       |  |

| U-0                | U-0                                                  | U-0                                                                    | R/W-1   | R/W-1                       | R/W-1            | R/W-1              | R/W-1 |  |

| -:+ 7              | _                                                    | —                                                                      |         |                             | U1RXR<4:0>       | •                  | h:+ 0 |  |

| bit 7              |                                                      |                                                                        |         |                             |                  |                    | bit C |  |

| Legend:            |                                                      |                                                                        |         |                             |                  |                    |       |  |

| R = Readab         | le bit                                               | W = Writable                                                           | oit     | U = Unimplen                | nented bit, read | d as '0'           |       |  |

| -n = Value a       | t POR                                                | '1' = Bit is set                                                       |         | '0' = Bit is clea           | ared             | x = Bit is unknown |       |  |

| bit 15-13          | Unimpleme                                            | nted: Read as '                                                        | )'      |                             |                  |                    |       |  |

| bit 12-8           | -                                                    | 0>: Assign UAR                                                         |         | end $(\overline{11000})$ to | the correspo     | ndina RPn nin      |       |  |

|                    |                                                      | ut tied to Vss                                                         |         |                             |                  | ionig i u ii pili  |       |  |

|                    |                                                      | ut tied to RP25                                                        |         |                             |                  |                    |       |  |

|                    | •                                                    |                                                                        |         |                             |                  |                    |       |  |

|                    | •                                                    |                                                                        |         |                             |                  |                    |       |  |

|                    |                                                      |                                                                        |         |                             |                  |                    |       |  |

|                    | •                                                    |                                                                        |         |                             |                  |                    |       |  |

|                    |                                                      | ut tied to RP1<br>ut tied to RP0                                       |         |                             |                  |                    |       |  |

| oit 7-5            | 00000 <b>= Inp</b>                                   |                                                                        | )'      |                             |                  |                    |       |  |

|                    | 00000 = Inp<br>Unimpleme                             | ut tied to RP0                                                         |         | 1RX) to the cor             | responding RF    | n pin              |       |  |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(                                     |         | 1RX) to the cor             | responding RF    | n pin              |       |  |

|                    | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss |         | 1RX) to the cor             | responding RF    | 'n pin             |       |  |

| bit 7-5<br>bit 4-0 | 00000 = Inp<br>Unimpleme<br>U1RXR<4:0<br>11111 = Inp | ut tied to RP0<br>nted: Read as '(<br>>: Assign UART<br>ut tied to Vss |         | 1RX) to the cor             | responding RF    | 'n pin             |       |  |

## REGISTER 11-8: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

00001 = Input tied to RP1 00000 = Input tied to RP0

## REGISTER 11-17: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                               | U-0 | U-0              | R/W-0                                 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-----------------------------------|-----|------------------|---------------------------------------|-------|-----------|-------|-------|

| _                                 | _   | —                |                                       |       | RP1R<4:0> |       |       |

| bit 15                            |     | ·                |                                       |       |           |       | bit 8 |

|                                   |     |                  |                                       |       |           |       |       |

| U-0                               | U-0 | U-0              | R/W-0                                 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|                                   |     | —                |                                       |       | RP0R<4:0> | •     |       |

| bit 7                             |     |                  |                                       |       |           |       | bit 0 |

|                                   |     |                  |                                       |       |           |       |       |

| Legend:                           |     |                  |                                       |       |           |       |       |

| R = Readable bit W = Writable bit |     |                  | U = Unimplemented bit, read as '0'    |       |           |       |       |

| -n = Value at P                   | OR  | '1' = Bit is set | t '0' = Bit is cleared x = Bit is unk |       |           |       | nown  |

bit 12-8 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 11-2 for peripheral function numbers)

## REGISTER 11-18: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP3R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP2R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 11-2 for peripheral function numbers)

## REGISTER 11-21: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| -n = Value at P | POR                           | '1' = Bit is set | et '0' = Bit is cleared x = Bit is |                                    |           | x = Bit is unkr | iown  |  |

|-----------------|-------------------------------|------------------|------------------------------------|------------------------------------|-----------|-----------------|-------|--|

| R = Readable    | Readable bit W = Writable bit |                  |                                    | U = Unimplemented bit, read as '0' |           |                 |       |  |

| Legend:         |                               |                  |                                    |                                    |           |                 |       |  |

|                 |                               |                  |                                    |                                    |           |                 |       |  |

| bit 7           |                               |                  |                                    |                                    |           |                 | bit 0 |  |

| —               | _                             | —                |                                    |                                    | RP8R<4:0> |                 |       |  |

| U-0             | U-0                           | U-0              | R/W-0                              | R/W-0                              | R/W-0     | R/W-0           | R/W-0 |  |

|                 |                               |                  |                                    |                                    |           |                 |       |  |

| bit 15          |                               |                  | •                                  |                                    |           |                 | bit 8 |  |

| _               |                               | _                |                                    |                                    | RP9R<4:0> |                 |       |  |

| U-0             | U-0                           | U-0              | R/W-0                              | R/W-0                              | R/W-0     | R/W-0           | R/W-0 |  |

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 11-2 for peripheral function numbers)

## REGISTER 11-22: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP11R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP10R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 11-2 for peripheral function numbers)

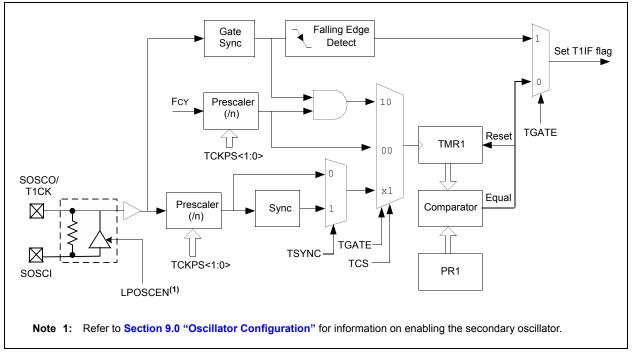

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source.

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

## TABLE 12-1: TIMER MODE SETTINGS

| Mode                 | TCS | TGATE | TSYNC |

|----------------------|-----|-------|-------|

| Timer                | 0   | 0     | Х     |

| Gated timer          | 0   | 1     | х     |

| Synchronous counter  | 1   | х     | 1     |

| Asynchronous counter | 1   | х     | 0     |

## FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

## REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                    |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                              |

|       | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.</li> <li>Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as $l^2C$ master)                                                                                                                                                        |

|       | 1 = Enables Receive mode for $l^2C$ . Hardware clear at end of eighth bit of master receive data byte<br>0 = Receive sequence not in progress                                                                            |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                        |

|       | 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence<br>0 = Stop condition not in progress                                                                                   |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                             |

|       | 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence                                                                                                     |

|       | 0 = Repeated Start condition not in progress                                                                                                                                                                             |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                              |

|       | <ul><li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li><li>0 = Start condition not in progress</li></ul>                                                         |

| REGISTER      | 19-15: CIDU                      | FPN14: ECA                                               |                  |                                         |               | REGISTER |       |  |

|---------------|----------------------------------|----------------------------------------------------------|------------------|-----------------------------------------|---------------|----------|-------|--|

| R/W-0         | R/W-0                            | R/W-0                                                    | R/W-0            | R/W-0                                   | R/W-0         | R/W-0    | R/W-0 |  |

|               | F15B                             | P<3:0>                                                   |                  | F14BP<3:0>                              |               |          |       |  |

| bit 15        |                                  |                                                          |                  |                                         |               |          | bit 8 |  |

| R/W-0         | R/W-0                            | R/W-0                                                    | R/W-0            | R/W-0                                   | R/W-0         | R/W-0    | R/W-0 |  |

| F13BP<3:0>    |                                  |                                                          |                  | F12BI                                   | ><3:0>        |          |       |  |

| bit 7         |                                  |                                                          |                  |                                         |               | bit 0    |       |  |

|               |                                  |                                                          |                  |                                         |               |          |       |  |

| Legend:       | d: C = Writable bit, but only '0 |                                                          |                  | D' can be written to clear the bit      |               |          |       |  |

| R = Readabl   | e bit                            | W = Writable                                             | bit              | U = Unimplemented bit, read as '0'      |               |          |       |  |

| -n = Value at | POR                              | '1' = Bit is set                                         | :                | '0' = Bit is cleared x = Bit is unknown |               |          |       |  |

| bit 15-12     | 1111 = Filte                     | RX Buffer ma<br>r hits received in<br>r hits received in | n RX FIFO buf    | fer                                     |               |          |       |  |

|               | 1110 <b>= Filte</b>              | r hits received in                                       | n RX Buffer 14   | ŀ                                       |               |          |       |  |

|               | •                                |                                                          |                  |                                         |               |          |       |  |

|               | •                                |                                                          |                  |                                         |               |          |       |  |

|               | 0001                             | r hits received in<br>r hits received in                 |                  |                                         |               |          |       |  |

| bit 11-8      | F14BP<3:0                        | : RX Buffer ma                                           | sk for Filter 14 | (same values                            | as bit 15-12) |          |       |  |

| bit 7-4       | F13BP<3:0                        | : RX Buffer ma                                           | sk for Filter 13 | (same values                            | as bit 15-12) |          |       |  |

|               |                                  |                                                          |                  |                                         |               |          |       |  |

## REGISTER 19-15: CiBUFPNT4: ECAN™ FILTER 12-15 BUFFER POINTER REGISTER

| bit 3-0 | <b>F12BP&lt;3:0&gt;:</b> RX Buffer mask for Filter 12 (same values as bit 15-12) |

|---------|----------------------------------------------------------------------------------|

| DIL 3-0 |                                                                                  |

| n (n = 0-15) |                         |                                           |                                                             |                                                                               |                                                                        |                                                                                      |

|--------------|-------------------------|-------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| R/W-x        | R/W-x                   | R/W-x                                     | R/W-x                                                       | R/W-x                                                                         | R/W-x                                                                  | R/W-x                                                                                |

| EID14        | EID13                   | EID12                                     | EID11                                                       | EID10                                                                         | EID9                                                                   | EID8                                                                                 |

|              |                         |                                           |                                                             |                                                                               |                                                                        | bit 8                                                                                |

|              |                         |                                           |                                                             |                                                                               |                                                                        |                                                                                      |

| R/W-x        | R/W-x                   | R/W-x                                     | R/W-x                                                       | R/W-x                                                                         | R/W-x                                                                  | R/W-x                                                                                |

| EID6         | EID5                    | EID4                                      | EID3                                                        | EID2                                                                          | EID1                                                                   | EID0                                                                                 |

|              |                         |                                           |                                                             |                                                                               |                                                                        | bit 0                                                                                |

|              |                         |                                           |                                                             |                                                                               |                                                                        |                                                                                      |

|              | R/W-x<br>EID14<br>R/W-x | R/W-x R/W-x<br>EID14 EID13<br>R/W-x R/W-x | R/W-x R/W-x R/W-x<br>EID14 EID13 EID12<br>R/W-x R/W-x R/W-x | R/W-x R/W-x R/W-x R/W-x<br>EID14 EID13 EID12 EID11<br>R/W-x R/W-x R/W-x R/W-x | R/W-xR/W-xR/W-xR/W-xEID14EID13EID12EID11EID10R/W-xR/W-xR/W-xR/W-xR/W-x | R/W-xR/W-xR/W-xR/W-xR/W-xEID14EID13EID12EID11EID10EID9R/W-xR/W-xR/W-xR/W-xR/W-xR/W-x |

| REGISTER 19-17: | CIRXFnEID: ECAN™ ACCEPTANCE FILTER EXTENDED IDENTIFIER REGISTER |

|-----------------|-----------------------------------------------------------------|

|                 | n (n = 0-15)                                                    |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                      |                    |  |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0'            |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-0

EID<15:0>: Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '0' to match filter

#### REGISTER 19-18: CiFMSKSEL1: ECAN™ FILTER 7-0 MASK SELECTION REGISTER

| R/W-0      | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0             |

|------------|--------|-------|--------|-------|--------|-------|-------------------|

| F7MSK<1:0> |        | F6MSł | <<1:0> | F5MS  | K<1:0> | F4MSł | <b>&lt;</b> <1:0> |

| bit 15     |        |       |        |       |        |       | bit 8             |

|            |        |       |        |       |        |       |                   |

| R/W-0      | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0             |

| F3MSI      | K<1:0> | F2MSł | <<1:0> | F1MS  | K<1:0> | F0MSł | <<1:0>            |

| bit 7      |        |       |        |       |        |       | bit 0             |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                                    |                    |  |  |

|-------------------|----------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | F7MSK<1:0>: Mask Source for Filter 7 bit<br>11 = No mask<br>10 = Acceptance Mask 2 registers contain mask<br>01 = Acceptance Mask 1 registers contain mask<br>00 = Acceptance Mask 0 registers contain mask |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-12 | <b>F6MSK&lt;1:0&gt;:</b> Mask Source for Filter 6 bit (same values as bit 15-14)                                                                                                                            |

| bit 11-10 | <b>F5MSK&lt;1:0&gt;:</b> Mask Source for Filter 5 bit (same values as bit 15-14)                                                                                                                            |

| bit 9-8   | F4MSK<1:0>: Mask Source for Filter 4 bit (same values as bit 15-14)                                                                                                                                         |

| bit 7-6   | F3MSK<1:0>: Mask Source for Filter 3 bit (same values as bit 15-14)                                                                                                                                         |

| bit 5-4   | F2MSK<1:0>: Mask Source for Filter 2 bit (same values as bit 15-14)                                                                                                                                         |

| bit 3-2   | F1MSK<1:0>: Mask Source for Filter 1 bit (same values as bit 15-14)                                                                                                                                         |

| bit 1-0   | F0MSK<1:0>: Mask Source for Filter 0 bit (same values as bit 15-14)                                                                                                                                         |

## BUFFER 19-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x                                                   | R/W-x | R/W-x            | R/W-x    | R/W-x                           | R/W-x | R/W-x           | R/W-x |

|---------------------------------------------------------|-------|------------------|----------|---------------------------------|-------|-----------------|-------|

|                                                         |       |                  | Ву       | rte 3                           |       |                 |       |

| bit 15                                                  |       |                  |          |                                 |       |                 | bit 8 |

|                                                         |       |                  |          |                                 |       |                 |       |

| R/W-x                                                   | R/W-x | R/W-x            | R/W-x    | R/W-x                           | R/W-x | R/W-x           | R/W-x |

|                                                         |       |                  | Ву       | rte 2                           |       |                 |       |

| bit 7                                                   |       |                  |          |                                 |       |                 | bit 0 |

| Legend:                                                 |       |                  |          |                                 |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit |       | nented bit, rea  | d as '0' |                                 |       |                 |       |

| -n = Value at P                                         | OR    | '1' = Bit is set |          | '0' = Bit is cleared x = Bit is |       | x = Bit is unkr | nown  |

bit 15-8 Byte 3<15:8>: ECAN™ Message Byte 3

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2

#### BUFFER 19-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x    | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------|-------|-------|-------|-------|-------|-------|-------|

| Byte 5   |       |       |       |       |       |       |       |

| bit 15 k |       |       |       |       |       | bit 8 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x             | R/W-x |

|-----------------|-------|------------------|-------|------------------------------------|-------|-------------------|-------|

|                 |       |                  | Ву    | te 4                               |       |                   |       |

| bit 7           |       |                  |       |                                    |       |                   | bit 0 |

| Legend:         |       |                  |       |                                    |       |                   |       |

| R = Readable b  | oit   | W = Writable b   | it    | U = Unimplemented bit, read as '0' |       |                   |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | red   | x = Bit is unknow | n     |

bit 15-8 Byte 5<15:8>: ECAN™ Message Byte 5

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4

## 22.0 AUDIO DIGITAL-TO-ANALOG CONVERTER (DAC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Audio Digital-to-Analog Converter (DAC) module is a 16-bit Delta-Sigma signal converter designed for audio applications. It has two output channels, left and right to support stereo applications. Each DAC output channel provides three voltage outputs, positive DAC output, negative DAC output, and the midpoint voltage output for the dsPIC33FJ64GP804 and dsPIC33FJ128GP804 The devices. dsPIC33FJ128GP802 dsPIC33FJ64GP802 and devices provide positive DAC output and negative DAC output voltages.

## 22.1 Key Features

- 16-bit resolution (14-bit accuracy)

- Second-Order Digital Delta-Sigma Modulator

- 256 X Over-Sampling Ratio

- 128-Tap FIR Current-Steering Analog Reconstruction Filter

- 100 ksps Maximum Sampling Rate

- User controllable Sample Clock

- Input Frequency 45 kHz max

- · Differential Analog Outputs

- Signal-To-Noise: 90 dB

- 4-deep input Buffer

- 16-bit Processor I/O, and DMA interfaces

## 22.2 DAC Module Operation

The functional block diagram of the Audio DAC module is shown in Figure 22-1. The Audio DAC module provides a 4-deep data input FIFO buffer for each output channel. If the DMA module and/or the processor cannot provide output data in a timely manner, and the FIFO becomes empty, the DAC accepts data from the DAC Default Data register (DACDFLT). This safety feature is useful for industrial control applications where the DAC output controls an important processor or machinery. The DACDFLT register should be initialized with a "safe" output value. Often the safe output value is either the midpoint value (0x8000) or a zero value (0x0000).

The digital interpolator up-samples the input signals, where the over-sampling ratio is 256x which creates data points between the user supplied data points. The interpolator also includes processing by digital filters to provide "noise shaping" to move the converter noise above 20 kHz (upper limit of the pass band). The output of the interpolator drives the Sigma-Delta modulator. The serial data bit stream from the Sigma-Delta modulator is processed by the reconstruction filter. The differential outputs of the reconstruction filter are amplified by Op Amps to provide the required peak-to-peak voltage swing.

**Note:** The DAC module is designed specifically for audio applications and is not recommended for control type applications.

## 22.3 DAC Output Format

The DAC output data stream can be in a two's complement signed number format or as an unsigned number format.

The Audio DAC module features the ability to accept the 16-bit input data in a two's complement signed number format or as an unsigned number format. The data formatting is controlled by the Data Format Control bit (FORM<8>) in the DAC1CON register. The supported formats are:

- 1 = Signed (two's complement)

- 0 = Unsigned

If the FORM bit is configured for "Unsigned data" then the user input data yields the following behavior:

- 0xFFFF = most positive output voltage

- 0x8000 = mid point output voltage

- 0x7FFF = a value just below the midpoint

- 0x0000 = minimum output voltage

If the FORM bit is configured for "signed data" then the user input data yields the following behavior:

- 0x7FFF = most positive output voltage

- 0x0000 = mid point output voltage

- 0xFFFF = value just below the midpoint

- 0x8000 = minimum output voltage

The Audio DAC provides an analog output proportional to the digital input value. The maximum 100,000 samples per second (100 ksps) update rate provides good quality audio reproduction.

© 2007-2012 Microchip Technology Inc.

# REGISTER 24-6: RTCVAL (WHEN RTCPTR<1:0> = 01): WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x     | R/W-x |

|--------|-----|-----|-----|-----|-------|-----------|-------|

| —      | —   |     |     | —   |       | WDAY<2:0> |       |

| bit 15 |     |     |     |     |       |           | bit 8 |

| U-0   | U-0 | R/W-x      | R/W-x | R/W-x      | R/W-x | R/W-x | R/W-x |

|-------|-----|------------|-------|------------|-------|-------|-------|

| _     | —   | HRTEN<1:0> |       | HRONE<3:0> |       |       |       |

| bit 7 |     |            |       |            |       |       | bit 0 |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6      |

| bit 7-6   | Unimplemented: Read as '0'                                                                |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2 |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9 |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## **REGISTER 24-7: RTCVAL (WHEN RTCPTR<1:0> =** 00): **MINUTES AND SECONDS VALUE REGISTER**

| U-0           | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|---------------|-------|-------|-------|-------|-------|---------|-------|

| — MINTEN<2:0> |       |       |       |       | MINON | IE<3:0> |       |

| bit 15        |       |       |       |       |       |         | bit 8 |

|               |       |       |       |       |       |         |       |

| U-0           | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|               |       |       |       |       |       |         |       |

| —     | SECTEN<2:0> | SECONE<3:0> |

|-------|-------------|-------------|

| bit 7 |             | bit 0       |

|       |             |             |

| Legend:           |                                                     |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      | , read as '0'      |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                   |  |

|-----------|----------------------------------------------------------------------------------------------|--|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit; contains a value from 0 to 5 |  |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit; contains a value from 0 to 9 |  |

| bit 7     | Unimplemented: Read as '0'                                                                   |  |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit; contains a value from 0 to 5 |  |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit; contains a value from 0 to 9 |  |

© 2007-2012 Microchip Technology Inc.

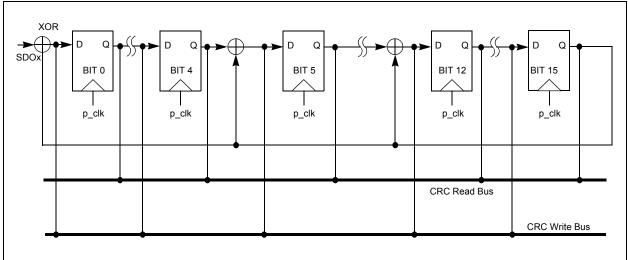

## FIGURE 25-2: CRC GENERATOR RECONFIGURED FOR $x^{16} + x^{12} + x^5 + 1$

## 25.2 User Interface

## 25.2.1 DATA INTERFACE

To start serial shifting, a '1' must be written to the CRCGO bit.

The module incorporates a FIFO that is 8 deep when PLEN (PLEN<3:0>) > 7, and 16 deep, otherwise. The data for which the CRC is to be calculated must first be written into the FIFO. The smallest data element that can be written into the FIFO is one byte. For example, if PLEN = 5, then the size of the data is PLEN + 1 = 6. The data must be written as follows:

```

data[5:0] = crc_input[5:0]

data[7:6] = `bxx

```

Once data is written into the CRCWDAT MSb (as defined by PLEN), the value of VWORD (VWORD<4:0>) increments by one. The serial shifter starts shifting data into the CRC engine when CRCGO = 1 and VWORD > 0. When the MSb is shifted out, VWORD decrements by one. The serial shifter continues shifting until the VWORD reaches 0. Therefore, for a given value of PLEN, it will take (PLEN + 1) \* VWORD number of clock cycles to complete the CRC calculations.

When VWORD reaches 8 (or 16), the CRCFUL bit will be set. When VWORD reaches 0, the CRCMPT bit will be set.

To continually feed data into the CRC engine, the recommended mode of operation is to initially "prime" the FIFO with a sufficient number of words so no interrupt is generated before the next word can be written. Once that is done, start the CRC by setting the CRCGO bit to '1'. From that point onward, the VWORD<4:0> bits should be polled. If they read less than 8 or 16, another word can be written into the FIFO. To empty words already written into a FIFO, the CRCGO bit must be set to '1' and the CRC shifter allowed to run until the CRCMPT bit is set.

Also, to get the correct CRC reading, it will be necessary to wait for the CRCMPT bit to go high before reading the CRCWDAT register.

If a word is written when the CRCFUL bit is set, the VWORD Pointer will roll over to 0. The hardware will then behave as if the FIFO is empty. However, the condition to generate an interrupt will not be met; therefore, no interrupt will be generated (See Section 25.2.2 "Interrupt Operation").

At least one instruction cycle must pass after a write to CRCWDAT before a read of the VWORD bits is done.

#### 25.2.2 INTERRUPT OPERATION

When the VWORD<4:0> bits make a transition from a value of '1' to '0', an interrupt will be generated.

## 25.3 Operation in Power-Saving Modes

#### 25.3.1 SLEEP MODE

If Sleep mode is entered while the module is operating, the module will be suspended in its current state until clock execution resumes.

#### 25.3.2 IDLE MODE

To continue full module operation in Idle mode, the CSIDL bit must be cleared prior to entry into the mode.

If CSIDL = 1, the module will behave the same way as it does in Sleep mode; pending interrupt events will be passed on, even though the module clocks are not available.

## REGISTER 26-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER (CONTINUED)

| bit 2 | <b>BEP:</b> Byte Enable Polarity bit <ol> <li>Byte enable active-high (PMBE)</li> <li>Byte enable active-low (PMBE)</li> </ol> |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                                |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00, 01, 10):                                                                  |

|       | 1 = Write strobe active-high (PMWR)                                                                                            |

|       | $0 = $ Write strobe active-low ( $\overline{PMWR}$ )                                                                           |

|       | For Master mode 1 (PMMODE<9:8> = 11):                                                                                          |

|       | 1 = Enable strobe active-high (PMENB)                                                                                          |

|       | 0 = Enable strobe active-low (PMENB)                                                                                           |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                                 |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00, 01, 10):                                                                  |

|       | 1 = Read strobe active-high (PMRD)                                                                                             |

|       | 0 = Read strobe active-low (PMRD)                                                                                              |

|       | For Master mode 1 (PMMODE<9:8> = 11):                                                                                          |

|       | 1 = Read/write strobe active-high (PMRD/PMWR)                                                                                  |

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** These bits have no effect when their corresponding pins are used as address lines.

## TABLE 27-5: CODE FLASH SECURITY SEGMENT SIZES FOR 128 KB DEVICES

| CONFIG BITS           | BSS<2:0> = x11 0K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BSS<2:0> = x10 1K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BSS<2:0> = x01 4K                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BSS<2:0> = x00 8K                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|