Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x10b/12b; D/A 2x16b                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp802t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.4 Special MCU Features

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/ X04, and dsPIC33FJ128GPX02/X04 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

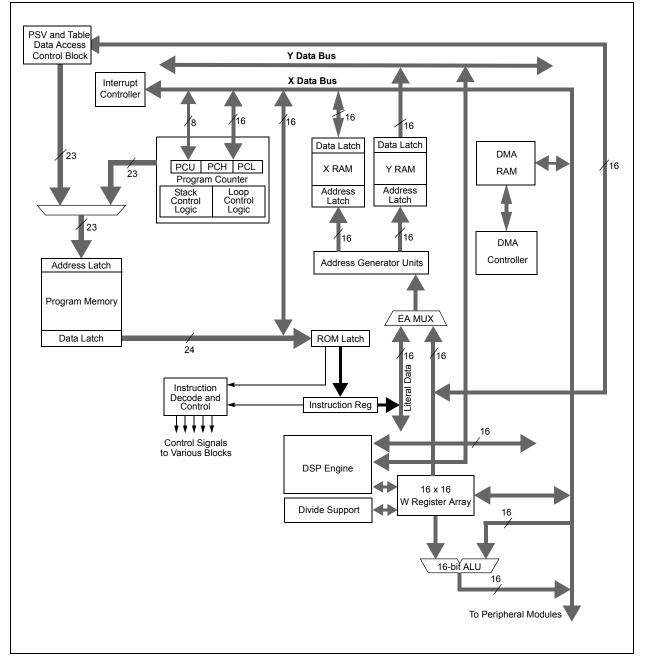

#### FIGURE 3-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 CPU CORE BLOCK DIAGRAM

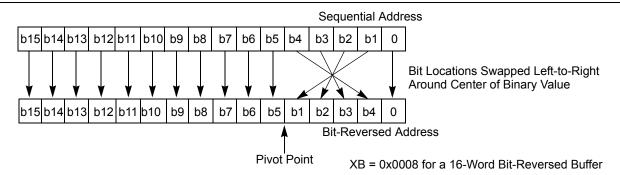

### TABLE 4-38: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |

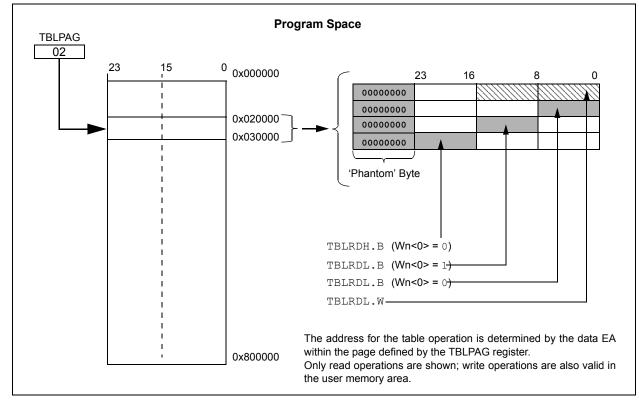

#### 4.8.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>), is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

### FIGURE 7-1: dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/ X04 INTERRUPT VECTOR TABLE

|                                   |                                      | -               |                                                        |

|-----------------------------------|--------------------------------------|-----------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction             | 0x000000        |                                                        |

|                                   | Reset – GOTO Address                 | 0x000002        |                                                        |

|                                   | Reserved                             | 0x000004        |                                                        |

|                                   | Oscillator Fail Trap Vector          |                 |                                                        |

|                                   | Address Error Trap Vector            | _               |                                                        |

|                                   | Stack Error Trap Vector              |                 |                                                        |

|                                   | Math Error Trap Vector               |                 |                                                        |

|                                   | DMA Error Trap Vector                |                 |                                                        |

|                                   | Reserved                             |                 |                                                        |

|                                   | Reserved                             |                 |                                                        |

|                                   | Interrupt Vector 0                   | 0x000014        |                                                        |

|                                   | Interrupt Vector 1                   |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | Interrupt Vector 52                  | 0x00007C        | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|                                   | Interrupt Vector 53                  | 0x00007E        |                                                        |

| ity                               | Interrupt Vector 54                  | 0x000080        |                                                        |

| Decreasing Natural Order Priority | ~                                    | 7               |                                                        |

| Ē.                                | ~                                    |                 |                                                        |

| de                                | ~                                    |                 |                                                        |

| ō                                 | Interrupt Vector 116                 | 0x0000FC        |                                                        |

| a                                 | Interrupt Vector 117                 | 0x0000FE        |                                                        |

| atu                               | Reserved                             | 0x000100        |                                                        |

| Ž                                 | Reserved                             | 0x000102        |                                                        |

| ing                               | Reserved                             |                 |                                                        |

| eas                               | Oscillator Fail Trap Vector          |                 |                                                        |

| SC                                | Address Error Trap Vector            |                 |                                                        |

| ĕ                                 | Stack Error Trap Vector              |                 |                                                        |

|                                   | Math Error Trap Vector               |                 |                                                        |

|                                   | DMA Error Trap Vector                |                 |                                                        |

|                                   | Reserved                             |                 | 7                                                      |

|                                   | Reserved                             |                 |                                                        |

|                                   | Interrupt Vector 0                   | 0x000114        |                                                        |

|                                   | Interrupt Vector 1                   |                 |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    | 1               |                                                        |

|                                   | ~                                    |                 | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                  | 0x00017C        |                                                        |

|                                   | Interrupt Vector 53                  | 0x00017E        |                                                        |

|                                   | Interrupt Vector 54                  | 0x000180        |                                                        |

|                                   | ~                                    |                 |                                                        |

|                                   | ~                                    | 7               |                                                        |

|                                   | ~                                    | ]               |                                                        |

|                                   | Interrupt Vector 116                 | ]               |                                                        |

| Ļ                                 | Interrupt Vector 117                 | 0x0001FE        |                                                        |

| V                                 | Start of Code                        | 0x000200        |                                                        |

|                                   |                                      | _               |                                                        |

|                                   |                                      |                 |                                                        |

|                                   |                                      |                 |                                                        |

| Note 1: Se                        | ee Table 7-1 for the list of impleme | ented interrupt | vectors.                                               |

|                                   |                                      |                 |                                                        |

|                                   |                                      |                 |                                                        |

| REGISTER      |                                                                              | : INTERRUPT F                                                 |               | CONTROL R        | EGISTER 8      |                  |       |  |  |  |  |

|---------------|------------------------------------------------------------------------------|---------------------------------------------------------------|---------------|------------------|----------------|------------------|-------|--|--|--|--|

| U-0           | R/W-1                                                                        | R/W-0                                                         | R/W-0         | U-0              | R/W-1          | R/W-0            | R/W-0 |  |  |  |  |

| —             |                                                                              | C1IP<2:0> <sup>(1)</sup>                                      |               |                  |                | C1RXIP<2:0>(1)   |       |  |  |  |  |

| bit 15        |                                                                              |                                                               |               |                  |                |                  | bi    |  |  |  |  |

| U-0           | R/W-1                                                                        | R/W-0                                                         | R/W-0         | U-0              | R/W-1          | R/W-0            | R/W-0 |  |  |  |  |

|               |                                                                              | SPI2IP<2:0>                                                   |               | _                |                | SPI2EIP<2:0>     |       |  |  |  |  |

| bit 7         |                                                                              |                                                               |               |                  |                |                  | bi    |  |  |  |  |

| Legend:       |                                                                              |                                                               |               |                  |                |                  |       |  |  |  |  |

| R = Readabl   | e bit                                                                        | W = Writable b                                                | it            | U = Unimpler     | mented bit, re | ad as '0'        |       |  |  |  |  |

| -n = Value at | POR                                                                          | '1' = Bit is set                                              |               | '0' = Bit is cle |                | x = Bit is unkno | own   |  |  |  |  |

|               |                                                                              |                                                               |               |                  |                |                  |       |  |  |  |  |

| bit 15        | Unimpleme                                                                    | ented: Read as '0                                             | 3             |                  |                |                  |       |  |  |  |  |

| bit 14-12     | C1IP<2:0>:                                                                   | C1IP<2:0>: ECAN1 Event Interrupt Priority bits <sup>(1)</sup> |               |                  |                |                  |       |  |  |  |  |

|               | 111 = Interr                                                                 | 111 = Interrupt is priority 7 (highest priority interrupt)    |               |                  |                |                  |       |  |  |  |  |

|               | •                                                                            |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | •                                                                            |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | 001 = Interrupt is priority 1                                                |                                                               |               |                  |                |                  |       |  |  |  |  |

|               |                                                                              | rupt source is disa                                           | bled          |                  |                |                  |       |  |  |  |  |

| bit 11        | Unimpleme                                                                    | ented: Read as '0                                             | 3             |                  |                |                  |       |  |  |  |  |

| bit 10-8      | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits <sup>(1)</sup> |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | 111 = Interr                                                                 | 111 = Interrupt is priority 7 (highest priority interrupt)    |               |                  |                |                  |       |  |  |  |  |

|               | •                                                                            | •                                                             |               |                  |                |                  |       |  |  |  |  |

|               | •                                                                            |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | 001 = Interr                                                                 | •<br>001 = Interrupt is priority 1                            |               |                  |                |                  |       |  |  |  |  |

|               |                                                                              | upt source is disa                                            | bled          |                  |                |                  |       |  |  |  |  |

| bit 7         | Unimpleme                                                                    | ented: Read as '0                                             | ,             |                  |                |                  |       |  |  |  |  |

| bit 6-4       | SPI2IP<2:0                                                                   | >: SPI2 Event Inte                                            | errupt Priori | ty bits          |                |                  |       |  |  |  |  |

|               | 111 = Interr                                                                 | 111 = Interrupt is priority 7 (highest priority interrupt)    |               |                  |                |                  |       |  |  |  |  |

|               | •                                                                            |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | •                                                                            |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | 001 = Interr                                                                 | •<br>001 = Interrupt is priority 1                            |               |                  |                |                  |       |  |  |  |  |

|               |                                                                              | upt source is disa                                            | bled          |                  |                |                  |       |  |  |  |  |

| bit 3         | Unimpleme                                                                    | Unimplemented: Read as '0'                                    |               |                  |                |                  |       |  |  |  |  |

| bit 2-0       | SPI2EIP<2:                                                                   | 0>: SPI2 Error Int                                            | errupt Prior  | ity bits         |                |                  |       |  |  |  |  |

|               | 111 = Interr                                                                 | rupt is priority 7 (h                                         | ighest priori | ty interrupt)    |                |                  |       |  |  |  |  |

|               | •                                                                            |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | •                                                                            |                                                               |               |                  |                |                  |       |  |  |  |  |

|               | 001 = Interr                                                                 | rupt is priority 1                                            |               |                  |                |                  |       |  |  |  |  |

|               |                                                                              | upt source is disa                                            | blod          |                  |                |                  |       |  |  |  |  |

#### -.... -----

NOTES:

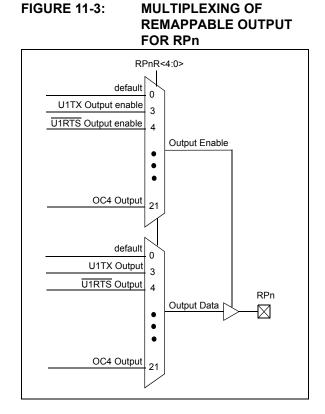

#### 11.6.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 11-17 through Register 11-29). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

#### Function RPnR<4:0> **Output Name** NULL RPn tied to default port pin 00000 C10UT RPn tied to Comparator1 Output 00001 C2OUT RPn tied to Comparator2 Output 00010 U1TX 00011 RPn tied to UART1 Transmit **U1RTS** 00100 RPn tied to UART1 Ready To Send U2TX RPn tied to UART2 Transmit 00101 U2RTS 00110 RPn tied to UART2 Ready To Send SDO1 RPn tied to SPI1 Data Output 00111 SCK1 01000 RPn tied to SPI1 Clock Output SS1 01001 RPn tied to SPI1 Slave Select Output SDO2 RPn tied to SPI2 Data Output 01010 RPn tied to SPI2 Clock Output SCK2 01011 SS2 RPn tied to SPI2 Slave Select Output 01100 CSDO 01101 RPn tied to DCI Serial Data Output CSCK RPn tied to DCI Serial Clock Output 01110 COFS RPn tied to DCI Frame Sync Output 01111 C1TX 10000 RPn tied to ECAN1 Transmit OC1 RPn tied to Output Compare 1 10010 OC2 RPn tied to Output Compare 2 10011 OC3 RPn tied to Output Compare 3 10100

RPn tied to Output Compare 4

### TABLE 11-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

10101

OC4

### REGISTER 11-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0                                | U-0 | U-0              | U-0                                     | U-0                                | U-0        | U-0   | U-0   |

|------------------------------------|-----|------------------|-----------------------------------------|------------------------------------|------------|-------|-------|

| _                                  | —   | _                | _                                       | —                                  | —          | _     | —     |

| bit 15                             |     |                  |                                         |                                    |            |       | bit 8 |

|                                    |     |                  |                                         |                                    |            |       |       |

| U-0                                | U-0 | U-0              | R/W-1                                   | R/W-1                              | R/W-1      | R/W-1 | R/W-1 |

| —                                  | —   | —                |                                         |                                    | OCFAR<4:0> |       |       |

| bit 7                              |     |                  |                                         |                                    |            |       | bit 0 |

|                                    |     |                  |                                         |                                    |            |       |       |

| Legend:                            |     |                  |                                         |                                    |            |       |       |

| R = Readable                       | bit | W = Writable bit |                                         | U = Unimplemented bit, read as '0' |            |       |       |

| -n = Value at POR '1' = Bit is set |     |                  | '0' = Bit is cleared x = Bit is unknown |                                    |            |       |       |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 OCFAR<4:0>: Assign Output Compare A (OCFA) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

### 15.2 Output Compare Resources

Many useful resources related to Output Compare are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/                                                                          |

|       | Devices.aspx?dDocName=en532311                                                                                 |

### 15.2.1 KEY RESOURCES

- Section 13. "Output Compare" (DS70209)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- **Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- **2:** Do not set both Primary and Secondary prescalers to the value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

### 18.3 UART Control Registers

### REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0    | R/W-0 |  |

|-----------------------|-----|-------|---------------------|-------|-----|----------|-------|--|

| UARTEN <sup>(1)</sup> | —   | USIDL | IREN <sup>(2)</sup> | RTSMD | —   | UEN<1:0> |       |  |

| bit 15 bit            |     |       |                     |       |     |          |       |  |

| R/W-0 HC | R/W-0  | R/W-0 HC | R/W-0  | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|----------|--------|----------|--------|-------|------------|-------|-------|

| WAKE     | LPBACK | ABAUD    | URXINV | BRGH  | PDSEL<1:0> |       | STSEL |

| bit 7    |        |          |        |       |            |       | bit 0 |

| Legend:           | HC = Hardware cleared |                                    |                    |  |

|-------------------|-----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15  | <ul> <li>UARTEN: UARTx Enable bit<sup>(1)</sup></li> <li>1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN&lt;1:0&gt;</li> <li>0 = UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption minimal</li> </ul>                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 13  | USIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                           |

| bit 12  | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = IrDA<sup>®</sup> encoder and decoder enabled</li> <li>0 = IrDA<sup>®</sup> encoder and decoder disabled</li> </ul>                                                                                                                                                                                                                                                                 |

| bit 11  | <b>RTSMD:</b> Mode Selection for UxRTS Pin bit                                                                                                                                                                                                                                                                                                                                                  |

|         | 1 = <u>UxRTS</u> pin in Simplex mode<br>0 = UxRTS pin in Flow Control mode                                                                                                                                                                                                                                                                                                                      |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                      |

| bit 9-8 | UEN<1:0>: UARTx Enable bits                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>11 = UxTX, UxRX and BCLK pins are enabled and used; UxCTS pin controlled by port latches</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> <li>01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches</li> <li>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by port latches</li> </ul> |

| bit 7   | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = UARTx continues to sample the UxRX pin; interrupt generated on falling edge; bit cleared<br/>in hardware on following rising edge</li> <li>0 = No wake-up enabled</li> </ul>                                                                                                                                                                                                       |

| bit 6   | LPBACK: UARTx Loopback Mode Select bit                                                                                                                                                                                                                                                                                                                                                          |

|         | 1 = Enable Loopback mode<br>0 = Loopback mode is disabled                                                                                                                                                                                                                                                                                                                                       |

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul>                                                                                                                                                           |

| Note 1: | Refer to <b>Section 17. "UART"</b> (DS70188) in the <i>"dsPIC33F/PIC24H Family Reference Manual"</i> for information on enabling the UART module for receive or transmit operation.                                                                                                                                                                                                             |

|         |                                                                                                                                                                                                                                                                                                                                                                                                 |

2: This feature is only available for the 16x BRG mode (BRGH = 0).

| R/W-0                             | R/W-0   | R/W-0            | U-0                                | R/W-0 HC         | R/W-0                | R-0                | R-1         |  |

|-----------------------------------|---------|------------------|------------------------------------|------------------|----------------------|--------------------|-------------|--|

| UTXISEL1                          | UTXINV  | UTXISEL0         | _                                  | UTXBRK           | UTXEN <sup>(1)</sup> | UTXBF              | TRMT        |  |

| bit 15                            |         |                  |                                    | -                |                      |                    | bit 8       |  |

|                                   |         |                  |                                    |                  |                      |                    |             |  |

| R/W-0                             | R/W-0   | R/W-0            | R-1                                | R-0              | R-0                  | R/C-0              | R-0         |  |

| URXISE                            | EL<1:0> | ADDEN            | RIDLE                              | PERR FERR        |                      | OERR               | URXDA       |  |

| bit 7                             |         |                  |                                    | -                |                      | -                  | bit 0       |  |

|                                   |         |                  |                                    |                  |                      |                    |             |  |

| Legend:                           |         | HC = Hardwar     | re cleared                         |                  |                      | C = Clea           | ar only bit |  |

| R = Readable bit W = Writable bit |         |                  | U = Unimplemented bit, read as '0' |                  |                      |                    |             |  |

| -n = Value at POR                 |         | '1' = Bit is set |                                    | '0' = Bit is cle | ared                 | x = Bit is unknown |             |  |

|                                   |         |                  |                                    |                  |                      |                    |             |  |

| bit 15,13 | UTXISEL<1:0>: Transmission Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>11 = Reserved; do not use</li> <li>10 = Interrupt when a character is transferred to the Transmit Shift register, and as a result, the</li> </ul>                                                                                                                                                                                                                                                |

|           | transmit buffer becomes empty<br>01 = Interrupt when the last character is shifted out of the Transmit Shift register; all transmit<br>operations are completed                                                                                                                                                                                                                                           |

|           | <ul> <li>00 = Interrupt when a character is transferred to the Transmit Shift register (this implies there is<br/>at least one character open in the transmit buffer)</li> </ul>                                                                                                                                                                                                                          |

| bit 14    | UTXINV: Transmit Polarity Inversion bit                                                                                                                                                                                                                                                                                                                                                                   |

|           | <u>If IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1 = UxTX Idle state is '0'                                                                                                                                                                                                                                                                                                                                                                                |

|           | 0 = UxTX Idle state is '1'                                                                                                                                                                                                                                                                                                                                                                                |

|           | $\frac{\text{If IREN = 1:}}{1 + 1 + 1}$                                                                                                                                                                                                                                                                                                                                                                   |

|           | 1 = IrDA <sup>®</sup> encoded UxTX Idle state is '1'<br>0 = IrDA <sup>®</sup> encoded UxTX Idle state is '0'                                                                                                                                                                                                                                                                                              |

| bit 12    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 11    | UTXBRK: Transmit Break bit                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                                                                                                                                                                                                      |

|           | 0 = Sync Break transmission disabled or completed                                                                                                                                                                                                                                                                                                                                                         |

| bit 10    | UTXEN: Transmit Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                 |

|           | 1 = Transmit enabled, UxTX pin controlled by UARTx                                                                                                                                                                                                                                                                                                                                                        |

|           | <ul> <li>Transmit disabled, any pending transmission is aborted and buffer is reset. UxTX pin controlled<br/>by port</li> </ul>                                                                                                                                                                                                                                                                           |

| bit 9     | UTXBF: Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                        |

|           | 1 = Transmit buffer is full                                                                                                                                                                                                                                                                                                                                                                               |

|           | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                                                                                                                                                                               |

| bit 8     | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> </ul>                                                                                                                                                                                    |

| bit 7-6   | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>11 = Interrupt is set on UxRSR transfer making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on UxRSR transfer making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters.</li> </ul> |

**Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER      | 19-15: CIDU                                 | FPN14: ECA                                               |                  |                                         |                                    | REGISTER |       |

|---------------|---------------------------------------------|----------------------------------------------------------|------------------|-----------------------------------------|------------------------------------|----------|-------|

| R/W-0         | R/W-0                                       | R/W-0                                                    | R/W-0            | R/W-0                                   | R/W-0                              | R/W-0    | R/W-0 |

|               | F15B                                        | P<3:0>                                                   |                  |                                         | F14BI                              | ><3:0>   |       |

| bit 15        |                                             |                                                          |                  |                                         |                                    | bit 8    |       |

| R/W-0         | R/W-0                                       | R/W-0                                                    | R/W-0            | R/W-0                                   | R/W-0                              | R/W-0    | R/W-0 |

| F13BP<3:0>    |                                             |                                                          |                  | F12BI                                   | ><3:0>                             |          |       |

| bit 7         |                                             |                                                          |                  |                                         |                                    |          | bit 0 |

|               |                                             |                                                          |                  |                                         |                                    |          |       |

| Legend:       | end: C = Writable bit, but only '0'         |                                                          |                  | ' can be writter                        | to clear the bit                   | t        |       |

| R = Readabl   | e bit                                       | W = Writable                                             | W = Writable bit |                                         | U = Unimplemented bit, read as '0' |          |       |

| -n = Value at | POR                                         | '1' = Bit is set                                         | :                | '0' = Bit is cleared x = Bit is unknown |                                    |          | nown  |

| bit 15-12     | 1111 = Filte                                | RX Buffer ma<br>r hits received in<br>r hits received in | n RX FIFO buf    | fer                                     |                                    |          |       |

|               | 1110 = Filter hits received in RX Buffer 14 |                                                          |                  |                                         |                                    |          |       |

|               | •                                           |                                                          |                  |                                         |                                    |          |       |

|               | •                                           |                                                          |                  |                                         |                                    |          |       |

|               | 0001                                        | r hits received in<br>r hits received in                 |                  |                                         |                                    |          |       |

| bit 11-8      | F14BP<3:0                                   | : RX Buffer ma                                           | sk for Filter 14 | (same values                            | as bit 15-12)                      |          |       |

| bit 7-4       | F13BP<3:0                                   | : RX Buffer ma                                           | sk for Filter 13 | (same values                            | as bit 15-12)                      |          |       |

|               |                                             |                                                          |                  |                                         |                                    |          |       |

### REGISTER 19-15: CiBUFPNT4: ECAN™ FILTER 12-15 BUFFER POINTER REGISTER

| bit 3-0 | <b>F12BP&lt;3:0&gt;:</b> RX Buffer mask for Filter 12 (same values as bit 15-12) |

|---------|----------------------------------------------------------------------------------|

| DIL 3-0 |                                                                                  |

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| REGISTER 19-24: CIRXOVF1: ECAN IIII RECEIVE BUFFER OVERFLOW REGISTER 1 |         |         |                   |                  |                    |        |        |

|------------------------------------------------------------------------|---------|---------|-------------------|------------------|--------------------|--------|--------|

| R/C-0                                                                  | R/C-0   | R/C-0   | R/C-0             | R/C-0            | R/C-0              | R/C-0  | R/C-0  |

| RXOVF15                                                                | RXOVF14 | RXOVF13 | RXOVF12           | RXOVF11          | RXOVF10            | RXOVF9 | RXOVF8 |

| bit 15                                                                 |         |         |                   |                  |                    |        | bit 8  |

|                                                                        |         |         |                   |                  |                    |        |        |

| R/C-0                                                                  | R/C-0   | R/C-0   | R/C-0             | R/C-0            | R/C-0              | R/C-0  | R/C-0  |

| RXOVF7                                                                 | RXOVF6  | RXOVF5  | RXOVF4            | RXOVF3           | RXOVF2             | RXOVF1 | RXOVF0 |

| bit 7                                                                  | bit 7   |         |                   |                  |                    |        | bit 0  |

|                                                                        |         |         |                   |                  |                    |        |        |

| Legend: C = Writable bit, but only                                     |         |         | oit, but only '0' | can be writter   | n to clear the bit |        |        |

| R = Readable bit W = Writable bit                                      |         | bit     | U = Unimpler      | nented bit, read | as '0'             |        |        |

'0' = Bit is cleared

x = Bit is unknown

### DECIOTED 40.04. CODVOVE4. FOANIM DECENCE DUFFED OVEDELOW DECIOTED 4

bit 15-0

-n = Value at POR

RXOVF<15:0>: Receive Buffer n Overflow bits

'1' = Bit is set

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition

### REGISTER 19-25: CIRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-0

RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition

### REGISTER 21-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 3 | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                                                                                                                                                                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <pre>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0' 1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or Samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01) 0 = Samples multiple channels individually in sequence</pre>                                                                                                                                        |

| bit 2 | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                  |

|       | <ul> <li>1 = Sampling begins immediately after last conversion. SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                |

| bit 1 | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                      |

|       | <ul> <li>1 = ADC sample/hold amplifiers are sampling</li> <li>0 = ADC sample/hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software can write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>       |

| bit 0 | DONE: ADC Conversion Status bit                                                                                                                                                                                                                                                                                                                                                                                  |

|       | <ul> <li>1 = ADC conversion cycle is completed.</li> <li>0 = ADC conversion not started or in progress</li> <li>Automatically set by hardware when ADC conversion is complete. Software can write '0' to clear</li> <li>DONE status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at start of a new conversion.</li> </ul> |

## dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

# REGISTER 24-6: RTCVAL (WHEN RTCPTR<1:0> = 01): WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x     | R/W-x |

|--------|-----|-----|-----|-----|-------|-----------|-------|

| —      | —   |     |     | —   |       | WDAY<2:0> |       |

| bit 15 |     |     |     |     |       |           | bit 8 |

| U-0   | U-0 | R/W-x      | R/W-x | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|------------|-------|-------|-------|--------|-------|

| _     | —   | HRTEN<1:0> |       |       | HRON  | E<3:0> |       |

| bit 7 |     |            |       |       |       |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                |

|-----------|-------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; contains a value from 0 to 6      |

| bit 7-6   | Unimplemented: Read as '0'                                                                |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; contains a value from 0 to 2 |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; contains a value from 0 to 9 |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### **REGISTER 24-7: RTCVAL (WHEN RTCPTR<1:0> =** 00): **MINUTES AND SECONDS VALUE REGISTER**

| U-0    | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|--------|-------------|-------|-------|-------|-------|---------|-------|

| —      | MINTEN<2:0> |       |       |       | MINON | IE<3:0> |       |

| bit 15 |             |       |       |       |       |         | bit 8 |

|        |             |       |       |       |       |         |       |

| U-0    | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|        |             |       |       |       |       |         |       |

| —     | SECTEN<2:0> | SECONE<3:0> |

|-------|-------------|-------------|

| bit 7 |             | bit 0       |

|       |             |             |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit; contains a value from 0 to 5 |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit; contains a value from 0 to 9 |

| bit 7     | Unimplemented: Read as '0'                                                                   |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit; contains a value from 0 to 5 |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit; contains a value from 0 to 9 |

© 2007-2012 Microchip Technology Inc.

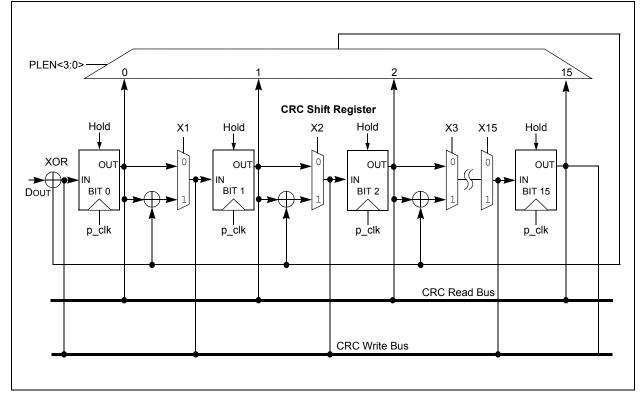

### 25.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304. dsPIC33FJ64GPX02/X04. and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet. refer to Section 36. "Programmable Cyclic Redundancy Check (CRC)" (DS70298) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable polynomial CRC equation

- Interrupt output

- Data FIFO

### FIGURE 25-1: CRC SHIFTER DETAILS

### 25.1 Overview

The module implements a software configurable CRC generator. The terms of the polynomial and its length can be programmed using the CRCXOR bits (X<15:1>) and the CRCCON bits (PLEN<3:0>), respectively.

### EQUATION 25-1: CRC EQUATION

$$x^{16} + x^{12} + x^5 + 1$$

To program this polynomial into the CRC generator, the CRC register bits should be set as shown in Table 25-1.

| TABLE 25-1: | EXAMPLE CRC SETUP |

|-------------|-------------------|

|-------------|-------------------|

| Bit Name  | Bit Value      |  |  |  |  |

|-----------|----------------|--|--|--|--|

| PLEN<3:0> | 1111           |  |  |  |  |

| X<15:1>   | 00010000010000 |  |  |  |  |

For the value of X<15:1>, the 12th bit and the 5th bit are set to '1', as required by the CRC equation. The 0th bit required by the CRC equation is always XORed. For a 16-bit polynomial, the 16th bit is also always assumed to be XORed; therefore, the X<15:1> bits do not have the 0th bit or the 16th bit.

The topology of a standard CRC generator is shown in Figure 25-2.

© 2007-2012 Microchip Technology Inc.

### 31.0 HIGH TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0 "Electrical Characteristics"** for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter DC10 in **Section 30.0 "Electrical Characteristics**" is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 high temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

### Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(4)</sup>                                   | 40°C to +150°C       |

|---------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                             | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                              | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(5)</sup>   | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $V_{DD} < 3.0V^{(5)}$   | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $V_{DD} \ge 3.0V^{(5)}$ | 0.3V to 5.6V         |

| Maximum current out of Vss pin                                                  |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                     | 60 mA                |

| Maximum junction temperature                                                    | +155°C               |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                   |                      |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                   | 4 mA                 |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                   | 8 mA                 |

| Maximum current sunk by all ports combined                                      | 70 mA                |

| Maximum current sourced by all ports combined <sup>(2)</sup>                    | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- **3:** Unlike devices at 125°C and below, the specifications in this section also apply to the CLKOUT, VREF+, VREF-, SCLx, SDAx, PGCx, and PGDx pins.

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Refer to the "Pin Diagrams" section for 5V tolerant pins.

### dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

| DC CHARACTERISTICS |        |                               | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+150°C for High Temperature |     |     |       |                                                                  |