Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b/12b; D/A 2x16b                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp804-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-37: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | for the source and destination EA.                                                    |  |  |  |  |  |  |  |

|       | However, the 4-bit Wb (Register Offset)                                               |  |  |  |  |  |  |  |

|       | field is shared by both source and                                                    |  |  |  |  |  |  |  |

|       | destination (but typically only used by                                               |  |  |  |  |  |  |  |

|       | one).                                                                                 |  |  |  |  |  |  |  |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the data pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register                                 | Indirect  | with    | Register  | Offset |  |  |  |  |  |

|-------|------------------------------------------|-----------|---------|-----------|--------|--|--|--|--|--|

|       | Addressing mode is available only for W9 |           |         |           |        |  |  |  |  |  |

|       | (in X spac                               | ce) and W | /11 (in | Y space). |        |  |  |  |  |  |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 6.0 RESETS

- Note 1: This data sheet summarizes the features dsPIC33FJ32GP302/304. of the dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

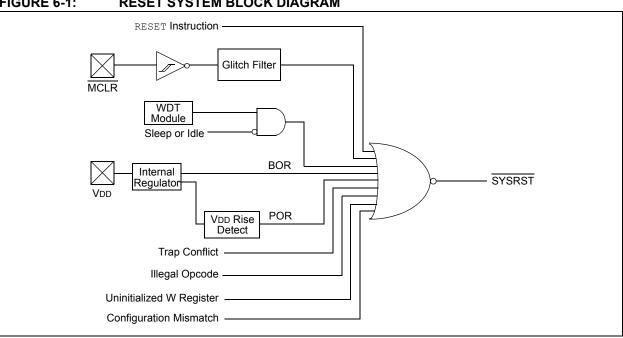

The Reset module combines all reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

The status bits in the RCON register Note: should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1

BOR: Brown-out Reset Flag bit

1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

bit 0

POR: Power-on Reset Flag bit

1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

- bit 3 CF: Clock Fail Detect bit (read/clear by application)

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2 Unimplemented: Read as '0'

- bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

- 1 = Enable secondary oscillator

- 0 = Disable secondary oscillator

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 39. "Oscillator (Part III)"** (DS70216) in the *"dsPIC33F/PIC24H Family Reference Manual"* (available from the Microchip website) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

| U-0           | U-0                          | U-0                                                | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |

|---------------|------------------------------|----------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|

| _             |                              | —                                                  |               |                  | SCK2R<4:0       | >               |       |  |  |

| bit 15        |                              |                                                    |               |                  |                 |                 | bit 8 |  |  |

| U-0           | U-0                          | U-0                                                | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |

| _             |                              | _                                                  | SDI2R<4:0>    |                  |                 |                 |       |  |  |

| bit 7         |                              |                                                    |               |                  |                 |                 | bit C |  |  |

|               |                              |                                                    |               |                  |                 |                 |       |  |  |

| Legend:       |                              |                                                    |               |                  |                 |                 |       |  |  |

| R = Readabl   | le bit                       | W = Writable I                                     | oit           | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |

| -n = Value at | t POR                        | '1' = Bit is set                                   |               | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |

|               | •                            | ut tied to RP25                                    |               |                  |                 |                 |       |  |  |

|               | 00001 = Inpu<br>00000 = Inpu |                                                    |               |                  |                 |                 |       |  |  |

| bit 7-5       | Unimplemen                   | ited: Read as '                                    | )'            |                  |                 |                 |       |  |  |

| bit 4-0       | 11111 = Inpu<br>11001 = Inpu | Assign SPI2 D<br>ut tied to Vss<br>ut tied to RP25 | ata Input (SD | I2) to the corre | esponding RPr   | ו pin           |       |  |  |

|               | •<br>•                       |                                                    |               |                  |                 |                 |       |  |  |

|               | 00001 = Inpu<br>00000 = Inpu |                                                    |               |                  |                 |                 |       |  |  |

# 15.3 Output Compare Control Register

# REGISTER 15-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2, 3 OR 4)

| U-0          | U-0                                                                                                                                  | R/W-0                                   | U-0           | U-0              | U-0             | U-0             | U-0   |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|--|

| —            | —                                                                                                                                    | OCSIDL                                  | —             | —                | —               | —               |       |  |  |  |

| bit 15       |                                                                                                                                      |                                         |               |                  |                 |                 | bit 8 |  |  |  |

|              |                                                                                                                                      |                                         |               |                  |                 |                 |       |  |  |  |

| U-0          | U-0                                                                                                                                  | U-0                                     | R-0 HC        | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|              | —                                                                                                                                    | OCM<2:0>                                |               |                  |                 |                 |       |  |  |  |

| bit 7        |                                                                                                                                      |                                         |               |                  |                 |                 | bit C |  |  |  |

| Legend:      |                                                                                                                                      | HC = Cleared ir                         | n Hardware    | HS = Set in H    | lardware        |                 |       |  |  |  |

| R = Readab   | le bit                                                                                                                               | W = Writable bi                         | t             | U = Unimpler     | nented bit, rea | id as '0'       |       |  |  |  |

| -n = Value a | t POR                                                                                                                                | '1' = Bit is set                        |               | '0' = Bit is cle | ared            | x = Bit is unkı | known |  |  |  |

|              |                                                                                                                                      |                                         |               |                  |                 |                 |       |  |  |  |

| bit 15-14    | Unimplemen                                                                                                                           | nted: Read as '0'                       | 1             |                  |                 |                 |       |  |  |  |

| bit 13       | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                                                 |                                         |               |                  |                 |                 |       |  |  |  |

|              | <ul> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul>  |                                         |               |                  |                 |                 |       |  |  |  |

|              | •                                                                                                                                    | -                                       | -             | in CPU Idle mo   | ode             |                 |       |  |  |  |

| bit 12-5     | -                                                                                                                                    | nted: Read as '0'                       |               |                  |                 |                 |       |  |  |  |

| bit 4        | OCFLT: PWM Fault Condition Status bit                                                                                                |                                         |               |                  |                 |                 |       |  |  |  |

|              | <ul> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred</li> </ul> |                                         |               |                  |                 |                 |       |  |  |  |

|              | (This bit is only used when $OCM<2:0> = 111.$ )                                                                                      |                                         |               |                  |                 |                 |       |  |  |  |

| bit 3        |                                                                                                                                      | OCTSEL: Output Compare Timer Select bit |               |                  |                 |                 |       |  |  |  |

|              | 1 = Timer3 is the clock source for Compare x                                                                                         |                                         |               |                  |                 |                 |       |  |  |  |

|              | 0 = Timer2 is the clock source for Compare x                                                                                         |                                         |               |                  |                 |                 |       |  |  |  |

| bit 2-0      | OCM<2:0>: Output Compare Mode Select bits                                                                                            |                                         |               |                  |                 |                 |       |  |  |  |

|              | 111 = PWM mode on OCx, Fault pin enabled                                                                                             |                                         |               |                  |                 |                 |       |  |  |  |

|              | 110 = PWM mode on OCx, Fault pin disabled<br>101 = Initialize OCx pin low, generate continuous output pulses on OCx pin              |                                         |               |                  |                 |                 |       |  |  |  |

|              |                                                                                                                                      | ze OCx pin low, g                       |               |                  |                 | JIII            |       |  |  |  |

|              |                                                                                                                                      | are event toggles                       |               | e calbar bares ( |                 |                 |       |  |  |  |

|              |                                                                                                                                      | ze OCx pin high,                        |               |                  |                 |                 |       |  |  |  |

|              | 001 = Initializ                                                                                                                      | ze OCx pin low, c                       | compare event | forces OCy nir   | n hiah          |                 |       |  |  |  |

|              |                                                                                                                                      | t compare chann                         |               |                  | ringii          |                 |       |  |  |  |

| R/W-0        | R/W-0        | R/W-0                                | U-0             | U-0              | U-0              | U-0              | U-0   |  |  |  |  |

|--------------|--------------|--------------------------------------|-----------------|------------------|------------------|------------------|-------|--|--|--|--|

| FRMEN        | SPIFSD       | FRMPOL                               | —               | —                | —                | —                | _     |  |  |  |  |

| bit 15       |              |                                      |                 |                  |                  |                  | bit 8 |  |  |  |  |

|              |              |                                      |                 |                  |                  |                  |       |  |  |  |  |

| U-0          | U-0          | U-0                                  | U-0             | U-0              | U-0              | R/W-0            | U-0   |  |  |  |  |

| —            |              |                                      | —               | —                | —                | FRMDLY           | —     |  |  |  |  |

| bit 7        |              |                                      |                 |                  |                  |                  | bit C |  |  |  |  |

| Legend:      |              |                                      |                 |                  |                  |                  |       |  |  |  |  |

| R = Readab   | lo hit       | W = Writable                         | hit             | II – Unimploy    | mented bit, read | d as '0'         |       |  |  |  |  |

|              |              |                                      |                 | •                |                  |                  |       |  |  |  |  |

| -n = Value a | TPOR         | '1' = Bit is set                     |                 | '0' = Bit is cle | ared             | x = Bit is unkno | own   |  |  |  |  |

| bit 15       | FRMEN: Fra   | imed SPIx Supp                       | ort bit         |                  |                  |                  |       |  |  |  |  |

|              |              | SPIx support en                      |                 | oin used as fram | ne sync pulse ir | nput/output)     |       |  |  |  |  |

|              | 0 = Framed   | SPIx support dis                     | sabled          |                  |                  |                  |       |  |  |  |  |

| bit 14       | SPIFSD: Fra  | ame Sync Pulse                       | Direction Co    | ntrol bit        |                  |                  |       |  |  |  |  |

|              | •            | 1 = Frame sync pulse input (slave)   |                 |                  |                  |                  |       |  |  |  |  |

|              | 0 = Frame sy | 0 = Frame sync pulse output (master) |                 |                  |                  |                  |       |  |  |  |  |

| bit 13       | FRMPOL: Fi   | rame Sync Puls                       | e Polarity bit  |                  |                  |                  |       |  |  |  |  |

|              |              | ync pulse is acti                    |                 |                  |                  |                  |       |  |  |  |  |

|              | 0 = Frame sy | ync pulse is acti                    | ve-low          |                  |                  |                  |       |  |  |  |  |

| bit 12-2     | Unimpleme    | nted: Read as '                      | 0'              |                  |                  |                  |       |  |  |  |  |

| bit 1        | FRMDLY: Fr   | ame Sync Pulse                       | e Edge Selec    | t bit            |                  |                  |       |  |  |  |  |

|              | 1 = Frame sy | ync pulse coinci                     | des with first  | bit clock        |                  |                  |       |  |  |  |  |

|              | 0 = Frame sy | ync pulse prece                      | des first bit c | lock             |                  |                  |       |  |  |  |  |

| hit O        |              | ntad. Daad as (                      | o'              |                  |                  |                  |       |  |  |  |  |

## REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

bit 0 **Unimplemented:** Read as '0' This bit must not be set to '1' by the user application.

# 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit  $(I^2C)$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation.

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly.

### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, refer to the "*dsPIC33F/PIC24H Family Reference Manual*". Please see the Microchip website (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual chapters.

| R/W-xR/W-xR/W-xR/W-xR/W-xSEG2PHTSSAMSEG1PH<2:0>PRSEG<2:0>bit 7bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0          | R/W-x         | U-0             | U-0          | U-0              | R/W-x           | R/W-x               | R/W-x |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-----------------|--------------|------------------|-----------------|---------------------|-------|--|--|--|--|

| R/W-x       R/W-x <th< td=""><td></td><td>WAKFIL</td><td>_</td><td>_</td><td></td><td></td><td>SEG2PH&lt;2:0&gt;</td><td></td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | WAKFIL        | _               | _            |                  |                 | SEG2PH<2:0>         |       |  |  |  |  |

| SEG2PHTS       SAM       SEG1PH<2:0>       PRSEG<2:0>         bit 7       bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       WaKFIL: Select CAN bus Line Filter for Wake-up bit       1 = Use CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         bit 13-11       Unimplemented: Read as '0'       00 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus Line bit         1 = Length is 1 x To       000 = Length is 1 x To         0 = CaptH       SEG2PH<2:0>: Phase Segment 1 bits         1 = Length is 1 x To       000 = Length is 1 x To         0 = Length is 1 x To       000 = Length is 8 x To         0 = Length is 8 x To       .         0 = Length is 8 x To       .         0 = Length i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 15       |               |                 |              |                  |                 |                     | bit   |  |  |  |  |

| SEG2PHTS       SAM       SEG1PH<2:0>       PRSEG<2:0>         bit 7       bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       WaKFIL: Select CAN bus Line Filter for Wake-up bit       1 = Use CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         bit 13-11       Unimplemented: Read as '0'       00 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus line filter for wake-up         0 = CAN bus line filter for wake-up       0 = CAN bus Line bit         1 = Length is 1 x To       000 = Length is 1 x To         0 = CaptH       SEG2PH<2:0>: Phase Segment 1 bits         1 = Length is 1 x To       000 = Length is 1 x To         0 = Length is 1 x To       000 = Length is 8 x To         0 = Length is 8 x To       .         0 = Length is 8 x To       .         0 = Length i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |               |                 |              |                  |                 |                     |       |  |  |  |  |

| bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       bit 14       WAKFIL: Select CAN bus Line filter for Wake-up bit       1 = Use CAN bus line filter for wake-up       0 = CAN bus line filter is not used for wake-up         0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up         0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up         0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up         0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter for Wake-up       0 = CAN bus line is sample for the CAN bus line bit         1 = Freely programmable       0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater         bit 6       SAM: Sample of the CAN bus Line bit       1 = Bus line is sampled once at the sample point         0 = Bus line is sampled once at the sample point       0 = Bus line is 8 x TQ         0 = 0       0 = Length is 1 x TQ       0 = 0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |               | R/W-x           |              |                  | R/W-x           |                     | R/W-x |  |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 Unimplemented: Read as '0'<br>bit 14 WAKFIL: Select CAN bus Line Filter for Wake-up bit<br>1 = Use CAN bus line filter for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>bit 13-11 Unimplemented: Read as '0'<br>bit 10-8 SEG2PH<2:0>: Phase Segment 2 bits<br>111 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 0 read the sample point<br>0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater<br>bit 6 SAM: Sample of the CAN bus Line bit<br>1 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled three times at the sample | SEG2PHT      | S SAM         |                 | SEG1PH<2:0   | >                |                 | PRSEG<2:0>          |       |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       ''       Bit is unknown         0 = CAN bus line filter for wake-up       0 = CAN bus line filter is not used for wake-up       ''         0 = CAN bus line filter is not used for wake-up       ''       ''         bit 13-11       Unimplemented: Read as '0'       ''         SEG2PH<2:0>: Phase Segment 2 bits       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       ''         000 = Length is 1 x TQ       ''       '''     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 7        |               |                 |              |                  |                 |                     | bit   |  |  |  |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       Unimplemented: Read as '0'       ''         bit 14       WAKFIL: Select CAN bus Line Filter for Wake-up bit       1 = Use CAN bus line filter is not used for wake-up         0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up         0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up         0 = CAN bus line filter is not used for wake-up       0 = CAN bus line filter is not used for wake-up         bit 13-11       Unimplemented: Read as '0'         SEG2PH-2:0>: Phase Segment 2 bits       111 = Length is 1 x TQ         000 = Length is 1 x TQ          000 = Length is 1 x TQ          000 = Length is is sampled three times at the sample point          000 = Length is 1 x TQ          bit 5-3       SEG1PH<2:0>: Phase Segment 1 bits         111 = Length is 8 x TQ                                          <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Legend:      |               |                 |              |                  |                 |                     |       |  |  |  |  |

| bit 15 Unimplemented: Read as '0'<br>bit 14 WAKFIL: Select CAN bus Line Filter for Wake-up bit<br>1 = Use CAN bus line filter for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>bit 13-11 Unimplemented: Read as '0'<br>bit 10-8 SEG2PH<2:0>: Phase Segment 2 bits<br>111 = Length is 8 x To<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R = Readab   | le bit        | W = Writable    | e bit        | U = Unimple      | mented bit, re  | ad as '0'           |       |  |  |  |  |

| bit 14 WAKFIL: Select CAN bus Line Filter for Wake-up bit<br>1 = Use CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>111 Unimplemented: Read as '0'<br>SEG2PH2:0>: Phase Segment 2 bits<br>111 = Length is 8 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>1 = Feely programmable<br>0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater<br>bit 6 SAM: Sample of the CAN bus Line bit<br>1 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>1 = Length is 8 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -n = Value a | t POR         | '1' = Bit is se | t            | '0' = Bit is cle | eared           | x = Bit is unkno    | own   |  |  |  |  |

| bit 14 WAKFIL: Select CAN bus Line Filter for Wake-up bit<br>1 = Use CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>0 = CAN bus line filter is not used for wake-up<br>111 Unimplemented: Read as '0'<br>SEG2PH2:0>: Phase Segment 2 bits<br>111 = Length is 8 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>1 = Feely programmable<br>0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater<br>bit 6 SAM: Sample of the CAN bus Line bit<br>1 = Bus line is sampled three times at the sample point<br>0 = Bus line is sampled once at the sample point<br>0 = Bus line is sampled once at the sample point<br>1 = Length is 8 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ<br>000 = Length is 1 x TQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | hit 15       | Unimplome     | atadı Dood oo   | · ^ '        |                  |                 |                     |       |  |  |  |  |

| <pre>1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up 0 = CAN bus line filter is not used for wake-up 0 = CAN bus line filter is not used for wake-up 0 = CAN bus line filter is not used for wake-up 0 = CAN bus line filter is not used for wake-up 0 = CAN bus line filter is not used for wake-up 0 = CAN bus line filter is not used for wake-up 0 = CAN bus line is 8 x TQ 0 = Length is 1 x TQ 0 = Length is 1 x TQ 0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Maximum of SEG1PH bits or lnformation Processing Time (IPT), whichever is greater 0 = Bus line is sampled of the CAN bus Line bit 1 = Bus line is sampled once at the sample point 0 = Bus line is sampled once at the sample point 0 = Length is 8 x TQ 0 = Length is 1 x TQ 0 = Length is 1 x TQ 0 = Length is 8 x</pre>                                                                  |              | -             |                 |              | laka wa hit      |                 |                     |       |  |  |  |  |

| <ul> <li>0 = CAN bus line filter is not used for wake-up</li> <li>bit 13-11 Unimplemented: Read as '0'</li> <li>SEG2PH-2:0&gt;: Phase Segment 2 bits <ul> <li>111 = Length is 8 x TQ</li> <li>.</li> <li></li></ul></li></ul>                                                 | DIC 14       |               |                 |              | vake-up bit      |                 |                     |       |  |  |  |  |

| bit 13-11 Unimplemented: Read as '0'<br>bit 10-8 SEG2PH<2:0>: Phase Segment 2 bits<br>111 = Length is 8 x TQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |               |                 |              | a_un             |                 |                     |       |  |  |  |  |

| bit 10-8 SEG2PH<2:0>: Phase Segment 2 bits<br>111 = Length is 8 x TQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | hit 13_11    |               |                 |              | c-up             |                 |                     |       |  |  |  |  |

| <pre>111 = Length is 8 x Tq 111 = Length is 8 x Tq 000 = Length is 1 x Tq bit 7 SEG2PHTS: Phase Segment 2 Time Select bit 1 = Freely programmable 0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater bit 6 SAM: Sample of the CAN bus Line bit 1 = Bus line is sampled three times at the sample point 0 = Bus line is sampled once at the sample point 0 = Bus line is sampled once at the sample point 0 = Bus line is sampled once at the sample point 0 = Bus line is 8 x Tq bit 5-3 SEG1PH&lt;2:0&gt;: Phase Segment 1 bits 111 = Length is 1 x Tq PRSEG&lt;2:0&gt;: Propagation Time Segment bits 111 = Length is 8 x Tq </pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |               |                 |              |                  |                 |                     |       |  |  |  |  |

| <ul> <li>bit 7</li> <li>SEG2PHTS: Phase Segment 2 Time Select bit <ol> <li>Freely programmable</li> <li>Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater</li> </ol> </li> <li>bit 6</li> <li>SAM: Sample of the CAN bus Line bit <ol> <li>Bus line is sampled three times at the sample point</li> <li>Bus line is sampled once at the sample point</li> <li>Bus line is sampled once at the sample point</li> </ol> </li> <li>bit 5-3</li> <li>SEG1PH&lt;2:0&gt;: Phase Segment 1 bits <ol> <li>Length is 1 x TQ</li> </ol> </li> <li>bit 2-0</li> <li>PRSEG&lt;2:0&gt;: Propagation Time Segment bits <ol> <li>Length is 8 x TQ</li> <li>Length is 8 x TQ</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |               |                 |              |                  |                 |                     |       |  |  |  |  |

| bit 7       SEG2PHTS: Phase Segment 2 Time Select bit         1 = Freely programmable       0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater         bit 6       SAM: Sample of the CAN bus Line bit         1 = Bus line is sampled three times at the sample point       0 = Bus line is sampled once at the sample point         0 = Bus line is sampled once at the sample point       0 = Bus line is sampled once at the sample point         bit 5-3       SEG1PH<2:0>: Phase Segment 1 bits         111 = Length is 8 x TQ       .         000 = Length is 1 x TQ       .         bit 2-0       PRSEG<2:0>: Propagation Time Segment bits         111 = Length is 8 x TQ       .         .       .         .       .         .       .         .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | •             |                 |              |                  |                 |                     |       |  |  |  |  |

| bit 7       SEG2PHTS: Phase Segment 2 Time Select bit         1 = Freely programmable       0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater         bit 6       SAM: Sample of the CAN bus Line bit         1 = Bus line is sampled three times at the sample point       0 = Bus line is sampled once at the sample point         0 = Bus line is sampled once at the sample point       0 = Bus line is sampled once at the sample point         bit 5-3       SEG1PH<2:0>: Phase Segment 1 bits         111 = Length is 8 x TQ       .         000 = Length is 1 x TQ       .         bit 2-0       PRSEG<2:0>: Propagation Time Segment bits         111 = Length is 8 x TQ       .         .       .         .       .         .       .         .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | •             |                 |              |                  |                 |                     |       |  |  |  |  |

| bit 7       SEG2PHTS: Phase Segment 2 Time Select bit         1 = Freely programmable       0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater         bit 6       SAM: Sample of the CAN bus Line bit         1 = Bus line is sampled three times at the sample point       0 = Bus line is sampled once at the sample point         0 = Bus line is sampled once at the sample point       0 = Bus line is sampled once at the sample point         bit 5-3       SEG1PH<2:0>: Phase Segment 1 bits         111 = Length is 8 x TQ       .         000 = Length is 1 x TQ       .         bit 2-0       PRSEG<2:0>: Propagation Time Segment bits         111 = Length is 8 x TQ       .         .       .         .       .         .       .         .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | •             | •               |              |                  |                 |                     |       |  |  |  |  |

| bit 7       SEG2PHTS: Phase Segment 2 Time Select bit         1 = Freely programmable       0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater         bit 6       SAM: Sample of the CAN bus Line bit         1 = Bus line is sampled three times at the sample point       0 = Bus line is sampled once at the sample point         0 = Bus line is sampled once at the sample point       0 = Bus line is sampled once at the sample point         bit 5-3       SEG1PH<2:0>: Phase Segment 1 bits         111 = Length is 8 x TQ       .         000 = Length is 1 x TQ       .         bit 2-0       PRSEG<2:0>: Propagation Time Segment bits         111 = Length is 8 x TQ       .         .       .         .       .         .       .         .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | 000 = 1  enat | h is 1 x To     |              |                  |                 |                     |       |  |  |  |  |