Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

|                            |                                                                                 |

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I2S, POR, PWM, WDT                            |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b/12b; D/A 2x16b                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp804-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

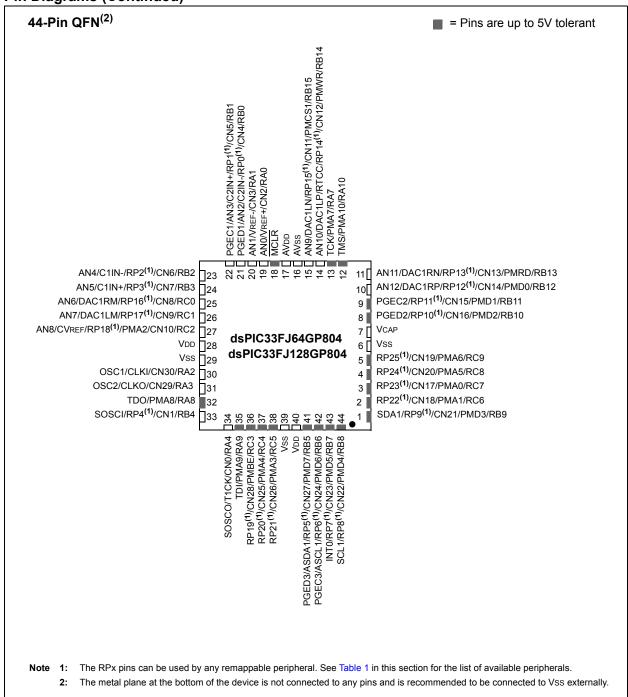

## Pin Diagrams (Continued)

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the "dsPIC33F/PIC24H Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ64GP804 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

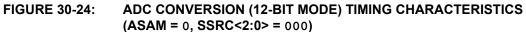

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

- Section 30. "I/O Ports with Peripheral Pin Select (PPS)" (DS70190)

- Section 32. "Interrupts (Part III)" (DS70214)

- Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211)

- Section 34. "Comparator" (DS70212)

- Section 35. "Parallel Master Port (PMP)" (DS70299)

- Section 36. "Programmable Cyclic Redundancy Check (CRC)" (DS70298)

- Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301)

- Section 38. "Direct Memory Access (DMA) (Part III)" (DS70215)

- Section 39. "Oscillator (Part III)" (DS70216)

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB® ICD 3 or MPLAB REAL ICE $^{\text{TM}}$ .

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- "Using MPLAB® ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB® ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB® REAL ICE™" (poster) DS51749

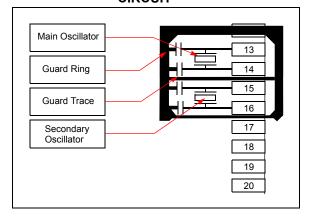

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins. not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3. Recommendations for crystals and ceramic resonators are provided in Table 2-1 and Table 2-2, respectively.

FIGURE 2-3: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

TABLE 2-1: CRYSTAL RECOMMENDATIONS

| Part<br>Number       | Vendor   | Freq.  | Load<br>Cap. | Package<br>Case | Frequency<br>Tolerance | Mounting<br>Type | Operating<br>Temperature |

|----------------------|----------|--------|--------------|-----------------|------------------------|------------------|--------------------------|

| ECS-40-20-4DN        | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-80-18-4DN        | ECS Inc. | 8 MHz  | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-100-18-4-DN      | ECS Inc. | 10 MHz | 18 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-200-20-4DN       | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | TH               | -40°C to +85°C           |

| ECS-40-20-5G3XDS-TR  | ECS Inc. | 4 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-80-20-5G3XDS-TR  | ECS Inc. | 8 MHz  | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-100-20-5G3XDS-TR | ECS Inc. | 10 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to +125°C          |

| ECS-200-20-5G3XDS-TR | ECS Inc. | 20 MHz | 20 pF        | HC49/US         | ±30 ppm                | SM               | -40°C to 125°C           |

| NX3225SA 20MHZ AT-W  | NDK      | 20 MHz | 8 pF         | 3.2 mm x 2.5 mm | ±50 ppm                | SM               | -40°C to 125°C           |

**Legend:** TH = Through Hole SM = Surface Mount

## TABLE 4-10: UART2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                        | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                 | Bit 6   | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|-------------------------------|--------|----------|--------|--------|--------|-------|-------|-----------------------|---------|-------|------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230        | UARTEN                        | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0  | WAKE                  | LPBACK  | ABAUD | URXINV     | BRGH         | PDSEI | L<1:0> | STSEL | 0000          |

| U2STA    | 0232        | UTXISEL1                      | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISI                | EL<1:0> | ADDEN | RIDLE      | PERR         | FERR  | OERR   | URXDA | 0110          |

| U2TXREG  | 0234        | -                             | _      | -        | _      | _      | _      | _     | UTX8  |                       |         | U     | ART Transn | nit Register |       |        |       | xxxx          |

| U2RXREG  | 0236        | -                             | _      | -        | _      | _      | _      | _     | URX8  | UART Receive Register |         |       |            |              |       |        |       | 0000          |

| U2BRG    | 0238        | Baud Rate Generator Prescaler |        |          |        |        |        |       |       |                       |         | 0000  |            |              |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### **TABLE 4-11: SPI1 REGISTER MAP**

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                    | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|-------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT | 0240        | SPIEN  | _                                         | SPISIDL | _      | _      | _      | _     | _     | _     | SPIROV | _     | _     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _                                         | -       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN |       | SPRE<2:0> | •     | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD                                    | FRMPOL  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        | SPI1 Transmit and Receive Buffer Register |         |        |        |        |       |       |       |        |       | 0000  |           |       |        |        |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-12: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                                    | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|-------------------------------------------|--------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN                                     | _      | SPISIDL | _      | _      | _      | _     | _     | _     | SPIROV | _     | _     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | _                                         | _      | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN                                     | SPIFSD | FRMPOL  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI2BUF  | 0268        | SPI2 Transmit and Receive Buffer Register |        |         |        |        |        |       |       |       |        | 0000  |       |           |       |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-0       | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------------|-------|

| _     | _   | _   | _   | _   |       | DMA3IP<2:0> |       |

| bit 7 |     |     |     |     |       |             | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0'

bit 2-0 DMA3IP<2:0>: DMA Channel 3 Data Transfer Complete Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

#### REGISTER 7-31: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | R-0 | R-0  | R-0   | R-0   |

|--------|-----|-----|-----|-----|------|-------|-------|

| _      | _   | _   | _   |     | ILR< | :3:0> |       |

| bit 15 |     |     |     |     |      |       | bit 8 |

|   | U-0   | R-0 | R-0 | R-0 | R-0        | R-0 | R-0 | R-0   |

|---|-------|-----|-----|-----|------------|-----|-----|-------|

|   | _     |     |     |     | VECNUM<6:0 | >   |     |       |

| Ī | bit 7 |     |     |     |            |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11-8 ILR<3:0>: New CPU Interrupt Priority Level bits

1111 = CPU Interrupt Priority Level is 15

•

.

0001 = CPU Interrupt Priority Level is 1

0000 = CPU Interrupt Priority Level is 0

bit 7 **Unimplemented:** Read as '0'

bit 6-0 **VECNUM<6:0>:** Vector Number of Pending Interrupt bits

0111111 = Interrupt Vector pending is number 135

.

•

0000001 = Interrupt Vector pending is number 9

0000000 = Interrupt Vector pending is number 8

#### **RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3 REGISTER 11-3:**

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | _   |       |       | T3CKR<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | T2CKR<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-8 T3CKR<4:0>: Assign Timer3 External Clock (T3CK) to the corresponding RPn pin

> 11111 = Input tied to Vss 11001 = Input tied to RP25

00001 = Input tied to RP1

00000 = Input tied to RP0

bit 7-5 Unimplemented: Read as '0'

T2CKR<4:0>: Assign Timer2 External Clock (T2CK) to the corresponding RPn pin bit 4-0

> 11111 = Input tied to Vss 11001 = Input tied to RP25

00001 = Input tied to RP1 00000 = Input tied to RP0

### REGISTER 11-7: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | OCFAR<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 OCFAR<4:0>: Assign Output Compare A (OCFA) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

## 13.0 TIMER2/3 AND TIMER4/5 FEATURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

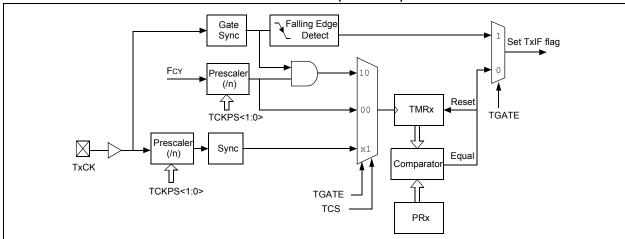

Timer2 and Timer4 are Type B timers with the following specific features:

- A Type B timer can be concatenated with a Type C timer to form a 32-bit timer

- The external clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

A block diagram of the Type B timer is shown in Figure 13-1.

Timer3 and Timer5 are Type C timers with the following specific features:

- A Type C timer can be concatenated with a Type B timer to form a 32-bit timer

- At least one Type C timer has the ability to trigger an analog-to-digital conversion.

- The external clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed before the prescaler

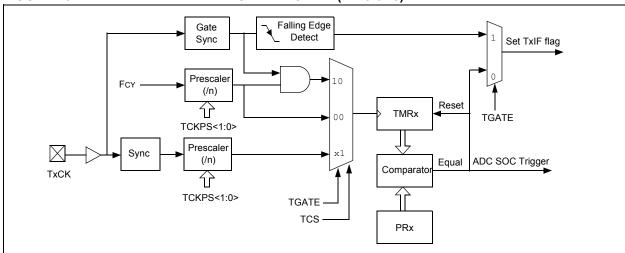

A block diagram of the Type C timer is shown in Figure 13-2.

FIGURE 13-1: TYPE B TIMER BLOCK DIAGRAM (x = 2 or 4)

FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 or 5)

Gate Falling Edge Set TylF Sync Detect Flag PRx PRy Equal Comparator **TGATE** Prescaler 10 (/n) Isw msw ADC SOC trigger Reset **TMRx TMRy** 00 TCKPS<1:0> Prescaler Sync x1 (/n) TxCK TMRyHLD TCKPS<1:0> TGATE TCS Data Bus <15:0> Note 1: ADC trigger is available only on TMR3:TMR2 and TMR5:TMR2 32-bit timers. 2: Timer x is a Type B Timer (x = 2 and 4). 3: Timer y is a Type C Timer (y = 3 and 5).

#### FIGURE 13-3: 32-BIT TIMER BLOCK DIAGRAM

#### 13.3 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en532311

#### 13.3.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0 HSC    | R-0 HSC | U-0 | U-0 | U-0 | R/C-0 HS | R-0 HSC | R-0 HSC |

|------------|---------|-----|-----|-----|----------|---------|---------|

| ACKSTAT    | TRSTAT  | _   | _   | _   | BCL      | GCSTAT  | ADD10   |

| bit 15 bit |         |     |     |     |          |         | bit 8   |

| R/C-0 HS | R/C-0 HS | R-0 HSC | R/C-0 HSC | R/C-0 HSC | R-0 HSC | R-0 HSC | R-0 HSC |

|----------|----------|---------|-----------|-----------|---------|---------|---------|

| IWCOL    | I2COV    | D_A     | Р         | S         | R_W     | RBF     | TBF     |

| bit 7    |          |         |           |           |         |         | bit 0   |

| Legend:           | U = Unimplemented bit, rea | ad as '0'            | C = Clear only bit         |

|-------------------|----------------------------|----------------------|----------------------------|

| R = Readable bit  | W = Writable bit           | HS = Set in hardware | HSC = Hardware set/cleared |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared | x = Bit is unknown         |

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as I<sup>2</sup>C<sup>™</sup> master, applicable to master transmit operation)

1 = NACK received from slave 0 = ACK received from slave

Hardware set or clear at end of slave Acknowledge.

naraware est of clour at one of clave hoursemouge.

**TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

1 = Master transmit is in progress (8 bits + ACK)

0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

bit 13-11 **Unimplemented:** Read as '0'

bit 14

bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision.

bit 9 GCSTAT: General Call Status bit

1 = General call address was received0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte

0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

1 = Indicates that the last byte received was data

0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

bit 4 **P:** Stop bit

1 = Indicates that a Stop bit has been detected last

0 = Stop bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

### 20.3 DCI Control Registers

#### REGISTER 20-1: DCICON1: DCI CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|---------|-----|-------|-------|-------|-------|

| DCIEN  | _   | DCISIDL | _   | DLOOP | CSCKD | CSCKE | COFSD |

| bit 15 |     |         |     |       |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0  |

|-------|-------|-------|-----|-----|-----|-------|--------|

| UNFM  | CSDOM | DJST  | _   | _   | _   | COFSI | M<1:0> |

| bit 7 |       |       |     |     |     |       | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 DCIEN: DCI Module Enable bit

1 = Module is enabled

0 = Module is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 DCISIDL: DCI Stop in Idle Control bit

1 = Module will halt in CPU Idle mode

0 = Module will continue to operate in CPU Idle mode

bit 12 **Unimplemented:** Read as '0'

bit 11 **DLOOP:** Digital Loopback Mode Control bit

1 = Digital Loopback mode is enabled. CSDI and CSDO pins internally connected.

0 = Digital Loopback mode is disabled

bit 10 CSCKD: Sample Clock Direction Control bit

1 = CSCK pin is an input when DCI module is enabled

0 = CSCK pin is an output when DCI module is enabled

bit 9 CSCKE: Sample Clock Edge Control bit

1 = Data changes on serial clock falling edge, sampled on serial clock rising edge

0 = Data changes on serial clock rising edge, sampled on serial clock falling edge

bit 8 **COFSD:** Frame Synchronization Direction Control bit

1 = COFS pin is an input when DCI module is enabled

0 = COFS pin is an output when DCI module is enabled

bit 7 UNFM: Underflow Mode bit

1 = Transmit last value written to the transmit registers on a transmit underflow

0 = Transmit '0's on a transmit underflow

bit 6 **CSDOM:** Serial Data Output Mode bit

1 = CSDO pin will be tri-stated during disabled transmit time slots

0 = CSDO pin drives '0's during disabled transmit time slots

bit 5 DJST: DCI Data Justification Control bit

1 = Data transmission/reception is begun during the same serial clock cycle as the frame synchronization pulse

0 = Data transmission/reception is begun one serial clock cycle after frame synchronization pulse

bit 4-2 **Unimplemented:** Read as '0'

bit 1-0 **COFSM<1:0>:** Frame Sync Mode bits

11 = 20-bit AC-Link mode

10 = 16-bit AC-Link mode

$01 = I^2S$  Frame Sync mode

00 = Multi-Channel Frame Sync mode

# 22.0 AUDIO DIGITAL-TO-ANALOG CONVERTER (DAC)

Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 33. "Audio Digital-to-Analog Converter (DAC)" (DS70211) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Audio Digital-to-Analog Converter (DAC) module is a 16-bit Delta-Sigma signal converter designed for audio applications. It has two output channels, left and right to support stereo applications. Each DAC output channel provides three voltage outputs, positive DAC output, negative DAC output, and the midpoint voltage output for the dsPIC33FJ64GP804 and dsPIC33FJ128GP804 The devices. dsPIC33FJ128GP802 dsPIC33FJ64GP802 and devices provide positive DAC output and negative DAC output voltages.

#### 22.1 Key Features

- 16-bit resolution (14-bit accuracy)

- Second-Order Digital Delta-Sigma Modulator

- 256 X Over-Sampling Ratio

- 128-Tap FIR Current-Steering Analog Reconstruction Filter

- · 100 ksps Maximum Sampling Rate

- · User controllable Sample Clock

- Input Frequency 45 kHz max

- Differential Analog Outputs

- · Signal-To-Noise: 90 dB

- · 4-deep input Buffer

- 16-bit Processor I/O, and DMA interfaces

## 22.2 DAC Module Operation

The functional block diagram of the Audio DAC module is shown in Figure 22-1. The Audio DAC module provides a 4-deep data input FIFO buffer for each output channel. If the DMA module and/or the processor cannot provide output data in a timely manner, and the FIFO becomes empty, the DAC accepts data from the DAC Default Data register (DACDFLT). This safety feature is useful for industrial

control applications where the DAC output controls an important processor or machinery. The DACDFLT register should be initialized with a "safe" output value. Often the safe output value is either the midpoint value (0x8000) or a zero value (0x0000).

The digital interpolator up-samples the input signals, where the over-sampling ratio is 256x which creates data points between the user supplied data points. The interpolator also includes processing by digital filters to provide "noise shaping" to move the converter noise above 20 kHz (upper limit of the pass band). The output of the interpolator drives the Sigma-Delta modulator. The serial data bit stream from the Sigma-Delta modulator is processed by the reconstruction filter. The differential outputs of the reconstruction filter are amplified by Op Amps to provide the required peak-to-peak voltage swing.

**Note:** The DAC module is designed specifically for audio applications and is not recommended for control type applications.

### 22.3 DAC Output Format

The DAC output data stream can be in a two's complement signed number format or as an unsigned number format.

The Audio DAC module features the ability to accept the 16-bit input data in a two's complement signed number format or as an unsigned number format. The data formatting is controlled by the Data Format Control bit (FORM<8>) in the DAC1CON register. The supported formats are:

- 1 = Signed (two's complement)

- 0 = Unsigned

If the FORM bit is configured for "Unsigned data" then the user input data yields the following behavior:

- 0xFFFF = most positive output voltage

- 0x8000 = mid point output voltage

- 0x7FFF = a value just below the midpoint

- 0x0000 = minimum output voltage

If the FORM bit is configured for "signed data" then the user input data yields the following behavior:

- 0x7FFF = most positive output voltage

- 0x0000 = mid point output voltage

- 0xFFFF = value just below the midpoint

- 0x8000 = minimum output voltage

The Audio DAC provides an analog output proportional to the digital input value. The maximum 100,000 samples per second (100 ksps) update rate provides good quality audio reproduction.

### 26.1 PMP Resources

Many useful resources related to PMP are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en532311

### 26.1.1 KEY RESOURCES

- Section 35. "Parallel Master Port (PMP)" (DS70299)

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- · Development Tools

TABLE 27-5: CODE FLASH SECURITY SEGMENT SIZES FOR 128 KB DEVICES

| CONFIG BITS           | BSS<2:0> = x11 0K | BSS<2:0> = x10 1K                                                                                                                                                                                                                                                       | BSS<2:0> = x01 4K | BSS<2:0> = x00 8K                                                                                                                                                                 |

|-----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0> = x11<br>0K  | VS = 256 IW       | VS = 256 IW  BS = 768 IW  0x0001FEh 0x000200h 0x0007FEh 0x00800h 0x001FFEh 0x00200h 0x003FFEh 0x002000h 0x007FFEh 0x004000h 0x007FFEh 0x008000h 0x007FFEh 0x008000h 0x007FFEh 0x008000h 0x007FFEH 0x008000h 0x007FFEH 0x008000h 0x007FFEH 0x008000h 0x007FFEH 0x010000h | VS = 256 IW       | VS = 256 IW                                                                                                                                                                       |

| SSS<2:0> = x10<br>4K  | VS = 256 IW       | VS = 256 IW                                                                                                                                                                                                                                                             | VS = 256 IW       | VS = 256 IW  BS = 7936 IW  BS = 7936 IW  0x000200h 0x00250h 0x007FEh 0x00200h 0x003FFEh 0x004000h 0x004FFEh 0x004000h 0x004FFEh 0x004000h 0x004FFEh 0x004000h 0x004FFEh 0x004BFEh |

| SSS<2:0> = x01<br>8K  | VS = 256 IW       | VS = 256 IW                                                                                                                                                                                                                                                             | VS = 256 IW       | VS = 256 IW                                                                                                                                                                       |

| SSS<2:0> = x00<br>16K | VS = 256 IW       | VS = 256 IW                                                                                                                                                                                                                                                             | VS = 256 IW       | VS = 256 IW                                                                                                                                                                       |

#### 29.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers and dsPIC® digital signal controllers are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>TM</sup> Assembler

- MPLINK™ Object Linker/ MPLIB™ Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- · Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 29.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows® operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

TABLE 31-6: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHA     | DC CHARACTERISTICS                                                                                                          |                                                                                                                |      |      | se state | -40°C ≤Ta ≤+150°C for High<br>Temperature      |                                                 |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|----------|------------------------------------------------|-------------------------------------------------|--|

| Param.     | Symbol                                                                                                                      | Characteristic                                                                                                 | Min. | Тур. | Max.     | Units                                          | Conditions                                      |  |

|            |                                                                                                                             | Output Low Voltage I/O Pins: 2x Sink Driver Pins - RA2, RA7-RA10, RB10, RB11, RB7, RB4, RC3-RC9                | _    | _    | 0.4      | V                                              | IoL ≤1.8 mA, VDD = 3.3V<br>See <b>Note 1</b>    |  |

| DO10       | Vol                                                                                                                         | Output Low Voltage I/O Pins: 4x Sink Driver Pins - RA0, RA1, RB0-RB3, RB5, RB6, RB8, RB9, RB12-RB15, RC0-RC2   | ı    | _    | 0.4      | V                                              | IoL ≤3.6 mA, VDD = 3.3V<br>See <b>Note 1</b>    |  |

|            |                                                                                                                             | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - RA3, RA4                                              | l    | _    | 0.4      | V                                              | IOL ⊴6 mA, VDD = 3.3V<br>See <b>Note 1</b>      |  |

|            |                                                                                                                             | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,<br>RB11, RC3-RC9 | 2.4  |      |          | V                                              | IOL ≥ -1.8 mA, VDD = 3.3V<br>See <b>Note 1</b>  |  |

| DO20 VOH   | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA0,<br>RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2 | 2.4                                                                                                            | _    | _    | ٧        | IOL ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>   |                                                 |  |

|            |                                                                                                                             | Output High Voltage I/O Pins: 8x Source Driver Pins - RA4, RA3                                                 | 2.4  |      |          | V                                              | IoL ≥ -6 mA, VDD = 3.3V<br>See <b>Note 1</b>    |  |

|            |                                                                                                                             | Output High Voltage I/O Pins:                                                                                  | 1.5  | _    | _        |                                                | IOH ≥ -1.9 mA, VDD = 3.3V<br>See <b>Note 1</b>  |  |

|            |                                                                                                                             | 2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,<br>RB11, RC3-RC9                                     | 2.0  | _    | _        | V                                              | IOH ≥ -1.85 mA, VDD = 3.3V<br>See <b>Note 1</b> |  |

|            |                                                                                                                             | NB11, NO3-NO3                                                                                                  | 3.0  | _    | _        |                                                | IOH ≥ -1.4 mA, VDD = 3.3V<br>See <b>Note 1</b>  |  |

|            |                                                                                                                             | Output High Voltage<br>4x Source Driver Pins - RA0,                                                            | 1.5  | _    | _        |                                                | IOH ≥ -3.9 mA, VDD = 3.3V<br>See <b>Note 1</b>  |  |

| DO20A Voh1 | RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2                                                                     | 2.0                                                                                                            | _    | _    | V        | IOH ≥ -3.7 mA, VDD = 3.3V<br>See <b>Note 1</b> |                                                 |  |

|            |                                                                                                                             |                                                                                                                | 3.0  | _    | _        |                                                | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>    |  |

|            |                                                                                                                             | Output High Voltage I/O Pins:                                                                                  | 1.5  | _    | _        |                                                | IOH ≥ -7.5 mA, VDD = 3.3V<br>See <b>Note 1</b>  |  |

|            |                                                                                                                             | 8x Source Driver Pins - RA3,<br>RA4                                                                            | 2.0  | _    | _        | V                                              | IOH ≥ -6.8 mA, VDD = 3.3V<br>See <b>Note 1</b>  |  |

|            |                                                                                                                             | tors are characterized but not too                                                                             | 3.0  | _    | _        |                                                | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>    |  |

**Note 1:** Parameters are characterized, but not tested.

7200

-40 -30 -20 -10 0

10 20 30 40 50 60 70 80 90 100 110 120

Temperature (Celsius)

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

## **Revision F (August 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

TABLE A-5: MAJOR SECTION UPDATES

| Section Name                                                                        | Update Description                                                                                                                 |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Updated the Recommendation Minimum Connection (see Figure 2-1).                                                                    |

| Section 27.0 "Special Features"                                                     | Added Note 3 to the Connections for the On-chip Voltage Regulator diagram (see Figure 27-1).                                       |

| Section 30.0 "Electrical Characteristics"                                           | Removed Voltage on VCAP with respect to Vss from the Absolute Maximum Ratings.                                                     |

|                                                                                     | Removed Note 3 and parameter DC10 (VCORE) from the DC Temperature and Voltage Specifications (see Table 30-4).                     |

|                                                                                     | Updated the Characteristics definition and Conditions for parameter BO10 in the Electrical Characteristics: BOR (see Table 30-11). |

|                                                                                     | Added Note 1 to the Internal Voltage Regulator Specifications (see Table 30-13).                                                   |

## Revision G (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 9.2 "Oscillator Resources" and Section 21.4 "ADC Helpful Tips".

All other major changes are referenced by their respective section in the following table.

TABLE A-6: MAJOR SECTION UPDATES

| Section Name                                                                        | Update Description                                                                                                                               |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 2.0 "Guidelines for Getting Started with 16-bit Digital Signal Controllers" | Added two new tables:  • Crystal Recommendations (see Table 2-1)                                                                                 |

|                                                                                     | Resonator Recommendations (see Table 2-2)                                                                                                        |

| Section 30.0 "Electrical Characteristics"                                           | Updated parameters DO10 and DO20 and removed parameters DO16 and DO26 in the DC Characteristics: I/O Pin Output Specifications (see Table 30-10) |