Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 80MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                   |

| Number of I/O              | 38                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 160K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l462ceu6   |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

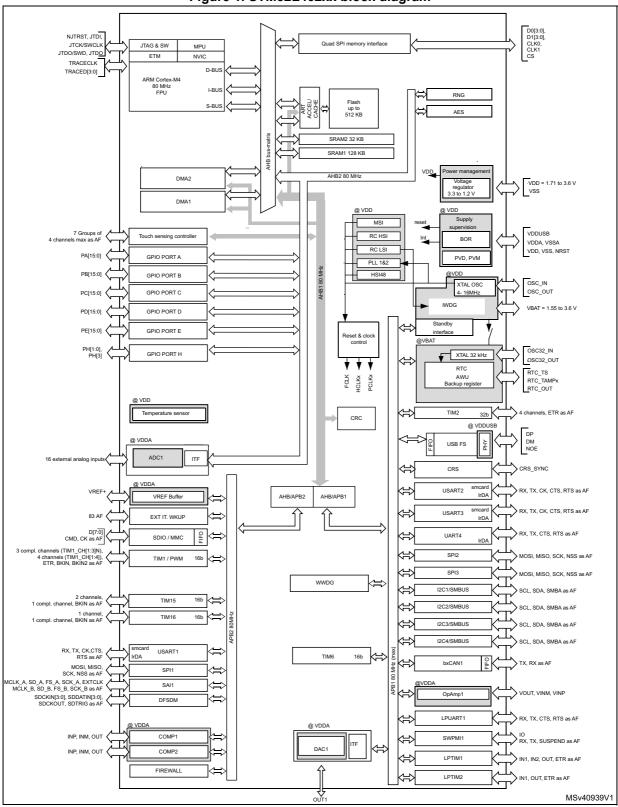

Figure 1. STM32L462xx block diagram

By default, the microcontroller is in Run mode after a system or a power Reset. It is up to the user to select one of the low-power modes described below:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Low-power run mode

This mode is achieved with  $V_{CORE}$  supplied by the low-power regulator to minimize the regulator's operating current. The code can be executed from SRAM or from Flash, and the CPU frequency is limited to 2 MHz. The peripherals with independent clock can be clocked by HSI16.

#### • Low-power sleep mode

This mode is entered from the low-power run mode. Only the CPU clock is stopped. When wakeup is triggered by an event or an interrupt, the system reverts to the lowpower run mode.

#### • Stop 0, Stop 1 and Stop 2 modes

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the V<sub>CORE</sub> domain are stopped, the PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are disabled. The LSE or LSI is still running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals with wakeup capability can enable the HSI16 RC during Stop mode to detect their wakeup condition.

Three Stop modes are available: Stop 0, Stop 1 and Stop 2 modes. In Stop 2 mode, most of the  $V_{CORE}$  domain is put in a lower leakage mode.

Stop 1 offers the largest number of active peripherals and wakeup sources, a smaller wakeup time but a higher consumption than Stop 2. In Stop 0 mode, the main regulator remains ON, allowing a very fast wakeup time but with much higher consumption.

The system clock when exiting from Stop 0, Stop 1 or Stop 2 modes can be either MSI up to 48 MHz or HSI16, depending on software configuration.

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the  $V_{CORE}$  domain is powered off. The PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are also switched off.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The brown-out reset (BOR) always remains active in Standby mode.

The state of each I/O during standby mode can be selected by software: I/O with internal pull-up, internal pull-down or floating.

After entering Standby mode, SRAM1 and register contents are lost except for registers in the Backup domain and Standby circuitry. Optionally, SRAM2 can be retained in Standby mode, supplied by the low-power Regulator (Standby with SRAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE). The system clock after wakeup is MSI up to 8 MHz.

The system clock after wakeup is wish up to a r

|                      |     |       |                      |                        | Stop | o 0/1             | Sto | op 2              | Star | ndby              | Shut | down              |      |

|----------------------|-----|-------|----------------------|------------------------|------|-------------------|-----|-------------------|------|-------------------|------|-------------------|------|

| Peripheral           | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | -    | Wakeup capability | -   | Wakeup capability | -    | Wakeup capability | -    | Wakeup capability | VBAT |

| CRC calculation unit | 0   | 0     | 0                    | 0                      | -    | -                 | -   | -                 | -    | -                 | -    | -                 | -    |

| GPIOs                | 0   | 0     | 0                    | 0                      | 0    | 0                 | 0   | 0                 | (9)  | 5<br>pins<br>(10) | (11) | 5<br>pins<br>(10) | -    |

Table 4. Functionalities depending on the working mode<sup>(1)</sup> (continued)

1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). - = Not available.

2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

3. The SRAM clock can be gated on or off.

4. SRAM2 content is preserved when the bit RRS is set in PWR\_CR3 register.

Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

6. UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

8. Voltage scaling Range 1 only.

9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

## 3.9.5 Reset mode

In order to improve the consumption under reset, the I/Os state under and after reset is "analog state" (the I/O schmitt trigger is disable). In addition, the internal reset pull-up is deactivated when the reset source is internal.

## 3.9.6 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present. The VBAT pin supplies the RTC with LSE and the backup registers. Three anti-tamper detection pins are available in VBAT mode.

VBAT operation is automatically activated when  $V_{\text{DD}}$  is not present.

An internal VBAT battery charging circuit is embedded and can be activated when  $\mathrm{V}_{\mathrm{DD}}$  is present.

*Note:* When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from VBAT operation.

# 3.15 Analog to digital converter (ADC)

The device embeds a successive approximation analog-to-digital converter with the following features:

- 12-bit native resolution, with built-in calibration

- 5.33 Msps maximum conversion rate with full resolution

- Down to 18.75 ns sampling time

- Increased conversion rate for lower resolution (up to 8.88 Msps for 6-bit resolution)

- Up to 16 external channels.

- 4 internal channels: internal reference voltage, temperature sensor, VBAT/3 and DAC1\_OUT1.

- One external reference pin is available on some package, allowing the input voltage range to be independent from the power supply

- Single-ended and differential mode inputs

- Low-power design

- Capable of low-current operation at low conversion rate (consumption decreases linearly with speed)

- Dual clock domain architecture: ADC speed independent from CPU frequency

- Highly versatile digital interface

- Single-shot or continuous/discontinuous sequencer-based scan mode: 2 groups of analog signals conversions can be programmed to differentiate background and high-priority real-time conversions

- ADC supports multiple trigger inputs for synchronization with on-chip timers and external signals

- Results stored into data register or in RAM with DMA controller support

- Data pre-processing: left/right alignment and per channel offset compensation

- Built-in oversampling unit for enhanced SNR

- Channel-wise programmable sampling time

- Three analog watchdog for automatic voltage monitoring, generating interrupts and trigger for selected timers

- Hardware assistant to prepare the context of the injected channels to allow fast context switching

### 3.15.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{TS}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN17 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

## 3.29 Serial peripheral interface (SPI)

Three SPI interfaces allow communication up to 40 Mbits/s in master and up to 24 Mbits/s slave modes, in half-duplex, full-duplex and simplex modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits. The SPI interfaces support NSS pulse mode, TI mode and Hardware CRC calculation.

All SPI interfaces can be served by the DMA controller.

# 3.30 Serial audio interfaces (SAI)

The device embeds 1 SAI. Refer to *Table 13: SAI implementation* for the features implementation. The SAI bus interface handles communications between the microcontroller and the serial audio protocol.

The SAI peripheral supports:

- Two independent audio sub-blocks which can be transmitters or receivers with their respective FIFO.

- 8-word integrated FIFOs for each audio sub-block.

- Synchronous or asynchronous mode between the audio sub-blocks.

- Master or slave configuration independent for both audio sub-blocks.

- Clock generator for each audio block to target independent audio frequency sampling when both audio sub-blocks are configured in master mode.

- Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit.

- Peripheral with large configurability and flexibility allowing to target as example the following audio protocol: I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF out.

- Up to 16 slots available with configurable size and with the possibility to select which ones are active in the audio frame.

- Number of bits by frame may be configurable.

- Frame synchronization active level configurable (offset, bit length, level).

- First active bit position in the slot is configurable.

- LSB first or MSB first for data transfer.

- Mute mode.

- Stereo/Mono audio frame capability.

- Communication clock strobing edge configurable (SCK).

- Error flags with associated interrupts if enabled respectively.

- Overrun and underrun detection.

- Anticipated frame synchronization signal detection in slave mode.

- Late frame synchronization signal detection in slave mode.

- Codec not ready for the AC'97 mode in reception.

- Interruption sources when enabled:

- Errors.

- FIFO requests.

- DMA interface with 2 dedicated channels to handle access to the dedicated integrated FIFO of each SAI audio sub-block.

The Quad SPI interface supports:

- Three functional modes: indirect, status-polling, and memory-mapped

- Dual-flash mode, where 8 bits can be sent/received simultaneously by accessing two flash memories in parallel.

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Each of the 5 following phases can be configured independently (enable, length, single/dual/quad communication)

- Instruction phase

- Address phase

- Alternate bytes phase

- Dummy cycles phase

- Data phase

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Programmable masking for external flash flag management

- Timeout management

- Interrupt generation on FIFO threshold, timeout, status match, operation complete, and access error

|   | 1                            | 2    | 3   | 4                    | 5                                                     | 6    | 7    | 8    | 9    | 10   | 11     | 12   |  |  |

|---|------------------------------|------|-----|----------------------|-------------------------------------------------------|------|------|------|------|------|--------|------|--|--|

| A | PE3                          | PE1  | PB8 | PH3-BOOT0<br>(BOOT0) | (BOOT0) PD7 PD5 (NJTRST) TRAČESWO) PA15 (JIDI) SWČLK) |      |      |      |      |      |        |      |  |  |

| в | PE4                          | PE2  | PB9 | PB7                  | PB6                                                   | PD6  | PD1  | PC12 | PC10 | PA11 |        |      |  |  |

| с | PC13                         | PE5  | PE0 | VDD                  | PB5                                                   |      |      | PD2  | PD0  | PC11 | VDDUSB | PA10 |  |  |

| D | PC14-<br>OSC32_IN<br>(PC14)  | PE6  | VSS |                      |                                                       | •    |      |      |      | PA9  | PA8    | PC9  |  |  |

| E | PC15-<br>OSC32_OUT<br>(PC15) | VBAT | vss | PC8 PC7              |                                                       |      |      |      |      |      | PC6    |      |  |  |

| F | PH0-OSC_IN<br>(PH0)          | vss  |     |                      | l                                                     |      | VSS  | VSS  |      |      |        |      |  |  |

| G | PH1-<br>OSC_OUT<br>(PH1)     | VDD  |     |                      |                                                       |      | VDD  | VDD  |      |      |        |      |  |  |

| н | PC0                          | NRST | VDD |                      |                                                       | PD15 | PD14 | PD13 |      |      |        |      |  |  |

| L | VSSA                         | PC1  | PC2 |                      |                                                       |      |      |      |      | PD12 | PD11   | PD10 |  |  |

| к | VREF-                        | PC3  | PA2 | PA5                  | PC4                                                   |      |      | PD9  | PD8  | PB15 | PB14   | PB13 |  |  |

| L | VREF+                        | PA0  | PA3 | PA6                  | PC5                                                   | PB2  | PE8  | PE10 | PE12 | PB10 | PB11   | PB12 |  |  |

| м | VDDA                         | PA1  | PA4 | PA7                  | PB0                                                   | PB1  | PE7  | PE9  | PE11 | PE13 | PE14   | PE15 |  |  |

|   |                              |      |     |                      |                                                       |      |      |      |      |      |        | MSv4 |  |  |

Figure 7. STM32L462Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

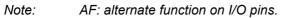

Figure 8. STM32L462Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|   | 1                            | 2    | 3   | 4                    | 5                       | 6           | 7                     | 8                     |

|---|------------------------------|------|-----|----------------------|-------------------------|-------------|-----------------------|-----------------------|

| A | PC14-<br>OSC32_IN<br>(PC14)  | PC13 | PB9 | PB4<br>(NJTRST)      | PB3 (JTDO/<br>TRACESWO) | PA15 (JTDI) | PA14 (JTCK/<br>SWCLK) | PA13 (JTMS/<br>SWDIO) |

| В | PC15-<br>OSC32_OUT<br>(PC15) | VBAT | PB8 | PH3-BOOT0<br>(BOOT0) | PD2                     | PC11        | PC10                  | PA12                  |

| c | PH0-OSC_IN<br>(PH0)          | VSS  | PB7 | PB5                  | PC12                    | PA10        | PA9                   | PA11                  |

| D | PH1-<br>OSC_OUT<br>(PH1)     | VDD  | PB6 | vss                  | VSS                     | vss         | PA8                   | PC9                   |

| E | NRST                         | PC1  | PC0 | VDD                  | VDDUSB                  | VDD         | PC7                   | PC8                   |

| F | VSSA/VREF-                   | PC2  | PA2 | PA5                  | PB0                     | PC6         | PB15                  | PB14                  |

| G | PC3                          | PA0  | PA3 | PA6                  | PB1                     | PB2         | PB10                  | PB13                  |

| н | VDDA/VREF+                   | PA1  | PA4 | PA7                  | PC4                     | PC5         | PB11                  | PB12                  |

|   |                              |      |     |                      |                         |             |                       |                       |

## Figure 9. STM32L462Rx UFBGA64 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

|   | . iguit |                       |                       |                         |     | ••••                 | Pinea                        | •                           |

|---|---------|-----------------------|-----------------------|-------------------------|-----|----------------------|------------------------------|-----------------------------|

|   | 1       | 2                     | 3                     | 4                       | 5   | 6                    | 7                            | 8                           |

| A | VDDUSB  | PA15 (JTDI)           | PC12                  | PB4<br>(NJTRST)         | PB7 | PB8                  | VSS                          | VDD                         |

| В | VSS     | VDD                   | PC11                  | PB3 (JTDO/<br>TRACESWO) | PB6 | PH3-BOOT0<br>(BOOT0) | VBAT                         | PC13                        |

| c | PA10    | PA13 (JTMS/<br>SWDIO) | PA14 (JTCK/<br>SWCLK) | PD2                     | PB5 | PB9                  | PC15-<br>OSC32_OUT<br>(PC15) | PC14-<br>OSC32_IN<br>(PC14) |

| D | PA9     | PA11                  | PA12                  | PC10                    | PC1 | PC2                  | PC0                          | PH0-OSC_IN<br>(PH0)         |

| E | PC7     | PC9                   | PA8                   | PC4                     | PA7 | PA1                  | PC3                          | PH1-<br>OSC_OUT<br>(PH1)    |

| F | PB15    | PC6                   | PC8                   | PB1                     | PA5 | PA3                  | VDDA/VREF+                   | NRST                        |

| G | PB14    | PB13                  | PB12                  | PB2                     | PC5 | PA4                  | PA2                          | VSSA/VREF-                  |

| н | VDD     | vss                   | PB11                  | PB10                    | PB0 | PA6                  | VDD                          | PA0                         |

|   |         |                       |                       |                         |     |                      |                              |                             |

## Figure 10. STM32L462Rx WLCSP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

| Π             |

|---------------|

|               |

| _             |

| _             |

| 0             |

| Ē.            |

| <b>—</b>      |

| ธ             |

| ۵u            |

| =             |

| _             |

| Q             |

| _             |

| $\mathbf{D}$  |

|               |

| Ξ.            |

|               |

|               |

|               |

| n d           |

|               |

| n d           |

| n d           |

| n d           |

| n d           |

| n descr       |

| n descript    |

| n descr       |

| n descript    |

| n description |

|        |      |         | Tabl                | le 16. Alternate        | function AF0 to           | o AF7 <sup>(1)</sup> (conti | nued)          |                      |                              |

|--------|------|---------|---------------------|-------------------------|---------------------------|-----------------------------|----------------|----------------------|------------------------------|

|        |      | AF0     | AF1                 | AF2                     | AF3                       | AF4                         | AF5            | AF6                  | AF7                          |

| Po     | ort  | SYS_AF  | TIM1/TIM2<br>LPTIM1 | I2C4/TIM1/<br>TIM2/TIM3 | I2C4/USART2/<br>CAN1/TIM1 | 2C1/ 2C2/<br> 2C3/ 2C4      | SPI1/SPI2/I2C4 | SPI3/DFSDM/<br>COMP1 | USART1/<br>USART2/<br>USART3 |

|        | PD0  | -       | -                   | -                       | -                         | -                           | SPI2_NSS       | -                    | -                            |

|        | PD1  | -       | -                   | -                       | -                         | -                           | SPI2_SCK       | -                    | -                            |

|        | PD2  | TRACED2 | -                   | TIM3_ETR                | -                         | -                           | -              | -                    | USART3_RTS_<br>DE            |

|        | PD3  | -       | -                   | -                       | -                         | -                           | SPI2_MISO      | DFSDM1_<br>DATIN0    | USART2_CTS                   |

|        | PD4  | -       | -                   | -                       | -                         | -                           | SPI2_MOSI      | DFSDM1_<br>CKIN0     | USART2_RTS_<br>DE            |

|        | PD5  | -       | -                   | -                       | -                         | -                           | -              | -                    | USART2_TX                    |

|        | PD6  | -       | -                   | -                       | -                         | -                           | -              | DFSDM1_<br>DATIN1    | USART2_RX                    |

| Port D | PD7  | -       | -                   | -                       | -                         | -                           | -              | DFSDM1_<br>CKIN1     | USART2_CK                    |

|        | PD8  | -       | -                   | -                       | -                         | -                           | -              | -                    | USART3_TX                    |

|        | PD9  | -       | -                   | -                       | -                         | -                           | -              | -                    | USART3_RX                    |

|        | PD10 | -       | -                   | -                       | -                         | -                           | -              | -                    | USART3_CK                    |

|        | PD11 | -       | -                   | -                       | -                         | I2C4_SMBA                   | -              | -                    | USART3_CTS                   |

|        | PD12 | -       | -                   | -                       | -                         | I2C4_SCL                    | -              | -                    | USART3_RTS_<br>DE            |

|        | PD13 | -       | -                   | -                       | -                         | I2C4_SDA                    | -              | -                    | -                            |

|        | PD14 | -       | -                   | -                       | -                         | -                           | -              | -                    | -                            |

|        | PD15 | -       | -                   | -                       | -                         | -                           | -              | -                    | -                            |

74/204

DS11913 Rev 4

5

| ·      |      | 1                          | labi       | e 17. Alternate      | function AF8 | to AF15 <sup>(1)</sup> (conti | nuea)     | 1                           |          |  |

|--------|------|----------------------------|------------|----------------------|--------------|-------------------------------|-----------|-----------------------------|----------|--|

|        |      | AF8                        | AF9        | AF10                 | AF11         | AF12                          | AF13      | AF14                        | AF15     |  |

|        | Port | UART4/<br>LPUART1/<br>CAN1 | CAN1/TSC   | CAN1/USB/<br>QUADSPI | -            | SDMMC1/<br>COMP1/<br>COMP2    | SAI1      | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |  |

|        | PC0  | LPUART1_RX                 | -          | -                    | -            | -                             | -         | LPTIM2_IN1                  | EVENTOUT |  |

|        | PC1  | LPUART1_TX                 | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |  |

|        | PC2  | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |  |

|        | PC3  | -                          | -          | -                    | -            | -                             | SAI1_SD_A | LPTIM2_ETR                  | EVENTOUT |  |

|        | PC4  | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |  |

|        | PC5  | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOUT |  |

|        | PC6  | -                          | TSC_G4_IO1 | -                    | -            | SDMMC1_D6                     | -         | -                           | EVENTOUT |  |

| Port ( | PC7  | -                          | TSC_G4_IO2 | -                    | -            | SDMMC1_D7                     | -         | -                           | EVENTOUT |  |

| FOIL   | PC8  | -                          | TSC_G4_IO3 | -                    | -            | SDMMC1_D0                     | -         | -                           | EVENTOUT |  |

|        | PC9  | -                          | TSC_G4_IO4 | USBNOE               | -            | SDMMC1_D1                     | -         | -                           | EVENTOUT |  |

|        | PC10 | UART4_TX                   | TSC_G3_IO2 | -                    | -            | SDMMC1_D2                     | -         | -                           | EVENTOU  |  |

|        | PC11 | UART4_RX                   | TSC_G3_IO3 | -                    | -            | SDMMC1_D3                     | -         | -                           | EVENTOUT |  |

|        | PC12 | -                          | TSC_G3_IO4 | -                    | -            | SDMMC1_CK                     | -         | -                           | EVENTOU  |  |

|        | PC13 | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOU  |  |

|        | PC14 | -                          | -          | -                    | -            | -                             | -         | -                           | EVENTOU  |  |

|        | PC15 |                            |            | -                    | -            | -                             | -         | -                           | EVENTOUT |  |

Table 47 Alt ... **.**.. -41 . . . . . . . (hou

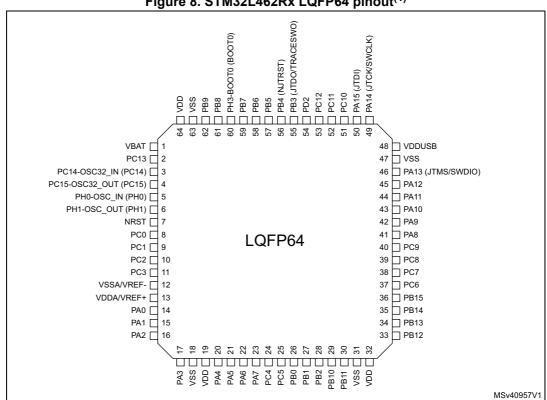

### 6.1.7 Current consumption measurement

Figure 16. Current consumption measurement scheme

The I<sub>DD\_ALL</sub> parameters given in *Table 26* to *Table 38* represent the total MCU consumption including the current supplying V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub> and V<sub>BAT</sub>.

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 19: Voltage characteristics*, *Table 20: Current characteristics* and *Table 21: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 qualification standard, extended mission profiles are available on demand.

| Symbol                             | Ratings                                                                         | Min                  | Мах                                                                                       | Unit |

|------------------------------------|---------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------|------|

| V <sub>DDX</sub> - V <sub>SS</sub> | External main supply voltage (including $V_{DD}, V_{DDA}, V_{DDUSB}, V_{BAT}$ ) | -0.3                 | 4.0                                                                                       | V    |

| (2)                                | Input voltage on FT_xxx pins                                                    | V <sub>SS</sub> -0.3 | min (V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>DDUSB</sub> )<br>+ 4.0 <sup>(3)(4)</sup> |      |

| $V_{IN}^{(2)}$                     | Input voltage on TT_xx pins                                                     | V <sub>SS</sub> -0.3 | 4.0                                                                                       | V    |

|                                    | Input voltage on any other pins                                                 | V <sub>SS</sub> -0.3 | 4.0                                                                                       |      |

|  | Table | 19. | Voltage | characteristics <sup>(1)</sup> |

|--|-------|-----|---------|--------------------------------|

|--|-------|-----|---------|--------------------------------|

| Symbol                                                       | Devementer                                               | Conditions                                                       |                 | ТҮР   |       |       |        |        | MAX <sup>(1)</sup> |       |       |        |        | Unit |

|--------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|-----------------|-------|-------|-------|--------|--------|--------------------|-------|-------|--------|--------|------|

| Symbol                                                       | Parameter                                                | -                                                                | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C              | 55 °C | 85 °C | 105 °C | 125 °C |      |

|                                                              |                                                          |                                                                  | 1.8 V           | 165   | 275   | 950   | 2600   | 6550   | -                  | -     | -     | -      | -      |      |

| in Shutdown<br>I <sub>DD_ALL</sub> mode<br>(Shutdown (backup | RTC clocked by LSE                                       | 2.4 V                                                            | 235             | 370   | 1150  | 3100  | 7650   | -      | -                  | -     | -     | -      |        |      |

|                                                              | bypassed at 32768 Hz                                     | 3 V                                                              | 325             | 485   | 1450  | 3750  | 9050   | -      | -                  | -     | -     | -      |        |      |

|                                                              |                                                          |                                                                  | 3.6 V           | 445   | 655   | 1900  | 4800   | 11500  | -                  | -     | -     | -      | -      | nA   |

|                                                              |                                                          | RTC clocked by LSE<br>quartz <sup>(2)</sup> in low drive<br>mode | 1.8 V           | 290   | 410   | 1050  | 2550   | 6700   | -                  | -     | -     | -      | -      | ПА   |

| ,                                                            |                                                          |                                                                  | 2.4 V           | 375   | 515   | 1250  | 3050   | 7800   | -                  | -     | -     | -      | -      |      |

|                                                              |                                                          |                                                                  | 3 V             | 480   | 645   | 1550  | 3700   | 8800   | -                  | -     | -     | -      | -      |      |

|                                                              |                                                          |                                                                  | 3.6 V           | 625   | 840   | 1950  | 4950   | 11500  | -                  | -     | -     | -      | -      |      |

| I <sub>DD_ALL</sub><br>(wakeup from<br>Shutdown)             | Supply current<br>during wakeup<br>from Shutdown<br>mode | Wakeup clock is<br>MSI = 4 MHz.<br>See <sup>(3)</sup> .          | 3 V             | 1.00  | -     | -     | -      | -      | -                  | -     | -     | -      | -      | mA   |

~ . . . . . .... ....

1. Guaranteed by characterization results, unless otherwise specified.

2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in Table 41: Low-power mode wakeup timings.

#### Table 39. Current consumption in VBAT mode

| Symbol Parameter | Conditions      |                                        |                  | TYP   |       |       | MAX <sup>(1)</sup> |        |       |       |       | Unit   |        |    |

|------------------|-----------------|----------------------------------------|------------------|-------|-------|-------|--------------------|--------|-------|-------|-------|--------|--------|----|

| Cymbol           | Falameter       | -                                      | V <sub>BAT</sub> | 25 °C | 55 °C | 85 °C | 105 °C             | 125 °C | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C |    |

|                  |                 |                                        | 1.8 V            | 3.00  | -     | -     | -                  | -      | -     | -     | -     | -      | -      |    |

|                  | RTC disabled    | 2.4 V                                  | 4.00             | -     | -     | -     | -                  | -      | -     | -     | -     | -      |        |    |

|                  |                 | ain                                    | 3 V              | 5.00  | -     | -     | -                  | -      | -     | -     | -     | -      | -      |    |

|                  | Backup domain   |                                        | 3.6 V            | 11.0  | -     | -     | -                  | -      | -     | -     | -     | -      | -      | nA |

|                  | supply current  |                                        | 1.8 V            | 145   | 165   | 285   | 550                | -      | -     | -     | -     | -      | -      | ПА |

|                  | RTC enabled and | 2.4 V                                  | 205              | 235   | 370   | 670   | -                  | -      | -     | -     | -     | -      |        |    |

|                  |                 | clocked by LSE<br>bypassed at 32768 Hz | 3 V              | 285   | 315   | 470   | 820                | -      | -     | -     | -     | -      | -      |    |

|                  |                 | bypasse                                |                  | 3.6 V | 375   | 430   | 715                | 1350   | -     | -     | -     | -      | -      | -  |

1. Guaranteed by characterization results, unless otherwise specified.

DS11913 Rev 4

111/204

- 1. Guaranteed by design.

- Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- 3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

| Symbol                     | Parameter                                                                       | Conditions                      |                                | Min   | Тур     | Max   | Unit  |

|----------------------------|---------------------------------------------------------------------------------|---------------------------------|--------------------------------|-------|---------|-------|-------|

|                            |                                                                                 |                                 | Range 0                        | 98.7  | 100     | 101.3 | - kHz |

|                            |                                                                                 |                                 | Range 1                        | 197.4 | 200     | 202.6 |       |

|                            |                                                                                 |                                 | Range 2                        | 394.8 | 400     | 405.2 |       |

|                            |                                                                                 |                                 | Range 3                        | 789.6 | 800     | 810.4 |       |

|                            |                                                                                 |                                 | Range 4                        | 0.987 | 1       | 1.013 |       |

|                            |                                                                                 | MSI mode                        | Range 5                        | 1.974 | 2       | 2.026 |       |

|                            |                                                                                 | INISI mode                      | Range 6                        | 3.948 | 4       | 4.052 |       |

|                            |                                                                                 |                                 | Range 7                        | 7.896 | 8       | 8.104 | MHz   |

|                            |                                                                                 |                                 | Range 8                        | 15.79 | 16      | 16.21 |       |

|                            | MSI frequency after factory calibration, done at $V_{DD}$ =3 V and $T_A$ =30 °C |                                 | Range 9                        | 23.69 | 24      | 24.31 |       |

|                            |                                                                                 |                                 | Range 10                       | 31.58 | 32      | 32.42 |       |

| f                          |                                                                                 |                                 | Range 11                       | 47.38 | 48      | 48.62 |       |

| f <sub>MSI</sub>           |                                                                                 | PLL mode<br>XTAL=<br>32.768 kHz | Range 0                        | -     | 98.304  | -     | - kHz |

|                            |                                                                                 |                                 | Range 1                        | -     | 196.608 | -     |       |

|                            |                                                                                 |                                 | Range 2                        | -     | 393.216 | -     |       |

|                            |                                                                                 |                                 | Range 3                        | -     | 786.432 | -     |       |

|                            |                                                                                 |                                 | Range 4                        | -     | 1.016   | -     | MHz   |

|                            |                                                                                 |                                 | Range 5                        | -     | 1.999   | -     |       |

|                            |                                                                                 |                                 | Range 6                        | -     | 3.998   | -     |       |

|                            |                                                                                 |                                 | Range 7                        | -     | 7.995   | -     |       |

|                            |                                                                                 |                                 | Range 8                        | -     | 15.991  | -     |       |

|                            |                                                                                 |                                 | Range 9                        | -     | 23.986  | -     |       |

|                            |                                                                                 |                                 | Range 10                       | -     | 32.014  | -     |       |

|                            |                                                                                 |                                 | Range 11                       | -     | 48.005  | -     | 1     |

| (2)                        | MSI oscillator                                                                  |                                 | T <sub>A</sub> = -0 to 85 °C   | -3.5  | -       | 3     |       |

| $\Delta_{TEMP}(MSI)^{(2)}$ | frequency drift<br>over temperature                                             | MSI mode                        | T <sub>A</sub> = -40 to 125 °C | -8    | -       | 6     | %     |

| Table 49. MSI oscillator characteristic | s <sup>(1)</sup> |

|-----------------------------------------|------------------|

|-----------------------------------------|------------------|

| Symbol                                            | Parameter                                          |                                                             | Conditions                   |                                     | Min  | Тур  | Max   | Unit |

|---------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|------------------------------|-------------------------------------|------|------|-------|------|

| (100)(2)                                          |                                                    |                                                             | Denne 0 to 2                 | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -1.2 | -    | 0.5   |      |

|                                                   |                                                    |                                                             | Range 0 to 3                 | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.5 | -    | - 0.5 |      |

|                                                   | MSI oscillator<br>frequency drift                  |                                                             | Range 4 to 7                 | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -2.5 | -    | 0.7   | %    |

| $\Delta_{VDD}(MSI)^{(2)}$                         | over V <sub>DD</sub><br>(reference is 3 V)         | MSI mode                                                    |                              | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.8 | -    | - 0.7 | 70   |

|                                                   |                                                    |                                                             | Range 8 to 11                | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -5   | -    | - 1   |      |

|                                                   |                                                    |                                                             | Range o to TT                | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -1.6 | -    |       |      |

|                                                   | Frequency                                          |                                                             | T <sub>A</sub> = -40 to 85 ° | °C                                  | -    | 1    | 2     |      |

| ∆F <sub>SAMPLING</sub><br>(MSI) <sup>(2)(6)</sup> | variation in sampling mode <sup>(3)</sup>          | MSI mode                                                    | T <sub>A</sub> = -40 to 125  | 0°C                                 | -    | 2    | 4     | %    |

| P_USB                                             | Period jitter for<br>USB clock <sup>(4)</sup>      | riod jitter for PLL mode<br>B clock <sup>(4)</sup> Range 11 | for next<br>transition       | -                                   | -    | -    | 3.458 | 20   |

| Jitter(MSI) <sup>(6)</sup>                        |                                                    |                                                             | for paired transition        | -                                   | -    | -    | 3.916 | ns   |

| MT_USB                                            | Medium term jitter<br>for USB clock <sup>(5)</sup> | PLL mode<br>Range 11                                        | for next<br>transition       | -                                   | -    | -    | 2     |      |

| Jitter(MSI) <sup>(6)</sup>                        |                                                    |                                                             | for paired transition        | -                                   | -    | -    | 1     | ns   |

| CC jitter(MSI) <sup>(6)</sup>                     | RMS cycle-to-<br>cycle jitter                      | PLL mode R                                                  | ange 11                      | -                                   | -    | 60   | -     | ps   |

| P jitter(MSI) <sup>(6)</sup>                      | RMS Period jitter                                  | PLL mode R                                                  | ange 11                      | -                                   | -    | 50   | -     | ps   |

|                                                   |                                                    | Range 0                                                     |                              | -                                   | -    | 10   | 20    |      |

|                                                   |                                                    | Range 1                                                     |                              | -                                   | -    | 5    | 10    | - us |

| t <sub>SU</sub> (MSI) <sup>(6)</sup>              | MSI oscillator                                     | Range 2                                                     |                              | -                                   | -    | 4    | 8     |      |

| ISU(MOI)                                          | start-up time                                      | Range 3                                                     |                              | -                                   | -    | 3    | 7     |      |

|                                                   |                                                    | Range 4 to 7                                                | 7                            | -                                   | -    | 3    | 6     |      |

|                                                   |                                                    | Range 8 to 11                                               |                              | -                                   | -    | 2.5  | 6     |      |

| t <sub>STAB</sub> (MSI) <sup>(6)</sup>            | MSI oscillator<br>stabilization time               | PLL mode<br>ne Range 11                                     | 10 % of final frequency      | -                                   | -    | 0.25 | 0.5   |      |

|                                                   |                                                    |                                                             | 5 % of final<br>frequency    | -                                   | -    | 0.5  | 1.25  | ms   |

|                                                   |                                                    |                                                             |                              | -                                   | -    | -    | 2.5   |      |

| Table 49. MSI oscillator characteristics <sup>(1)</sup> ( | (continued) |

|-----------------------------------------------------------|-------------|

|-----------------------------------------------------------|-------------|

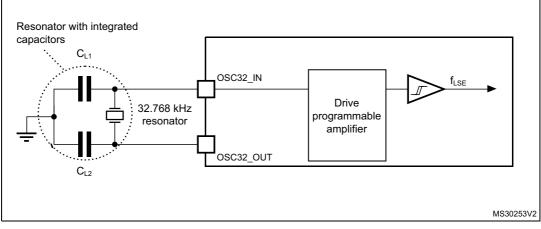

Figure 23. Typical current consumption versus MSI frequency

High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                   | Parameter                             | Parameter Conditions                                               |                   | Тур                  | Max                 | Unit |  |

|--------------------------|---------------------------------------|--------------------------------------------------------------------|-------------------|----------------------|---------------------|------|--|

| f <sub>HSI48</sub>       | HSI48 Frequency                       | V <sub>DD</sub> =3.0V, T <sub>A</sub> =30°C                        | -                 | 48                   | -                   | MHz  |  |

| TRIM                     | HSI48 user trimming step              | -                                                                  | -                 | 0.11 <sup>(2)</sup>  | 0.18 <sup>(2)</sup> | %    |  |

| USER TRIM<br>COVERAGE    | HSI48 user trimming coverage          | ±32 steps                                                          | ±3 <sup>(3)</sup> | ±3.5 <sup>(3)</sup>  | -                   | %    |  |

| DuCy(HSI48)              | Duty Cycle                            | -                                                                  | 45 <sup>(2)</sup> | -                    | 55 <sup>(2)</sup>   | %    |  |

| ACC <sub>HSI48_REL</sub> | Accuracy of the HSI48 oscillator      | V <sub>DD</sub> = 3.0 V to 3.6 V,<br>T <sub>A</sub> = -15 to 85 °C | -                 | -                    | ±3 <sup>(3)</sup>   | %    |  |

|                          | over temperature (factory calibrated) | $V_{DD}$ = 1.65 V to 3.6 V,<br>T <sub>A</sub> = -40 to 125 °C      | -                 | -                    | ±4.5 <sup>(3)</sup> |      |  |

|                          | HSI48 oscillator frequency drift      | V <sub>DD</sub> = 3 V to 3.6 V                                     | -                 | 0.025 <sup>(3)</sup> | 0.05 <sup>(3)</sup> | - %  |  |

| D <sub>VDD</sub> (HSI48) | with V <sub>DD</sub>                  | V <sub>DD</sub> = 1.65 V to 3.6 V                                  | -                 | 0.05 <sup>(3)</sup>  | 0.1 <sup>(3)</sup>  |      |  |

| t <sub>su</sub> (HSI48)  | HSI48 oscillator start-up time        | -                                                                  | -                 | 2.5 <sup>(2)</sup>   | 6 <sup>(2)</sup>    | μs   |  |

| I <sub>DD</sub> (HSI48)  | HSI48 oscillator power<br>consumption | -                                                                  | -                 | 340 <sup>(2)</sup>   | 380 <sup>(2)</sup>  | μA   |  |

- 2. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V.

- 3. Fast channels are: PC0, PC1, PC2, PC3, PA0, PA1.

- 4. Slow channels are: all ADC inputs except the fast channels.

| Symbol                  | Parameter                                                            | Con                                                                                                | ditions        | Min        | Тур        | Max   | Unit |

|-------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------|------------|------------|-------|------|

| CM                      |                                                                      | Normal mode                                                                                        |                | -          | 13         | -     |      |

| GM                      | Gain margin                                                          | Low-power mode                                                                                     | Low-power mode |            |            | -     | dB   |

| •                       | Wake up time                                                         | $\label{eq:loss} \textit{Vake up time} \mbox{om OFF state.} \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ |                | -          | 5          | 10    |      |

| <sup>t</sup> wakeup     | from OFF state.                                                      |                                                                                                    |                | -          | 10         | 30    | μs   |

| I <sub>bias</sub>       | OPAMP input<br>bias current                                          | General purpose in                                                                                 | put            | -          | -          | _(4)  | nA   |

|                         |                                                                      |                                                                                                    |                | -          | 2          | -     |      |

| PGA gain <sup>(3)</sup> | Non inverting<br>gain value                                          |                                                                                                    | -              | 4          | -          |       |      |

| PGA gain**              |                                                                      | -                                                                                                  |                | -          | 8          |       | -    |

|                         |                                                                      |                                                                                                    | -              | 16         | -          |       |      |

|                         | R2/R1 internal<br>resistance<br>values in PGA<br>mode <sup>(5)</sup> | PGA Gain = 2                                                                                       | -              | 80/80      | -          | κΩ/κΩ |      |

|                         |                                                                      | PGA Gain = 4                                                                                       | -              | 120/<br>40 | -          |       |      |

| R <sub>network</sub>    |                                                                      | PGA Gain = 8                                                                                       | -              | 140/<br>20 | -          |       |      |

|                         |                                                                      | PGA Gain = 16                                                                                      | -              | 150/<br>10 | -          |       |      |

| Delta R                 | Resistance<br>variation (R1 or<br>R2)                                |                                                                                                    | -15            | -          | 15         | %     |      |

| PGA gain error          | PGA gain error                                                       |                                                                                                    | -1             | -          | 1          | %     |      |

|                         | PGA bandwidth<br>for different non<br>inverting gain                 | Gain = 2                                                                                           | -              | -          | GBW/<br>2  | -     |      |

| PGA BW                  |                                                                      | Gain = 4                                                                                           | -              | -          | GBW/<br>4  | -     | MHz  |

| FGADW                   |                                                                      | Gain = 8 -                                                                                         |                | -          | GBW/<br>8  | -     |      |

|                         |                                                                      | Gain = 16                                                                                          | -              | -          | GBW/<br>16 | -     |      |

Table 76. OPAMP characteristics<sup>(1)</sup> (continued)

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

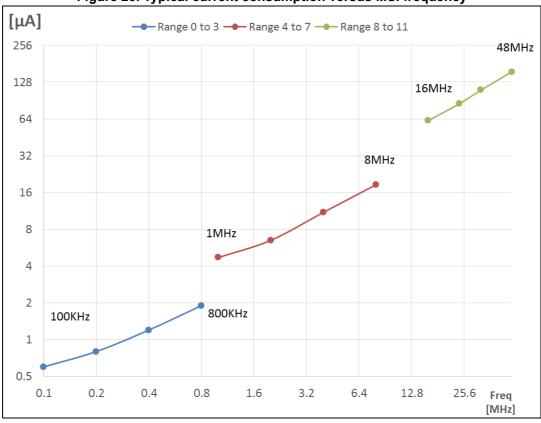

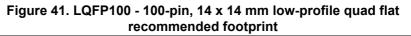

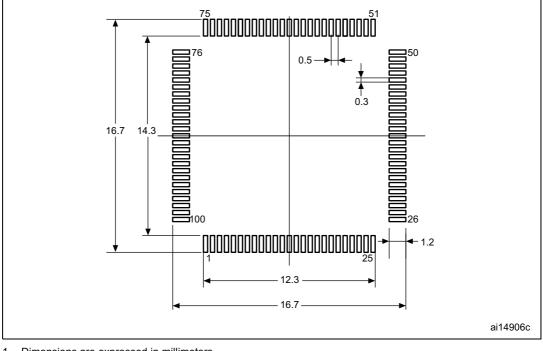

# 7.1 LQFP100 package information

Figure 40. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 91. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

| Symbol |                | millimeters |       | inches <sup>(1)</sup> |     |        |

|--------|----------------|-------------|-------|-----------------------|-----|--------|

| Symbol | Symbol Min Typ |             | Мах   | Min                   | Тур | Max    |

| А      | -              | -           | 1.600 | -                     | -   | 0.0630 |

| A1     | 0.050          | -           | 0.150 | 0.0020                | -   | 0.0059 |

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|--|

|        | Min         | Тур    | Max    | Min                   | Тур    | Мах    |  |  |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |  |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |  |

| E      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |  |

| k      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |  |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |  |

# Table 91. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.