Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | ARM® Cortex®-M4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                           |

| Number of I/O              | 83                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 160K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

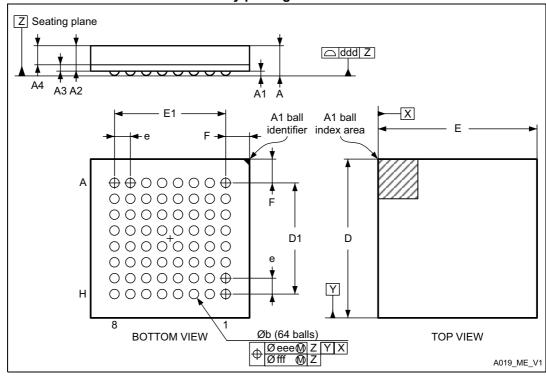

| Package / Case             | 100-UFBGA                                                                       |

| Supplier Device Package    | 100-UFBGA (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l462vei6           |

# List of tables

| Table 1.  | STM32L462xx family device features and peripheral counts                         | 14    |

|-----------|----------------------------------------------------------------------------------|-------|

| Table 2.  | Access status versus readout protection level and execution modes                |       |

| Table 3.  | STM32L462xx modes overview                                                       |       |

| Table 4.  | Functionalities depending on the working mode                                    |       |

| Table 5.  | STM32L462xx peripherals interconnect matrix                                      |       |

| Table 6.  | DMA implementation                                                               |       |

| Table 7.  | Temperature sensor calibration values                                            |       |

| Table 8.  | Internal voltage reference calibration values                                    |       |

| Table 9.  | DFSDM1 implementation                                                            |       |

| Table 10. | Timer feature comparison                                                         |       |

| Table 10. | I2C implementation                                                               |       |

| Table 11. | STM32L462xx USART/UART/LPUART features                                           |       |

| Table 12. |                                                                                  |       |

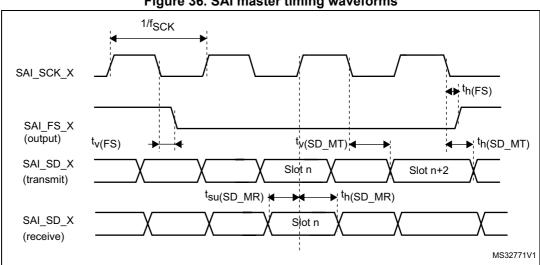

| Table 13. | SAI implementation.                                                              |       |

| Table 14. | Legend/abbreviations used in the pinout table                                    |       |

|           | STM32L462xx pin definitions                                                      |       |

| Table 16. | Alternate function AF0 to AF7                                                    |       |

| Table 17. | Alternate function AF8 to AF15                                                   |       |

| Table 18. | STM32L462xx memory map and peripheral register boundary addresses                |       |

| Table 19. | Voltage characteristics                                                          |       |

| Table 20. | Current characteristics                                                          |       |

| Table 21. | Thermal characteristics                                                          |       |

| Table 22. | General operating conditions                                                     |       |

| Table 23. | Operating conditions at power-up / power-down                                    |       |

| Table 24. | Embedded reset and power control block characteristics                           |       |

| Table 25. | Embedded internal voltage reference                                              | 96    |

| Table 26. | Current consumption in Run and Low-power run modes, code with data processing    |       |

|           | running from Flash, ART enable (Cache ON Prefetch OFF)                           | 99    |

| Table 27. | Current consumption in Run and Low-power run modes, code with data processing    |       |

|           | running from Flash, ART disable                                                  | . 100 |

| Table 28. | Current consumption in Run and Low-power run modes, code with data processing    |       |

|           | running from SRAM1                                                               | . 101 |

| Table 29. | Typical current consumption in Run and Low-power run modes, with different codes |       |

|           | running from Flash, ART enable (Cache ON Prefetch OFF)                           | . 102 |

| Table 30. | Typical current consumption in Run and Low-power run modes, with different codes |       |

|           | running from Flash, ART disable                                                  | . 103 |

| Table 31. | Typical current consumption in Run and Low-power run modes, with different codes |       |

|           | running from SRAM1                                                               |       |

| Table 32. | Current consumption in Sleep and Low-power sleep modes, Flash ON                 |       |

| Table 33. | Current consumption in Low-power sleep modes, Flash in power-down                |       |

| Table 34. | Current consumption in Stop 2 mode                                               |       |

| Table 35. | Current consumption in Stop 1 mode                                               |       |

| Table 36. | Current consumption in Stop 0                                                    |       |

| Table 37. | Current consumption in Standby mode                                              | . 109 |

| Table 38. | Current consumption in Shutdown mode                                             |       |

| Table 39. | Current consumption in VBAT mode                                                 |       |

| Table 40. | Peripheral current consumption                                                   | . 113 |

| Table 41. | Low-power mode wakeup timings                                                    | . 115 |

| Table 42. | Regulator modes transition times                                                 | . 117 |

By default, the microcontroller is in Run mode after a system or a power Reset. It is up to the user to select one of the low-power modes described below:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### • Low-power run mode

This mode is achieved with  $V_{CORE}$  supplied by the low-power regulator to minimize the regulator's operating current. The code can be executed from SRAM or from Flash, and the CPU frequency is limited to 2 MHz. The peripherals with independent clock can be clocked by HSI16.

#### • Low-power sleep mode

This mode is entered from the low-power run mode. Only the CPU clock is stopped. When wakeup is triggered by an event or an interrupt, the system reverts to the low-power run mode.

#### • Stop 0, Stop 1 and Stop 2 modes

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are disabled. The LSE or LSI is still running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals with wakeup capability can enable the HSI16 RC during Stop mode to detect their wakeup condition.

Three Stop modes are available: Stop 0, Stop 1 and Stop 2 modes. In Stop 2 mode, most of the  $V_{CORE}$  domain is put in a lower leakage mode.

Stop 1 offers the largest number of active peripherals and wakeup sources, a smaller wakeup time but a higher consumption than Stop 2. In Stop 0 mode, the main regulator remains ON, allowing a very fast wakeup time but with much higher consumption.

The system clock when exiting from Stop 0, Stop 1 or Stop 2 modes can be either MSI up to 48 MHz or HSI16, depending on software configuration.

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the  $V_{CORE}$  domain is powered off. The PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are also switched off.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The brown-out reset (BOR) always remains active in Standby mode.

The state of each I/O during standby mode can be selected by software: I/O with internal pull-up, internal pull-down or floating.

After entering Standby mode, SRAM1 and register contents are lost except for registers in the Backup domain and Standby circuitry. Optionally, SRAM2 can be retained in Standby mode, supplied by the low-power Regulator (Standby with SRAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

DS11913 Rev 4 27/204

The main features of the touch sensing controller are the following:

- Proven and robust surface charge transfer acquisition principle

- Supports up to 21 capacitive sensing channels

- Up to 3 capacitive sensing channels can be acquired in parallel offering a very good response time

- Spread spectrum feature to improve system robustness in noisy environments

- Full hardware management of the charge transfer acquisition sequence

- Programmable charge transfer frequency

- Programmable sampling capacitor I/O pin

- Programmable channel I/O pin

- Programmable max count value to avoid long acquisition when a channel is faulty

- Dedicated end of acquisition and max count error flags with interrupt capability

- One sampling capacitor for up to 3 capacitive sensing channels to reduce the system components

- Compatible with proximity, touchkey, linear and rotary touch sensor implementation

- Designed to operate with STMTouch touch sensing firmware library

Note: The number of capacitive sensing channels is dependent on the size of the packages and subject to I/O availability.

## 3.21 Digital filter for Sigma-Delta Modulators (DFSDM)

The device embeds one DFSDM with 2 digital filters modules and 4 external input serial channels (transceivers) or alternately 4 internal parallel inputs support.

The DFSDM peripheral is dedicated to interface the external  $\Sigma\Delta$  modulators to microcontroller and then to perform digital filtering of the received data streams (which represent analog value on  $\Sigma\Delta$  modulators inputs). DFSDM can also interface PDM (Pulse Density Modulation) microphones and perform PDM to PCM conversion and filtering in

DS11913 Rev 4

43/204

## 3.26 Inter-integrated circuit interface (I<sup>2</sup>C)

The device embeds four I2C. Refer to *Table 11: I2C implementation* for the features implementation.

The I<sup>2</sup>C bus interface handles communications between the microcontroller and the serial I<sup>2</sup>C bus. It controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing.

#### The I2C peripheral supports:

- I<sup>2</sup>C-bus specification and user manual rev. 5 compatibility:

- Slave and master modes, multimaster capability

- Standard-mode (Sm), with a bitrate up to 100 kbit/s

- Fast-mode (Fm), with a bitrate up to 400 kbit/s

- Fast-mode Plus (Fm+), with a bitrate up to 1 Mbit/s and 20 mA output drive I/Os

- 7-bit and 10-bit addressing mode, multiple 7-bit slave addresses

- Programmable setup and hold times

- Optional clock stretching

- System Management Bus (SMBus) specification rev 2.0 compatibility:

- Hardware PEC (Packet Error Checking) generation and verification with ACK control

- Address resolution protocol (ARP) support

- SMBus alert

- Power System Management Protocol (PMBus<sup>TM</sup>) specification rev 1.1 compatibility

- Independent clock: a choice of independent clock sources allowing the I2C communication speed to be independent from the PCLK reprogramming. Refer to Figure 4: Clock tree.

- Wakeup from Stop mode on address match

- Programmable analog and digital noise filters

- 1-byte buffer with DMA capability

**Table 11. I2C implementation**

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 | I2C3 | I2C4 |

|-------------------------------------------------------------|------|------|------|------|

| Standard-mode (up to 100 kbit/s)                            | Χ    | X    | X    | X    |

| Fast-mode (up to 400 kbit/s)                                | Х    | Х    | Х    | Х    |

| Fast-mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    | Х    | Х    |

| Programmable analog and digital noise filters               | Х    | Х    | Х    | Х    |

| SMBus/PMBus hardware support                                | Х    | Х    | Х    | Х    |

| Independent clock                                           | Х    | Х    | Х    | Х    |

| Wakeup from Stop 1 mode on address match                    | Х    | Х    | Х    | Х    |

| Wakeup from Stop 2 mode on address match                    | -    | -    | Х    | -    |

1. X: supported

- 2. The related I/O structures in *Table 15* are: FT\_u, FT\_fu.

- 3. The related I/O structures in *Table 15* are: FT\_a, FT\_fa, TT\_a.

Table 15. STM32L462xx pin definitions

|          | F       | Pin I  | Numl    | ber     |          |                                          |          |               |            | Pin fund                                                                   | ctions                               |

|----------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|------------|----------------------------------------------------------------------------|--------------------------------------|

| UFQFPN48 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes      | Alternate functions                                                        | Additional functions                 |

| -        | -       | -      | -       | 1       | B2       | PE2                                      | I/O      | FT            | -          | TRACECK, TIM3_ETR,<br>TSC_G7_IO1,<br>SAI1_MCLK_A,<br>EVENTOUT              | -                                    |

| -        | -       | -      | -       | 2       | A1       | PE3                                      | I/O      | FT            | -          | TRACED0, TIM3_CH1,<br>TSC_G7_IO2, SAI1_SD_B,<br>EVENTOUT                   | -                                    |

| -        | -       | -      | 1       | 3       | B1       | PE4                                      | I/O      | FT            | -          | TRACED1, TIM3_CH2,<br>DFSDM1_DATIN3,<br>TSC_G7_IO3, SAI1_FS_A,<br>EVENTOUT | -                                    |

| -        | -       | -      | -       | 4       | C2       | PE5                                      | I/O      | FT            | -          | TRACED2, TIM3_CH3,<br>DFSDM1_CKIN3,<br>TSC_G7_IO4,<br>SAI1_SCK_A, EVENTOUT | -                                    |

| -        | -       | -      | -       | 5       | D2       | PE6                                      | I/O      | FT            | -          | TRACED3, TIM3_CH4,<br>SAI1_SD_A, EVENTOUT                                  | RTC_TAMP3, WKUP3                     |

| 1        | В7      | 1      | B2      | 6       | E2       | VBAT                                     | S        | -             | -          | -                                                                          | -                                    |

| 2        | В8      | 2      | A2      | 7       | C1       | PC13                                     | I/O      | FT            | (1)<br>(2) | EVENTOUT                                                                   | RTC_TAMP1, RTC_TS,<br>RTC_OUT, WKUP2 |

| 3        | C8      | 3      | A1      | 8       | D1       | PC14-<br>OSC32_<br>IN<br>(PC14)          | I/O      | FT            | (1)<br>(2) | EVENTOUT                                                                   | OSC32_IN                             |

| 4        | C7      | 4      | B1      | 9       | E1       | PC15-<br>OSC32_<br>OUT<br>(PC15)         | I/O      | FT            | (1)<br>(2) | EVENTOUT                                                                   | OSC32_OUT                            |

| -        | -       | -      | -       | 10      | F2       | VSS                                      | S        | -             | -          | -                                                                          | -                                    |

| -        | -       | -      | -       | 11      | G2       | VDD                                      | S        | -             | -          | -                                                                          | -                                    |

| 5        | D8      | 5      | C1      | 12      | F1       | PH0-<br>OSC_IN<br>(PH0)                  | I/O      | FT            | -          | EVENTOUT                                                                   | OSC_IN                               |

| 6        | E8      | 6      | D1      | 13      | G1       | PH1-<br>OSC_<br>OUT<br>(PH1)             | I/O      | FT            | -          | EVENTOUT                                                                   | OSC_OUT                              |

Table 15. STM32L462xx pin definitions (continued)

|          | ı       | Pin I  | Numl    | ber     |          | Din nome                                 |          | 0             |       | Pin fund                                                                                                          | ctions               |

|----------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------|----------------------|

| UFQFPN48 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                               | Additional functions |

| -        | C4      | 54     | B5      | 83      | C8       | PD2                                      | I/O      | FT            | ı     | TRACED2, TIM3_ETR, USART3_RTS_DE, TSC_SYNC, SDMMC1_CMD, EVENTOUT                                                  | -                    |

| -        | -       | -      | -       | 84      | В8       | PD3                                      | I/O      | FT            | ı     | SPI2_MISO, DFSDM1_DATIN0, USART2_CTS, QUADSPI_BK2_NCS, EVENTOUT                                                   | -                    |

| -        | -       | -      | -       | 85      | В7       | PD4                                      | I/O      | FT            | ı     | SPI2_MOSI, DFSDM1_CKIN0, USART2_RTS_DE, QUADSPI_BK2_IO0, EVENTOUT                                                 | -                    |

| -        | -       | -      | -       | 86      | A6       | PD5                                      | I/O      | FT            | 1     | USART2_TX,<br>QUADSPI_BK2_IO1,<br>EVENTOUT                                                                        | -                    |

| -        | -       | -      | -       | 87      | В6       | PD6                                      | I/O      | FT            | ı     | DFSDM1_DATIN1,<br>USART2_RX,<br>QUADSPI_BK2_IO2,<br>SAI1_SD_A, EVENTOUT                                           | -                    |

| -        | -       | -      | -       | 88      | A5       | PD7                                      | I/O      | FT            | ı     | DFSDM1_CKIN1,<br>USART2_CK,<br>QUADSPI_BK2_IO3,<br>EVENTOUT                                                       | -                    |

| 39       | B4      | 55     | A5      | 89      | A8       | PB3<br>(JTDO/<br>TRACE<br>SWO)           | I/O      | FT_a          | (3)   | JTDO/TRACESWO,<br>TIM2_CH2, SPI1_SCK,<br>SPI3_SCK,<br>USART1_RTS_DE,<br>SAI1_SCK_B, EVENTOUT                      | COMP2_INM            |

| 40       | A4      | 56     | A4      | 90      | A7       | PB4<br>(NJTRST)                          | I/O      | FT_fa         | (3)   | NJTRST, TIM3_CH1,<br>I2C3_SDA, SPI1_MISO,<br>SPI3_MISO,<br>USART1_CTS,<br>TSC_G2_IO1,<br>SAI1_MCLK_B,<br>EVENTOUT | COMP2_INP            |

Table 18. STM32L462xx memory map and peripheral register boundary addresses<sup>(1)</sup> (continued)

| Bus     | Boundary address          | Size(bytes) | Peripheral |

|---------|---------------------------|-------------|------------|

|         | 0x4000 9800 - 0x4000 FFFF | 26 KB       | Reserved   |

|         | 0x4000 9400 - 0x4000 97FF | 1 KB        | LPTIM2     |

|         | 0x4000 8800 - 0x4000 93FF | 3 KB        | Reserved   |

|         | 0x4000 8400 - 0x4000 87FF | 1 KB        | I2C4       |

|         | 0x4000 8000 - 0x4000 83FF | 1 KB        | LPUART1    |

|         | 0x4000 7C00 - 0x4000 7FFF | 1 KB        | LPTIM1     |

|         | 0x4000 7800 - 0x4000 7BFF | 1 KB        | OPAMP      |

|         | 0x4000 7400 - 0x4000 77FF | 1 KB        | DAC1       |

|         | 0x4000 7000 - 0x4000 73FF | 1 KB        | PWR        |

|         | 0x4000 6C00 - 0x4000 6FFF | 1 KB        | USB SRAM   |

|         | 0x4000 6800 - 0x4000 6BFF | 1 KB        | USB FS     |

|         | 0x4000 6400 - 0x4000 67FF | 1 KB        | CAN1       |

| A DD4   | 0x4000 6000 - 0x4000 63FF | 1 KB        | CRS        |

| APB1    | 0x4000 5C00- 0x4000 5FFF  | 1 KB        | I2C3       |

|         | 0x4000 5800 - 0x4000 5BFF | 1 KB        | I2C2       |

|         | 0x4000 5400 - 0x4000 57FF | 1 KB        | I2C1       |

|         | 0x4000 5000 - 0x4000 53FF | 1 KB        | Reserved   |

|         | 0x4000 4C00 - 0x4000 4FFF | 1 KB        | UART4      |

|         | 0x4000 4800 - 0x4000 4BFF | 1 KB        | USART3     |

|         | 0x4000 4400 - 0x4000 47FF | 1 KB        | USART2     |

|         | 0x4000 4000 - 0x4000 43FF | 1 KB        | Reserved   |

|         | 0x4000 3C00 - 0x4000 3FFF | 1 KB        | SPI3       |

|         | 0x4000 3800 - 0x4000 3BFF | 1 KB        | SPI2       |

|         | 0x4000 3400 - 0x4000 37FF | 1 KB        | Reserved   |

|         | 0x4000 3000 - 0x4000 33FF | 1 KB        | IWDG       |

|         | 0x4000 2C00 - 0x4000 2FFF | 1 KB        | WWDG       |

|         | 0x4000 2800 - 0x4000 2BFF | 1 KB        | RTC        |

|         | 0x4000 1400 - 0x4000 27FF | 5 KB        | Reserved   |

| A D D 4 | 0x4000 1000 - 0x4000 13FF | 1 KB        | TIM6       |

| APB1    | 0x4000 0800- 0x4000 0FFF  | 2 KB        | Reserved   |

|         | 0x4000 0400 - 0x4000 07FF | 1 KB        | TIM3       |

|         | 0x4000 0000 - 0x4000 03FF | 1 KB        | TIM2       |

<sup>1.</sup> The gray color is used for reserved boundary addresses.

Table 30. Typical current consumption in Run and Low-power run modes, with different codes running from Flash, ART disable

|                                |                         | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Conditio                          | ins                         | TYP   |      | TYP   |        |

|--------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------|-------|------|-------|--------|

| Symbol                         | Parameter               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Voltage scaling                   | Code                        | 25 °C | Unit | 25 °C | Unit   |

|                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Z                                 | Reduced code <sup>(1)</sup> | 2.75  |      | 106   |        |

| Supply Current in              |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Range 2<br>LK = 26 MHz            | Coremark                    | 2.50  |      | 96    |        |

|                                |                         | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ange<br>= 2(                      | Dhrystone 2.1               | 2.50  | mA   | 96    | μA/MHz |

|                                |                         | 48 MHz included,<br>bypass mode<br>ent in PLL ON above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ra<br>fHCLK                       | Fibonacci                   | 2.30  |      | 88    |        |

|                                | Supply<br>current in    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ť                                 | While(1)                    | 2.20  |      | 84.6  |        |

| (Rūn)                          | Run mode                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Range 1<br><sub>-K</sub> = 80 MHz | Reduced code <sup>(1)</sup> | 8.85  |      | 111   |        |

|                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   | Coremark                    | 8.15  |      | 102   |        |

|                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   | Dhrystone 2.1               | 8.15  | mA   | 102   | μA/MHz |

|                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ra<br>fHCLK                       | Fibonacci                   | 7.55  |      | 94    |        |

|                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ξ                                 | While(1)                    | 7.95  |      | 99    |        |

|                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   | Reduced code <sup>(1)</sup> | 340   |      | 170   |        |

|                                | Supply                  | f -f -2 MI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J                                 | Coremark                    | 380   |      | 190   | μΑ/MHz |

| I <sub>DD_ALL</sub><br>(LPRun) | current in<br>Low-power | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 MI<br>all peripherals disa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   | Dhrystone 2.1               | 355   | μΑ   | 178   |        |

| (=: : (4)                      | run                     | p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p p |                                   | Fibonacci                   | 355   |      | 178   |        |

|                                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   | While(1)                    | 405   |      | 203   |        |

<sup>1.</sup> Reduced code used for characterization results provided in *Table 26*, *Table 27*, *Table 28*.

Table 31. Typical current consumption in Run and Low-power run modes, with different codes running from SRAM1

|                                |                      |                                                                                         | Conditio                              | ons                         | TYP      |      | TYP   |        |     |        |        |     |       |        |    |           |      |  |    |

|--------------------------------|----------------------|-----------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|----------|------|-------|--------|-----|--------|--------|-----|-------|--------|----|-----------|------|--|----|

| Symbol                         | Parameter            | -                                                                                       | Voltage scaling                       | Code                        | 25 °C    | Unit | 25 °C | Unit   |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      |                                                                                         | HZ                                    | Reduced code <sup>(1)</sup> | 2.40     |      | 92    |        |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      |                                                                                         | Range 2<br><sub>LK</sub> = 26 MHz     | Coremark                    | 2.20     |      | 85    |        |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                                              | ange<br>= 26                          | Dhrystone 2.1               | 2.35     | mA   | 90    | μΑ/MHz |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      | 48 MHz included,<br>bypass mode<br>PLL ON above<br>48 MHz all<br>peripherals<br>disable | Ranç<br>f <sub>HCLK</sub> =           | Fibonacci                   | 2.20     |      | 85    |        |     |        |        |     |       |        |    |           |      |  |    |

| I <sub>DD_ALL</sub>            | Supply current in    |                                                                                         | f.                                    | While(1)                    | 2.30     |      | 88    |        |     |        |        |     |       |        |    |           |      |  |    |

| (Run)                          | Run mode             |                                                                                         | Range 1<br>f <sub>HCLK</sub> = 80 MHz | Reduced code <sup>(1)</sup> | 8.55     |      | 107   |        |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      |                                                                                         |                                       | Coremark                    | 7.75     |      | 97    |        |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      |                                                                                         |                                       | Dhrystone 2.1               | 8.45     | mA   | 106   | µA/MHz |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      |                                                                                         |                                       | R 7.                        | R.<br>X. | , X  | 2 2 Z | R 및    | 쪘 爿 | 훘<br>기 | R. Alc | Z X | CLK R | CLK RR | R. | Fibonacci | 7.80 |  | 98 |

|                                |                      |                                                                                         | Ť,                                    | While(1)                    | 8.75     |      | 109   |        |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      |                                                                                         |                                       | Reduced code <sup>(1)</sup> | 220      |      | 110   |        |     |        |        |     |       |        |    |           |      |  |    |

|                                | Supply               | f -f -0.MI                                                                              | ı_                                    | Coremark                    | 190      |      | 95    |        |     |        |        |     |       |        |    |           |      |  |    |

| I <sub>DD_ALL</sub><br>(LPRun) | current in Low-power | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 MH<br>  all peripherals disa                   |                                       | Dhrystone 2.1               | 215      | μΑ   | 108   | μΑ/MHz |     |        |        |     |       |        |    |           |      |  |    |

| (El rail)                      | run                  | an penpherale alea                                                                      | <b></b>                               | Fibonacci                   | 200      |      | 100   |        |     |        |        |     |       |        |    |           |      |  |    |

|                                |                      |                                                                                         |                                       | While(1)                    | 210      |      | 105   |        |     |        |        |     |       |        |    |           |      |  |    |

<sup>1.</sup> Reduced code used for characterization results provided in *Table 26*, *Table 27*, *Table 28*.

DS11913 Rev 4 103/204

Electrical characteristics

Table 32. Current consumption in Sleep and Low-power sleep modes, Flash ON

|                     |                    | Cond                                                 | ditions         |         |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |        |        |

|---------------------|--------------------|------------------------------------------------------|-----------------|---------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|--------|

| Symbol              | Parameter          | -                                                    | Voltage scaling |         |       | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | Unit   |

|                     |                    |                                                      |                 | 26 MHz  | 0.700 | 0.730 | 0.830 | 1.00   | 1.35   | 0.80  | 0.90  | 1.05               | 1.30   | 1.90   |        |

|                     |                    |                                                      |                 | 16 MHz  | 0.475 | 0.505 | 0.605 | 0.775  | 1.10   | 0.55  | 0.65  | 0.80               | 1.05   | 1.65   |        |

|                     |                    |                                                      |                 | 8 MHz   | 0.300 | 0.325 | 0.425 | 0.590  | 0.920  | 0.35  | 0.45  | 0.60               | 0.85   | 1.45   |        |

|                     |                    |                                                      | Range 2         | 4 MHz   | 0.210 | 0.235 | 0.335 | 0.500  | 0.830  | 0.25  | 0.30  | 0.45               | 0.75   | 1.35   |        |

|                     |                    | f <sub>HCLK</sub> = f <sub>HSE</sub> up<br>to 48 MHz |                 | 2 MHz   | 0.165 | 0.190 | 0.290 | 0.455  | 0.785  | 0.20  | 0.25  | 0.40               | 0.70   | 1.25   |        |

|                     | Supply             | included, bypass<br>mode<br>pll ON above             |                 | 1 MHz   | 0.145 | 0.170 | 0.265 | 0.430  | 0.760  | 0.15  | 0.25  | 0.40               | 0.65   | 1.25   |        |

| I <sub>DD_ALL</sub> | current in         |                                                      |                 | 100 kHz | 0.125 | 0.150 | 0.245 | 0.410  | 0.740  | 0.15  | 0.20  | 0.35               | 0.65   | 1.20   | mA     |

| (Sleep)             | sleep              |                                                      | 8 MHz all       | 80 MHz  | 2.30  | 2.35  | 2.45  | 2.65   | 3.05   | 2.55  | 2.65  | 2.85               | 3.15   | 3.80   | ] '''' |

|                     | mode,              | peripherals                                          |                 | 72 MHz  | 2.10  | 2.15  | 2.25  | 2.45   | 2.80   | 2.35  | 2.40  | 2.60               | 2.90   | 3.55   |        |

|                     |                    | disable                                              |                 | 64 MHz  | 1.90  | 1.90  | 2.05  | 2.25   | 2.60   | 2.10  | 2.20  | 2.35               | 2.70   | 3.35   |        |

|                     |                    |                                                      | Range 1         | 48 MHz  | 1.40  | 1.40  | 1.55  | 1.75   | 2.15   | 1.60  | 1.65  | 1.85               | 2.15   | 2.80   |        |

|                     |                    |                                                      |                 | 32 MHz  | 0.970 | 1.00  | 1.15  | 1.30   | 1.70   | 1.10  | 1.20  | 1.40               | 1.70   | 2.35   |        |

|                     |                    |                                                      |                 | 24 MHz  | 0.765 | 0.800 | 0.920 | 1.10   | 1.50   | 0.90  | 0.95  | 1.15               | 1.45   | 2.10   |        |

|                     |                    |                                                      |                 | 16 MHz  | 0.555 | 0.590 | 0.705 | 0.895  | 1.25   | 0.65  | 0.75  | 0.90               | 1.20   | 1.85   |        |

|                     | Supply             |                                                      |                 | 2 MHz   | 76.0  | 110   | 215   | 395    | 745    | 120   | 185   | 355                | 610    | 1250   |        |

| I <sub>DD ALL</sub> | current in         | f <sub>HCLK</sub> = f <sub>MSI</sub>                 |                 | 1 MHz   | 54.0  | 86.5  | 195   | 370    | 725    | 88.5  | 160   | 335                | 585    | 1250   | μA     |

| (LPSleep)           | low-power<br>sleep | all peripherals dis                                  | able            | 400 kHz | 39.0  | 70.5  | 175   | 355    | 710    | 68.5  | 140   | 320                | 570    | 1200   | μΛ     |

|                     | mode               |                                                      |                 | 100 kHz | 35.5  | 75.0  | 195   | 345    | 715    | 66.0  | 130   | 305                | 560    | 1200   |        |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 60: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

#### Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 40: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{\mbox{\scriptsize SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

C<sub>S</sub> is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

Table 40. Peripheral current consumption (continued)

|      | Peripheral                       | Range 1 | Range 2 | Low-power run and sleep | Unit   |

|------|----------------------------------|---------|---------|-------------------------|--------|

|      | DAC1                             | 2.4     | 1.8     | 2.2                     |        |

|      | RTCA                             | 1.7     | 1.1     | 2.1                     |        |

|      | CRS                              | 0.3     | 0.3     | 0.6                     |        |

|      | USB FS independent clock domain  | 2.9     | N/A     | N/A                     |        |

|      | USB FS clock domain              | 2.3     | N/A     | N/A                     |        |

|      | I2C1 independent clock domain    | 3.5     | 2.8     | 3.4                     |        |

|      | I2C1 clock domain                | 1.1     | 0.9     | 1.0                     |        |

|      | I2C2 independent clock domain    | 3.5     | 3.0     | 3.4                     |        |

|      | I2C2 clock domain                | 1.1     | 0.7     | 0.9                     |        |

|      | I2C3 independent clock domain    | 2.9     | 2.3     | 2.5                     |        |

|      | I2C3 clock domain                | 0.9     | 0.4     | 0.8                     |        |

|      | LPUART1 independent clock domain | 1.9     | 1.6     | 1.8                     |        |

|      | LPUART1 clock domain             | 0.6     | 0.6     | 0.6                     |        |

|      | LPTIM1 independent clock domain  | 2.9     | 2.4     | 2.8                     |        |

| APB1 | LPTIM1 clock domain              | 0.8     | 0.4     | 0.7                     | μΑ/MHz |

|      | LPTIM2 independent clock domain  | 3.1     | 2.7     | 3.9                     |        |

|      | LPTIM2 clock domain              | 0.8     | 0.7     | 0.8                     |        |

|      | OPAMP                            | 0.4     | 0.2     | 0.4                     |        |

|      | PWR                              | 0.4     | 0.1     | 0.4                     |        |

|      | SPI2                             | 1.8     | 1.6     | 1.6                     |        |

|      | SPI3                             | 1.7     | 1.3     | 1.6                     |        |

|      | TIM2                             | 6.2     | 5.0     | 5.9                     |        |

|      | TIM6                             | 1.0     | 0.6     | 0.9                     |        |

|      | USART2 independent clock domain  | 4.1     | 3.6     | 3.8                     |        |

|      | USART2 clock domain              | 1.3     | 0.9     | 1.1                     |        |

|      | USART3 independent clock domain  | 4.3     | 3.5     | 4.2                     |        |

|      | USART3 clock domain              | 1.5     | 1.1     | 1.3                     |        |

|      | WWDG                             | 0.5     | 0.5     | 0.5                     |        |

|      | All APB1 on                      | 51.5    | 35.5    | 48.6                    |        |

| Symbol                               | Parameter            |                     | Conditions |   |   |      | Max | Unit |

|--------------------------------------|----------------------|---------------------|------------|---|---|------|-----|------|

|                                      |                      |                     | Range 0    | - | - | 0.6  | 1   |      |

|                                      |                      |                     | Range 1    | - | - | 0.8  | 1.2 |      |

|                                      |                      |                     | Range 2    | - | - | 1.2  | 1.7 | ]    |

|                                      |                      |                     | Range 3    | - | - | 1.9  | 2.5 | 1    |

|                                      |                      |                     | Range 4    | - | - | 4.7  | 6   | 1    |

| (MACI)(6)                            | MSI oscillator       | MSI and<br>PLL mode | Range 5    | - | - | 6.5  | 9   | μΑ   |

| I <sub>DD</sub> (MSI) <sup>(6)</sup> | power<br>consumption |                     | Range 6    | - | - | 11   | 15  |      |

|                                      |                      |                     | Range 7    | - | - | 18.5 | 25  |      |

|                                      |                      |                     | Range 8    | - | - | 62   | 80  |      |

|                                      |                      |                     | Range 9    | - | - | 85   | 110 |      |

|                                      |                      |                     | Range 10   | - | - | 110  | 130 |      |

|                                      |                      |                     | Range 11   | - | - | 155  | 190 | 1    |

Table 49. MSI oscillator characteristics<sup>(1)</sup> (continued)

6. Guaranteed by design.

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> This is a deviation for an individual part once the initial frequency has been measured.

<sup>3.</sup> Sampling mode means Low-power run/Low-power sleep modes with Temperature sensor disable.

Average period of MSI @48 MHz is compared to a real 48 MHz clock over 28 cycles. It includes frequency tolerance + jitter of MSI @48 MHz clock.

<sup>5.</sup> Only accumulated jitter of MSI @48 MHz is extracted over 28 cycles. For next transition: min. and max. jitter of 2 consecutive frame of 28 cycles of the MSI @48 MHz, for 1000 captures over 28 cycles. For paired transitions: min. and max. jitter of 2 consecutive frame of 56 cycles of the MSI @48 MHz, for 1000 captures over 56 cycles.

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                                           | Monitored frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |  |

|------------------|------------|------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------|------|--|

|                  |            |                                                                                                      |                          | 8 MHz/ 80 MHz                                     |      |  |

|                  |            | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25 °C,<br>LQFP100 package<br>compliant with IEC<br>61967-2 | 0.1 MHz to 30 MHz        | -8                                                |      |  |

|                  |            |                                                                                                      | 30 MHz to 130 MHz        | 2                                                 | dBµV |  |

| S <sub>EMI</sub> | Peak level |                                                                                                      | 130 MHz to 1 GHz         | 5                                                 | αБμν |  |

|                  |            |                                                                                                      | 1 GHz to 2 GHz           | 8                                                 |      |  |

|                  |            |                                                                                                      | EMI Level                | 2.5                                               | -    |  |

Table 56. EMI characteristics

### 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                               | Conditions                                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |  |  |  |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------------|-------|---------------------------------|------|--|--|--|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESDA/JEDEC<br>JS-001 | 2     | 2000                            | V    |  |  |  |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C,<br>conforming to ANSI/ESD<br>STM5.3.1      | C3    | 250                             | v    |  |  |  |

Table 57. ESD absolute maximum ratings

1. Guaranteed by characterization results.

DS11913 Rev 4 133/204

Table 68. ADC accuracy - limited test conditions  $\mathbf{1}^{(1)(2)(3)}$

| Sym-<br>bol  | Parameter               | Table 68. ADC accura                                     | Min                                   | Тур                      | Max  | Unit |     |      |

|--------------|-------------------------|----------------------------------------------------------|---------------------------------------|--------------------------|------|------|-----|------|

|              |                         |                                                          | Single                                | Fast channel (max speed) | -    | 4    | 5   |      |

| ET           | Total                   |                                                          | ended                                 | Slow channel (max speed) | -    | 4    | 5   |      |

| E1           | unadjusted<br>error     |                                                          | Differential                          | Fast channel (max speed) | -    | 3.5  | 4.5 |      |

|              |                         |                                                          | Differential Slow channel (max speed) | -                        | 3.5  | 4.5  |     |      |

|              |                         |                                                          | Single Fast channel (max speed        | Fast channel (max speed) | -    | 1    | 2.5 |      |

| EO           | Offset                  |                                                          | ended                                 | Slow channel (max speed) | -    | 1    | 2.5 |      |

|              | error                   |                                                          | Differential                          | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

|              |                         |                                                          | Dillerential                          | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

|              |                         |                                                          | Single                                | Fast channel (max speed) | -    | 2.5  | 4.5 |      |

| EG           | Gain error              | E                                                        | ended                                 | Slow channel (max speed) | -    | 2.5  | 4.5 | LSB  |

| EG Gain enoi |                         | Fast channel (max speed)                                 | -                                     | 2.5                      | 3.5  | LSB  |     |      |

|              |                         |                                                          | Slow channel (max speed               | -                        | 2.5  | 3.5  |     |      |

|              |                         |                                                          | Single                                | Fast channel (max speed) | -    | 1    | 1.5 |      |

| ED lin       | Differential            |                                                          | ended                                 | Slow channel (max speed) | -    | 1    | 1.5 |      |

|              | linearity<br>error      | ADC clock frequency ≤ 80 MHz, Sampling rate ≤ 5.33 Msps, | Differential                          | Fast channel (max speed) | -    | 1    | 1.2 |      |

|              |                         |                                                          |                                       | Slow channel (max speed) | -    | 1    | 1.2 |      |

|              |                         | V <sub>DDA</sub> = VREF+ = 3 V,<br>ntegral<br>nearity    | Single<br>ended                       | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

| EL           | Integral                |                                                          |                                       | Slow channel (max speed) | -    | 1.5  | 2.5 | _    |

| EL           | error                   |                                                          | Differential                          | Fast channel (max speed) | -    | 1    | 2   |      |

|              |                         |                                                          |                                       | Slow channel (max speed) | -    | 1    | 2   |      |

|              |                         | Single                                                   | Single                                | Fast channel (max speed) | 10.4 | 10.5 | -   |      |

| ENOB         | Effective               |                                                          | ended                                 | Slow channel (max speed) | 10.4 | 10.5 | -   | bits |

| ENOB         | number of bits          |                                                          | Differential                          | Fast channel (max speed) | 10.8 | 10.9 | -   | DILS |

|              |                         |                                                          | Dillerential                          | Slow channel (max speed) | 10.8 | 10.9 | -   |      |

|              | Cianal to               |                                                          | Single                                | Fast channel (max speed) | 64.4 | 65   | -   |      |

| SINAD        | Signal-to-<br>noise and |                                                          | ended                                 | Slow channel (max speed) | 64.4 | 65   | -   |      |

| SINAD        | distortion ratio        |                                                          | Differential                          | Fast channel (max speed) | 66.8 | 67.4 | -   |      |

| rat          | Tallo                   |                                                          | Differential                          | Slow channel (max speed) | 66.8 | 67.4 | -   | 40   |

|              |                         |                                                          | Single                                | Fast channel (max speed) | 65   | 66   | -   | dB   |

| CNID         | Signal-to-              |                                                          | ended                                 | Slow channel (max speed) | 65   | 66   | -   |      |

| SNR          | noise ratio             |                                                          | Differential                          | Fast channel (max speed) | 67   | 68   | -   |      |

|              |                         |                                                          | Differential                          | Slow channel (max speed) | 67   | 68   | -   |      |

Table 69. ADC accuracy - limited test conditions  $2^{(1)(2)(3)}$  (continued)

| Sym-<br>bol | Parameter  | C                                                                                   | Min             | Тур                      | Max | Unit |     |    |

|-------------|------------|-------------------------------------------------------------------------------------|-----------------|--------------------------|-----|------|-----|----|

|             |            | Total harmonic distortion  ADC clock frequency ≤ 80 MHz, Sampling rate ≤ 5.33 Msps, | Single<br>ended | Fast channel (max speed) | -   | -74  | -65 |    |

| THD         | Total      |                                                                                     |                 | Slow channel (max speed) | 1   | -74  | -67 | dB |

|             | distortion |                                                                                     | Differential    | Fast channel (max speed) | 1   | -79  | -70 | uБ |

|             |            | 2 V ≤ V <sub>DDA</sub>                                                              | Dillerential    | Slow channel (max speed) | -   | -79  | -71 |    |

- 1. Guaranteed by design.

- 2. ADC DC accuracy values are measured after internal calibration.

- ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this

significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a

Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when  $V_{DDA}$  < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when  $V_{DDA}$  < 2.4 V). It is disable when  $V_{DDA} \ge 2.4$  V. No oversampling.

Table 71. ADC accuracy - limited test conditions  $4^{(1)(2)(3)}$

| Sym-<br>bol   | Parameter                    | (                                  | Min                      | Тур                      | Max  | Unit |     |      |

|---------------|------------------------------|------------------------------------|--------------------------|--------------------------|------|------|-----|------|

|               |                              |                                    | Single                   | Fast channel (max speed) | -    | 5    | 5.4 |      |

| ГТ            | Total                        |                                    | ended                    | Slow channel (max speed) | -    | 4    | 5   |      |

| ET            | unadjusted<br>error          |                                    | Differential             | Fast channel (max speed) | -    | 4    | 5   |      |

|               | Differential Slow channel (r | Slow channel (max speed)           | -                        | 3.5                      | 4.5  |      |     |      |

|               |                              | Single Fast channel (max speed)    | -                        | 2                        | 4    |      |     |      |

| EO            | Offset                       |                                    | ended                    | Slow channel (max speed) | -    | 2    | 4   |      |

|               | error                        |                                    | Differential             | Fast channel (max speed) | -    | 2    | 3.5 |      |

|               |                              |                                    | Differential             | Slow channel (max speed) | -    | 2    | 3.5 |      |

|               |                              |                                    | Single                   | Fast channel (max speed) | -    | 4    | 4.5 |      |

| FC            | Cain arrar                   |                                    | ended                    | Slow channel (max speed) | -    | 4    | 4.5 | LOD  |

| EG Gain error |                              | Differential                       | Fast channel (max speed) | -                        | 3    | 4    | LSB |      |

|               |                              |                                    | Slow channel (max speed  | -                        | 3    | 4    |     |      |

|               |                              |                                    | Single                   | Fast channel (max speed) | -    | 1    | 1.5 |      |

|               | Differential linearity       | rity ADC clock frequency ≤ 26 MHz, | ended                    | Slow channel (max speed) | -    | 1    | 1.5 |      |

|               | error                        |                                    | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |      |

|               |                              |                                    |                          | Slow channel (max speed) | -    | 1    | 1.2 |      |

|               |                              | earity                             | Single<br>ended          | Fast channel (max speed) | -    | 2.5  | 3   |      |

| EL            | Integral                     |                                    |                          | Slow channel (max speed) | -    | 2.5  | 3   |      |

|               | error                        |                                    | Differential             | Fast channel (max speed) | -    | 2    | 2.5 |      |

|               |                              |                                    |                          | Slow channel (max speed) | -    | 2    | 2.5 |      |

|               |                              | 5                                  | Single                   | Fast channel (max speed) | 10.2 | 10.5 | -   |      |

| ENOB          | Effective number of          |                                    | ended                    | Slow channel (max speed) | 10.2 | 10.5 | -   | bits |

| ENOB          | bits                         |                                    | Differential             | Fast channel (max speed) | 10.6 | 10.7 | -   | DILS |

|               |                              |                                    | Dillerential             | Slow channel (max speed) | 10.6 | 10.7 | -   |      |