Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | e200z0h                                                     |

| Core Size                  | 32-Bit Single-Core                                          |

| Speed                      | 64MHz                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, QSPI, SCI, SPI            |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                     |

| Number of I/O              | 136                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 64K x 8                                                     |

| RAM Size                   | 48K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | A/D 16x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 176-LQFP                                                    |

| Supplier Device Package    | 176-LQFP (24x24)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5606sf2clu6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1. MPC5606S family device comparison (continued)

| Feature                                                | MPC5602S    | MPC5604S                 | MPC5606S                                                     |

|--------------------------------------------------------|-------------|--------------------------|--------------------------------------------------------------|

| Real-Time Counter and<br>Autonomous Periodic Interrupt | Yes         | Yes                      | Yes                                                          |

| Periodic Interrupt Timer (PIT)                         |             | 4 ch, 32-bit             | 1                                                            |

| Software Watchdog Timer (SWT)                          |             | Yes                      |                                                              |

| System Timer Module (STM)                              |             | 4 ch, 32-bit             |                                                              |

| Timed I/O <sup>2</sup>                                 |             | 8 ch, 16-bit IC/OC       |                                                              |

|                                                        |             | 16 ch, 16-bit OPWM/IC/OC | 3                                                            |

| ADC <sup>4</sup>                                       |             | 16 channels, 10-bit      |                                                              |

| CAN (64 mailboxes)                                     | 1 × FlexCAN | 2 × FlexCAN              | 2 × FlexCAN                                                  |

| CAN sampler                                            |             | Yes                      |                                                              |

| SCI                                                    |             | 2 × LINFlex              |                                                              |

| SPI                                                    | 2 × DSPI    | 2 × DSPI                 | $3^5 \times \text{DSPI}$                                     |

| QuadSPI serial flash interface                         | No          | No                       | Yes                                                          |

| I <sup>2</sup> C                                       | 2           | 2                        | 4                                                            |

| GPIO                                                   | 105         | 105                      | 105 (144-pin package)<br>133 (176-pin package)               |

| Debug                                                  | Nexus 1     | Nexus 1                  | Nexus 2+ <sup>6</sup>                                        |

| Package                                                | 144 LQFP    | 144 LQFP                 | 144 LQFP <sup>7</sup><br>176 LQFP<br>208 MAPBGA <sup>8</sup> |

<sup>1</sup> Configuration is software-programmable.

<sup>2</sup> IC-Input Capture, OC-Output Compare, OPWM-Output Pulse Width Modulation.

<sup>3</sup> This functionality is split over two eMIOS blocks.

<sup>4</sup> Support for external multiplexer enabling up to 23 channels.

<sup>5</sup> QuadSPI serial Flash controller can be optionally used as a third DSPI.

<sup>6</sup> Nexus2+ available on 176 LQFP as alternate pin function and on 208 MAPBGA.

<sup>7</sup> Not all features are available simultaneously in 144 LQFP package option.

<sup>8</sup> The 208-pin package is not a production package; it is available in limited quantities for tool development only.

# 1.4 MPC5606S series blocks

### 1.4.1 Block diagram

Figure 1 shows a high-level block diagram of the MPC5606S series.

#### Overview

- Two-wire bi-directional serial bus for on-board communications

- Compatibility with I<sup>2</sup>C bus standard

- Multimaster operation

- Software-programmable for one of 256 different serial clock frequencies

- Software-selectable acknowledge bit

- Interrupt-driven, byte-by-byte data transfer

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus-busy detection

# 1.5.6 Interrupt Controller (INTC)

The INTC provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high-priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software-configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource cannot preempt each other.

Multiple processors can assert interrupt requests to each other through software-settable interrupt requests. These same software-settable interrupt requests also can be used to break the work involved in servicing an interrupt request into a high-priority portion and a low-priority portion. The high-priority portion is initiated by a peripheral interrupt request, but then the ISR asserts a software-settable interrupt request to finish the servicing in a lower priority ISR. Therefore these software-settable interrupt requests can be used instead of the peripheral ISR scheduling a task through the RTOS. The INTC provides the following features:

- Unique 9-bit vector for each of the possible 128 separate interrupt sources

- Eight software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority

- Modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources

- External NMI directly accessing the main core critical interrupt mechanism

- 32 external interrupts

# 1.5.7 QuadSPI serial flash controller

The QuadSPI module enables use of external serial flash memories supporting single, dual, and quad modes of operation. It features the following:

- Memory mapping of external serial flash memory

- Automatic serial flash read command generation by CPU, DMA, or DCU read access on AHB bus

- Supports single, dual, and quad serial flash read commands

- Flexible buffering scheme to maximize read bandwidth of serial flash

#### Overview

• Separate internal power domain applied to full SRAM block, 8 KB SRAM block during Standby modes to retain contents during low-power mode.

### 1.5.11 On-chip graphics SRAM

The MPC5606S microcontroller has 160 KB on-chip graphics SRAM with the following features:

- Usable as general purpose SRAM

- Typical SRAM access time: 0 wait-state for reads and 32-bit writes

- Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

### 1.5.12 Memory Protection Unit (MPU)

The MPU features the following:

- 12 region descriptors for per-master protection

- Start and end address defined with 32-byte granularity

- Overlapping regions supported

- Protection attributes can optionally include process ID

- Protection offered for three concurrent read ports

- Read and write attributes for all masters

- Execute and supervisor/user mode attributes for processor masters

# 1.5.13 Boot Assist Module (BAM)

The BAM is a block of read-only memory that is programmed once by Freescale. The BAM program is executed every time the MCU is started up or reset in normal mode. The BAM supports different modes of booting. They are:

- Booting from internal flash memory

- Serial boot loading (a program is downloaded into RAM via FlexCAN or LINFlex and then executed)

- Booting from external memory

Additionally the BAM:

- Enables and manages the transition of the MCU from reset to user code execution

- Configures device for serial bootload

- Enables multiple bootcode starting locations out of reset through implementation of search for valid Reset Configuration Halfword

# 1.5.14 Enhanced Modular Input/Output System (eMIOS)

MPC5606S microcontrollers have two eMIOS modules—one with 16 channels and one with eight—with input/output channels supporting a range of 16-bit input capture, output compare, and Pulse Width Modulation functions.

The modules are configurable and can implement 8-channel, 16-bit input capture/output compare or 16-channel, 16-bit output pulse width modulation/input compare/output compare. As many as five additional channels are configurable as modulus counters.

eMIOS other features include:

- Selectable clock source from main FMPLL, auxiliary FMPLL, external 4–16 MHz oscillator or 16 MHz internal RC oscillator

- Timed I/O channels with 16-bit counter resolution

- Buffered updates

- Support for shifted PWM outputs to minimize occurrence of concurrent edges

- MPC5606S includes a 32 KHz low-power external oscillator for slow execution, reduced power consumption, and Real Time Clock

- Dedicated internal 128 kHz RC oscillator for low-power mode operation and self wakeup

- ±10% accuracy across voltage and temperature (after factory trimming)

- Trimming registers to support improved accuracy with in-application calibration

- Dedicated 16 MHz internal RC oscillator

- Used as default clock source out of reset

- Provides a clock for rapid startup from low-power modes

- Provides a backup clock in the event of PLL or external oscillator clock failure

- Offers an independent clock source for the watchdog timer

- ±5% accuracy across voltage and temperature (after factory trimming)

- Trimming registers to support frequency adjustment with in-application calibration

### **1.5.20** Periodic Interrupt Timer module (PIT)

The PIT features the following:

- Four general-purpose interrupt timers

- As many as two dedicated interrupt timers for triggering ADC conversions

- 32-bit counter resolution

- Clocked by system clock frequency

- 32-bit counter for Real Time Interrupt, clocked from main external oscillator

# 1.5.21 Real Time Counter (RTC)

The RTC supports wakeup from low-power modes or Real Time Clock generation

- Configurable resolution for different timeout periods

- 1 s resolution for >1 hour period

- 1 ms resolution for 2 second period

- Selectable clock sources from external 32 KHz crystal, external 4–16 MHz crystal, internal 128 kHz RC oscillator, or divided internal 16 MHz RC oscillator

# 1.5.22 System Timer Module (STM)

The STM is a 32-bit timer designed to support commonly required system and application software timing functions. The STM includes a 32-bit up counter and four 32-bit compare channels with a separate interrupt source for each channel. The counter is driven by the system clock divided by an 8-bit prescale value (1 to 256).

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

# 1.5.23 Software Watchdog Timer (SWT)

The Watchdog features the following:

- Watchdog can be activated by software or enabled out of reset

- Supports normal or windowed mode

- Watchdog timer value writable once after reset

- Static debug

- Watchpoint messaging

- Ownership trace messaging

- Program trace messaging

- Real time read/write of any internally memory-mapped resources through JTAG pins

- Overrun control, which selects whether to stall before Nexus overruns or else keep executing and allow overwrite

of information

- Watchpoint triggering, watchpoint triggers program tracing

- Configured via the IEEE 1149.1 (JTAG) port

- Nexus Auxiliary port supported on the 176 LQFP and 208-pin BGA package FOR DEVELOPMENT ONLY

- Narrow Auxiliary Nexus port supporting support trace, with two MDO pins

- Wide Auxiliary Nexus port supporting higher bandwidth trace, with four MDO pins

# 2 Pinout and signal descriptions

# 2.1 144 LQFP package pinouts

This section shows the pinouts for the 144-pin LQFP packages.

#### CAUTION

Any pins labeled "NC" must not be connected to any external circuit.

| ŝ  |

|----|

| õõ |

| Port   | PCR      | Alternate                                    | Function                                  | Special               | Peripheral <sup>3</sup>         | I/O       | Pad               | RESET                |          | Pin number<br>144 LQFP 176 LQFP 208 MAP |            |  |

|--------|----------|----------------------------------------------|-------------------------------------------|-----------------------|---------------------------------|-----------|-------------------|----------------------|----------|-----------------------------------------|------------|--|

| pin    | register | function <sup>1</sup>                        | Function                                  | function <sup>2</sup> | Peripheral                      | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP | 176 LQFP                                | 208 MAPBGA |  |

| PC[10] | PCR[40]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[40]<br>—<br>SOUND<br>—               | ANS[10]               | SIUL<br>—<br>SGL<br>—           | I/O       | J                 | None,<br>None        | 60       | 76                                      | Т9         |  |

| PC[11] | PCR[41]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[41]<br>—<br>MA0<br>PCS2_1            | ANS[11]               | SIUL<br><br>ADC<br>DSPI_1       | I/O       | J                 | None,<br>None        | 59       | 75                                      | R9         |  |

| PC[12] | PCR[42]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[42]<br>—<br>MA1<br>PCS1_1            | ANS[12]               | SIUL<br><br>ADC<br>DSPI_1       | I/O       | J                 | None,<br>None        | 58       | 74                                      | P9         |  |

| PC[13] | PCR[43]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[43]<br>—<br>MA2<br>PCS0_1            | ANS[13]               | SIUL<br><br>ADC<br>DSPI_1       | I/O       | J                 | None,<br>None        | 57       | 73                                      | N9         |  |

| PC[14] | PCR[44]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[44]<br>—<br>—<br>—                   | ANS[14]<br>EXTAL32    | SIUL<br>—<br>—<br>—             | I/O       | J                 | None,<br>None        | 56       | 72                                      | T8         |  |

| PC[15] | PCR[45]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[45]<br>—<br>—<br>—                   | ANS[15]<br>XTAL32     | SIUL<br>—<br>—<br>—             | I/O       | J                 | None,<br>None        | 55       | 71                                      | R8         |  |

| PD[0]  | PCR[46]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[46]<br>M0C0M<br>SSD0_0<br>eMIOSB[23] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 73       | 89                                      | R16        |  |

| PD[1]  | PCR[47]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[47]<br>M0C0P<br>SSD0_1<br>eMIOSB[22] | —                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 74       | 90                                      | P16        |  |

Pinout and signal descriptions

Freescale Semiconductor

| Port  | PCR      | Alternate                                    | Function                                  | Special               | Peripheral <sup>3</sup>         | I/O       | Pad               | RESET                |          | Pin number |            |

|-------|----------|----------------------------------------------|-------------------------------------------|-----------------------|---------------------------------|-----------|-------------------|----------------------|----------|------------|------------|

| pin   | register | function <sup>1</sup>                        | Function                                  | function <sup>2</sup> | Peripheral*                     | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP | 176 LQFP   | 208 MAPBGA |

| PD[2] | PCR[48]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[48]<br>M0C1M<br>SSD0_2<br>eMIOSB[21] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 75       | 91         | P15        |

| PD[3] | PCR[49]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[49]<br>M0C1P<br>SSD0_3<br>eMIOSB[20] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 76       | 92         | N16        |

| PD[4] | PCR[50]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[50]<br>M1C0M<br>SSD1_0<br>eMIOSB[19] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 79       | 95         | N15        |

| PD[5] | PCR[51]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[51]<br>M1C0P<br>SSD1_1<br>eMIOSB[18] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 80       | 96         | M15        |

| PD[6] | PCR[52]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[52]<br>M1C1M<br>SSD1_2<br>eMIOSB[17] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 81       | 97         | M16        |

| PD[7] | PCR[53]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[53]<br>M1C1P<br>SSD1_3<br>eMIOSB[16] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 82       | 98         | K16        |

| PD[8] | PCR[54]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[54]<br>M2C0M<br>SSD2_0<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 83       | 99         | J16        |

| PD[9] | PCR[55]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[55]<br>M2C0P<br>SSD2_1<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 84       | 100        | K15        |

### Table 8. Port pin summary (continued)

MPC5606S Microcontroller Data Sheet, Rev. 8

39

Pinout and signal descriptions

| Port               | PCR      | Alternate                                    | Function                                     | Special               | Peripheral <sup>3</sup>               | I/O       | Pad               | RESET                |          | Pin number |            |

|--------------------|----------|----------------------------------------------|----------------------------------------------|-----------------------|---------------------------------------|-----------|-------------------|----------------------|----------|------------|------------|

| pin                | register | function <sup>1</sup>                        | Function                                     | function <sup>2</sup> | Peripheral                            | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP | 176 LQFP   | 208 MAPBGA |

| PG[8]              | PCR[94]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[94]<br>DCU_VSYNC<br>—                   | BP0                   | SIUL<br>DCU<br>—                      | I/O       | M2                | Input,<br>None       | 17       | 17         | J3         |

| PG[9]              | PCR[95]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[95]<br>DCU_HSYNC<br>—                   | BP1                   | SIUL<br>DCU<br>—                      | I/O       | M1                | Input,<br>None       | 18       | 18         | КЗ         |

| PG[10]             | PCR[96]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[96]<br>DCU_DE<br>—                      | BP2                   | SIUL<br>DCU<br>—                      | I/O       | M2                | None,<br>None        | 19       | 19         | J4         |

| PG[11]             | PCR[97]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[97]<br>DCU_PCLK<br>—                    | BP3                   | SIUL<br>DCU<br>—                      | I/O       | M1                | None,<br>None        | 20       | 20         | K4         |

| PG[12]             | PCR[98]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[98]<br>eMIOSA[23]<br>SOUND<br>eMIOSA[8] | FP30                  | SIUL<br>PWM/Timer<br>SGL<br>PWM/Timer | I/O       | S                 | None,<br>None        | 126      | 156        | D10        |

| PG[13]             | _        | _                                            | Reserved                                     | —                     | _                                     |           |                   | _                    | _        | —          | —          |

| PG[14]             | _        |                                              | Reserved                                     | —                     | —                                     | —         |                   | _                    |          | —          | —          |

| PG[15]             | —        | _                                            | Reserved                                     | —                     | —                                     | —         | _                 | —                    | —        | —          | —          |

| PH[0] <sup>7</sup> | PCR[99]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[99]<br>TCK<br>—<br>—                    | _                     | SIUL<br>JTAG<br>—                     | I/O       | S                 | Input,<br>Pullup     | 36       | 43         | R1         |

| PH[1] <sup>7</sup> | PCR[100] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[100]<br>TDI<br>—<br>—                   | _                     | SIUL<br>JTAG<br>—                     | I/O       | S                 | Input,<br>Pullup     | 33       | 36         | P2         |

Table 8. Port pin summary (continued)

MPC5606S Microcontroller Data Sheet, Rev. 8

45

Pinout and signal descriptions

| Port  | PCR      | Alternate                                    | Function                                     | Special               | Peripheral <sup>3</sup>               | I/O       | Pad               | RESET                |          | Pin number |            |

|-------|----------|----------------------------------------------|----------------------------------------------|-----------------------|---------------------------------------|-----------|-------------------|----------------------|----------|------------|------------|

| pin   | register | function <sup>1</sup>                        | Function                                     | function <sup>2</sup> | Peripheral*                           | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP | 176 LQFP   | 208 MAPBGA |

| PJ[1] | PCR[106] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[106]<br>PDI_HSYNC<br>—                  | _                     | SIUL<br>PDI<br>—                      | I/O       | S                 | None,<br>None        | _        | 120        | A3         |

| PJ[2] | PCR[107] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[107]<br>PDI_VSYNC<br>—                  | _                     | SIUL<br>PDI<br>—                      | I/O       | S                 | None,<br>None        | _        | 121        | B3         |

| PJ[3] | PCR[108] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[108]<br>PDI_PCLK<br>—                   | -                     | SIUL<br>PDI<br>—                      | I/O       | M1                | None,<br>None        | _        | 122        | A4         |

| PJ[4] | PCR[109] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[109]<br>PDI[0]<br>CANRX_0<br>—          | -                     | SIUL<br>PDI<br>FlexCAN_0<br>—         | I/O       | S                 | None,<br>None        | _        | 57         | B4         |

| PJ[5] | PCR[110] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[110]<br>PDI[1]<br>CANTX_0<br>—          | -                     | SIUL<br>PDI<br>FlexCAN_0<br>—         | I/O       | M1                | None,<br>None        | _        | 58         | A5         |

| PJ[6] | PCR[111] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[111]<br>PDI[2]<br>CANRX_1<br>eMIOSA[22] | -                     | SIUL<br>PDI<br>FlexCAN_1<br>PWM/Timer | I/O       | S                 | None,<br>None        | _        | 59         | B5         |

| PJ[7] | PCR[112] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[112]<br>PDI[3]<br>CANTX_1<br>eMIOSA[21] | _                     | SIUL<br>PDI<br>FlexCAN_1<br>PWM/Timer | I/O       | M1                | None,<br>None        | _        | 60         | A6         |

| PJ[8] | PCR[113] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[113]<br>PDI[4]<br>—                     | _                     | SIUL<br>PDI<br>—                      | I/O       | S                 | None,<br>None        | _        | 125        | B6         |

Table 8. Port pin summary (continued)

MPC5606S Microcontroller Data Sheet, Rev. 8

47

| Symb             | 0  | с | Parameter                                                 | Conditions | Va                 | lue                      | Unit |

|------------------|----|---|-----------------------------------------------------------|------------|--------------------|--------------------------|------|

| Symb             | 01 | C | Falantelei                                                | Conditions | Min                | Max                      | Onit |

| V <sub>LCD</sub> | SR |   | Voltage on VLCD (LCD supply) pin with respect to $V_{SS}$ |            | 0                  | V <sub>DDE_A</sub> + 0.3 | V    |

| TV <sub>DD</sub> | SR | С | V <sub>DD</sub> slope to ensure correct power up          | —          | 5×10 <sup>−6</sup> | 0.25                     | V/µs |

| T <sub>A</sub>   | SR | С | Ambient temperature under bias                            | —          | -40                | 105                      | °C   |

| TJ               | SR | С | Junction temperature under bias                           |            | -40                | 150                      |      |

Table 15. Recommended operating conditions (3.3 V) (continued)

$^{1}$  100 nF capacitance needs to be provided between V\_{DDA}/V\_{SSA} pair.

$^2$  At least 10  $\mu F$  capacitance must be connected between  $V_{DDR}$  and  $V_{SSR}$ . This is required because of sharp surge due to external ballast.

$^{3}$  V<sub>DD</sub> refers collectively to I/O voltage supplies, i.e., V<sub>DDE\_A</sub>, V<sub>DDE\_B</sub>, V<sub>DDE\_C</sub>, V<sub>DDE\_E</sub>, V<sub>DDMA</sub>, V<sub>DDMB</sub> and V<sub>DDMC</sub>.

- <sup>4</sup> 100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair

- <sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/O's DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub> device is reset.

- <sup>6</sup> V<sub>SS</sub> refers collectively to I/O voltage supply grounds, i.e., V<sub>SSE\_A</sub>, V<sub>SSE\_B</sub>, V<sub>SSE\_C</sub>, V<sub>SSE\_E</sub>, V<sub>SSMA</sub>, V<sub>SSMB</sub> and V<sub>SSMC</sub>) unless otherwise noted.

| Symbo                          |    | с | Parameter                                                                                                                 | Conditions                        | Va                    | lue                   | Unit |

|--------------------------------|----|---|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|-----------------------|------|

| Symbo                          | וכ | C | Falameter                                                                                                                 | Conditions                        | Min                   | Max                   |      |

| V <sub>DDA</sub> <sup>1</sup>  | SR | С | Voltage on VDDA pin (ADC reference) with                                                                                  | _                                 | 4.5                   | 5.5                   | V    |

|                                |    | С | respect to ground (V <sub>SS</sub> )                                                                                      | Voltage drop <sup>2</sup>         | 3.0                   | 5.5                   |      |

|                                |    | С |                                                                                                                           | Relative to<br>V <sub>DDE_C</sub> | V <sub>DD</sub> – 0.1 | V <sub>DD</sub> + 0.1 |      |

| V <sub>SSA</sub>               | SR | С | Voltage on VSSA (ADC reference) pin with respect $\rm V_{SS}$                                                             | —                                 | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>SSPLL</sub>             | SR | С | Voltage on VSSPLL pin with respect to V <sub>SS12</sub>                                                                   | —                                 | 0                     | 0                     | V    |

| V <sub>DDR</sub> <sup>3</sup>  | SR | С | Voltage on VDDR pin (regulator supply) with                                                                               | —                                 | 4.5                   | 5.5                   | V    |

|                                |    | С | respect to ground (V <sub>SSR</sub> )                                                                                     | Voltage drop <sup>2</sup>         | 3.0                   | 5.5                   |      |

|                                |    | С |                                                                                                                           | Relative to V <sub>DD</sub>       | V <sub>DD</sub> – 0.1 | V <sub>DD</sub> + 0.1 |      |

| V <sub>SSR</sub>               | SR | С | Voltage on VSSR (regulator ground) pin with respect to $\rm V_{SS12}$                                                     | —                                 | 0                     | 0                     | V    |

| V <sub>SS12</sub>              | СС | С | Voltage on VSS12 pin with respect to $V_{SS}$                                                                             | —                                 | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>DD</sub> <sup>4,5</sup> | SR | С | Voltage on VDD pins (VDDE_A, VDDE_B,<br>VDDE_C, VDDE_E, VDDMA, VDDMB,<br>VDDMC) with respect to ground (V <sub>SS</sub> ) | Voltage drop <sup>2</sup>         | 4.5                   | 5.5                   | V    |

| V <sub>SS</sub> <sup>6</sup>   | SR | С | I/O supply ground                                                                                                         | —                                 | 0                     | 0                     | V    |

| V <sub>DDE_A</sub>             | SR | С | Voltage on VDDE_A (I/O supply) pin with respect to ground (V <sub>SSE_A</sub> )                                           | —                                 | 4.5                   | 5.5                   | V    |

Table 16. Recommended operating conditions (5.0 V)

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0 V ±10% range

- LVDLVCOR monitors power domain No. 1

- LVDLVBKP monitors power domain No. 0

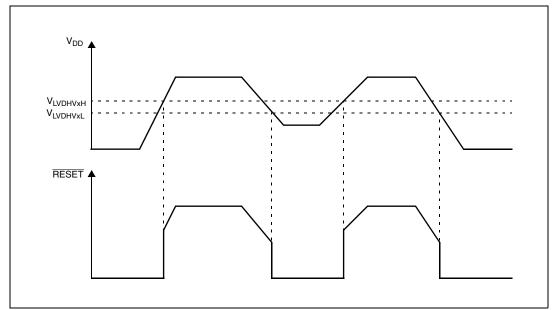

Figure 9. Low voltage monitor vs. reset

| Symbol                              |    | с | Parameter                                    | Conditions <sup>1</sup> |      | Value |      | Unit |

|-------------------------------------|----|---|----------------------------------------------|-------------------------|------|-------|------|------|

| Symbol                              |    | Ŭ | i arameter                                   | Conditions              | Min  | Тур   | Max  | onn  |

| V <sub>PORH</sub>                   | СС | Ρ | Power-on reset threshold                     | _                       | 1.5  |       | 2.6  | V    |

| V <sub>LVDHV3H</sub>                | СС | Ρ | LVDHV3 low voltage detector high threshold   | —                       | _    | _     | 2.9  | V    |

| V <sub>LVDHV5H</sub>                | СС | Ρ | LVDHV5 low voltage detector high threshold   | —                       | _    | _     | 4.4  | V    |

| V <sub>LVDHV3L</sub>                | СС | Ρ | LVDHV3 low voltage detector low threshold    | _                       | 2.6  |       | _    | V    |

| V <sub>LVDHV5L</sub>                | СС | Ρ | LVDHV5 low voltage detector low threshold    | —                       | 3.8  | _     | _    | V    |

| V <sub>LVDLVCORH</sub> <sup>2</sup> | СС | Ρ | LVDLVCOR low voltage detector high threshold | T <sub>A</sub> = 25 °C, |      | _     | 1.15 | V    |

| V <sub>LVDLVCORL</sub>              | СС | Ρ | LVDLVCOR low voltage detector low threshold  | after trimming          | 1.08 | _     | —    | V    |

#### Table 26. Low voltage monitor electrical characteristics

<sup>1</sup> V<sub>DD</sub> = 3.3 V ±10% / 5.0 V ±10%, T<sub>A</sub> = -40 to 105 °C, unless otherwise specified.

<sup>2</sup> L<sub>VDLVBKP</sub> has same post-trim thresholds as LVDLVCOR.

### 3.7.3 Low voltage domain power consumption

Table 27 provides DC electrical characteristics for significant application modes. These values are indicative values; actual consumption depends on the application.

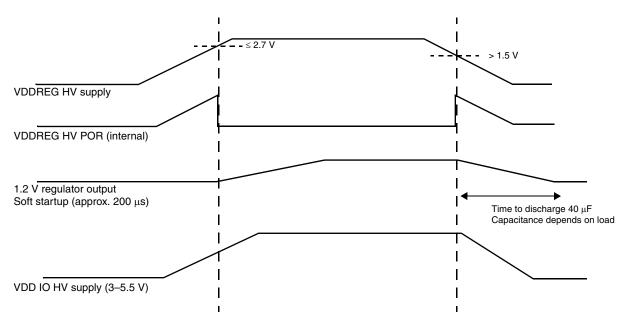

Figure 11. Recommended order for powering down the power supplies

### CAUTION

The VDD IO HV supply must be disabled after the VDDREG HV supply voltage drops below 1.5 V. This is to ensure that the 1.2 V regulator shuts down before the 3.3 V regulator shuts down.

### 3.7.5 Power-up inrush current profile

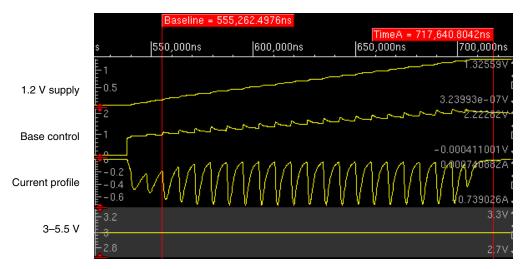

Figure 12 shows the power up inrush current profile of the ballast transistor under the worst possible startup condition (fastest PVT and fastest power ramp time).

Figure 12. Power-up inrush current profile

| Sym               | bol | с | Parameter                                                    | Conditions <sup>1</sup>                                                           |     | Value |     | Unit  |

|-------------------|-----|---|--------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-------|-----|-------|

| Synn              | 501 | C | Falameter                                                    | Conditions                                                                        | Min | Тур   | Max | Onit  |

| T <sub>tr</sub>   | CC  | Т | Output transition time output pin <sup>3</sup>               | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0              | _   | —     | 4   | ns    |

|                   |     | Т | FAST configuration                                           | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0              | —   | —     | 6   |       |

|                   |     | Т |                                                              | $C_L = 100 \text{ pF},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ |     | —     | 12  |       |

|                   |     | Т |                                                              | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1              | _   | —     | 4   |       |

|                   |     | Т |                                                              | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1              | _   | —     | 7   |       |

|                   |     | Т |                                                              | C <sub>L</sub> = 100 pF,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1             |     | —     | 12  |       |

| $\Delta I_{tr50}$ | CC  | D | Current slew at C <sub>L</sub> = 50 pF<br>FAST configuration | $V_{DD} = 5.0 V \pm 10\%$ , PAD3V5V = 0 (recommended configuration)               | —   | —     | 55  | mA/ns |

|                   |     | D |                                                              | $V_{DD} = 3.3 \text{ V} \pm 10\%$ , PAD3V5V = 1<br>(recommended configuration)    |     | —     | 40  |       |

|                   |     | D |                                                              | V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 1                                         | _   | —     | 100 |       |

#### Table 34. FAST configuration output buffer electrical characteristics (continued)

$^1~V_{DD}$  = 3.3 V  $\pm 10\%$  / 5.0 V  $\pm 10\%,~T_A$  = –40 to 105 °C, unless otherwise specified

<sup>2</sup> This is a transient configuration during power-up. All pads but RESET and NEXUS output (MDOx, EVTO, MCK) are configured in input or in high impedance state.

<sup>3</sup> C<sub>L</sub> includes device and package capacitance (C<sub>PKG</sub> < 5 pF).

| Symbo             | 2  | с | Parameter                  | Conditions                            |                        | Value   |                       | Unit |

|-------------------|----|---|----------------------------|---------------------------------------|------------------------|---------|-----------------------|------|

| Symbo             | ,  | C | Farameter                  | Conditions                            | Min                    | Typ Max |                       | Onit |

| V <sub>IL</sub>   | CC | Ρ | Low level input voltage    | -                                     | -0.4                   | _       | $0.35 \times V_{DDM}$ | V    |

| V <sub>IH</sub>   | CC | Ρ | High level input voltage   | -                                     | $0.65 \times V_{DDM}$  | _       | V <sub>DDM</sub> +0.4 |      |

| V <sub>HYST</sub> | CC | С | Schmitt trigger hysteresis | _                                     | 0.1×V <sub>DDM</sub>   | _       | —                     |      |

| V <sub>OL</sub>   | CC | Ρ | Low level output voltage   | I <sub>OL</sub> = 20 mA <sup>1</sup>  | —                      | _       | 0.32                  |      |

|                   |    |   |                            | I <sub>OL</sub> = 30 mA <sup>2</sup>  | —                      | _       | 0.48                  |      |

| V <sub>OH</sub>   | CC | Ρ | High level output voltage  | I <sub>OH</sub> = -20 mA <sup>1</sup> | V <sub>DDM</sub> -0.32 | _       | —                     |      |

|                   |    |   |                            | I <sub>OH</sub> = -30 mA <sup>2</sup> | V <sub>DDM</sub> -0.48 | _       | —                     |      |

#### Table 35. SMD pad electrical characteristics

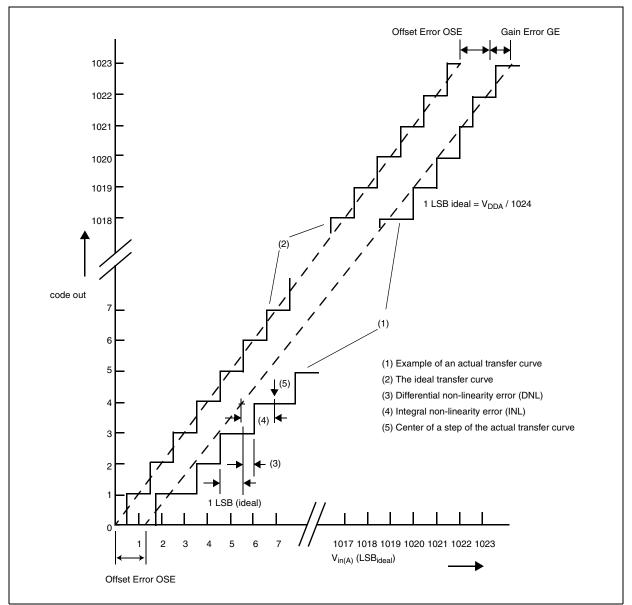

Figure 21. ADC Characteristics and Error Definitions

# 3.17.1 Input impedance and ADC accuracy

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; furthermore, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

- $^1~V_{DDA}$  = 3.3 V ±10% / 5.0 V ±10%,  $T_A$  = –40 to 105 °C, unless otherwise specified.

- <sup>2</sup> Analog and digital V<sub>SS</sub> **must** be common (to be tied together externally).

- <sup>3</sup> V<sub>AINx</sub> may exceed V<sub>SSA</sub> and V<sub>DDA</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0x3FF.

- <sup>4</sup> At 32 MHz the minimum sampling time must be at least 180 ns.

- <sup>5</sup> During the sample time the input capacitance  $C_S$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_{ADC_S}$ . After the end of the sample time  $t_{ADC_S}$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample clock  $t_{ADC_S}$  depend on programming.

- <sup>6</sup> The maximum sample rate is 1 million samples per second, provided the source impedance and current limiter(> 1 k $\Omega$ ) are calculated adequately.

— Filter capacitor at analog source output must meet the criteria Cf (filter capacitor) >  $2048 \times Cs$  (sampling capacitor is 3 pF).

<sup>7</sup> This parameter does not include the sample time t<sub>ADC\_S</sub>, but only the time for determining the digital result and the time to load the result's register with the conversion result.

# 3.18 LCD driver electrical characteristics

#### Table 51. LCD driver specifications

| Symbol             |    | с | Parameter                                                                                                                                            |     | Unit |            |     |

|--------------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------------|-----|

| Symbol             |    | C | Falameter                                                                                                                                            | Min | Тур  | Max        | Ome |

| VLCD               | SR | С | Voltage on VLCD (LCD supply) pin with respect to VSS                                                                                                 | 0   | _    | VDDE + 0.3 | V   |

| Z <sub>BP/FP</sub> | CC | Т | LCD output impedance<br>(BP[n-1:0],FP[m-1:0]) for output levels<br>VLCD, VSS <sup>2</sup>                                                            | _   | _    | 5.0        | kΩ  |

| I <sub>BP/FP</sub> | CC | Т | LCD output current<br>(BP[n-1:0],FP[m-1:0]) for outputs<br>charge/discharge voltage levels<br>VLCD2/3, VLCD1/2, VLCD1/3) <sup>2</sup> , <sup>3</sup> | _   | 25   | _          | μA  |

$^1~V_{DD}$  = 5.0 V  $\pm$  10%,  $T_A$  = –40–105 °C, unless otherwise specified

<sup>2</sup> Outputs measured one at a time, low impedance voltage source connected to the VLCD pin.

<sup>3</sup> With PWR=10, BSTEN=0, and BSTAO=0

# 3.19 Pad AC specifications

| No. Pad |      | Tswitchon <sup>1</sup><br>(ns) |     |     | Rise/Fall <sup>2</sup><br>(ns) |     |     | Frequency<br>(MHz) |     |     | Current slew<br>(mA/ns) |     |     | Load drive<br>(pF) |

|---------|------|--------------------------------|-----|-----|--------------------------------|-----|-----|--------------------|-----|-----|-------------------------|-----|-----|--------------------|

|         |      |                                | Тур | Max | Min                            | Тур | Max | Min                | Тур | Max | Min                     | Тур | Max | (рі)               |

| 1       | Slow | 1.5                            |     | 30  | 6                              | _   | 50  | _                  | —   | 4   | 0.04                    |     | 2   | 25                 |

|         |      | 1.5                            |     | 30  | 9                              | _   | 100 | _                  |     | 2   | 0.04                    |     | 2   | 50                 |

|         |      | 1.5                            | —   | 30  | 12                             | —   | 125 | —                  | —   | 2   | 0.04                    | —   | 2   | 100                |

|         |      | 1.5                            | —   | 30  | 16                             | _   | 150 | _                  | —   | 2   | 0.04                    | —   | 2   | 200                |

#### Table 52. Pad AC specifications $(5.0 \text{ V}, \text{PAD3V5V} = 0)^1$

| No. | No. Pad                     |     | Tswitchon <sup>1</sup><br>(ns) |     |     | Rise/Fall <sup>2</sup><br>(ns) |      |     | Frequency<br>(MHz) |     |     | rrent s<br>mA/ns | Load drive<br>(pF) |      |

|-----|-----------------------------|-----|--------------------------------|-----|-----|--------------------------------|------|-----|--------------------|-----|-----|------------------|--------------------|------|

|     |                             | Min | Тур                            | Max | Min | Тур                            | Max  | Min | Тур                | Max | Min | Тур              | Max                | (61) |

| 3   | Fast                        | 1   |                                | 6   | 1   | —                              | 4    | _   | —                  | 72  | 3   | —                | 40                 | 25   |

|     |                             | 1   |                                | 6   | 1.5 | _                              | 7    |     |                    | 55  | 3   |                  | 40                 | 50   |

|     |                             | 1   | —                              | 6   | 3   | —                              | 12   | —   | —                  | 40  | 3   | —                | 40                 | 100  |

|     |                             | 1   |                                | 6   | 5   | —                              | 18   | _   |                    | 25  | 3   |                  | 40                 | 200  |

| 4   | Pull Up/Down<br>(3.6 V max) | _   | —                              | —   | —   | —                              | 7500 | _   | —                  | —   | _   | —                | —                  | 50   |

|     | Parameter<br>Classification |     | D                              |     | С   |                                | С    |     |                    | с   |     |                  | n/a                |      |

### Table 53. Pad AC specifications $(3.3 \text{ V}, \text{PAD3V5V} = 1)^1$ (continued)

$^{1}$  Propagation delay from V<sub>DD</sub>/2 of internal signal to Pchannel/Nchannel on condition

<sup>2</sup> Slope at rising/falling edge

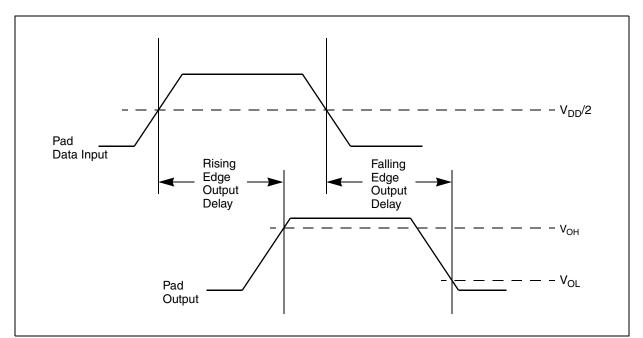

Figure 26. Pad output delay

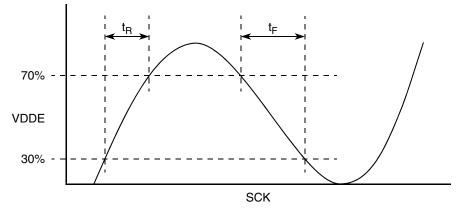

The clock profile in Figure 49 is measured at 30% to 70% levels of VDDE.

Figure 49. QuadSPI clock profile

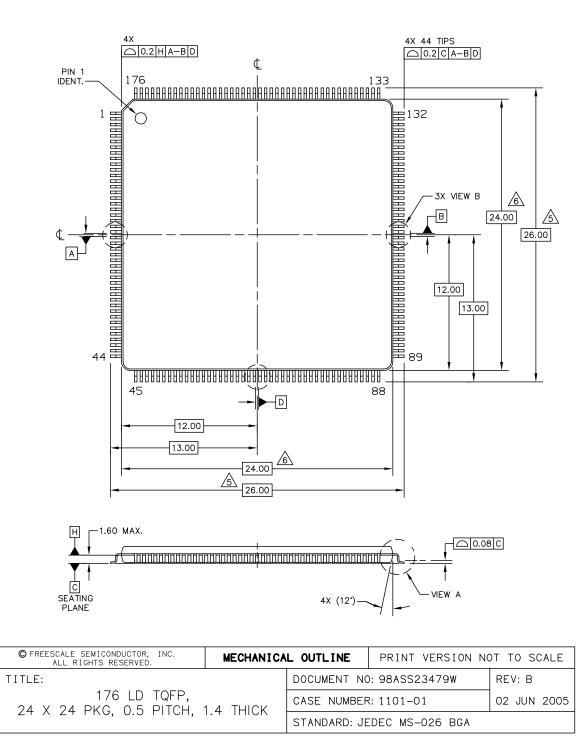

## 4.2 176 LQFP

Figure 53. LQFP176 mechanical drawing (Part 1 of 3)

| Table 66. Document revis | sion history |

|--------------------------|--------------|

|--------------------------|--------------|

| Revision | Date               | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S        | Date<br>1 Sep 2010 | Substantive changes           Editorial changes and improvements.           Replaced "validation" with "characterization" throughout.           Added an entry for Rev. 3 to this table.           In the block diagram, in the SXOSC block, changed "32 kHz" to "32 KHz".           Revised the feature section and added the "Feature details" subsection.           Renamed the analog pins (were AN, are ANS) throughout.           Changed several pin names that contained _A, _B, _C, to contain _0, _1, _2, throughout.           Changed the PCS and oscillator pin names throughout.           Revised the feature section and added the "Feature details" subsection.           Deleted the out-of-date "Block summary" section.           In the 144_pin pinout:           • For pin 122, changed PCS_B 1 to PCS1_1.           In the 'I74-pin pinout:           • For pin 152, changed PCS_B 1 to PCS1_1.           • For pin 153, changed PCS_B 0 to PCS0_1.           Revised the "Pad configuration during reset phases", "Voltage supply pins", "Pad types", "System pins", and "Nexus pins" sections.           In the "Voltage supply pin descriptions" table, changed pad type M1.           In the "Bad types" section, changed 'registers in the device reference manual".           Changed the name of the port-pin summary section (was "Functional ports A, B, C, D, E, F, G, H, I, J, K', is "Port pin summary").           In the "Signal details" section.           Renamed the analog pi |

|          |                    | Added a footnote to the "Special function" column title.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### **Revision history**

| Revision | Date        | Substantive changes                                                                                                                                                    |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 14 Jan 2011 | Editorial changes and improvements.                                                                                                                                    |

|          |             | Swapped XTAL and EXTAL pins for the 208-pin BGA package and throughout.                                                                                                |

|          |             | In the "Pinout and signal descriptions" section, changed WARNING labels to CAUTION labels.                                                                             |

|          |             | Updated the "Absolute maximum ratings" and "Recommended operating conditions" tables.                                                                                  |

|          |             | Added footnote reference to V <sub>ss12</sub> in "Recommended operating conditions (3.3 V)" table.                                                                     |

|          |             | Updated the "Connecting power supply pins" section.                                                                                                                    |

|          |             | Removed footnote regarding characterization in the "Thermal characteristics" table.                                                                                    |

|          |             | Updated the V <sub>DD12</sub> /V <sub>DDPLL</sub> operating voltages in the "Electromagnetic interference" table.                                                      |

|          |             | Added typical values and updated the "Voltage regulator electrical characteristics,"<br>"Low-power voltage regulator electrical characteristics," and "Ultra-low-power |

|          |             | voltage regulator electrical characteristics" tables.                                                                                                                  |

|          |             | Updated classifications and values in the "Low voltage monitor electrical characteristics" table.                                                                      |

|          |             | Made major modifications and updates to the "DC electrical characteristics" table.                                                                                     |

|          |             | Made major modifications and updates to the "I/O input DC electrical characteristics" table.                                                                           |

|          |             | Made major modifications and updates to the "I/O pull-up/pull-down DC electrical characteristics" table.                                                               |

|          |             | Changed "SMC" pads to "SMD" pads throughout.                                                                                                                           |

|          |             | Made updates to the "SMD pad electrical characteristics" table.                                                                                                        |

|          |             | Added run current during RESET to the "Reset electrical characteristics" table.                                                                                        |

|          |             | Updated the FMPLL jitter (peak to peak) specification in the "FMPLL electrical characteristics" table.                                                                 |

|          |             | Updated f <sub>FIRC</sub> and t <sub>FIRCSU</sub> in the "Fast internal RC oscillator (16 MHz) electrical characteristics" table.                                      |

|          |             | Updated f <sub>SIRC</sub> and t <sub>SIRCSU</sub> in the "Slow internal RC oscillator (128 kHz) electrical characteristics" table.                                     |

|          |             | Removed "symmetric" pad type from the "Pad AC specifications (5.0 V, PAD3V5V = 0)" table.                                                                              |

|          |             | Removed "symmetric" pad type from the "Pad AC specifications (3.3 V, PAD3V5V = 1)" table.                                                                              |

|          |             | Updated V <sub>DD12</sub> post-trimming minimum value in the "Low-power voltage regulator electrical characteristics" table.                                           |

|          |             | Updated V <sub>DD12</sub> post-trimming minimum value in the "Ultra-low-power voltage regulator electrical characteristics" table.                                     |

|          |             | Updated V <sub>LVDLVCORH</sub> maximum value in the "Low voltage monitor electrical characteristics" table.                                                            |

|          |             | Updated V <sub>LVDLVCORL</sub> minimum value in the "Low voltage monitor electrical characteristics" table.                                                            |

|          |             | Updated value of V <sub>DD12</sub> /V <sub>DDPLL</sub> operating voltages in the "Input DC electrical characteristics" table.                                          |

|          |             | Corrected erroneous value of I <sub>LKG</sub> (105°C case) in the "Input DC electrical characteristics" table.                                                         |

### Table 66. Document revision history