Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, QSPI, SCI, SPI                        |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                                 |

| Number of I/O              | 108                                                                     |

| Program Memory Size        | 1MB (1M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K × 8                                                                 |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5606sf2vlq6r |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.5.3 Crossbar switch (XBAR)

The XBAR multi-port crossbar switch supports simultaneous connections between four master ports and four slave ports. The crossbar supports a 32-bit address bus width and a 32-bit data bus width.

The crossbar allows four concurrent transactions to occur from any master port to any slave port, but one of those transfers must be an instruction fetch from internal flash. If a slave port is simultaneously requested by more than one master port, arbitration logic selects the higher priority master and grants it ownership of the slave port. All other masters requesting that slave port are stalled until the higher priority master completes its transactions. Requesting masters having equal priority are granted access to a slave port in round-robin fashion, based upon the ID of the last master to be granted access.

The crossbar provides the following features:

- Four master ports:

- e200z0h core instruction port

- e200z0h core complex load/store data port

- eDMA controller

- Display control unit

- Four slave ports:

- One flash port dedicated to the CPU

- Platform SRAM

- QuadSPI serial flash controller

- One slave port combining:

- Flash port dedicated to the Display Control Unit and eDMA module

- Graphics SRAM

- Peripheral bridge

- 32-bit internal address bus, 32-bit internal data bus

### 1.5.4 Enhanced Direct Memory Access (eDMA)

The eDMA module is a controller capable of performing complex data movements via 16 programmable channels, with minimal intervention from the host processor. The hardware micro architecture includes a DMA engine, that performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is utilized to minimize the overall block size. The eDMA module provides the following features:

- 16 channels support independent 8-, 16-, or 32-bit single value or block transfers.

- Supports variable-sized queues and circular queues.

- Source and destination address registers are independently configured to post-increment or remain constant.

- Each transfer is initiated by a peripheral, CPU, periodic timer interrupt, or eDMA channel request.

- Each DMA channel can optionally send an interrupt request to the CPU on completion of a single value or block transfer.

- DMA transfers possible between system memories, QuadSPI, DSPIs, I<sup>2</sup>C, ADC, eMIOS, and General Purpose I/Os (GPIOs).

- Programmable DMA Channel Mux allows assignment of any DMA source to any available DMA channel with as many as 64 potential request sources.

# 1.5.5 Inter-IC communications module (I<sup>2</sup>C)

The I<sup>2</sup>C module features the following:

• As many as four I<sup>2</sup>C modules supported

Overview

- Eight clock and transfer attributes registers

- Chip select strobe available as alternate function on one of the chip select pins for deglitching

- FIFOs for buffering as many as four transfers on the transmit and receive side

- General purpose I/O functionality on pins when not used for SPI

- Queueing operation possible through use of eDMA

### 1.5.17 FlexCAN

The MPC5606S MCU contains two controller area network (FlexCAN) modules. The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness, and required bandwidth.

The FlexCan modules offer the following:

- Compliant with CAN protocol specification, Version 2.0B active

- 64 mailboxes, each configurable as transmit or receive

- Mailboxes configurable while module remains synchronized to CAN bus

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- Eight mailboxes configurable as a 6-entry receive FIFO

- Eight programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

- Listen-only mode capabilities

- CAN Sampler

- Can catch the first message sent on the CAN network while the MPC5606S is stopped; this guarantees a clean startup of the system without missing messages on the CAN network

- CAN sampler is connected to one of the CAN RX pins

# 1.5.18 Serial communication interface module (LINFlex)

The MPC5606S devices include as many as two LINFlex modules and support for LIN Master mode, LIN Slave mode, and UART mode. The modules are LIN state machine-compliant to the LIN 1.3 and 2.0 and 2.1 specifications and handle LIN frame transmission and reception without CPU intervention.

Other features include:

- Autonomous LIN frame handling

- Message buffer to store identifier and as many as 8 data bytes

- Supports message length as long as 64 bytes

- Detection and flagging of LIN errors

- Sync field, Delimiter, ID parity, Bit, Framing, Checksum, and Timeout errors

- Classic or extended checksum calculation

The PDI features the following:

- Supported color modes:

- 8-bit mono

- 8-bit color multiplexed

- RGB565

- 16-bit/18-bit RAW color

- Supported synchronization modes:

- Embedded ITU-R BT.656-4 (RGB565 mode 2)

- HSYNC, VSYNC

- Data enable

- Direct interface with DCU background plane FIFO

- Synchronization generation for the DCU

# 1.5.26 Liquid Crystal Display (LCD) driver

The LCD driver module has two configurations allowing a maximum of 160 or 228 LCD segments:

- As many as 40 frontplane drivers and four backplane drivers

- As many as 38 frontplane drivers and six backplane drivers

Each segment is controlled and can be masked by a corresponding bit in the LCD RAM.

Four to six multiplex modes (1/1, 1/2, 1/3, 1/4, 1/5, 1/6 duty), and three bias (1/1, 1/2, 1/3) methods are available. All frontplane and backplane pins can be multiplexed with other port functions.

The LCD driver module features the following:

- Programmable frame clock generator from different clock sources:

- System clock

- Internal RC oscillator

- Programmable bias voltage level selector

- On-chip generation of all output voltage levels

- LCD voltage reference taken from main 5 V supply

- LCD RAM contains the data to be displayed on the LCD

- Data can be read from or written to the display RAM at any time

- End-of-frame interrupt:

- Optimize data refresh without visual artifacts

- Selectable number of frames between each interrupt

- Contrast adjustment using programmable internal voltage reference

- Remapping capability of four or six backplanes with frontplanes

- Increases pin selection flexibility

- In low-power modes, LCD operation can be suspended under software control; the LCD can also operate in low-power modes, clocked by the internal 128 kHz IRC or external 32 KHz crystal oscillator

- Selectable output current boost during transitions

# 1.5.27 Stepper Motor Controller (SMC)

The SMC module is a PWM motor controller suitable to drive instruments in a cluster configuration or any other loads requiring a PWM signal. The motor controller has twelve PWM channels associated with two pins each (24 pins in total).

The SMC module includes the following features:

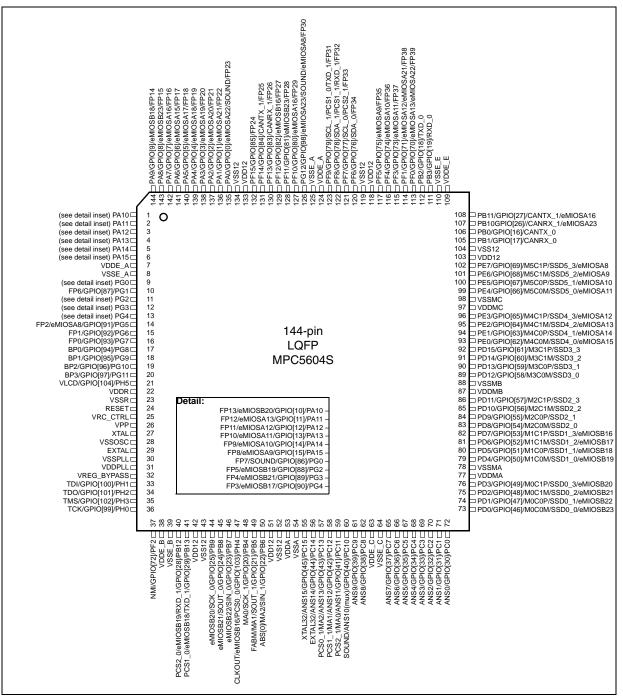

#### **Pinout and signal descriptions**

Figure 3. 144-pin LQFPpinout for MPC5604S

# 2.9.1 Signal details

| Signal                                   | Peripheral | Description                                                                                                                                                                                   |

|------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABS[0]                                   | BAM        | Alternate Boot Select. Gives an option to boot by downloading code via CAN or LIN.                                                                                                            |

| ANS[0:15]                                | ADC        | Inputs used to bring into the device sensor-based signals for A/D conversion. ANS[0:15] connect to ATD channels [32:47].                                                                      |

| MA[0:2]                                  | ADC        | These three control bits are output to enable the selection for an external Analog Mux for expansion channels. The available 8 multiplexed channels connect to ATD channels [64:71].          |

| FABM                                     |            | Force Alternate Boot mode. Forces the device to boot from the external bus (Can or LIN). If not asserted, the device boots up from the lowest flash sector containing a valid boot signature. |

| DCU_DE                                   | DCU        | Indicates that valid pixels are present.                                                                                                                                                      |

| DCU_HSYNC                                | DCU        | Horizontal sync pulse for TFT-LCD display.                                                                                                                                                    |

| DCU_PCLK                                 | DCU        | Output pixel clock for TFT-LCD display.                                                                                                                                                       |

| DCU_R[0:7],<br>DCU_G[0:7],<br>DCU_B[0:7] | DCU        | Red, green and blue color 8-bit pixel values for TFT-LCD displays.                                                                                                                            |

| DCU_TAG                                  | DCU        | Indicates when a tagged pixel is present in safety mode.                                                                                                                                      |

| DCU_VSYNC                                | DCU        | Vertical sync pulse for TFT-LCD display.                                                                                                                                                      |

| PCS[02]_0,<br>PCS[02]_1                  | DSPI       | Peripheral chip selects when device is in Master mode; not used in slave modes.                                                                                                               |

| SCK_0,<br>SCK_1                          | DSPI       | SPI clock signal—bidirectional.                                                                                                                                                               |

| SIN_0,<br>SIN_1                          | DSPI       | SPI data input signal.                                                                                                                                                                        |

| SOUT_0,<br>SOUT_1                        | DSPI       | SPI data output signal.                                                                                                                                                                       |

| PCS0_2                                   | QuadSPI    | Peripheral chip select for serial flash mode or chip select 0 for SPI master mode.                                                                                                            |

| IO2/PCS1_2                               | QuadSPI    | Chip select 1 for SPI master mode and bidirectional IO2 for serial flash mode.                                                                                                                |

| IO3/PCS2_2                               | QuadSPI    | Chip select 2 for SPI master mode and bidirectional IO3 for serial flash mode.                                                                                                                |

| IO0/SIN_2                                | QuadSPI    | Data input signal for SPI master and slave modes and bidirectional IO0 for serial flash mode.                                                                                                 |

| IO1/SOUT_2                               | QuadSPI    | Data output signal for SPI master and slave modes and bidirectional IO1 for serial flash mode.                                                                                                |

| SCK_2                                    | QuadSPI    | Clock output signal for SPI master and serial flash modes and clock input signal for SPI slave mode.                                                                                          |

| eMIOSA[8:23],<br>eMIOSB[16:23]           | eMIOS      | Enhanced Modular Input Output System. 16+8 channel eMIOS for timed input or output functions.                                                                                                 |

### Table 10. Signal details

| Symbol                                                           |    | с | Parameter                                                                                    | Conditions                  | Va                    | alue                     | Unit |

|------------------------------------------------------------------|----|---|----------------------------------------------------------------------------------------------|-----------------------------|-----------------------|--------------------------|------|

| Symbo                                                            | 1  | C | Parameter                                                                                    | Conditions                  | Min                   | Мах                      | Unit |

| V <sub>DDE_B</sub> <sup>1</sup>                                  | SR | С | Voltage on VDDE_B (I/O supply) pin with respect to ground (V <sub>SSE_B</sub> )              |                             | -0.3                  | 6.0                      | V    |

| V <sub>DDE_C</sub> <sup>1</sup>                                  | SR | С | Voltage on VDDE_C (I/O supply) pin with respect to ground (V <sub>SSE_C</sub> )              | —                           | -0.3                  | 6.0                      | V    |

| V <sub>DDE_E</sub> <sup>1</sup>                                  | SR | С | Voltage on VDDE_E (I/O supply) pin with respect to ground (V <sub>SSE_E</sub> )              |                             | -0.3                  | 6.0                      | V    |

| V <sub>DDMA</sub> <sup>1</sup>                                   | SR | С | Voltage on VDDMA (stepper motor supply) pin with respect to ground (V <sub>SSMA</sub> )      |                             | -0.3                  | 6.0                      | V    |

| V <sub>DDMB</sub> <sup>1</sup><br>V <sub>DDMC</sub> <sup>1</sup> | SR | С | Voltage on VDDMB/C (stepper motor supply)<br>pin with respect to ground (V <sub>SSMB</sub> ) |                             | -0.3                  | 6.0                      | V    |

| V <sub>SS</sub> <sup>2</sup>                                     | SR | С | I/O supply ground                                                                            | _                           | 0                     | 0                        | V    |

| V <sub>SSOSC</sub>                                               | SR | С | Voltage on VSSOSC (oscillator ground) pin with respect to $V_{SS}$                           |                             | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1    | V    |

| V <sub>LCD</sub>                                                 | SR | С | Voltage on VLCD (LCD supply) pin with respect to $\mathrm{V}_{\mathrm{SS}}$                  |                             | 0                     | V <sub>DDE_A</sub> + 0.3 | V    |

| V <sub>IN</sub>                                                  | SR | С | Voltage on any GPIO pin with respect to ground                                               | —                           | -0.3                  | 6.0                      | V    |

|                                                                  |    | С | (V <sub>SS</sub> )                                                                           | Relative to $V_{\text{DD}}$ | -0.3                  | $V_{DD} + 0.3^{3}$       |      |

| I <sub>INJPAD</sub>                                              | SR | С | Injected input current on any pin during overload condition                                  |                             | -10                   | 10                       | mA   |

| I <sub>INJSUM</sub>                                              | SR | С | Absolute sum of all injected input currents during overload condition                        | —                           | -50                   | 50                       |      |

| I <sub>MAX</sub>                                                 | СС | D | Absolute maximum current drive rating                                                        | —                           | _                     | 45                       |      |

| T <sub>STORAGE</sub>                                             | SR | С | Storage temperature                                                                          | _                           | -55                   | 150                      | °C   |

<sup>1</sup> Throughout the remainder of this document V<sub>DD</sub> refers collectively to I/O voltage supplies, i.e., V<sub>DDE\_A</sub>, V<sub>DDE\_B</sub>, V<sub>DDE\_C</sub>, V<sub>DDE\_E</sub>, V<sub>DDE\_E</sub>, V<sub>DDMA</sub>, V<sub>DDMB</sub> and V<sub>DDMC</sub>, unless otherwise noted.

<sup>2</sup> Throughout the remainder of this document V<sub>SS</sub> refers collectively to I/O voltage supply grounds, i.e., V<sub>SSE\_A</sub>, V<sub>SSE\_B</sub>, V<sub>SSE\_C</sub>, V<sub>SSE\_E</sub>, V<sub>SSMA</sub>, V<sub>SSMB</sub> and V<sub>SSMC</sub>, unless otherwise noted.

<sup>3</sup> As long as the current injection specification is adhered to, then a higher potential is allowed.

#### NOTE

Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ), the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the recommended values.

# 3.6.2 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

- Software recommendations The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

- Prequalification trials Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring.

# 3.6.3 Electromagnetic interference (EMI)

#### Table 18. EMI testing specifications<sup>1</sup>

| Symbol C Parameter |    | Parameter | Conditions                                                   |                                                                                               |      | Unit |      |      |

|--------------------|----|-----------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| Cynte              |    | Ŭ         | randicter                                                    | Conditions                                                                                    | Min  | Тур  | Мах  | onne |

| —                  | SR | Т         | Scan range                                                   | 150 kHz – 30 MHz: RBW 9 kHz, step size 5 kHz<br>30 MHz – 1 GHz: RBW 120 kHz, step size 80 kHz | 0.15 | —    | 1000 | MHz  |

| _                  | SR | Т         | Operating frequency                                          | Crystal frequency 8 MHz                                                                       | _    | 64   | _    | MHz  |

| —                  | SR | Т         | V <sub>DD12</sub> , V <sub>DDPLL</sub><br>operating voltages | _                                                                                             |      | 1.28 | _    | V    |

| _                  | SR | Т         | VDD, VDDA<br>operating voltages                              | _                                                                                             | -    | 5    | -    | V    |

| —                  | SR | Т         | Maximum amplitude                                            | No PLL frequency modulation                                                                   | _    | 33   | _    | dBµV |

|                    |    |           |                                                              | ±2% PLL frequency modulation                                                                  | _    | 30   | _    |      |

| _                  | SR | Т         | Operating<br>temperature                                     | _                                                                                             |      | 25   | _    | °C   |

<sup>1</sup> EMI testing and I/O port waveforms per SAE J1752/3 issued 1995-03.

# 3.6.4 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

### 3.6.4.1 Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

- Fast pads These provide maximum speed. There are used for improved NEXUS debugging capability.

- SMD pads These provide additional current capability to drive stepper motor loads.

- Digital I/O with analog (J) pad These provide input and output digital features and analog input for ADC.

M2 and Fast pads can disable slew rate to reduce electromagnetic emission, at the cost of reducing AC performance.

### 3.8.2 I/O input DC characteristics

Table 30 provides input DC electrical characteristics as described in Figure 14.

Figure 14. I/O input DC electrical characteristics definition

| Sum              | Symbol |   | Parameter                                                          | Conditions <sup>1</sup> | Value              |     |                                                                                        |      |

|------------------|--------|---|--------------------------------------------------------------------|-------------------------|--------------------|-----|----------------------------------------------------------------------------------------|------|

| Sym              | IDOI   | С | Farameter                                                          | Conditions              | Min                | Тур | Max<br>V <sub>DD</sub> + 0.3<br>0.35V <sub>DD</sub><br>—<br>1<br>—<br>500<br>1000<br>1 | Unit |

| V <sub>IH</sub>  | SR     | Ρ | Input high level CMOS Schmitt trigger                              | —                       | $0.65 V_{DD}$      | _   | $V_{DD} + 0.3$                                                                         | V    |

| V <sub>IL</sub>  | SR     | Ρ | Input low level CMOS Schmitt trigger                               | _                       | -0.3               |     | 0.35V <sub>DD</sub>                                                                    |      |

| V <sub>HYS</sub> | CC     | D | Input hysteresis CMOS Schmitt trigger                              | _                       | 0.1V <sub>DD</sub> |     | —                                                                                      |      |

| I <sub>LKG</sub> | CC     | Ρ | Input leakage current                                              | _                       | -1                 |     | 1                                                                                      | μA   |

|                  |        |   |                                                                    | $T_A = -40^{\circ}C$    |                    | 2   | —                                                                                      | nA   |

|                  |        |   |                                                                    | $T_A = 25^{\circ}C$     |                    | 2   | —                                                                                      | nA   |

|                  |        | С |                                                                    | T <sub>A</sub> = 105°C  |                    | 12  | 500                                                                                    | nA   |

|                  |        | Ρ |                                                                    | T <sub>J</sub> = 150°C  | _                  | 70  | 1000                                                                                   | nA   |

| R <sub>ON</sub>  | CC     | D | Resistance of the analog switch inside the J pad type <sup>2</sup> | Supply range<br>3.3–5 V | _                  | _   | 1                                                                                      | kΩ   |

| Table 30. | I/O | input | DC | electrical | characteristics |

|-----------|-----|-------|----|------------|-----------------|

|-----------|-----|-------|----|------------|-----------------|

<sup>1</sup> V<sub>DD</sub> = 3.3 V ±10% / 5.0 V ±10%, T<sub>A</sub> = -40 to 105 °C.

<sup>2</sup> Applies to the J pad type only.

# 3.8.3 I/O output DC characteristics

The following tables provide DC characteristics for bidirectional pads:

- Table 31 provides weak pull figures. Both pull-up and pull-down resistances are supported.

- Table 32 provides output driver characteristics for I/O pads when in SLOW configuration.

- Table 33 provides output driver characteristics for I/O pads when in MEDIUM configuration (applies to both M1 and M2 type pads).

- Table 34 provides output driver characteristics for I/O pads when in FAST configuration.

- Table 35 provides SMD pad characteristics.

| Symbol           |     | c | с                      | Parameter                                 | Conditions <sup>2</sup> |    |     | Unit |    |

|------------------|-----|---|------------------------|-------------------------------------------|-------------------------|----|-----|------|----|

| Synn             | 501 | C | Farameter              | Conditions                                |                         |    | Тур | Max  |    |

| II <sub>W-</sub> | С   |   |                        | $V_{IN}=V_{IL},V_{DD}=5.0V\pm\!10\%$      | PAD3V5V = 0             | 10 |     | 150  | μA |

| PU               | С   | С | absolute value         |                                           | $PAD3V5V = 1^3$         | 10 |     | 250  |    |

|                  |     | Ρ |                        | $V_{IN}=V_{IL},V_{DD}=3.3V\pm\!10\%$      | PAD3V5V = 1             | 10 |     | 150  |    |

| II <sub>W-</sub> | С   | Ρ | Weak pull-down current | $V_{IN}=V_{IL},V_{DD}=5.0V\pm\!10\%$      | PAD3V5V = 0             | 10 |     | 150  | μA |

| PD               | С   | С | absolute value         |                                           | PAD3V5V = 1             | 10 |     | 250  |    |

|                  |     | Ρ |                        | $V_{IN} = V_{IL}, V_{DD} = 3.3V \pm 10\%$ | PAD3V5V = 1             | 10 | _   | 150  |    |

#### Table 31. I/O pull-up/pull-down DC electrical characteristics <sup>1</sup>

<sup>1</sup> The pull currents are dependent on the HVE settings.

$^2~V_{DD}$  = 3.3 V  $\pm 10\%$  / 5.0 V  $\pm 10\%,~T_A$  = –40 to 125 °C, unless otherwise specified.

<sup>3</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

| Table 32. SLOW configura | tion output buffer   | electrical characteristics |

|--------------------------|----------------------|----------------------------|

|                          | tion output building |                            |

| Syml            | hol | с | Parameter                               | Conditions <sup>1</sup>                                                                             |                       | Value |                    | Unit |

|-----------------|-----|---|-----------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|-------|--------------------|------|

| - Oyini         | 501 | Ŭ | i didineter                             | Conditions                                                                                          | Min                   | Тур   | Max                | Onit |

| V <sub>OH</sub> | СС  | Ρ | Output high level<br>SLOW configuration | Push Pull, $I_{OH} = -2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0<br>(recommended) | 0.8V <sub>DD</sub>    | _     | —                  | V    |

|                 |     | D |                                         | Push Pull, $I_{OH} = -2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 1 <sup>2</sup>     | 0.8V <sub>DD</sub>    |       | —                  |      |

|                 |     | С |                                         | Push Pull, $I_{OH} = -1 \text{ mA}$ ,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1<br>(recommended) | V <sub>DD</sub> – 0.8 |       | _                  |      |

| V <sub>OL</sub> | СС  | Ρ | Output low level<br>SLOW configuration  | Push Pull, $I_{OL} = 2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0<br>(recommended)  |                       | -     | 0.1V <sub>DD</sub> | V    |

|                 |     | D |                                         | Push Pull, I <sub>OL</sub> = 2 mA,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 1 <sup>2</sup>        | _                     | _     | 0.1V <sub>DD</sub> |      |

|                 |     | С |                                         | Push Pull, I <sub>OL</sub> = 1 mA,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1<br>(recommended)    |                       | _     | 0.5                |      |

### Table 37. I/O consumption

| Sumbo               |    | _ | Parameter                                             | Conditions <sup>1</sup>                                                     |                                                              | Value |      | Unit |

|---------------------|----|---|-------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------|-------|------|------|

| Symbo               | 1  | С | Parameter                                             | Conditions                                                                  | Min         Typ         Max           —         —         20 |       | Unit |      |

| I <sub>SWTSLW</sub> | СС | D | Dynamic I/O current for SLOW configuration            | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0        |                                                              | —     | 20   | mA   |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1        |                                                              | —     | 16   | -    |

| I <sub>SWTMED</sub> | СС | D | Dynamic I/O current for MEDIUM configuration          | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0        | _                                                            | —     | 29   | mA   |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1        | _                                                            | —     | 17   |      |

| I <sub>SWTFST</sub> | СС | D | Dynamic I/O current for FAST configuration            | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0        | _                                                            | —     | 110  | mA   |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1        | _                                                            | —     | 50   |      |

| I <sub>RMSSLW</sub> | СС | D | Root mean square I/O current for SLOW configuration   | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0  |                                                              | —     | 2.3  | mA   |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0  | _                                                            | —     | 3.2  |      |

|                     |    | D |                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0 |                                                              | —     | 6.6  |      |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1  | _                                                            | —     | 1.6  | -    |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1  |                                                              | _     | 2.3  | -    |

|                     |    | D |                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1 |                                                              |       | 4.7  | -    |

| I <sub>RMSMED</sub> | СС | D | Root mean square I/O current for MEDIUM configuration | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0  |                                                              | —     | 6.6  | mA   |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0  | _                                                            | —     | 13.4 |      |

|                     |    | D |                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0 | _                                                            | —     | 18.3 |      |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1  | —                                                            | —     | 5.0  |      |

|                     |    | D |                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1  | _                                                            | —     | 8.5  |      |

|                     |    | D |                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1 | _                                                            | —     | 11.0 |      |

| Symbo               |    | с | Parameter                                                             | Conditions <sup>1</sup>                                                           |     | Value                                                                                                                                                                                                                                                                            |      | Unit |

|---------------------|----|---|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Symbo               | 1  | C | Falameter                                                             | Conditions                                                                        | Min | Min         Typ         Max           —         —         22.0           —         —         22.0           —         —         33.0           —         —         56.0           —         —         14.0           —         —         20.0           —         —         25.0 |      | Unit |

| I <sub>RMSFST</sub> | СС | D | Root mean square I/O current for FAST configuration                   | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0        | —   |                                                                                                                                                                                                                                                                                  | 22.0 | mA   |

|                     |    | D |                                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0        |     |                                                                                                                                                                                                                                                                                  | 33.0 |      |

|                     |    | D |                                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ±10%, PAD3V5V = 0       | _   |                                                                                                                                                                                                                                                                                  | 56.0 |      |

|                     |    | D |                                                                       | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1        | —   | _                                                                                                                                                                                                                                                                                | 14.0 |      |

|                     |    | D |                                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1        | —   | _                                                                                                                                                                                                                                                                                | 20.0 |      |

|                     |    | D |                                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1       | _   |                                                                                                                                                                                                                                                                                  | 25.0 |      |

| I <sub>DYNSEG</sub> | SR | D | Sum of all the dynamic and static                                     | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                            | _   | _                                                                                                                                                                                                                                                                                | 110  | mA   |

|                     |    | D | I/O current within a supply seg-<br>ment                              | V <sub>DD</sub> = 3.3 V ±10%, PAD3V5V = 1                                         | _   | _                                                                                                                                                                                                                                                                                | 65   |      |

| IAVGSEG             | SR | D | Sum of all the static I/O current                                     | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                            | —   |                                                                                                                                                                                                                                                                                  | 70   | mA   |

|                     |    | D | within a supply segment                                               | $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$                            | —   | _                                                                                                                                                                                                                                                                                | 65   |      |

| IDDMxAVG            | SR | D | Sum of currents of two motors assigned to segment V <sub>DDMx</sub> , | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>T <sub>J</sub> = 130 °C | —   |                                                                                                                                                                                                                                                                                  | 90   |      |

|                     |    |   | V <sub>SSMx</sub> pair                                                | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>T <sub>J</sub> = -40 °C | —   |                                                                                                                                                                                                                                                                                  | 120  |      |

| Table 37. | I/O | consumption | n (continued) |  |

|-----------|-----|-------------|---------------|--|

|           |     |             |               |  |

$^{1}$  V\_{DD} = 3.3 V  $\pm 10\%$  / 5.0 V  $\pm 10\%$  , T\_A = -40 to 105 °C, unless otherwise specified

# 3.9 SSD specifications

# 3.9.1 Electrical characteristics

#### Table 38. SSD electrical characteristics

| Symbol               |    | с | Parameter                                      |                    |                     | Unit               |      |

|----------------------|----|---|------------------------------------------------|--------------------|---------------------|--------------------|------|

| Symbol               |    | C | Falance                                        | Min                | Тур                 | Мах                | onit |

| V <sub>VREF</sub>    | CC | Ρ | Reference voltage (I <sub>VREF</sub> = 0)      | $V_{DDM}/2 - 0.03$ | V <sub>DDM</sub> /2 | $V_{DDM}/2 + 0.03$ | V    |

| I <sub>VREF</sub>    | CC | Ρ | Reference voltage output current               | 1.85               | _                   | —                  | mA   |

| R <sub>IN</sub>      | CC | D | Input resistance (against V <sub>DDM</sub> /2) | 0.8                | 1.0                 | 1.2                | MΩ   |

| V <sub>IN</sub>      | CC | С | Input common mode range                        | V <sub>SSM</sub>   | _                   | V <sub>DDM</sub>   | V    |

| SSD <sub>CONST</sub> | СС | С | SSD constant                                   | 0.549              | 0.572               | 0.597              | _    |

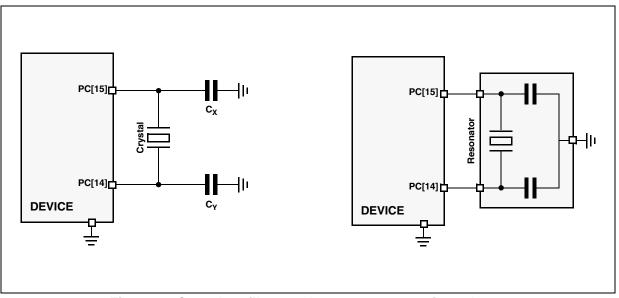

Figure 19. Crystal oscillator and resonator connection scheme

### NOTE

PC[14]/PC[15] must not be directly used to drive external circuits.

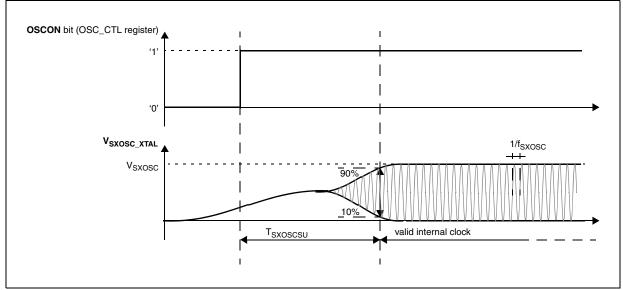

Figure 20. Slow external crystal oscillator (32 KHz) timing

| Symb                | al | с | Parameter                                                                                        | Conditions <sup>1</sup>                                              |                       | Value |                        | Unit |

|---------------------|----|---|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------|-------|------------------------|------|

| Symb                | 01 | C | Farameter                                                                                        | Conditions                                                           | Min                   | Тур   | Max                    | Unit |

| V <sub>SSA</sub>    | SR | D | Voltage on VSSA (ADC<br>reference) pin with<br>respect to ground (V <sub>SS</sub> ) <sup>2</sup> | _                                                                    | -0.1                  |       | 0.1                    | V    |

| V <sub>DDA</sub>    | SR | D | Voltage on VDDA pin<br>(ADC reference) with<br>respect to ground (V <sub>SS</sub> )              | _                                                                    | V <sub>DD</sub> – 0.1 | _     | V <sub>DD</sub> + 0.1  | V    |

| V <sub>AINx</sub>   | SR | D | Analog input voltage <sup>3</sup>                                                                | —                                                                    | $V_{SSA} - 0.1$       | —     | V <sub>DDA</sub> + 0.1 | V    |

| f <sub>ADC</sub>    | SR | D | ADC analog frequency <sup>4</sup>                                                                | _                                                                    | 6                     | —     | 32                     | MHz  |

| t <sub>ADC_PU</sub> | SR | D | ADC power up delay                                                                               | —                                                                    | —                     |       | 1.5                    | μs   |

| t <sub>ADC_S</sub>  | СС | Т | Sample time <sup>5,6</sup>                                                                       | f <sub>ADC</sub> = 32 MHz,<br>ADC_conf_sample_input = 17             | 0.5                   | —     | —                      | μs   |

|                     |    | Т |                                                                                                  | f <sub>ADC</sub> = 6 MHz,<br>ADC_conf_sample_input = 127             | _                     | —     | 21                     |      |

| t <sub>ADC_C</sub>  | СС | Т | Conversion time <sup>7</sup> $f_{ADC} = 32 \text{ MHz},$<br>ADC_conf_comp = 2                    |                                                                      | 0.625                 | _     | —                      | μs   |

| C <sub>S</sub>      | СС | D | ADC input sampling — — capacitance                                                               |                                                                      | _                     | —     | 3                      | pF   |

| C <sub>P1</sub>     | СС | D | ADC input pin<br>capacitance 1                                                                   | _                                                                    |                       | —     | 3                      | pF   |

| C <sub>P2</sub>     | СС | D | ADC input pin<br>capacitance 2                                                                   | _                                                                    |                       | —     | 1                      | pF   |

| C <sub>P3</sub>     | СС | D | ADC input pin<br>capacitance 3                                                                   | _                                                                    | —                     | —     | 1                      | pF   |

| R <sub>SW1</sub>    | СС | D | Internal resistance of<br>analog source                                                          | _                                                                    |                       | —     | 1                      | kΩ   |

| R <sub>SW2</sub>    | СС | D | Internal resistance of<br>analog source                                                          | _                                                                    |                       |       | 1                      | kΩ   |

| R <sub>AD</sub>     | СС | D | Internal resistance of<br>analog source                                                          | _                                                                    |                       | -     | 0.1                    | kΩ   |

| I <sub>INJ</sub>    | SR | Т | Input current Injection                                                                          | Current injection on one ADC input, different from the converted one | -5                    |       | 5                      | mA   |

| INL                 | CC | Ρ | Integral Non Linearity                                                                           | No overload                                                          | 2.5                   |       | 2.5                    | LSB  |

| DNL                 | СС | Ρ | Differential Non Linearity                                                                       | No overload                                                          | -1.0                  | -     | 1.0                    | LSB  |

| OFS                 | СС | Т | Offset error                                                                                     | After offset cancellation                                            | —                     | 0.5   | —                      | LSB  |

| GNE                 | СС | Т | Gain error                                                                                       | _                                                                    | —                     | 0.6   | —                      | LSB  |

| TUEx                | СС | Ρ | Total unadjusted error for                                                                       | Without current injection                                            | -3                    | —     | 3                      | LSB  |

|                     |    | т | extended channel                                                                                 | With current injection                                               | -4                    |       | 4                      | 1    |

#### Table 50. ADC conversion characteristics

| No.                         | Pad                         | Ts  | Tswitchon <sup>1</sup><br>(ns) |     | R   | Rise/Fall <sup>2</sup><br>(ns) |      | Frequency<br>(MHz) |     |     | Current slew<br>(mA/ns) |     |     | Load drive<br>(pF) |

|-----------------------------|-----------------------------|-----|--------------------------------|-----|-----|--------------------------------|------|--------------------|-----|-----|-------------------------|-----|-----|--------------------|

|                             |                             | Min | Тур                            | Max | Min | Тур                            | Max  | Min                | Тур | Max | Min                     | Тур | Мах | (Pr)               |

| 2                           | Medium                      | 1   |                                | 15  | 3   |                                | 10   |                    | —   | 40  | 2.5                     |     | 7   | 25                 |

|                             |                             | 1   | _                              | 15  | 5   | _                              | 20   | _                  |     | 20  | 2.5                     |     | 7   | 50                 |

|                             |                             | 1   | _                              | 15  | 9   | _                              | 40   | _                  | —   | 13  | 2.5                     |     | 8   | 100                |

|                             |                             | 1   | _                              | 15  | 12  | _                              | 70   | _                  |     | 7   | 2.5                     |     | 8   | 200                |

| 3                           | Fast                        | 1   | —                              | 6   | 1   | —                              | 4    | —                  | —   | 100 | 18                      | —   | 55  | 25                 |

|                             |                             | 1   | _                              | 6   | 1.5 | —                              | 6    | _                  | —   | 80  | 18                      | —   | 55  | 50                 |

|                             |                             | 1   | _                              | 6   | 3   | _                              | 12   | _                  |     | 40  | 18                      |     | 55  | 100                |

|                             |                             | 1   | _                              | 6   | 5   | _                              | 16   | _                  | —   | 25  | 18                      |     | 55  | 200                |

| 4                           | Pull Up/Down<br>(5.5 V max) | —   | _                              | —   | —   | _                              | 5000 | _                  | —   | —   | _                       | —   | —   | 50                 |

| Parameter<br>Classification |                             |     | D                              |     |     | С                              |      |                    | С   |     |                         | С   |     | n/a                |

Table 52. Pad AC specifications (5.0 V, PAD3V5V = 0)<sup>1</sup> (continued)

<sup>1</sup> Propagation delay from V<sub>DD</sub>/2 of internal signal to Pchannel/Nchannel on condition <sup>2</sup> Slope at rising/falling edge

| No.  | Pad    | Tswitchon <sup>1</sup><br>(ns) |     | on <sup>1</sup> | Rise/Fall <sup>2</sup><br>(ns) |     | Frequency<br>(MHz) |     |     | Current slew<br>(mA/ns) |      |     | Load drive |      |

|------|--------|--------------------------------|-----|-----------------|--------------------------------|-----|--------------------|-----|-----|-------------------------|------|-----|------------|------|

| 110. | i au   | Min                            | Тур | Мах             | Min                            | Тур | Мах                | Min | Тур | Мах                     | Min  | Тур | Мах        | (pF) |

| 1    | Slow   | 3                              |     | 40              | 4                              | _   | 40                 | _   |     | 4                       | 0.01 | _   | 2          | 25   |

|      |        | 3                              | —   | 40              | 6                              |     | 50                 |     | —   | 2                       | 0.01 | —   | 2          | 50   |

|      |        | 3                              | —   | 40              | 10                             |     | 75                 |     | —   | 2                       | 0.01 | —   | 2          | 100  |

|      |        | 3                              |     | 40              | 14                             | _   | 100                | _   | —   | 2                       | 0.01 | —   | 2          | 200  |

| 2    | Medium | 1                              | —   | 15              | 2                              | —   | 12                 | _   | —   | 40                      | 2.5  | —   | 7          | 25   |

|      |        | 1                              | —   | 15              | 4                              | _   | 25                 | _   | _   | 20                      | 2.5  | —   | 7          | 50   |

|      |        | 1                              | —   | 15              | 8                              | —   | 40                 | —   | —   | 13                      | 2.5  | —   | 7          | 100  |

|      |        | 1                              | _   | 15              | 14                             |     | 70                 | _   |     | 7                       | 2.5  | —   | 7          | 200  |

Table 53. Pad AC specifications  $(3.3 \text{ V}, \text{PAD3V5V} = 1)^1$

| Sym              | bol | С | Parameter               | Value                                               | Unit |

|------------------|-----|---|-------------------------|-----------------------------------------------------|------|

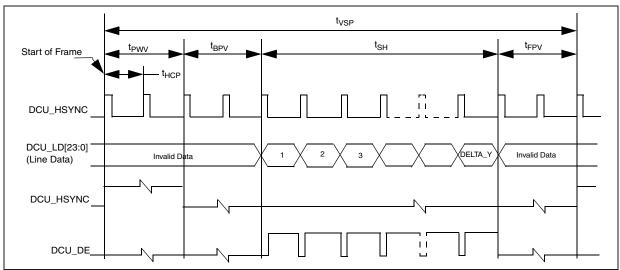

| t <sub>BPV</sub> | CC  | D | VSYNC back porch width  | $BP_V \times t_{HSP}$                               | ns   |

| t <sub>FPV</sub> | CC  | D | VSYNC front porch width | $FP_V \times t_{HSP}$                               | ns   |

| t <sub>SH</sub>  | CC  | D | Screen height           | $DELTA\_Y \times t_{HSP}$                           | ns   |

| t <sub>VSP</sub> | CC  | D | VSYNC (frame) period    | $(PW\_V + BP\_V + FP\_V + DELTA\_Y) \times t_{HSP}$ | ns   |

Table 57. LCD interface timing parameters—horizontal and vertical (continued)

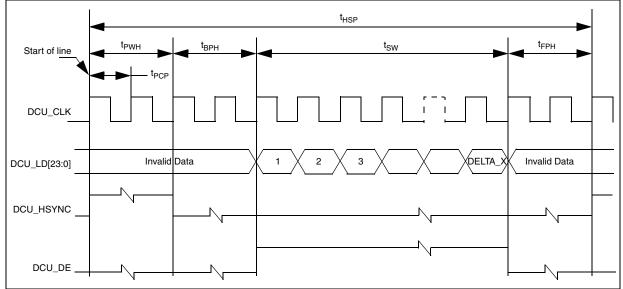

Figure 34. Horizontal sync timing

Figure 35. Vertical sync pulse

MPC5606S Microcontroller Data Sheet, Rev. 8

# 3.20.6 FlexCAN timing

The CAN functions are available as TX pins at normal I/O pads and as RX pins at the always on domain. There is no filter for the wakeup dominant pulse. Any high-to-low edge can cause wakeup if configured.

Table 61. FlexCAN timing<sup>1</sup>

| No. | Svmb               |    | с | Parameter                                                 | Va  | Unit  |      |

|-----|--------------------|----|---|-----------------------------------------------------------|-----|-------|------|

|     |                    |    | Ŭ | i didiletti                                               | Min | Max   | onit |

| 1   | t <sub>CANOV</sub> | CC | D | CTNX Output Valid after CLKOUT Rising Edge (Output Delay) |     | 22.48 | ns   |

| 2   | t <sub>CANSU</sub> | CC | D | CNRX Input Valid to CLKOUT Rising Edge (Setup Time)       | _   | 12.46 | ns   |

<sup>1</sup> FlexCAN timing specified at  $f_{SYS}$  = 64 MHz,  $V_{DD12}$  = 1.14 V to 1.32 V, VDDE\_x = 3.0 V to 5.5 V,  $T_A$  = -40 to 105 °C, and  $C_L$  = 50 pF with SRC = 0b00.

# 3.20.7 Deserial Serial Peripheral Interface (DSPI)

| Na  | o. Symbol         |      | _ | Parameter                                                                                                        | Conditions                                                                                            | Va                     | lue                    | Unit                 |

|-----|-------------------|------|---|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------|------------------------|----------------------|

| No. | Sym               | IDOI | С | Parameter                                                                                                        | Conditions                                                                                            | Min                    | Max                    | Unit                 |

| 1   | t <sub>SCK</sub>  | CC   | D | DSPI Cycle TIme <sup>2,3</sup>                                                                                   | Master (MTFE = 0)<br>Slave (MTFE = 0)<br>Slave Receive Only Mode                                      | 62<br>62<br>62         |                        | ns<br>ns<br>ns       |

| 2   | t <sub>CSC</sub>  | СС   | D | PCS to SCK Delay <sup>4</sup>                                                                                    | —                                                                                                     | 20                     | —                      | ns                   |

| 3   | t <sub>ASC</sub>  | СС   | D | After SCK Delay <sup>5</sup>                                                                                     | —                                                                                                     | 20                     | —                      | ns                   |

| 4   | t <sub>SDC</sub>  | СС   | D | SCK Duty Cycle                                                                                                   | —                                                                                                     | 0.4 x t <sub>SCK</sub> | 0.6 x t <sub>SCK</sub> | ns                   |

| 5   | t <sub>A</sub>    | CC   | D | Slave Access Time<br>(PCSx active to SOUT driven)                                                                | SS active to SOUT valid                                                                               | —                      | 40                     | ns                   |

| 6   | t <sub>DIS</sub>  | CC   | D | Slave SOUT Disable Time<br>(PCSx inactive to SOUT High-Z<br>or invalid)<br>SS inactive to SOUT High-Z<br>invalid |                                                                                                       | _                      | 10                     | ns                   |

| 7   | t <sub>PCSC</sub> |      |   | PCSx to PCSS time                                                                                                | —                                                                                                     | 20                     |                        | ns                   |

| 8   | t <sub>PASC</sub> |      |   | PCSS to PCSx time                                                                                                | —                                                                                                     | 20                     | —                      | ns                   |

| 9   | t <sub>SUI</sub>  | CC   | D | Data Setup Time for Inputs                                                                                       | Master (MTFE = 0)<br>Slave<br>Master (MTFE = 1, CPHA = 0) <sup>6</sup><br>Master (MTFE = 1, CPHA = 1) | 35<br>2<br>20<br>35    |                        | ns<br>ns<br>ns<br>ns |

| 10  | t <sub>HI</sub>   | CC   | D | Data Hold Time for Inputs                                                                                        | Master (MTFE = 0)<br>Slave<br>Master (MTFE = 1, CPHA = 0) <sup>6</sup><br>Master (MTFE = 1, CPHA = 1) | -5<br>5<br>10<br>-5    | <br>                   | ns<br>ns<br>ns<br>ns |

#### Table 62. DSPI timing<sup>1</sup>

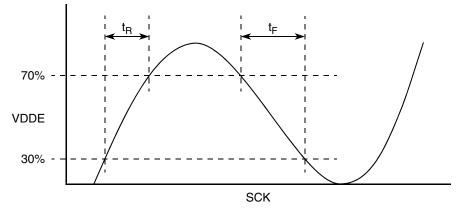

The clock profile in Figure 49 is measured at 30% to 70% levels of VDDE.

Figure 49. QuadSPI clock profile

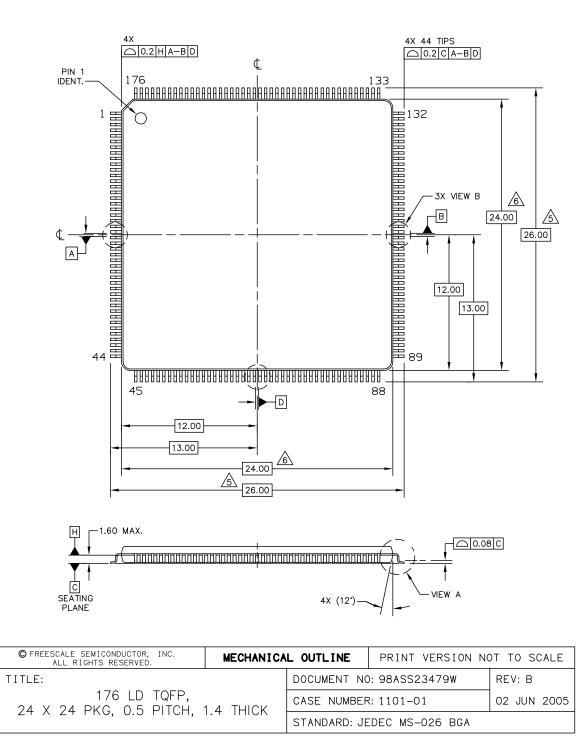

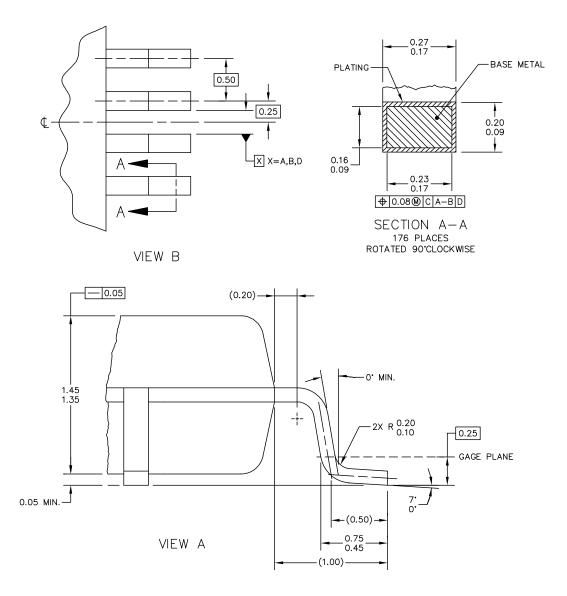

### 4.2 176 LQFP

Figure 53. LQFP176 mechanical drawing (Part 1 of 3)

MPC5606S Microcontroller Data Sheet, Rev. 8

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO  | : 98ASS23479W    | REV: B      |

| 176 LD TQFP,<br>24 X 24 PKG, 0.5 PITCH, 1.4             |           | CASE NUMBER  | 2: 1101-01       | 02 JUN 2005 |

|                                                         |           | STANDARD: JE | DEC MS-026 BGA   |             |

MPC5606S Microcontroller Data Sheet, Rev. 8

#### **Revision history**

| Revision | Date        | Substantive changes                                                                                                                                                    |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 14 Jan 2011 | Editorial changes and improvements.                                                                                                                                    |

|          |             | Swapped XTAL and EXTAL pins for the 208-pin BGA package and throughout.                                                                                                |

|          |             | In the "Pinout and signal descriptions" section, changed WARNING labels to CAUTION labels.                                                                             |

|          |             | Updated the "Absolute maximum ratings" and "Recommended operating conditions" tables.                                                                                  |

|          |             | Added footnote reference to V <sub>ss12</sub> in "Recommended operating conditions (3.3 V)" table.                                                                     |

|          |             | Updated the "Connecting power supply pins" section.                                                                                                                    |

|          |             | Removed footnote regarding characterization in the "Thermal characteristics" table.                                                                                    |

|          |             | Updated the V <sub>DD12</sub> /V <sub>DDPLL</sub> operating voltages in the "Electromagnetic interference" table.                                                      |

|          |             | Added typical values and updated the "Voltage regulator electrical characteristics,"<br>"Low-power voltage regulator electrical characteristics," and "Ultra-low-power |

|          |             | voltage regulator electrical characteristics" tables.                                                                                                                  |

|          |             | Updated classifications and values in the "Low voltage monitor electrical characteristics" table.                                                                      |

|          |             | Made major modifications and updates to the "DC electrical characteristics" table.                                                                                     |

|          |             | Made major modifications and updates to the "I/O input DC electrical characteristics" table.                                                                           |

|          |             | Made major modifications and updates to the "I/O pull-up/pull-down DC electrical characteristics" table.                                                               |

|          |             | Changed "SMC" pads to "SMD" pads throughout.                                                                                                                           |

|          |             | Made updates to the "SMD pad electrical characteristics" table.                                                                                                        |

|          |             | Added run current during RESET to the "Reset electrical characteristics" table.                                                                                        |

|          |             | Updated the FMPLL jitter (peak to peak) specification in the "FMPLL electrical characteristics" table.                                                                 |

|          |             | Updated f <sub>FIRC</sub> and t <sub>FIRCSU</sub> in the "Fast internal RC oscillator (16 MHz) electrical characteristics" table.                                      |

|          |             | Updated f <sub>SIRC</sub> and t <sub>SIRCSU</sub> in the "Slow internal RC oscillator (128 kHz) electrical characteristics" table.                                     |

|          |             | Removed "symmetric" pad type from the "Pad AC specifications (5.0 V, PAD3V5V = 0)" table.                                                                              |

|          |             | Removed "symmetric" pad type from the "Pad AC specifications (3.3 V, PAD3V5V = 1)" table.                                                                              |

|          |             | Updated V <sub>DD12</sub> post-trimming minimum value in the "Low-power voltage regulator electrical characteristics" table.                                           |

|          |             | Updated V <sub>DD12</sub> post-trimming minimum value in the "Ultra-low-power voltage regulator electrical characteristics" table.                                     |

|          |             | Updated V <sub>LVDLVCORH</sub> maximum value in the "Low voltage monitor electrical characteristics" table.                                                            |

|          |             | Updated V <sub>LVDLVCORL</sub> minimum value in the "Low voltage monitor electrical characteristics" table.                                                            |

|          |             | Updated value of V <sub>DD12</sub> /V <sub>DDPLL</sub> operating voltages in the "Input DC electrical characteristics" table.                                          |

|          |             | Corrected erroneous value of I <sub>LKG</sub> (105°C case) in the "Input DC electrical characteristics" table.                                                         |

### Table 66. Document revision history