#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | Coldfire V2                                                |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 80MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                 |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 56                                                         |

| Program Memory Size        | 256KB (256K x 8)                                           |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 32K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                  |

| Data Converters            | A/D 8x12b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 81-LBGA                                                    |

| Supplier Device Package    | 81-MAPBGA (10x10)                                          |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf52223cvm80 |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Famil | y Configurations                          |

|---|-------|-------------------------------------------|

|   | 1.1   | Block Diagram                             |

|   | 1.2   | Features                                  |

|   | 1.3   | Reset Signals                             |

|   | 1.4   | PLL and Clock Signals                     |

|   | 1.5   | Mode Selection                            |

|   | 1.6   | External Interrupt Signals                |

|   | 1.7   | Queued Serial Peripheral Interface (QSPI) |

|   | 1.8   | USB On-the-Go                             |

|   | 1.9   | I <sup>2</sup> C I/O Signals              |

|   | 1.10  | UART Module Signals                       |

|   | 1.11  | DMA Timer Signals                         |

|   | 1.12  | ADC Signals                               |

|   | 1.13  | General Purpose Timer Signals             |

|   | 1.14  | Pulse Width Modulator Signals             |

|   | 1.15  | Debug Support Signals                     |

|   | 1.16  | EzPort Signal Descriptions                |

|   | 1.17  | Power and Ground Pins                     |

| 2 | Elect | rical Characteristics                     |

|   | 2.1   | Maximum Ratings                           |

|   | 2.2   | Current Consumption                       |

|   |       |                                           |

|   | 2.3   | Thermal Characteristics                             |

|---|-------|-----------------------------------------------------|

|   | 2.4   | Flash Memory Characteristics                        |

|   | 2.5   | EzPort Electrical Specifications                    |

|   | 2.6   | ESD Protection                                      |

|   | 2.7   | DC Electrical Specifications                        |

|   | 2.8   | Clock Source Electrical Specifications              |

|   | 2.9   | General Purpose I/O Timing                          |

|   | 2.10  | Reset Timing                                        |

|   | 2.11  | I <sup>2</sup> C Input/Output Timing Specifications |

|   | 2.12  | Analog-to-Digital Converter (ADC) Parameters        |

|   | 2.12  | Equivalent Circuit for ADC Inputs                   |

|   | 2.14  | DMA Timers Timing Specifications                    |

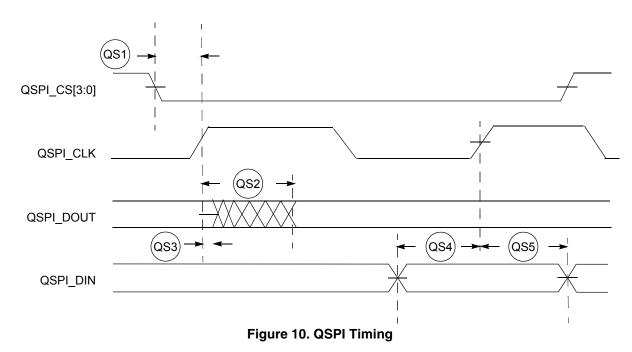

|   | 2.14  | QSPI Electrical Specifications                      |

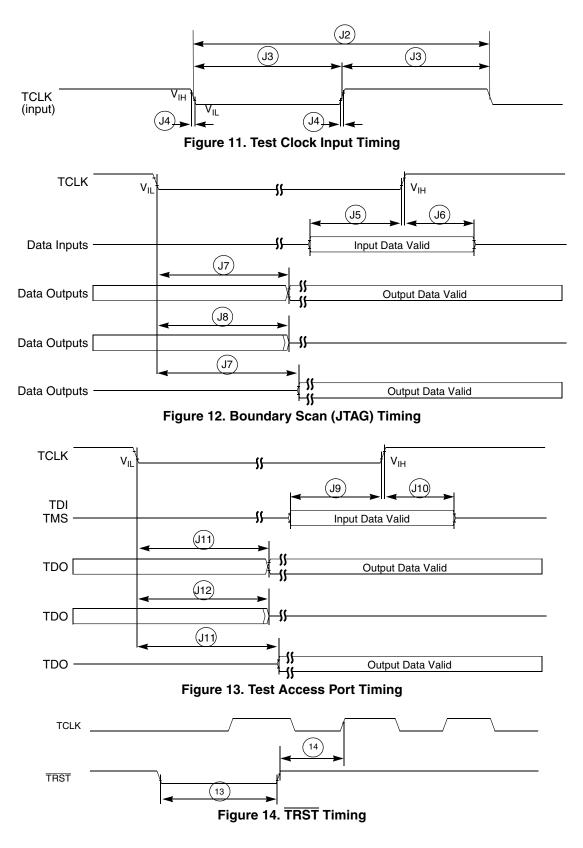

|   | 2.15  | JTAG and Boundary Scan Timing                       |

|   |       |                                                     |

| ~ | 2.17  | Debug AC Timing Specifications                      |

| 3 |       | nanical Outline Drawings                            |

|   | 3.1   | 64-pin LQFP Package 44                              |

|   | 3.2   | 81 MAPBGA Package 50                                |

|   | 3.3   | 100-pin LQFP Package 52                             |

| 4 | Revis | sion History 54                                     |

NP

#### Family Configurations

- 16-bit counter

- Selectable as free running or count down

- Real-Time Clock (RTC)

- Maintains system time-of-day clock

- Provides stopwatch and alarm interrupt functions

- Software watchdog timer

- 32-bit counter

- Low-power mode support

- Clock generation features

- Crystal, on-chip trimmed relaxation oscillator, or external oscillator reference options

- Trimmed relaxation oscillator

- Pre-divider capable of dividing the clock source frequency into the PLL reference frequency range

- System can be clocked from PLL or directly from crystal oscillator or relaxation oscillator

- Low power modes supported

- $2^n (0 \le n \le 15)$  low-power divider for extremely low frequency operation

- Interrupt controller

- Uniquely programmable vectors for all interrupt sources

- Fully programmable level and priority for all peripheral interrupt sources

- Seven external interrupt signals with fixed level and priority

- Unique vector number for each interrupt source

- Ability to mask any individual interrupt source or all interrupt sources (global mask-all)

- Support for hardware and software interrupt acknowledge (IACK) cycles

- Combinatorial path to provide wake-up from low-power modes

- DMA controller

- Four fully programmable channels

- Dual-address transfer support with 8-, 16-, and 32-bit data capability, along with support for 16-byte (4×32-bit) burst transfers

- Source/destination address pointers that can increment or remain constant

- 24-bit byte transfer counter per channel

- Auto-alignment transfers supported for efficient block movement

- Bursting and cycle-steal support

- Software-programmable DMA requests for the UARTs (3) and 32-bit timers (4)

- Reset

- Separate reset in and reset out signals

- Seven sources of reset:

- Power-on reset (POR)

- External

- Software

- Watchdog

- Loss of clock

- Loss of lock

- Low-voltage detection (LVD)

- Status flag indication of source of last reset

- Chip configuration module (CCM)

- System configuration during reset

## 1.2.20 DMA Controller

The direct memory access (DMA) controller provides an efficient way to move blocks of data with minimal processor intervention. It has four channels that allow byte, word, longword, or 16-byte burst line transfers. These transfers are triggered by software explicitly setting a DCR*n*[START] bit or by the occurrence of certain UART or DMA timer events.

## 1.2.21 Reset

The reset controller determines the source of reset, asserts the appropriate reset signals to the system, and keeps track of what caused the last reset. There are seven sources of reset:

- External reset input

- Power-on reset (POR)

- Watchdog timer

- Phase locked-loop (PLL) loss of lock

- PLL loss of clock

- Software

- Low-voltage detector (LVD)

Control of the LVD and its associated reset and interrupt are managed by the reset controller. Other registers provide status flags indicating the last source of reset and a control bit for software assertion of the  $\overline{\text{RSTO}}$  pin.

## 1.2.22 GPIO

Nearly all pins on the device have general purpose I/O capability and are grouped into 8-bit ports. Some ports do not use all eight bits. Each port has registers that configure, monitor, and control the port pin.

## 1.2.23 Part Numbers and Packaging

This product is RoHS-compliant. Refer to the product page at freescale.com or contact your sales office for up-to-date RoHS information.

| Freescale Part<br>Number | Description              | Speed<br>(MHz) | Flash/SRAM<br>(Kbytes) | Package   | Temp range<br>(°C) |

|--------------------------|--------------------------|----------------|------------------------|-----------|--------------------|

| MCF52221CAE66            | MCF52221 Microcontroller | 66             | 128/16                 | 64 LQFP   | -40 to +85         |

| MCF52221CVM66            | MCF52221 Microcontroller | 66             | 128/16                 | 81 MAPBGA | -40 to +85         |

| MCF52221CAF66            | MCF52221 Microcontroller | 66             | 128/16                 | 100 LQFP  | -40 to +85         |

| MCF52221CVM80            | MCF52221 Microcontroller | 80             | 128/16                 | 81 MAPBGA | -40 to +85         |

| MCF52221CAF80            | MCF52221 Microcontroller | 80             | 128/16                 | 100 LQFP  | -40 to +85         |

| MCF52223CVM66            | MCF52223 Microcontroller | 66             | 128/16                 | 81 MAPBGA | -40 to +85         |

| MCF52223CAF66            | MCF52223 Microcontroller | 66             | 128/16                 | 100 LQFP  | -40 to +85         |

| MCF52223CVM80            | MCF52223 Microcontroller | 80             | 128/16                 | 81 MAPBGA | -40 to +85         |

| MCF52223CAF80            | MCF52223 Microcontroller | 80             | 128/16                 | 100 LQFP  | -40 to +85         |

### **Table 3. Orderable Part Number Summary**

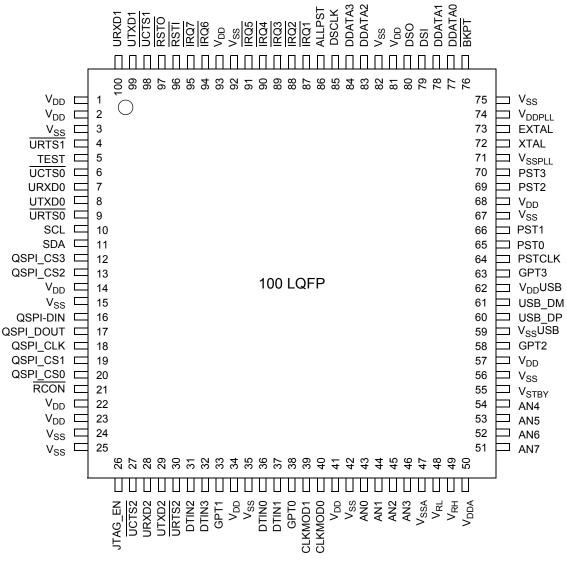

Figure 5 shows the pinout configuration for the 100 LQFP.

Figure 2. 100 LQFP Pin Assignments

19

| Pin<br>Group | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP                      | Pin on 81<br>MAPBGA      | Pin on 64<br>LQFP  |

|--------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------|--------------------------|--------------------|

| UART 1       | UCTS1               | SYNCA                 | URXD2                | GPIO                   | PDSR[15]                                    | PSRR[15]                            | —                                   | 98                                      | C3                       | 61                 |

|              | URTS1               | SYNCB                 | UTXD2                | GPIO                   | PDSR[14]                                    | PSRR[14]                            | —                                   | 4                                       | B1                       | 2                  |

|              | URXD1               | —                     | —                    | GPIO                   | PDSR[13]                                    | PSRR[13]                            | —                                   | 100                                     | B2                       | 63                 |

|              | UTXD1               | —                     | —                    | GPIO                   | PDSR[12]                                    | PSRR[12]                            | —                                   | 99                                      | A2                       | 62                 |

| UART 2       | UCTS2               | —                     | —                    | GPIO                   | PDSR[27]                                    | PSRR[27]                            | —                                   | 27                                      | —                        | —                  |

|              | URTS2               | —                     | —                    | GPIO                   | PDSR[26]                                    | PSRR[26]                            | —                                   | 30                                      | —                        | —                  |

|              | URXD2               | —                     | —                    | GPIO                   | PDSR[25]                                    | PSRR[25]                            | —                                   | 28                                      | _                        |                    |

|              | UTXD2               | —                     | —                    | GPIO                   | PDSR[24]                                    | PSRR[24]                            | —                                   | 29                                      | —                        | —                  |

| VSTBY        | VSTBY               | —                     | —                    | —                      | N/A                                         | N/A                                 | —                                   | 55                                      | F8                       | 37                 |

| USB          | VDDUSB              | —                     | _                    | —                      | N/A                                         | N/A                                 | —                                   | 62                                      | D8                       | 43                 |

|              | VSSUSB              | —                     | —                    | —                      | N/A                                         | N/A                                 | —                                   | 59                                      | F7                       | 40                 |

|              | USB_DM              | —                     | —                    | —                      | N/A                                         | N/A                                 | —                                   | 61                                      | D9                       | 42                 |

|              | USB_DP              | —                     | —                    | —                      | N/A                                         | N/A                                 | —                                   | 60                                      | E9                       | 41                 |

| VDD          | VDD                 | —                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 1,2,14,22,<br>23,34,41,<br>57,68,81,93  | D5,E3–E7,<br>F5          | 1,10,20,39,<br>2   |

| VSS          | VSS                 | —                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 3,15,24,25,3<br>5,42,56,<br>67,75,82,92 | A1,A9,D4,D<br>6,F4,F6,J1 | 11,21,38,<br>53,64 |

### Table 4. Pin Functions by Primary and Alternate Purpose (continued)

The PDSR and PSSR registers are described in the General Purpose I/O chapter. All programmable signals default to 2 mA drive and FAST slew rate in <sup>2</sup> All signals have a pull-up in GPIO mode.

<sup>3</sup> These signals are multiplexed on other pins.

For primary and GPIO functions only.

Only when JTAG mode is enabled.

CLKMOD0 and CLKMOD1 have internal pull-down resistors; however, the use of external resistors is very strongly recommended.

<sup>7</sup> When these pins are configured for USB signals, they should use the USB transceiver's internal pull-up/pull-down resistors (see the description of the OTG\_CTRL register). If these pins are not configured for USB signals, each pin should be pulled down externally using a 10 kΩ resistor.

<sup>8</sup> For secondary and GPIO functions only.

<sup>9</sup> RSTI has an internal pull-up resistor; however, the use of an external resistor is very strongly recommended.

<sup>10</sup> For GPIO function. Primary Function has pull-up control within the GPT module.

# 1.17 Power and Ground Pins

The pins described in Table 19 provide system power and ground to the chip. Multiple pins are provided for adequate current capability. All power supply pins must have adequate bypass capacitance for high-frequency noise suppression.

| Signal Name       | Abbreviation        | Function                                                                                                                                          |

|-------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL Analog Supply | VDDPLL,<br>VSSPLL   | Dedicated power supply signals to isolate the sensitive PLL analog circuitry from the normal levels of noise present on the digital power supply. |

| USB Power Supply  | V <sub>DD</sub> USB | This pin supplies power to the USB Module.                                                                                                        |

| USB Ground Supply | V <sub>SS</sub> USB | This pin is the negative (ground) supply pin for the USB Module.                                                                                  |

| Positive Supply   | VDD                 | These pins supply positive power to the core logic.                                                                                               |

| Ground            | VSS                 | This pin is the negative supply (ground) to the chip.                                                                                             |

### Table 19. Power and Ground Pins

# 2.2 Current Consumption

Table 21, Table 22, and Figure 5 show the typical current consumption in low-power modes.

Table 21. Current Consumption in Low-Power Mode, Code From Flash Memory<sup>1,2,3</sup>

| Mode                                 | 8 MHz (Typ) | 16 MHz (Typ) | 64 MHz (Typ) | 80 MHz (Typ) | Units |  |  |

|--------------------------------------|-------------|--------------|--------------|--------------|-------|--|--|

| Stop mode 3 (Stop 11) <sup>4</sup>   |             | 0.0          | )70          |              | mA    |  |  |

| Stop mode 2 (Stop 10) <sup>4</sup>   |             | 2.9          |              |              |       |  |  |

| Stop mode 1 (Stop 01) <sup>4,5</sup> | 3.6         | 3.9          | 6            | 6.7          |       |  |  |

| Stop mode 0 (Stop 00) <sup>5</sup>   | 3.6         | 3.9          | 6            | 6.7          |       |  |  |

| Wait / Doze                          | 13          | 23           | 38           | 44           |       |  |  |

| Run                                  | TBD         | TBD          | TBD          | TBD          |       |  |  |

<sup>1</sup> All values are measured with a 3.30V power supply. Tests performed at room temperature.

<sup>2</sup> Refer to the Power Management chapter in the *MCF52223 Reference Manual* for more information on low-power modes.

<sup>3</sup> CLKOUT, PST/DDATA signals, and all peripheral clocks except UART0 and CFM off before entering low-power mode. CLKOUT is disabled.

<sup>4</sup> See the description of the Low-Power Control Register (LPCR) in the *MCF52223 Reference Manual* for more information on stop modes 0–3.

<sup>5</sup> Results are identical to STOP 00 for typical values because they only differ by CLKOUT power consumption. CLKOUT is already disabled in this instance prior to entering low-power mode.

Table 22. Current Consumption in Low-Power Mode, Code From SRAM<sup>1,2,3</sup>

| Mode                                 | 8 MHz (Typ) | 16 MHz (Typ) | 64 MHz (Typ) | 80 MHz (Typ) | Units |

|--------------------------------------|-------------|--------------|--------------|--------------|-------|

| Stop mode 3 (Stop 11) <sup>4</sup>   |             | 0.0          | 010          |              | mA    |

| Stop mode 2 (Stop 10) <sup>4</sup>   |             | 2            | .7           |              |       |

| Stop mode 1 (Stop 01) <sup>4,5</sup> | 3.4         | 3.7          | 5.8          | 6.5          |       |

| Stop mode 0 (Stop 00) <sup>5</sup>   | 3.4         | 3.7          | 5.8          | 6.5          |       |

| Wait / Doze                          | 6           | 8            | 22           | 27           |       |

| Run                                  | 7           | 11           | 33           | 41           |       |

<sup>1</sup> All values are measured with a 3.30V power supply. Tests performed at room temperature.

<sup>2</sup> Refer to the Power Management chapter in the *MCF52223 Reference Manual* for more information on low-power modes.

<sup>3</sup> CLKOUT, PST/DDATA signals, and all peripheral clocks except UART0 off before entering low-power mode. CLKOUT is disabled. Code executed from SRAM with flash memory shut off by writing 0x0 to the FLASHBAR register.

<sup>4</sup> See the description of the Low-Power Control Register (LPCR) in the MCF52223 Reference Manual for more information on stop modes 0–3.

<sup>5</sup> Results are identical to STOP 00 for typical values because they only differ by CLKOUT power consumption. CLKOUT is already disabled in this instance prior to entering low-power mode.

## 2.5 **EzPort Electrical Specifications**

### Table 27. EzPort Electrical Specifications

| Name | Characteristic                                         | Min                | Max                  | Unit |

|------|--------------------------------------------------------|--------------------|----------------------|------|

| EP1  | EPCK frequency of operation (all commands except READ) |                    | f <sub>sys</sub> / 2 | MHz  |

| EP1a | EPCK frequency of operation (READ command)             | _                  | f <sub>sys</sub> / 8 | MHz  |

| EP2  | EPCS_b negation to next EPCS_b assertion               | $2 \times T_{cyc}$ | _                    | ns   |

| EP3  | EPCS_B input valid to EPCK high (setup)                | 5                  | _                    | ns   |

| EP4  | EPCK high to EPCS_B input invalid (hold)               | 5                  | _                    | ns   |

| EP5  | EPD input valid to EPCK high (setup)                   | 2                  | _                    | ns   |

| EP6  | EPCK high to EPD input invalid (hold)                  | 5                  |                      | ns   |

| EP7  | EPCK low to EPQ output valid (out setup)               | _                  | 12                   | ns   |

| EP8  | EPCK low to EPQ output invalid (out hold)              | 0                  | _                    | ns   |

| EP9  | EPCS_B negation to EPQ tri-state                       |                    | 12                   | ns   |

## 2.6 ESD Protection

### Table 28. ESD Protection Characteristics<sup>1, 2</sup>

| Characteristics                                                                            | Symbol              | Value  | Units |

|--------------------------------------------------------------------------------------------|---------------------|--------|-------|

| ESD target for Human Body Model                                                            | HBM                 | 2000   | V     |

| ESD target for Machine Model                                                               | MM                  | 200    | V     |

| HBM circuit description                                                                    | R <sub>series</sub> | 1500   | Ω     |

|                                                                                            | С                   | 100    | pF    |

| MM circuit description                                                                     | R <sub>series</sub> | 0      | Ω     |

|                                                                                            | С                   | 200    | pF    |

| Number of pulses per pin (HBM)<br>• Positive pulses<br>• Negative pulses                   |                     | 1<br>1 | —     |

| Number of pulses per pin (MM) <ul> <li>Positive pulses</li> <li>Negative pulses</li> </ul> |                     | 3<br>3 | _     |

| Interval of pulses                                                                         | —                   | 1      | sec   |

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing is performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

# 2.7 DC Electrical Specifications

Table 29. DC Electrical Specifications <sup>1</sup>

| Characteristic                                                                                                      | Symbol              | Min                   | Мах                  | Unit |

|---------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|----------------------|------|

| Supply voltage                                                                                                      | V <sub>DD</sub>     | 3.0                   | 3.6                  | V    |

| Standby voltage                                                                                                     | V <sub>STBY</sub>   | 1.8                   | 3.6                  | V    |

| Input high voltage                                                                                                  | V <sub>IH</sub>     | $0.7 	imes V_{DD}$    | 4.0                  | V    |

| Input low voltage                                                                                                   | V <sub>IL</sub>     | V <sub>SS</sub> – 0.3 | $0.35 \times V_{DD}$ | V    |

| Input hysteresis <sup>2</sup>                                                                                       | V <sub>HYS</sub>    | $0.06 \times V_{DD}$  | _                    | mV   |

| Low-voltage detect trip voltage (V <sub>DD</sub> falling)                                                           | V <sub>LVD</sub>    | 2.15                  | 2.3                  | V    |

| Low-voltage detect hysteresis (V <sub>DD</sub> rising)                                                              | V <sub>LVDHYS</sub> | 60                    | 120                  | mV   |

| Input leakage current $V_{in} = V_{DD}$ or $V_{SS}$ , digital pins                                                  | l <sub>in</sub>     | -1.0                  | 1.0                  | μA   |

| Output high voltage (all input/output and all output pins) $I_{OH} = -2.0 \text{ mA}$                               | V <sub>OH</sub>     | V <sub>DD</sub> – 0.5 | _                    | V    |

| Output low voltage (all input/output and all output pins) $I_{OL} = 2.0 \text{mA}$                                  | V <sub>OL</sub>     | _                     | 0.5                  | V    |

| Output high voltage (high drive)<br>I <sub>OH</sub> = -5 mA                                                         | V <sub>OH</sub>     | V <sub>DD</sub> – 0.5 | _                    | V    |

| Output low voltage (high drive)<br>I <sub>OL</sub> = 5 mA                                                           | V <sub>OL</sub>     |                       | 0.5                  | V    |

| Output high voltage (low drive)<br>I <sub>OH</sub> = -2 mA                                                          | V <sub>OH</sub>     | V <sub>DD</sub> - 0.5 | _                    | V    |

| Output low voltage (low drive)<br>I <sub>OL</sub> = 2 mA                                                            | V <sub>OL</sub>     | _                     | 0.5                  | V    |

| Weak internal pull Up device current, tested at $V_{IL}$ Max. <sup>3</sup>                                          | I <sub>APU</sub>    | -10                   | -130                 | μA   |

| Input Capacitance <sup>4</sup> <ul> <li>All input-only pins</li> <li>All input/output (three-state) pins</li> </ul> | C <sub>in</sub>     | _                     | 7<br>7               | pF   |

<sup>1</sup> Refer to Table 30 for additional PLL specifications.

<sup>2</sup> Only for pins: IRQ1, IRQ2. IRQ3, IRQ4, IRQ5, IRQ6. IRQ7, RSTIN\_B, RCON\_B, PCS0, SCK, I2C\_SDA, I2C\_SCL, TCLK, TRST\_B

<sup>3</sup> Refer to Table 13 for pins having internal pull-up devices.

<sup>4</sup> This parameter is characterized before qualification rather than 100% tested.

## 2.8 Clock Source Electrical Specifications

### Table 30. Oscillator and PLL Electrical Specifications

| Characteristic                                                                                                                                                           | Symbol                                   | Min                        | Max                                                  | Unit               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|------------------------------------------------------|--------------------|

| Clock Source Frequency Range of EXTAL Frequency Range<br>• Crystal<br>• External <sup>1</sup>                                                                            | f <sub>crystal</sub><br>f <sub>ext</sub> | 1<br>0                     | 25.0 <sup>2</sup><br>66.67 or 80                     | MHz                |

| PLL reference frequency range                                                                                                                                            | f <sub>ref_pll</sub>                     | 2                          | 10.0                                                 | MHz                |

| System frequency <sup>3</sup><br>• External clock mode<br>• On-chip PLL frequency                                                                                        | f <sub>sys</sub>                         | 0<br>f <sub>ref</sub> / 32 | 66.67 or 80 <sup>4</sup><br>66.67 or 80 <sup>4</sup> | MHz                |

| Loss of reference frequency <sup>5, 7</sup>                                                                                                                              | f <sub>LOR</sub>                         | 100                        | 1000                                                 | kHz                |

| Self clocked mode frequency <sup>6</sup>                                                                                                                                 | f <sub>SCM</sub>                         | 1                          | 5                                                    | MHz                |

| Crystal start-up time <sup>7, 8</sup>                                                                                                                                    | t <sub>cst</sub>                         | _                          | 10                                                   | ms                 |

| EXTAL input high voltage <ul> <li>External reference</li> </ul>                                                                                                          | V <sub>IHEXT</sub>                       | 2.0                        | 3.0 <sup>2</sup>                                     | V                  |

| EXTAL input low voltage <ul> <li>External reference</li> </ul>                                                                                                           | V <sub>ILEXT</sub>                       | V <sub>SS</sub>            | 0.8                                                  | V                  |

| PLL lock time <sup>4,9</sup>                                                                                                                                             | t <sub>ipii</sub>                        | _                          | 500                                                  | μS                 |

| Duty cycle of reference <sup>4</sup>                                                                                                                                     | t <sub>dc</sub>                          | 40                         | 60                                                   | % f <sub>ref</sub> |

| Frequency un-LOCK range                                                                                                                                                  | f <sub>UL</sub>                          | -1.5                       | 1.5                                                  | % f <sub>ref</sub> |

| Frequency LOCK range                                                                                                                                                     | f <sub>LCK</sub>                         | -0.75                      | 0.75                                                 | % f <sub>ref</sub> |

| CLKOUT period jitter <sup>4, 5, 10,11</sup> , measured at f <sub>SYS</sub> Max<br>• Peak-to-peak (clock edge to clock edge)<br>• Long term (averaged over 2 ms interval) | C <sub>jitter</sub>                      | _                          | 10<br>.01                                            | % f <sub>sys</sub> |

| On-chip oscillator frequency                                                                                                                                             | f <sub>oco</sub>                         | 7.84                       | 8.16                                                 | MHz                |

<sup>1</sup> In external clock mode, it is possible to run the chip directly from an external clock source without enabling the PLL.

<sup>2</sup> This value has been updated.

<sup>3</sup> All internal registers retain data at 0 Hz.

<sup>4</sup> Depending on packaging; see the orderable part number summary.

- <sup>5</sup> Loss of Reference Frequency is the reference frequency detected internally, which transitions the PLL into self clocked mode.

- <sup>6</sup> Self clocked mode frequency is the frequency at which the PLL operates when the reference frequency falls below f<sub>LOR</sub> with default MFD/RFD settings.

- <sup>7</sup> This parameter is characterized before qualification rather than 100% tested.

- <sup>8</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>9</sup> This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- <sup>10</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>sys</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>jitter</sub> percentage for a given interval.

- $^{11}$  Based on slow system clock of 40 MHz measured at  $\rm f_{sys}$  max.

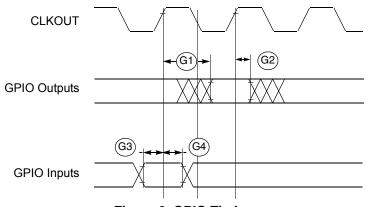

# 2.9 General Purpose I/O Timing

GPIO can be configured for certain pins of the QSPI, DDR Control, timer, UART, Interrupt and USB interfaces. When in GPIO mode, the timing specification for these pins is given in Table 31 and Figure 6.

The GPIO timing is met under the following load test conditions:

- 50 pF / 50  $\Omega$  for high drive

- $25 \text{ pF} / 25 \Omega$  for low drive

### Table 31. GPIO Timing

| NUM | Characteristic                     | Symbol             | Min | Мах | Unit |

|-----|------------------------------------|--------------------|-----|-----|------|

| G1  | CLKOUT High to GPIO Output Valid   | t <sub>CHPOV</sub> | _   | 10  | ns   |

| G2  | CLKOUT High to GPIO Output Invalid | t <sub>CHPOI</sub> | 1.5 | —   | ns   |

| G3  | GPIO Input Valid to CLKOUT High    | t <sub>PVCH</sub>  | 9   | _   | ns   |

| G4  | CLKOUT High to GPIO Input Invalid  | t <sub>CHPI</sub>  | 1.5 | —   | ns   |

Figure 6. GPIO Timing

## 2.10 Reset Timing

### Table 32. Reset and Configuration Override Timing

$(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, V_{SS} = 0 \text{ V}, T_A = T_L \text{ to } T_H)^1$

| NUM | Characteristic                     | Symbol             | Min | Мах | Unit             |

|-----|------------------------------------|--------------------|-----|-----|------------------|

| R1  | RSTI input valid to CLKOUT High    | t <sub>RVCH</sub>  | 9   | _   | ns               |

| R2  | CLKOUT High to RSTI Input invalid  | t <sub>CHRI</sub>  | 1.5 | _   | ns               |

| R3  | RSTI input valid time <sup>2</sup> | t <sub>RIVT</sub>  | 5   | _   | t <sub>CYC</sub> |

| R4  | CLKOUT High to RSTO Valid          | t <sub>CHROV</sub> | _   | 10  | ns               |

<sup>1</sup> All AC timing is shown with respect to 50%  $V_{DD}$  levels unless otherwise noted.

<sup>2</sup> During low power STOP, the synchronizers for the RSTI input are bypassed and RSTI is asserted asynchronously to the system. Thus, RSTI must be held a minimum of 100 ns.

| Name                | Characteristic                                 | Min | Typical      | Max  | Unit |

|---------------------|------------------------------------------------|-----|--------------|------|------|

| X <sub>IN</sub>     | Input impedance                                | _   | See Figure 9 |      | W    |

| I <sub>ADI</sub>    | Input injection current <sup>7</sup> , per pin | —   | —            | 3    | mA   |

| I <sub>VREFH</sub>  | V <sub>REFH</sub> current                      | —   | 0            | _    | mA   |

| V <sub>OFFSET</sub> | Offset voltage internal reference              | —   | ±8           | ±15  | mV   |

| E <sub>GAIN</sub>   | Gain error (transfer path)                     | .99 | 1            | 1.01 | —    |

| V <sub>OFFSET</sub> | Offset voltage external reference              | —   | ±3           | 9    | mV   |

| SNR                 | Signal-to-noise ratio                          | —   | 62 to 66     | _    | dB   |

| THD                 | Total harmonic distortion                      | _   | -75          |      | dB   |

| SFDR                | Spurious free dynamic range                    | —   | 67 to 70.3   | _    | dB   |

| SINAD               | Signal-to-noise plus distortion                | —   | 61 to 63.9   | _    | dB   |

| ENOB                | Effective number of bits                       | 9.1 | 10.6         |      | Bits |

## Table 35. ADC Parameters<sup>1</sup> (continued)

<sup>1</sup> All measurements are made at  $V_{DD}$  = 3.3V,  $V_{REFH}$  = 3.3V, and  $V_{REFL}$  = ground

<sup>2</sup> INL measured from  $V_{IN} = V_{REFL}$  to  $V_{IN} = V_{REFH}$

<sup>3</sup> LSB = Least Significant Bit

$^4~$  INL measured from  $V_{IN}$  = 0.1V\_{REFH} to  $V_{IN}$  = 0.9V\_{REFH}

$^5\,$  Includes power-up of ADC and  $V_{REF}\,$

<sup>6</sup> ADC clock cycles

<sup>7</sup> Current that can be injected or sourced from an unselected ADC signal input without impacting the performance of the ADC

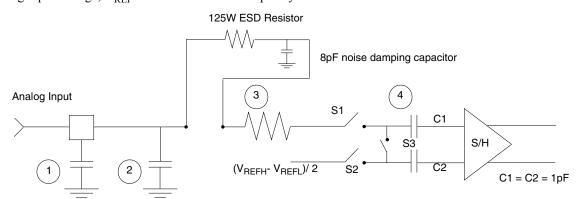

# 2.13 Equivalent Circuit for ADC Inputs

Figure 9 shows the ADC input circuit during sample and hold. S1 and S2 are always open/closed at the same time that S3 is closed/open. When S1/S2 are closed & S3 is open, one input of the sample and hold circuit moves to  $(V_{REFH}-V_{REFL})/2$ , while the other charges to the analog input voltage. When the switches are flipped, the charge on C1 and C2 are averaged via S3, with the result that a single-ended analog input is switched to a differential voltage centered about  $(V_{REFH}-V_{REFL})/2$ . The switches switch on every cycle of the ADC clock (open one-half ADC clock, closed one-half ADC clock). There are additional capacitances associated with the analog input pad, routing, etc., but these do not filter into the S/H output voltage, as S1 provides isolation during the charge-sharing phase. One aspect of this circuit is that there is an on-going input current, which is a function of the analog input voltage,  $V_{REF}$  and the ADC clock frequency.

- 1. Parasitic capacitance due to package, pin-to-pin and pin-to-package base coupling; 1.8pF

- 2. Parasitic capacitance due to the chip bond pad, ESD protection devices and signal routing; 2.04pF

MCF52223 ColdFire Microcontroller, Rev. 3

**Electrical Characteristics**

# 2.16 JTAG and Boundary Scan Timing

Table 38. JTAG and Boundary Scan Timing

| Num | Characteristics <sup>1</sup>                       | Symbol              | Min                | Max | Unit               |

|-----|----------------------------------------------------|---------------------|--------------------|-----|--------------------|

| J1  | TCLK frequency of operation                        | f <sub>JCYC</sub>   | DC                 | 1/4 | f <sub>sys/2</sub> |

| J2  | TCLK cycle period                                  | t <sub>JCYC</sub>   | $4 \times t_{CYC}$ | —   | ns                 |

| J3  | TCLK clock pulse width                             | t <sub>JCW</sub>    | 26                 | —   | ns                 |

| J4  | TCLK rise and fall times                           | t <sub>JCRF</sub>   | 0                  | 3   | ns                 |

| J5  | Boundary scan input data setup time to TCLK rise   | t <sub>BSDST</sub>  | 4                  | —   | ns                 |

| J6  | Boundary scan input data hold time after TCLK rise | t <sub>BSDHT</sub>  | 26                 | —   | ns                 |

| J7  | TCLK low to boundary scan output data valid        | t <sub>BSDV</sub>   | 0                  | 33  | ns                 |

| J8  | TCLK low to boundary scan output high Z            | t <sub>BSDZ</sub>   | 0                  | 33  | ns                 |

| J9  | TMS, TDI input data setup time to TCLK rise        | t <sub>TAPBST</sub> | 4                  | —   | ns                 |

| J10 | TMS, TDI Input data hold time after TCLK rise      | t <sub>TAPBHT</sub> | 10                 | —   | ns                 |

| J11 | TCLK low to TDO data valid                         | t <sub>TDODV</sub>  | 0                  | 26  | ns                 |

| J12 | TCLK low to TDO high Z                             | t <sub>TDODZ</sub>  | 0                  | 8   | ns                 |

| J13 | TRST assert time                                   | t <sub>TRSTAT</sub> | 100                | —   | ns                 |

| J14 | TRST setup time (negation) to TCLK high            | t <sub>TRSTST</sub> | 10                 | —   | ns                 |

<sup>1</sup> JTAG\_EN is expected to be a static signal. Hence, it is not associated with any timing.

MCF52223 ColdFire Microcontroller, Rev. 3

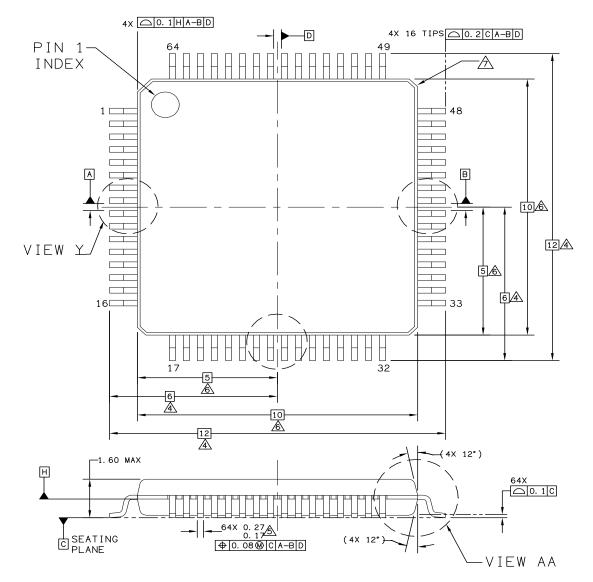

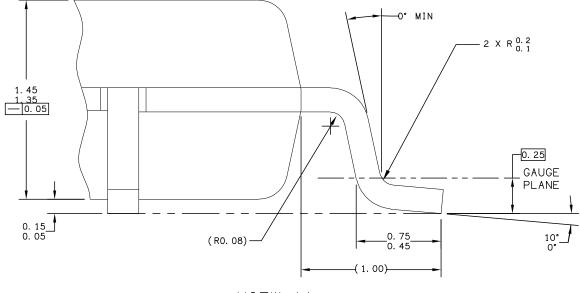

# 3.1 64-pin LQFP Package

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |              | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------------|--------------|------------------|-------------|

| TITLE: 64LD LQFP.                                       |                    | DOCUMENT NO  | : 98ASS23234₩    | REV: D      |

| 10 X 10 X 1.4 PKG,                                      |                    | CASE NUMBER  | 2:840F-02        | 06 APR 2005 |

| 0.5 PITCH, CASE OUTLINE                                 |                    | STANDARD: JE | DEC MS-026 BCD   |             |

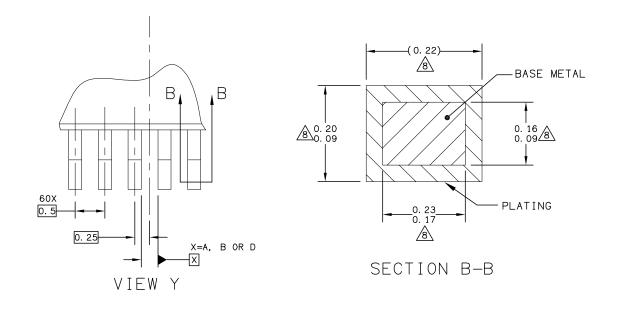

### **Mechanical Outline Drawings**

VIEW AA

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | Mechanical outline |              | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------------|--------------|------------------|-------------|

| TITLE: 64LD LQFP,                                       |                    | DOCUMENT NO  | ): 98ASS23234₩   | REV: D      |

| 10 X 10 X 1.4 PKG,<br>O.5 PITCH, CASE OUTLINE           |                    | CASE NUMBER  | 2:840F-02        | 06 APR 2005 |

|                                                         |                    | STANDARD: JE | DEC MS-026 BCD   |             |

### MCF52223 ColdFire Microcontroller, Rev. 3

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

- 4. DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.

- 5. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 mm AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 mm.

- A. THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

- / EXACT SHAPE OF EACH CORNER IS OPTIONAL.

- AND 0.25 mm FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | Mechanical outline |              | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--------------------|--------------|------------------|-------------|

| TITLE: 64LD LQFP,                                       |                    | DOCUMENT NO  | ): 98ASS23234₩   | REV: D      |

| 10 X 10 X 1.4 PKG,                                      |                    | CASE NUMBER  | 2:840F-02        | 06 APR 2005 |

| 0.5 PITCH, CASE OUTLINE                                 |                    | STANDARD: JE | DEC MS-026 BCD   |             |

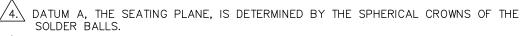

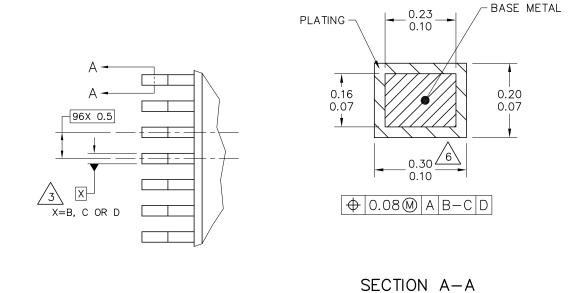

#### **Mechanical Outline Drawings**

NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- /3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

5. PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|--------------------|------------------|-------------|

| TITLE: PBGA, LOW PROFIL                                 | E, DOCUMENT N      | D: 98ASA10670D   | REV: O      |

| 81 I/O, 10 X 10 PI                                      |                    | ₹: 1662–01       | 04 FEB 2005 |

| 1 MM PITCH (MAP                                         | ) STANDARD: N      | ON-JEDEC         |             |

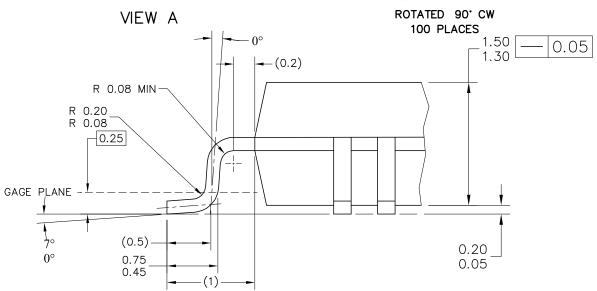

**Mechanical Outline Drawings**

VIEW B

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE PRINT |              | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|--------------------------|--------------|------------------|-------------|

| TITLE:                                                  |                          | DOCUMENT NO  | ): 98ASS23308W   | REV: G      |

| 100 LEAD LQFP<br>14 X 14, 0.5 PITCH, 1.4 THICK          |                          | CASE NUMBER  | 2: 983–03        | 07 APR 2005 |

|                                                         |                          | STANDARD: NO | N-JEDEC          |             |

# 4 Revision History

### Table 40. Revision History

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | <ul> <li>Formatting, layout, spelling, and grammar corrections.</li> <li>Removed the "Preliminary" label.</li> <li>Added missing current consumption data (Section 2.2).</li> <li>Added revision history.</li> <li>Corrected signal names in block diagram to match those in the signal description table.</li> <li>Added an entry for standby voltage (V<sub>STBY</sub>) to the "DC electrical specifications" table.</li> <li>Deleted the PSTCLK cycle time row in the "Debug AC timing specifications" table.</li> <li>Changed the frequency above the "Min" and "Max" column headings in the "Debug AC timing specifications" table (was 166 MHz, is 66/80 MHz).</li> <li>Added the following signals to the "Pin functions by primary and alternate purpose" table (alternates to IRQ1-6, respectively): USB_ALT_CLK, USB_SESSVLD, USB_SESSEND, USB_PULLUP, USB_VBUSVLD, and USB_ID.</li> <li>Changed the minimum value for SNR, THD, SFDR, and SINAD in the "ADC parameters" table (was TBD, is "").</li> <li>Added values for I<sub>OH</sub> and I<sub>OL</sub> to the "DC electrical specifications" table.</li> <li>Added values for V<sub>DH</sub> and I<sub>OL</sub> to the "Absolute maximum ratings" table in this document and the reference manual.</li> <li>Added a specification for V<sub>DDUSB</sub> to the "Absolute maximum ratings" table.</li> <li>Deleted entries for the nonexistent 64 QFN package from the "Thermal Resistances" table.</li> </ul> |

| 3        | Updated Table 7 to reflect orderable part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4        | <ul> <li>Updated Clock generation features</li> <li>Updated Table: Clocking Modes and added appropriate footnote</li> <li>In Table: CLock Source Electrical Specifications, updated the following values:</li> <li>fcrystal, fext, fref_pll, EXTAL input high voltage (External reference)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |