#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1516-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Pin Utilization

Five pins are needed for ICSP<sup>™</sup> programming. The pins are listed in Table 1-1 and Table 1-2.

| Pin Name     | During Programming  |                  |                                              |  |

|--------------|---------------------|------------------|----------------------------------------------|--|

|              | Function            | Pin Type         | Pin Description                              |  |

| RB6          | ICSPCLK             | l                | Clock Input – Schmitt Trigger Input          |  |

| RB7          | ICSPDAT             | I/O              | Data Input/Output – Schmitt Trigger Input    |  |

| RG5/MCLR/VPP | Program/Verify mode | P <sup>(1)</sup> | Program Mode Select/Programming Power Supply |  |

| Vdd          | Vdd                 | Р                | Power Supply                                 |  |

| Vss          | Vss                 | Р                | Ground                                       |  |

### TABLE 1-1: PIN DESCRIPTIONS DURING PROGRAMMING – PIC16(L)F1526 AND PIC16(L)F1527

**Legend:** I = Input, O = Output, P = Power

**Note 1:** The programming high voltage is internally generated. To activate the Program/Verify mode, high voltage needs to be applied to MCLR input. Since the MCLR is used for a level source, MCLR does not draw any significant current.

# TABLE 1-2:PIN DESCRIPTIONS DURING PROGRAMMING – PIC16(L)F1512, PIC16(L)F1513,<br/>PIC16(L)F1516, PIC16(L)F1517, PIC16(L)F1518 and PIC16(L)F1519

| Pin Name     | During Programming  |                  |                                              |  |

|--------------|---------------------|------------------|----------------------------------------------|--|

|              | Function            | Pin Type         | Pin Description                              |  |

| RB6          | ICSPCLK             | I                | Clock Input – Schmitt Trigger Input          |  |

| RB7          | ICSPDAT             | I/O              | Data Input/Output – Schmitt Trigger Input    |  |

| RE3/MCLR/VPP | Program/Verify mode | P <sup>(1)</sup> | Program Mode Select/Programming Power Supply |  |

| Vdd          | Vdd                 | Р                | Power Supply                                 |  |

| Vss          | Vss                 | Р                | Ground                                       |  |

Legend: I = Input, O = Output, P = Power

**Note 1:** The programming high voltage is internally generated. To activate the Program/Verify mode, high voltage needs to be applied to MCLR input. Since the MCLR is used for a level source, MCLR does not draw any significant current.

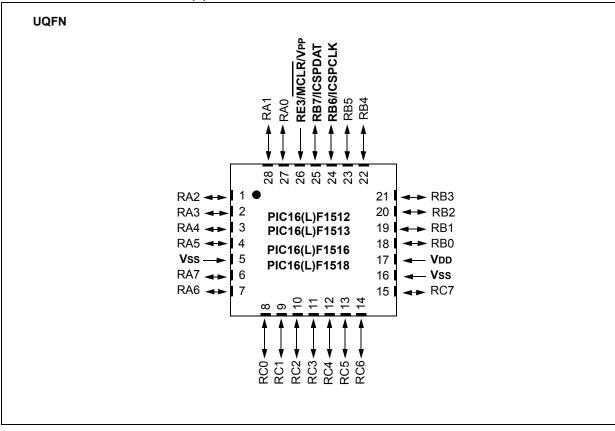

### FIGURE 2-2: 28-PIN UQFN DIAGRAM FOR PIC16(L)F1512, PIC16(L)F1513, PIC16(L)F1516 AND PIC16(L)F1518

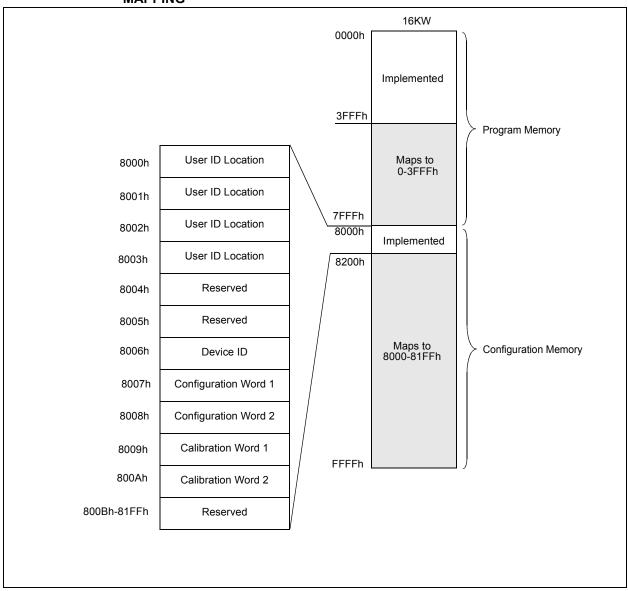

# FIGURE 3-4: PIC16(L)F1527, PIC16(L)F1518 AND PIC16(L)F1519 PROGRAM MEMORY MAPPING

|                     |                                                                                                                                        | R/P-1                                  | R/P-1                     | R/P-1             | R/P-1                | R/P-1        | U-1   |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------|-------------------|----------------------|--------------|-------|--|

|                     |                                                                                                                                        | LVP                                    | DEBUG                     | LPBOR             | BORV                 | STVREN       | _     |  |

|                     |                                                                                                                                        | bit 13                                 |                           |                   |                      |              | bit   |  |

|                     |                                                                                                                                        |                                        |                           |                   |                      |              |       |  |

| U-1                 | U-1                                                                                                                                    | U-1                                    | R/P-1                     | U-1               | U-1                  | R/P-1        | R/P-1 |  |

| _                   | _                                                                                                                                      | _                                      | VCAPEN <sup>(2)</sup>     | _                 | _                    | WRT<         | 1:0>  |  |

| bit 7               |                                                                                                                                        |                                        |                           |                   | I                    | I            | bit   |  |

|                     |                                                                                                                                        |                                        |                           |                   |                      |              |       |  |

| Legend:             |                                                                                                                                        |                                        |                           |                   |                      |              |       |  |

| R = Readable bit    | t                                                                                                                                      | P = Programma                          | ble bit                   | U = Unimpleme     | nted bit, read as '1 |              |       |  |

| 0' = Bit is cleared | t                                                                                                                                      | '1' = Bit is set                       |                           | -n = Value whe    | n blank or after B   | ulk Erase    |       |  |

|                     |                                                                                                                                        |                                        |                           |                   |                      |              |       |  |

| bit 13              | LVP: Low-Volta                                                                                                                         | age Programming                        | Enable bit <sup>(1)</sup> |                   |                      |              |       |  |

|                     |                                                                                                                                        | e programming e                        |                           |                   |                      |              |       |  |

|                     |                                                                                                                                        | LR/VPP must be u                       | 1 0                       | ning              |                      |              |       |  |

| bit 12              |                                                                                                                                        | rcuit Debugger Mo                      |                           |                   |                      |              |       |  |

|                     |                                                                                                                                        | )ebugger disabled<br>)ebugger enabled  |                           | •                 |                      | •            |       |  |

| bit 11              | LPBOR: Low-F                                                                                                                           |                                        | ,                         |                   |                      | -990         |       |  |

| 2.1                 |                                                                                                                                        | r BOR is disabled                      |                           |                   |                      |              |       |  |

|                     | 0 = Low-Power                                                                                                                          | r BOR is enabled                       |                           |                   |                      |              |       |  |

| bit 10              |                                                                                                                                        | out Reset Voltage                      |                           |                   |                      |              |       |  |

|                     |                                                                                                                                        | Reset voltage (Vi                      | · · ·                     |                   |                      |              |       |  |

| h# 0                |                                                                                                                                        | Reset voltage (Vi                      | <i>/</i> <b>0</b> 11      |                   |                      |              |       |  |

| bit 9               |                                                                                                                                        | k Overflow/Under<br>flow or Underflow  |                           |                   |                      |              |       |  |

|                     | <ul> <li>1 = Stack Overflow or Underflow will cause a Reset</li> <li>0 = Stack Overflow or Underflow will not cause a Reset</li> </ul> |                                        |                           |                   |                      |              |       |  |

| bit 8-5             | Unimplemented: Read as '1'                                                                                                             |                                        |                           |                   |                      |              |       |  |

| bit 4               | VCAPEN: Volta                                                                                                                          | age Regulator Ca                       | pacitor Enable bi         | ts <sup>(1)</sup> |                      |              |       |  |

|                     | 0 = VCAP funct                                                                                                                         | ionality is enabled                    | d on VCAP pin             |                   |                      |              |       |  |

|                     | 1 = All VCAP pi                                                                                                                        | n functions are di                     | sabled                    |                   |                      |              |       |  |

| bit 3-2             | Unimplemente                                                                                                                           | ed: Read as '1'                        |                           |                   |                      |              |       |  |

| bit 1-0             |                                                                                                                                        | ash Memory Self-                       |                           | bits              |                      |              |       |  |

|                     |                                                                                                                                        | emory (PIC16(L)F<br>ite protection off | <u>1512)</u> :            |                   |                      |              |       |  |

|                     |                                                                                                                                        | 0h to 1FFh write-p                     | protected, 200h to        | o 7FFh may be m   | nodified by PMCC     | N control    |       |  |

|                     | 01 = 000                                                                                                                               | 0h to FFFh write-                      | protected, 400h to        | o 7FFh may be m   | nodified by PMCC     | N control    |       |  |

|                     |                                                                                                                                        | Oh to 7FFh write-                      |                           | resses may be n   | nodified by PMCC     | ON control   |       |  |

|                     |                                                                                                                                        | emory (PIC16(L)F<br>ite protection off | <u>1513)</u> .            |                   |                      |              |       |  |

|                     |                                                                                                                                        | 0h to 1FFh write-p                     | protected, 200h to        | o FFFh may be m   | nodified by PMCC     | N control    |       |  |

|                     |                                                                                                                                        | 0h to 7FFh write-p                     | ,                         | ,                 | ,                    |              |       |  |

|                     |                                                                                                                                        | Dh to FFFh write-p<br>mory (PIC16F/LF  |                           | •                 | nodified by PMCO     | N control    |       |  |

|                     |                                                                                                                                        | ite protection off                     | 1310/1317/1320            | 1.                |                      |              |       |  |

|                     | 10 = 000                                                                                                                               | 0h to 1FFh write-p                     |                           |                   |                      |              |       |  |

|                     |                                                                                                                                        | Oh to FFFh write-                      |                           |                   |                      |              |       |  |

|                     |                                                                                                                                        | 0h to 1FFFh write<br>emory (PIC16F/L   | •                         |                   | modified by PINC     | ON control   |       |  |

|                     |                                                                                                                                        | ite protection off                     |                           | <u></u> .         |                      |              |       |  |

|                     | 10 = 000                                                                                                                               | 0h to 1FFh write-p                     |                           |                   |                      |              |       |  |

|                     | 01 - 000                                                                                                                               |                                        |                           |                   | a madified by DN     | ICON control |       |  |

|                     |                                                                                                                                        | 0h to 1FFFh write<br>0h to 3FFFh write |                           |                   |                      |              |       |  |

## REGISTER 3-3: CONFIGURATION WORD 2

2: Applies to PIC16F151X/152X devices only. On PIC16LF151X/152X, the VCAPEN bit is unimplemented.

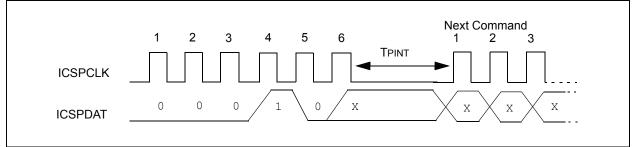

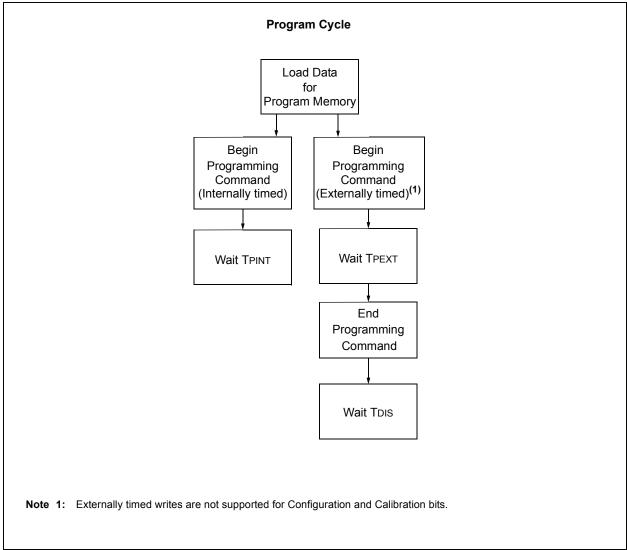

#### 4.3.6 BEGIN INTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. An internal timing mechanism executes the write. The user must allow for the program cycle time, TPINT, for the programming to complete.

The End Externally Timed Programming command is not needed when the Begin Internally Timed Programming is used to start the programming.

The program memory address that is being programmed is not erased prior to being programmed.

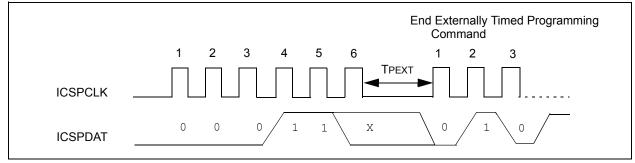

#### 4.3.7 BEGIN EXTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. To complete the programming the End Externally Timed Programming command must be sent in the specified time window defined by TPEXT (see Figure 4-7).

Externally timed writes are not supported for Configuration and Calibration bits. Any externally timed write to the Configuration or Calibration Word will have no effect on the targeted word.

### FIGURE 4-7: BEGIN EXTERNALLY TIMED PROGRAMMING

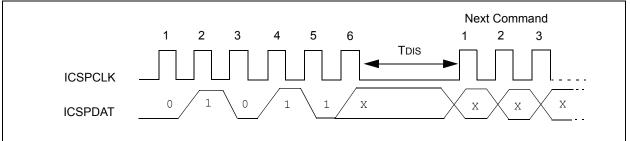

# 4.3.8 END EXTERNALLY TIMED PROGRAMMING

This command is required after a Begin Externally Timed Programming command is given. This command must be sent within the time window specified by TPEXT after the Begin Externally Timed Programming command is sent.

After sending the End Externally Timed Programming command, an additional delay (TDIS) is required before sending the next command. This delay is longer than the delay ordinarily required between other commands (see Figure 4-8).

### FIGURE 4-8: END EXTERNALLY TIMED PROGRAMMING

# 4.3.9 BULK ERASE PROGRAM MEMORY

The Bulk Erase Program Memory command performs two different functions dependent on the current state of the address.

Address 0000h-7FFFh:

Program Memory is erased

Configuration Words are erased

### Address 8000h-8008h:

Program Memory is erased

Configuration Words are erased

User ID Locations are erased

A Bulk Erase Program Memory command should not be issued when the address is greater than 8008h.

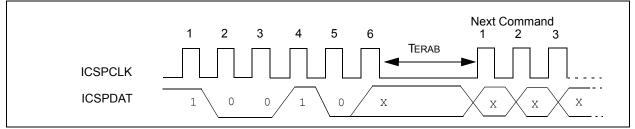

## FIGURE 4-9: BULK ERASE PROGRAM MEMORY

After receiving the Bulk Erase Program Memory command the erase will not complete until the time interval, TERAB, has expired.

Note: The code protection Configuration bit (CP) has no effect on the Bulk Erase Program Memory command.

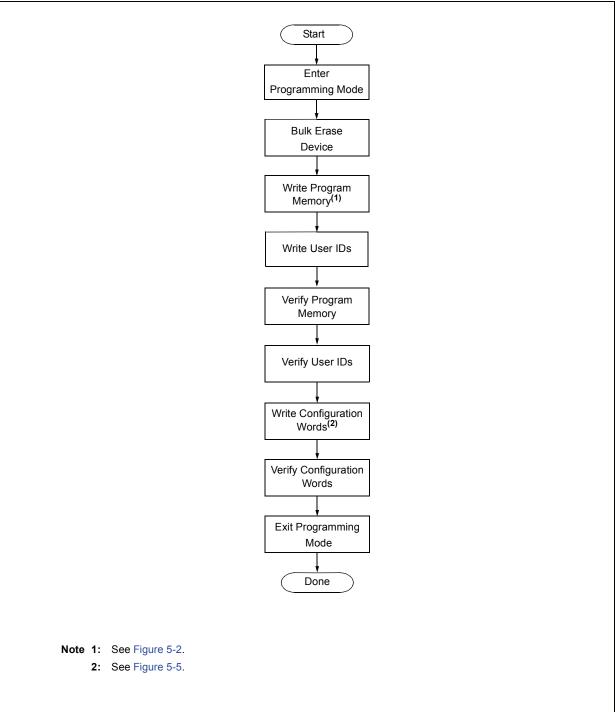

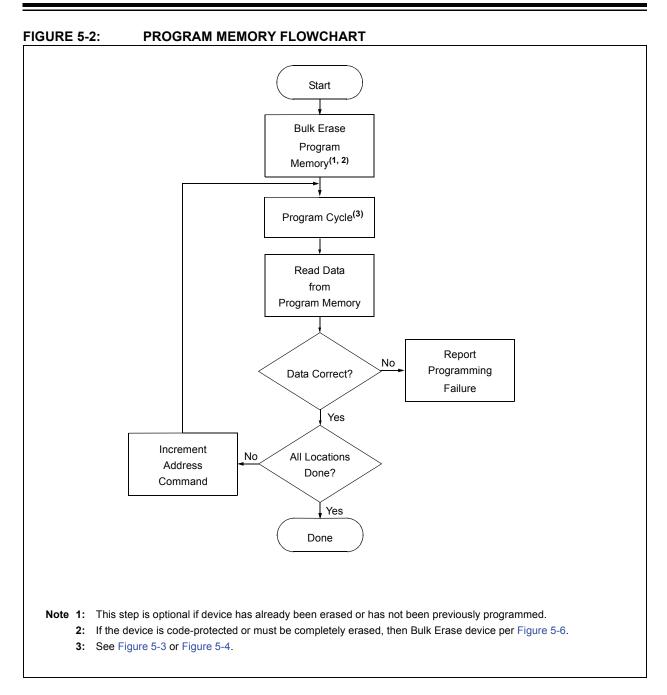

# 5.0 PROGRAMMING ALGORITHMS

The devices use internal latches to temporarily store the 14-bit words used for programming. Refer to Table 4-2 for specific latch information. The data latches allow the user to write the program words with a single Begin Externally Timed Programming or Begin Internally Timed Programming command. The Load Program Data or the Load Configuration command is used to load a single data latch. The data latch will hold the data until the Begin Externally Timed Programming or Begin Internally Timed Programming or Begin Internally Timed Programming command is given.

The data latches are aligned with the LSbs of the address. The PC's address at the time the Begin Externally Timed Programming or Begin Internally Timed Programming command is given will determine which location(s) in memory are written. Writes cannot cross the physical boundary. For example, with the PIC16F1527, attempting to write from address 0002h-0009h will result in data being written to 0008h-000Fh.

If more than the maximum number of data latches are written without a Begin Externally Timed Programming or Begin Internally Timed Programming command, the data in the data latches will be overwritten. The following figures show the recommended flowcharts for programming.

**ONE-WORD PROGRAM CYCLE**

# 7.3 Checksum Computation

The checksum is calculated by two different methods dependent on the setting of the CP Configuration bit.

| MASK VALUES |                        |                        |  |  |  |  |  |

|-------------|------------------------|------------------------|--|--|--|--|--|

| Device      | Config. Word 1<br>Mask | Config. Word 2<br>Mask |  |  |  |  |  |

| PIC16F1512  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16F1513  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16F1516  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16F1517  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16F1518  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16F1519  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16LF1512 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

| PIC16LF1513 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

| PIC16LF1516 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

| PIC16LF1517 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

| PIC16LF1518 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

| PIC16LF1519 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

| PIC16F1526  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16F1527  | 3EFFh                  | 3E13h                  |  |  |  |  |  |

| PIC16LF1526 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

| PIC16LF1527 | 3EFFh                  | 3E03h                  |  |  |  |  |  |

# TABLE 7-1: CONFIGURATION WORD MASK VALUES

## 7.3.1 PROGRAM CODE PROTECTION DISABLED

With the program code protection disabled, the checksum is computed by reading the contents of the PIC16(L)F151X/152X program memory locations and adding up the program memory data starting at address 0000h, up to the maximum user addressable location. Any Carry bit exceeding 16 bits are ignored. Additionally, the relevant bits of the Configuration Words are added to the checksum. All unimplemented Configuration bits are masked to '0'.

unimplemented bits are '0'.

#### EXAMPLE 7-1: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION DISABLED PIC16F1527, BLANK DEVICE

| PIC16F15 | 527 Sum of Memory add                           | resses 0000h-3FFFh <sup>(1)</sup> | C000h                                       |  |

|----------|-------------------------------------------------|-----------------------------------|---------------------------------------------|--|

|          | Configuration Word                              | 1 <sup>(2)</sup>                  | 3FFFh                                       |  |

|          | Configuration Word                              | 1 mask <sup>(3)</sup>             | 3EFFh                                       |  |

|          | Configuration Word                              | 2 <sup>(2)</sup>                  | 3FFFh                                       |  |

|          | Configuration Word                              | 2 mask <sup>(3)</sup>             | 3E13h                                       |  |

|          | Checksum                                        | = C000h + (3FFFh and 3EFF         | h) + (3FFFh and 3E13h)                      |  |

|          |                                                 | = C000h + 3EFFh + 3E13h           |                                             |  |

|          |                                                 | = 3D12h                           |                                             |  |

| Note 1:  | Sum of memory addresse<br>truncated to 16 bits. | s = (Total number of program m    | emory address locations) x (3FFFh) = C000h, |  |

- 2: Configuration Word 1 and 2 = all bits are '1'; thus, code-protect is disabled.

- 3: Configuration Word 1 and 2 Mask = all bits are set to '1', except for unimplemented bits that are '0'.

### EXAMPLE 7-2: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION DISABLED PIC16LF1527, 00AAh AT FIRST AND LAST ADDRESS

| PIC16LF1 | 527 Sum of Memory ad                  | ldresses 0000h-3FFFh <sup>(1)</sup>                                                                                                                                 | 4156h                                      |  |  |

|----------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

|          | Configuration Word                    | 1 1 <sup>(2)</sup>                                                                                                                                                  | 3FFFh                                      |  |  |

|          | Configuration Word                    | 1 mask <sup>(3)</sup>                                                                                                                                               | 3EFFh                                      |  |  |

|          | Configuration Word                    | 1 2 <sup>(2)</sup>                                                                                                                                                  | 3FFFh                                      |  |  |

|          | Configuration Word                    | l 2 mask <sup>(4)</sup>                                                                                                                                             | 3E03h                                      |  |  |

|          | Checksum                              | = 4156h + (3FFFh and 3EFF                                                                                                                                           | ) + (3FFFh and 3E03h)                      |  |  |

|          |                                       | = 4156h + 3EFFh + 3E03h                                                                                                                                             |                                            |  |  |

|          |                                       | = BE58h                                                                                                                                                             |                                            |  |  |

| Note 1:  | 0                                     | otal number of Program memory address locations: 3FFFh + 1 = 4000h. Then, 4000h - 2 = 3FFEh.<br>hus, [(3FFEh x 3FFFh) + (2 x 00AAh)] = 4156h, truncated to 16 bits. |                                            |  |  |

| 2:       | Configuration Word 1 an               | onfiguration Word 1 and 2 = all bits are '1'; thus, code-protect is disabled.                                                                                       |                                            |  |  |

| 3:       | Configuration Word 1 Ma that are '0'. | Configuration Word 1 Mask = all Configuration Word bits are set to '1', except for unimplemented bits<br>that are '0'.                                              |                                            |  |  |

| 4:       | On the PIC16LF1527 de                 | vice, the VCAPEN bit is not imple                                                                                                                                   | emented in Configuration Word 2; Thus, all |  |  |

### 7.3.2 PROGRAM CODE PROTECTION ENABLED

With the program code protection enabled, the checksum is computed in the following manner: The Least Significant nibble of each user ID is used to create a 16-bit value. The masked value of user ID location 8000h is the Most Significant nibble. This sum of user IDs is summed with the Configuration Words (all unimplemented Configuration bits are masked to '0').

### EXAMPLE 7-3: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION ENABLED PIC16F1527, BLANK DEVICE

| PIC16F1 | 527 Configuration Word                                                                                                      | (2) 3F7Fh                                                 |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

|         | Configuration Word                                                                                                          | mask <sup>(3)</sup> 3EFFh                                 |  |  |  |

|         | Configuration Word 2                                                                                                        | (2) 3FFFh                                                 |  |  |  |

|         | Configuration Word 2                                                                                                        | mask <sup>(3)</sup> 3E13h                                 |  |  |  |

|         | User ID (8000h) <sup>(1)</sup>                                                                                              | 0006h                                                     |  |  |  |

|         | User ID (8001h) <sup>(1)</sup>                                                                                              | 0007h                                                     |  |  |  |

|         | User ID (8002h) <sup>(1)</sup>                                                                                              | 0001h                                                     |  |  |  |

|         | User ID (8003h) <sup>(1)</sup>                                                                                              | 0002h                                                     |  |  |  |

|         | Sum of User IDs <sup>(4)</sup>                                                                                              | = (0006h and 000Fh) << 12 + (0007h and 000Fh) << 8 +      |  |  |  |

|         |                                                                                                                             | (0001h and 000Fh) << 4 + (0002h and 000Fh)                |  |  |  |

|         |                                                                                                                             | = 6000h + 0700h + 0010h + 0002h                           |  |  |  |

|         | = 6712h                                                                                                                     |                                                           |  |  |  |

|         | Checksum                                                                                                                    | = (3F7Fh and 3EFFh) + (3FFFh and 3E13h) + Sum of User IDs |  |  |  |

|         |                                                                                                                             | = 3E7Fh +3713h + 6712h                                    |  |  |  |

|         |                                                                                                                             | = DCA4h                                                   |  |  |  |

| Note 1: | User ID values in this example are random values.                                                                           |                                                           |  |  |  |

| 2:      | Configuration Word 1 and 2 = all bits are '1' except the code-protect enable bit.                                           |                                                           |  |  |  |

| 3:      | Configuration Word 1 and 2 Mask = all Configuration Word bits are set to '1', except for unimplemented bits which read '0'. |                                                           |  |  |  |

| 4:      |                                                                                                                             |                                                           |  |  |  |

<= shift left, thus the LSb of the first user ID value is the MSb of the sum of user IDs and so on, unti the LSb of the last user ID value becomes the LSb of the sum of user IDs.

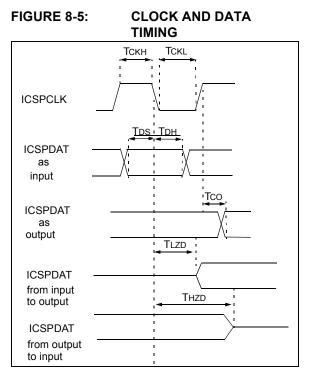

## TABLE 8-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY

| AC/DC CHARACTERISTICS |                                                           | Standard Operating Conditions<br>Production tested at 25°C |      |          |          |                                       |

|-----------------------|-----------------------------------------------------------|------------------------------------------------------------|------|----------|----------|---------------------------------------|

| Sym. Characteristics  |                                                           | Min.                                                       | Тур. | Max.     | Units    | Conditions/Comments                   |

| TPINT                 | Internally timed programming operation time               |                                                            |      | 2.5<br>5 | ms<br>ms | Program memory<br>Configuration Words |

| TPEXT                 | Externally timed programming pulse                        | 1.0                                                        | —    | 2.1      | ms       | Note 1                                |

| TDIS                  | Time delay from program to compare<br>(HV discharge time) | 300                                                        | —    | —        | μs       |                                       |

| TEXIT                 | Time delay when exiting Program/Verify mode               | 1                                                          | —    |          | μS       |                                       |

Note 1: Externally timed writes are not supported for Configuration and Calibration bits.

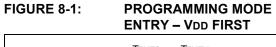

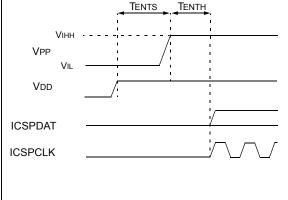

# 8.1 AC Timing Diagrams

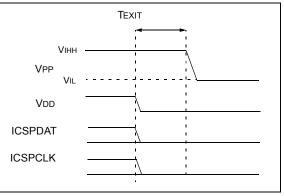

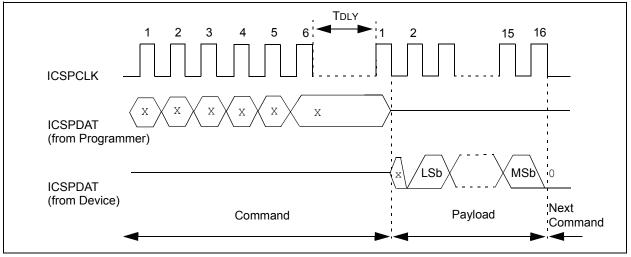

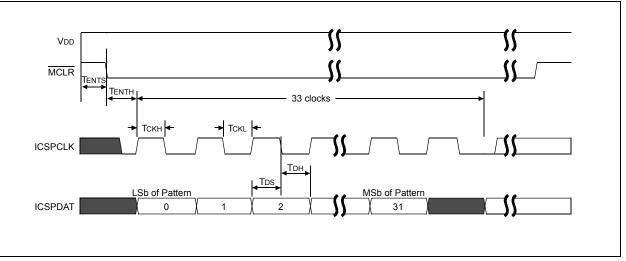

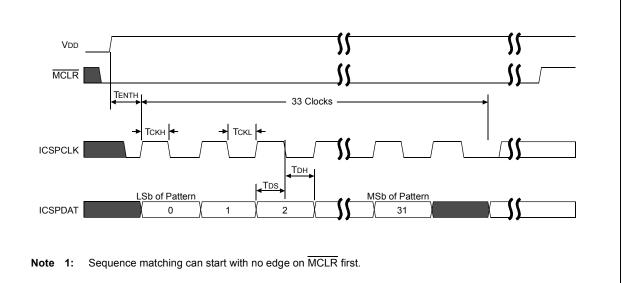

### FIGURE 8-2:

PROGRAMMING MODE ENTRY – VPP FIRST

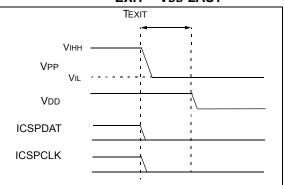

# FIGURE 8-3:

### PROGRAMMING MODE EXIT – VPP LAST

FIGURE 8-4:

### PROGRAMMING MODE EXIT – VDD LAST

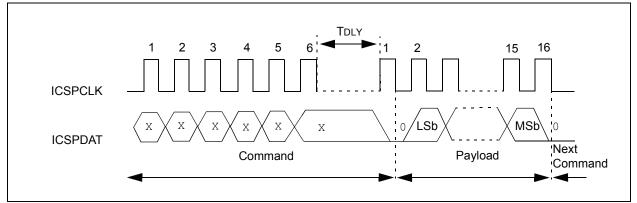

FIGURE 8-6:

#### WRITE COMMAND-PAYLOAD TIMING

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820