Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1517-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

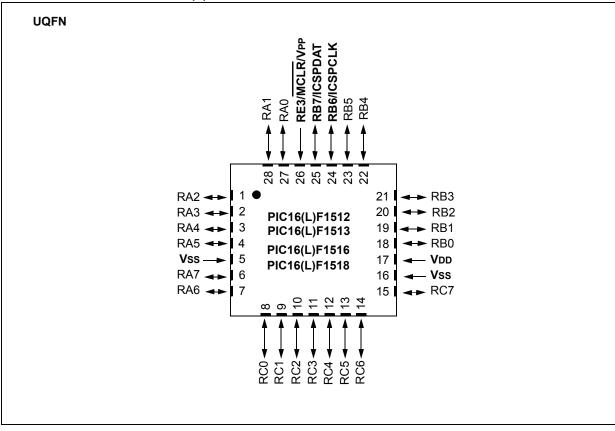

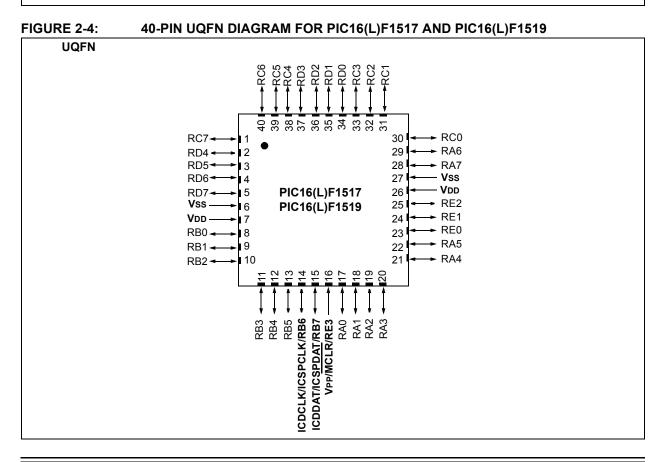

## 2.0 DEVICE PINOUTS

The pin diagrams for the PIC16(L)F151X/152X family are shown in Figure 2-1 through Figure 2-7. The pins that are required for programming are listed in Table 1-1 and shown in bold lettering in the pin diagrams.

## FIGURE 2-1: 28-PIN SPDIP, SOIC, SSOP DIAGRAM FOR PIC16(L)F1512, PIC16(L)F1513, PIC16(L)F1516 AND PIC16(L)F1518

| SPDIP, SOIC, SSOP   |                                 |                               |

|---------------------|---------------------------------|-------------------------------|

|                     | $\bigcirc$                      | 28 <b>_ ← ► RB7/ICSPDAT</b>   |

| RA0 🛶 🗖 🛛           |                                 |                               |

| RA1 🛶 🗖 🕄           | }                               | 26 <b>- →</b> RB5             |

| RA2 🛶               | ļ                               | 25 <b>_</b> ←► RB4            |

| RA3 🛶 🔤             |                                 | 24 <b>→</b> RB3               |

| RA4 🛶               | 512<br>513<br>516<br>518<br>518 | 23 <b>→</b> RB2               |

| RA5 🔸 🗌 7           | ĔĔĔĔ                            | 22 <b>- →</b> RB1             |

| Vss →               |                                 | , 21 <b>_ </b> ← <b>→</b> RB0 |

| RA7 🔫 🗕             | ូ ភូភូភូភូ                      |                               |

| RA6                 |                                 | 19 <b>−−− V</b> ss            |

| RC0 -               | 1                               | 18 <b>-</b> RC7               |

| RC1 -               | 2                               | 17 <b> ← ►</b> RC6            |

| RC2 <del>→ </del> 1 | 3                               | 16 <b> →</b> RC5              |

| RC3 <b>◄ ►</b> []1  | 4                               | 15 <b>- - - - - - - - - -</b> |

|                     |                                 |                               |

#### FIGURE 2-2: 28-PIN UQFN DIAGRAM FOR PIC16(L)F1512, PIC16(L)F1513, PIC16(L)F1516 AND PIC16(L)F1518

| FIGURE 2-3: | 40-PIN PDIP DIAGRAM F | OR PIC1                        | 6(L)F1517 AND PIC16(L)F1519 |

|-------------|-----------------------|--------------------------------|-----------------------------|

| PDIP        |                       |                                |                             |

|             | Vpp/MCLR/RE3 1        | $\bigcirc$                     | 40 RB7/ICSPDAT/ICDDAT       |

|             | RA0 🔶 2               |                                |                             |

|             | RA1 🗕 🗕 🔤 3           |                                | 38 <b>→</b> RB5             |

|             | RA2 🛶 🗖 4             |                                | 37 <b>→</b> RB4             |

|             | RA3 🛶 🗖 5             |                                | 36 <b>→</b> RB3             |

|             | RA4 🖛 🛏 6             |                                | 35 🗌 🗲 → RB2                |

|             | RA5 🔶 7               |                                | 34 <b>→</b> RB1             |

|             | RE0 🗕 🕨 🔤 8           | <u>⊳</u> 6                     | 33 <b>- →</b> RB0           |

|             | RE1 🛶 🕨 🗍 9           | 151                            | 32 - VDD                    |

|             | RE2                   | PIC16(L)F1517<br>PIC16(L)F1519 | 31 <b> </b>                 |

|             | <b>V</b> DD —— 11     | :16(<br>:16(                   | 30 - → RD7                  |

|             | <b>Vss —►</b> 12      |                                | 29 🗌 🖛 🕨 RD6                |

|             | RA7 🛶 🗖 13            |                                | 28 🗌 🔸 RD5                  |

|             | RA6 💶 14              |                                | 27 🗌 🖛 → RD4                |

|             | RC0 🔶 🚺 15            |                                | 26 <b>- →</b> RC7           |

|             | RC1 🗕 🗕 16            |                                | 25 🗌 🛶 RC6                  |

|             | RC2 🗕 ► 🗌 17          |                                | 24 🗌 🛶 RC5                  |

|             | RC3 🗕 ► 🗌 18          |                                | 23 🗌 🖛 RC4                  |

|             | RD0 🗕 ► 🗌 19          |                                | 22 <b>- →</b> RD3           |

|             | RD1 ← ► 20            |                                | 21 RD2                      |

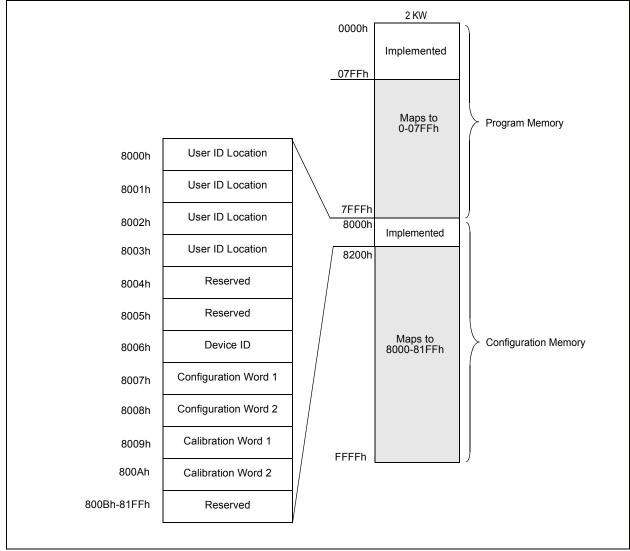

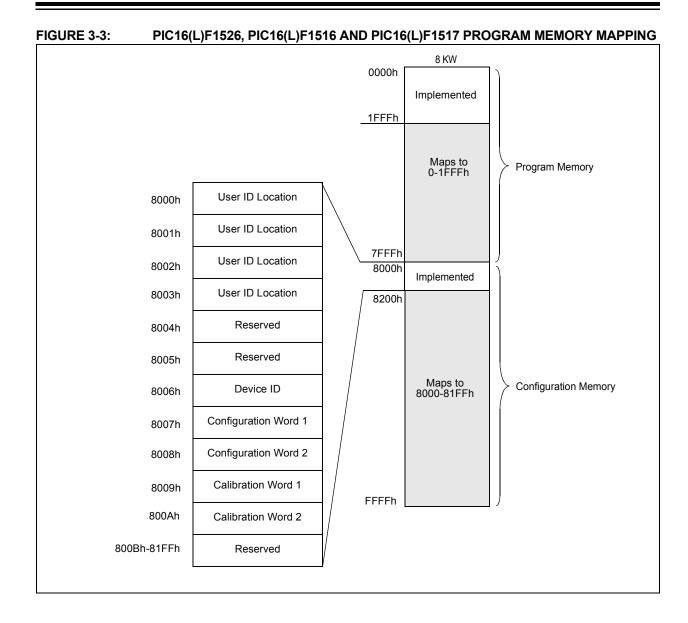

### 3.0 MEMORY MAP

The memory for the PIC16(L)F151X/152X devices is broken into two sections: program memory and configuration memory. Only the size of the program memory changes between devices, the configuration memory remains the same.

|             | DEVICE        | ID VALUES |

|-------------|---------------|-----------|

| DEVICE      | DEV           | REV       |

| PIC16F1527  | 0001 0101 101 | x xxxx    |

| PIC16F1526  | 0001 0101 100 | x xxxx    |

| PIC16LF1527 | 0001 0101 111 | x xxxx    |

| PIC16LF1526 | 0001 0101 110 | x xxxx    |

| PIC16F1519  | 0001 0110 111 | x xxxx    |

| PIC16F1518  | 0001 0110 110 | x xxxx    |

| PIC16F1517  | 0001 0110 101 | x xxxx    |

| PIC16F1516  | 0001 0110 100 | x xxxx    |

| PIC16F1513  | 0001 0110 010 | x xxxx    |

| PIC16F1512  | 0001 0111 000 | x xxxx    |

| PIC16LF1519 | 0001 0111 111 | x xxxx    |

| PIC16LF1518 | 0001 0111 110 | x xxxx    |

| PIC16LF1517 | 0001 0111 101 | x xxxx    |

| PIC16LF1516 | 0001 0111 100 | x xxxx    |

| PIC16LF1513 | 0001 0111 010 | X XXXX    |

| PIC16LF1512 | 0001 0111 001 | X XXXX    |

### TABLE 3-1: DEVICE ID VALUES

### 3.3 Configuration Words

There are two Configuration Words, Configuration Word 1 (8007h) and Configuration Word 2 (8008h). The individual bits within these Configuration Words are used to enable or disable device functions such as the Brown-out Reset, code protection and Power-up Timer.

### 3.4 Calibration Words

The internal calibration values are factory calibrated and stored in Calibration Words 1 and 2 (8009h, 800Ah).

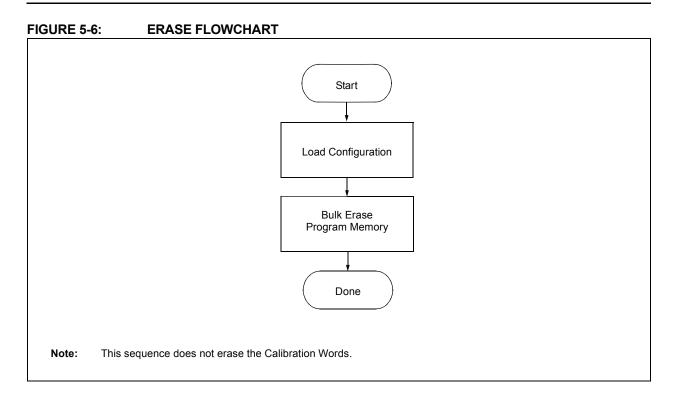

The Calibration Words do not participate in erase operations. The device can be erased without affecting the Calibration Words.

#### **REGISTER 3-2: CONFIGURATION WORD 1**

|                     |                                                                                                                                                                                                                                              | R/P-1                                                                                                                                     | R/P-1                                                                                                                          | R/P-1                                                                                | R/P-1               | R/P-1               | U-1        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------|---------------------|------------|

|                     |                                                                                                                                                                                                                                              | FCMEN                                                                                                                                     | IESO                                                                                                                           | CLKOUTEN                                                                             | BORE                | EN<1:0>             | _          |

|                     |                                                                                                                                                                                                                                              | bit 13                                                                                                                                    |                                                                                                                                |                                                                                      | •                   |                     | bit 8      |

|                     |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| R/P-1               | R/P-1                                                                                                                                                                                                                                        | R/P-1                                                                                                                                     | R/P-1                                                                                                                          | R/P-1                                                                                | R/P-1               | R/P-1               | R/P-1      |

| CP                  | MCLRE                                                                                                                                                                                                                                        | PWRTE                                                                                                                                     | WD <sup>-</sup>                                                                                                                | ΓE<1:0>                                                                              |                     | FOSC<2:0>           |            |

| bit 7               |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     | bit        |

|                     |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| Legend:             |                                                                                                                                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| R = Readable bit    |                                                                                                                                                                                                                                              | P = Programmat                                                                                                                            | DIE DIT                                                                                                                        |                                                                                      | nted bit, read as ' |                     |            |

| 0' = Bit is cleared | 1                                                                                                                                                                                                                                            | '1' = Bit is set                                                                                                                          |                                                                                                                                | -n = value whe                                                                       | n blank or after E  | SUIK Erase          |            |

| bit 13              | 1 = Fail-Safe Clo                                                                                                                                                                                                                            | afe Clock Monitor E<br>ock Monitor is enal<br>ock Monitor is disa                                                                         | bled                                                                                                                           |                                                                                      |                     |                     |            |

| bit 12              | 1 = Internal/Exte                                                                                                                                                                                                                            | external Switchover<br>ernal Switchover m<br>ernal Switchover m                                                                           | ode is enabled                                                                                                                 |                                                                                      |                     |                     |            |

| bit 11              | 1 = CLKOUT fu                                                                                                                                                                                                                                | ock Out Enable bit<br>unction is disabled<br>unction is enabled                                                                           | I/O or oscillato                                                                                                               | r function on CLKO                                                                   | UT pin.             |                     |            |

| bit 10-9            | 11 = BOR enabl<br>10 = BOR enabl                                                                                                                                                                                                             | ed during operatio olled by SBOREN                                                                                                        | n and disabled i                                                                                                               | •                                                                                    |                     |                     |            |

| bit 8               | Unimplemented: Read as '1'                                                                                                                                                                                                                   |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| bit 7               |                                                                                                                                                                                                                                              | ction bit <sup>(2)</sup><br>mory code protect<br>mory code protect                                                                        |                                                                                                                                |                                                                                      |                     |                     |            |

| bit 6               | $\frac{\text{If LVP bit} = 1}{\text{This bit is ig}}$ $\frac{\text{If LVP bit} = 0}{1 = \text{MCLR}}$                                                                                                                                        | VPP pin function is                                                                                                                       | MCLR; Weak pul                                                                                                                 | I-up enabled.<br>R internally disabled                                               | t Weak pull-up un   | ider control of WPL | A register |

| bit 5               |                                                                                                                                                                                                                                              | -up Timer Enable b<br>abled                                                                                                               |                                                                                                                                |                                                                                      | ,                   |                     |            |

| bit 4-3             | WDTE<1:0>: Wa<br>11 = WDT enab<br>10 = WDT enab                                                                                                                                                                                              | atchdog Timer Ena<br>bled<br>bled while running<br>rolled by the SWD                                                                      | and disabled in                                                                                                                |                                                                                      |                     |                     |            |

| bit 2-0             | FOSC<2:0>: Os           111 =         ECH: Ex           110 =         ECM: Ex           101 =         ECL: Ex           100 =         INTOSC           011 =         EXTRC           010 =         HS oscil           001 =         XT oscil | cillator Selection b<br>kternal Clock, High<br>xternal Clock, Med<br>(ternal Clock, Low-<br>c oscillator: I/O fund<br>oscillator: RC fund | -Power mode: c<br>ium-Power mode<br>Power mode: or<br>ction on OSC1 p<br>tion on OSC1 p<br>crystal/resonato<br>nator on OSC2 p | e: on CLKIN pin<br>n CLKIN pin<br>bin<br>in<br>r on OSC2 pin and<br>bin and OSC1 pin | OSC1 pin            |                     |            |

|                     | -                                                                                                                                                                                                                                            |                                                                                                                                           | -                                                                                                                              | le Power-up Timer.<br>de protection is turr                                          | ned off.            |                     |            |

|                     |                                                                                                                                                   | R/P-1                                  | R/P-1                     | R/P-1             | R/P-1                | R/P-1        | U-1   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------|-------------------|----------------------|--------------|-------|

|                     |                                                                                                                                                   | LVP                                    | DEBUG                     | LPBOR             | BORV                 | STVREN       | _     |

|                     |                                                                                                                                                   | bit 13                                 |                           |                   |                      |              | bit   |

|                     |                                                                                                                                                   |                                        |                           |                   |                      |              |       |

| U-1                 | U-1                                                                                                                                               | U-1                                    | R/P-1                     | U-1               | U-1                  | R/P-1        | R/P-1 |

| _                   | _                                                                                                                                                 | _                                      | VCAPEN <sup>(2)</sup>     | _                 | _                    | WRT<         | 1:0>  |

| bit 7               |                                                                                                                                                   |                                        |                           |                   | I                    | I            | bit   |

|                     |                                                                                                                                                   |                                        |                           |                   |                      |              |       |

| Legend:             |                                                                                                                                                   |                                        |                           |                   |                      |              |       |

| R = Readable bit    | t                                                                                                                                                 | P = Programma                          | ble bit                   | U = Unimpleme     | nted bit, read as '1 |              |       |

| 0' = Bit is cleared | t                                                                                                                                                 | '1' = Bit is set                       |                           | -n = Value whe    | n blank or after B   | ulk Erase    |       |

|                     |                                                                                                                                                   |                                        |                           |                   |                      |              |       |

| bit 13              | LVP: Low-Volta                                                                                                                                    | age Programming                        | Enable bit <sup>(1)</sup> |                   |                      |              |       |

|                     |                                                                                                                                                   | e programming e                        |                           |                   |                      |              |       |

|                     |                                                                                                                                                   | LR/VPP must be u                       | 1 0                       | ning              |                      |              |       |

| bit 12              |                                                                                                                                                   | rcuit Debugger Mo                      |                           |                   |                      |              |       |

|                     |                                                                                                                                                   | )ebugger disabled<br>)ebugger enabled  |                           | •                 |                      | •            |       |

| bit 11              | LPBOR: Low-F                                                                                                                                      |                                        | ,                         |                   |                      | -990         |       |

| 2.1                 |                                                                                                                                                   | r BOR is disabled                      |                           |                   |                      |              |       |

|                     | 0 = Low-Power                                                                                                                                     | r BOR is enabled                       |                           |                   |                      |              |       |

| bit 10              |                                                                                                                                                   | out Reset Voltage                      |                           |                   |                      |              |       |

|                     | <ol> <li>= Brown-out Reset voltage (VBOR), low trip point selected</li> <li>= Brown-out Reset voltage (VBOR), high trip point selected</li> </ol> |                                        |                           |                   |                      |              |       |

| h# 0                |                                                                                                                                                   | <b>U</b>                               | <i>/</i> <b>0 1 1</b>     |                   |                      |              |       |

| bit 9               |                                                                                                                                                   | k Overflow/Under<br>flow or Underflow  |                           |                   |                      |              |       |

|                     | <ol> <li>Stack Overflow or Underflow will cause a Reset</li> <li>Stack Overflow or Underflow will not cause a Reset</li> </ol>                    |                                        |                           |                   |                      |              |       |

| bit 8-5             | Unimplemented: Read as '1'                                                                                                                        |                                        |                           |                   |                      |              |       |

| bit 4               | VCAPEN: Volta                                                                                                                                     | age Regulator Ca                       | pacitor Enable bi         | ts <sup>(1)</sup> |                      |              |       |

|                     | 0 = VCAP funct                                                                                                                                    | ionality is enabled                    | d on VCAP pin             |                   |                      |              |       |

|                     | 1 = All VCAP pi                                                                                                                                   | n functions are di                     | sabled                    |                   |                      |              |       |

| bit 3-2             | Unimplemente                                                                                                                                      | ed: Read as '1'                        |                           |                   |                      |              |       |

| bit 1-0             | WRT<1:0>: Flash Memory Self-Write Protection bits<br>2 kW Flash memory (PIC16(L)F1512):                                                           |                                        |                           |                   |                      |              |       |

|                     |                                                                                                                                                   | ite protection off                     | <u>1512)</u> :            |                   |                      |              |       |

|                     |                                                                                                                                                   | 0h to 1FFh write-p                     | protected, 200h to        | o 7FFh may be m   | nodified by PMCC     | N control    |       |

|                     | 01 = 000                                                                                                                                          | 0h to FFFh write-                      | protected, 400h to        | o 7FFh may be m   | nodified by PMCC     | N control    |       |

|                     |                                                                                                                                                   | Oh to 7FFh write-                      |                           | resses may be n   | nodified by PMCC     | ON control   |       |

|                     |                                                                                                                                                   | emory (PIC16(L)F<br>ite protection off | <u>1513)</u> .            |                   |                      |              |       |

|                     |                                                                                                                                                   | 0h to 1FFh write-p                     | protected, 200h to        | o FFFh may be m   | nodified by PMCC     | N control    |       |

|                     |                                                                                                                                                   | 0h to 7FFh write-p                     | ,                         | ,                 | ,                    |              |       |

|                     |                                                                                                                                                   | Dh to FFFh write-p<br>mory (PIC16F/LF  |                           | •                 | nodified by PMCO     | N control    |       |

|                     |                                                                                                                                                   | ite protection off                     | 1310/1317/1320            | 1.                |                      |              |       |

|                     | 10 = 000                                                                                                                                          | 0h to 1FFh write-p                     |                           |                   |                      |              |       |

|                     |                                                                                                                                                   | Oh to FFFh write-                      |                           |                   |                      |              |       |

|                     |                                                                                                                                                   | 0h to 1FFFh write<br>emory (PIC16F/L   | •                         |                   | modified by PINC     | ON control   |       |

|                     |                                                                                                                                                   | ite protection off                     |                           | <u></u> .         |                      |              |       |

|                     | 10 = 000                                                                                                                                          | 0h to 1FFh write-p                     |                           |                   |                      |              |       |

|                     | 01 - 000                                                                                                                                          |                                        |                           |                   | a madified by DN     | ICON control |       |

|                     |                                                                                                                                                   | 0h to 1FFFh write<br>0h to 3FFFh write |                           |                   |                      |              |       |

### REGISTER 3-3: CONFIGURATION WORD 2

2: Applies to PIC16F151X/152X devices only. On PIC16LF151X/152X, the VCAPEN bit is unimplemented.

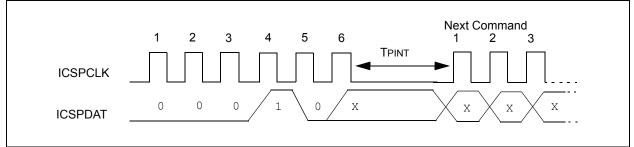

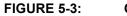

#### 4.3.6 BEGIN INTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. An internal timing mechanism executes the write. The user must allow for the program cycle time, TPINT, for the programming to complete.

The End Externally Timed Programming command is not needed when the Begin Internally Timed Programming is used to start the programming.

The program memory address that is being programmed is not erased prior to being programmed.

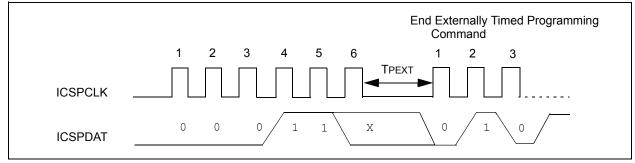

#### 4.3.7 BEGIN EXTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. To complete the programming the End Externally Timed Programming command must be sent in the specified time window defined by TPEXT (see Figure 4-7).

Externally timed writes are not supported for Configuration and Calibration bits. Any externally timed write to the Configuration or Calibration Word will have no effect on the targeted word.

### FIGURE 4-7: BEGIN EXTERNALLY TIMED PROGRAMMING

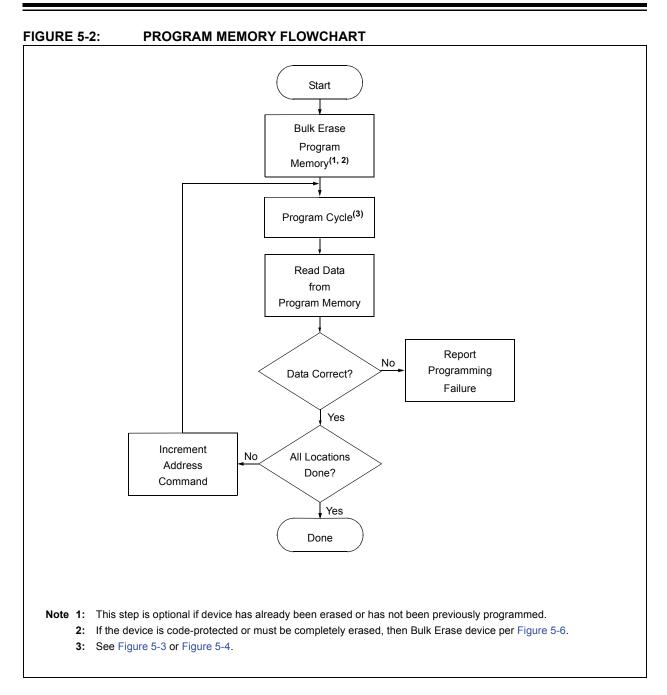

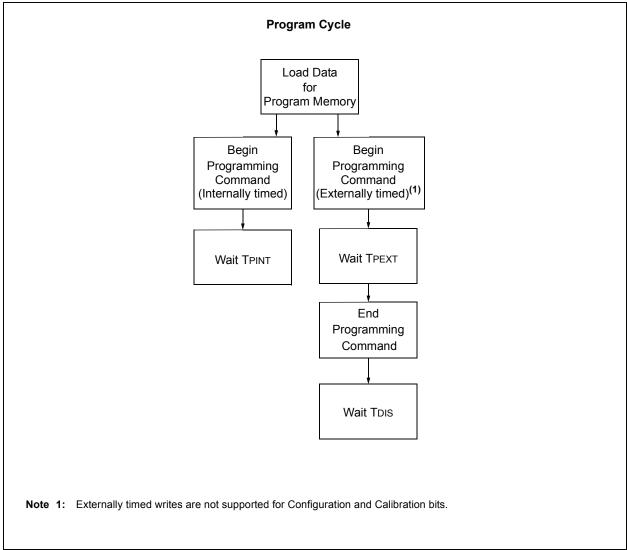

### 5.0 PROGRAMMING ALGORITHMS

The devices use internal latches to temporarily store the 14-bit words used for programming. Refer to Table 4-2 for specific latch information. The data latches allow the user to write the program words with a single Begin Externally Timed Programming or Begin Internally Timed Programming command. The Load Program Data or the Load Configuration command is used to load a single data latch. The data latch will hold the data until the Begin Externally Timed Programming or Begin Internally Timed Programming or Begin Internally Timed Programming command is given.

The data latches are aligned with the LSbs of the address. The PC's address at the time the Begin Externally Timed Programming or Begin Internally Timed Programming command is given will determine which location(s) in memory are written. Writes cannot cross the physical boundary. For example, with the PIC16F1527, attempting to write from address 0002h-0009h will result in data being written to 0008h-000Fh.

If more than the maximum number of data latches are written without a Begin Externally Timed Programming or Begin Internally Timed Programming command, the data in the data latches will be overwritten. The following figures show the recommended flowcharts for programming.

**ONE-WORD PROGRAM CYCLE**

### 7.3 Checksum Computation

The checksum is calculated by two different methods dependent on the setting of the CP Configuration bit.

| MASK VALUES |                        |                        |  |  |  |  |

|-------------|------------------------|------------------------|--|--|--|--|

| Device      | Config. Word 1<br>Mask | Config. Word 2<br>Mask |  |  |  |  |

| PIC16F1512  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16F1513  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16F1516  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16F1517  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16F1518  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16F1519  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16LF1512 | 3EFFh                  | 3E03h                  |  |  |  |  |

| PIC16LF1513 | 3EFFh                  | 3E03h                  |  |  |  |  |

| PIC16LF1516 | 3EFFh                  | 3E03h                  |  |  |  |  |

| PIC16LF1517 | 3EFFh                  | 3E03h                  |  |  |  |  |

| PIC16LF1518 | 3EFFh                  | 3E03h                  |  |  |  |  |

| PIC16LF1519 | 3EFFh                  | 3E03h                  |  |  |  |  |

| PIC16F1526  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16F1527  | 3EFFh                  | 3E13h                  |  |  |  |  |

| PIC16LF1526 | 3EFFh                  | 3E03h                  |  |  |  |  |

| PIC16LF1527 | 3EFFh                  | 3E03h                  |  |  |  |  |

## TABLE 7-1: CONFIGURATION WORD MASK VALUES

### 7.3.1 PROGRAM CODE PROTECTION DISABLED

With the program code protection disabled, the checksum is computed by reading the contents of the PIC16(L)F151X/152X program memory locations and adding up the program memory data starting at address 0000h, up to the maximum user addressable location. Any Carry bit exceeding 16 bits are ignored. Additionally, the relevant bits of the Configuration Words are added to the checksum. All unimplemented Configuration bits are masked to '0'.

#### 7.3.2 PROGRAM CODE PROTECTION ENABLED

With the program code protection enabled, the checksum is computed in the following manner: The Least Significant nibble of each user ID is used to create a 16-bit value. The masked value of user ID location 8000h is the Most Significant nibble. This sum of user IDs is summed with the Configuration Words (all unimplemented Configuration bits are masked to '0').

#### EXAMPLE 7-3: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION ENABLED PIC16F1527, BLANK DEVICE

| PIC16F1 | 527 Configuration Word                                                            | (2) 3F7Fh                                                                   |  |  |  |

|---------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

|         | Configuration Word                                                                | mask <sup>(3)</sup> 3EFFh                                                   |  |  |  |

|         | Configuration Word 2                                                              | (2) 3FFFh                                                                   |  |  |  |

|         | Configuration Word 2                                                              | mask <sup>(3)</sup> 3E13h                                                   |  |  |  |

|         | User ID (8000h) <sup>(1)</sup>                                                    | 0006h                                                                       |  |  |  |

|         | User ID (8001h) <sup>(1)</sup>                                                    | 0007h                                                                       |  |  |  |

|         | User ID (8002h) <sup>(1)</sup>                                                    | 0001h                                                                       |  |  |  |

|         | User ID (8003h) <sup>(1)</sup>                                                    | 0002h                                                                       |  |  |  |

|         | Sum of User IDs <sup>(4)</sup>                                                    | = (0006h and 000Fh) << 12 + (0007h and 000Fh) << 8 +                        |  |  |  |

|         | (0001h and 000Fh) << 4 + (0002h and 000Fh)                                        |                                                                             |  |  |  |

|         | = 6000h + 0700h + 0010h + 0002h                                                   |                                                                             |  |  |  |

|         |                                                                                   | = 6712h                                                                     |  |  |  |

|         | Checksum                                                                          | = (3F7Fh and 3EFFh) + (3FFFh and 3E13h) + Sum of User IDs                   |  |  |  |

|         |                                                                                   | = 3E7Fh +3713h + 6712h                                                      |  |  |  |

|         |                                                                                   | = DCA4h                                                                     |  |  |  |

| Note 1: | : User ID values in this example are random values.                               |                                                                             |  |  |  |

| 2:      | Configuration Word 1 and 2 = all bits are '1' except the code-protect enable bit. |                                                                             |  |  |  |

| 3:      | Configuration Word 1 and bits which read '0'.                                     | Mask = all Configuration Word bits are set to '1', except for unimplemented |  |  |  |

| 4:      |                                                                                   |                                                                             |  |  |  |

<= shift left, thus the LSb of the first user ID value is the MSb of the sum of user IDs and so on, unti the LSb of the last user ID value becomes the LSb of the sum of user IDs.

### EXAMPLE 7-4: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION ENABLED PIC16LF1527, 00AAh AT FIRST AND LAST ADDRESS

|                                                                                                                                                                                                                   | · · · · ·                                                                     |                                                                          |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

| PIC16LF                                                                                                                                                                                                           | 1527 Configuration Word 1 <sup>(2)</sup>                                      | 3F7Fh                                                                    |  |  |  |

|                                                                                                                                                                                                                   | Configuration Word 1 mask <sup>(3)</sup>                                      | 3EFFh                                                                    |  |  |  |

|                                                                                                                                                                                                                   | Configuration Word 2 <sup>(2)</sup>                                           | 3FFFh                                                                    |  |  |  |

|                                                                                                                                                                                                                   | Configuration Word 2 mask <sup>(3), (5)</sup>                                 | ) 3E03h                                                                  |  |  |  |

|                                                                                                                                                                                                                   | User ID (8000h) <sup>(1)</sup>                                                | 000Eh                                                                    |  |  |  |

|                                                                                                                                                                                                                   | User ID (8001h) <sup>(1)</sup>                                                | 0008h                                                                    |  |  |  |

|                                                                                                                                                                                                                   | User ID (8002h) <sup>(1)</sup>                                                | 0005h                                                                    |  |  |  |

|                                                                                                                                                                                                                   | User ID (8003h) <sup>(1)</sup>                                                | 0008h                                                                    |  |  |  |

|                                                                                                                                                                                                                   | Sum of User IDs <sup>(4)</sup> = (000Eh a                                     | and 000Fh) << 12 + (0008h and 000Fh) << 8 +                              |  |  |  |

|                                                                                                                                                                                                                   | (0005h a                                                                      | and 000Fh) << 4 + (0008h and 000Fh)                                      |  |  |  |

|                                                                                                                                                                                                                   | = E000h +                                                                     | 0800h + 0050h + 0008h                                                    |  |  |  |

| = E858h                                                                                                                                                                                                           |                                                                               |                                                                          |  |  |  |

|                                                                                                                                                                                                                   | Checksum = (3F7Fh a                                                           | nd 3EFFh) + (3FFFh and 3E03h) + Sum of User IDs                          |  |  |  |

|                                                                                                                                                                                                                   | = 3E7Fh +3                                                                    | 3E03h + E858h                                                            |  |  |  |

|                                                                                                                                                                                                                   | = 64DAh                                                                       |                                                                          |  |  |  |

| Note 1:                                                                                                                                                                                                           | User ID values in this example are randor                                     | m values                                                                 |  |  |  |

| 2:                                                                                                                                                                                                                | Configuration Word 1 and 2 = all bits are                                     |                                                                          |  |  |  |

| 3:                                                                                                                                                                                                                | •                                                                             |                                                                          |  |  |  |

| <ul> <li>&lt;&lt; = shift left, thus the LSb of the first user ID value is the MSb of the sum of user IDs and so on, unt<br/>the LSb of the last user ID value becomes the LSb of the sum of user IDs.</li> </ul> |                                                                               |                                                                          |  |  |  |

| 5:                                                                                                                                                                                                                | On the PIC16LF1527 device, the $\overline{VCAPE}$ unimplemented bits are '0'. | $\overline{N}$ bit is not implemented in Configuration Word 2; thus, all |  |  |  |

### 8.0 ELECTRICAL SPECIFICATIONS

Refer to device specific data sheet for absolute maximum ratings.

#### TABLE 8-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY MODE

| AC/DC CHARACTERISTICS |                                                                                                     |                            | Standard O<br>Production      |           | <b>J Conditions</b><br>25°C   | ;                   |                                                                            |

|-----------------------|-----------------------------------------------------------------------------------------------------|----------------------------|-------------------------------|-----------|-------------------------------|---------------------|----------------------------------------------------------------------------|

| Sym.                  | Characteristics                                                                                     | Min.                       | Тур.                          | Max.      | Units                         | Conditions/Comments |                                                                            |

|                       |                                                                                                     | Supply Volt                | ages and C                    | urrents   |                               |                     |                                                                            |

| Vdd                   | Supply Voltage                                                                                      | PIC16F151X<br>PIC16F152X   | 2.3                           | _         | 5.5                           | V                   |                                                                            |

|                       | (VDDMIN, VDDMAX)                                                                                    | PIC16LF151X<br>PIC16LF152X | 1.8                           | —         | 3.6                           | V                   |                                                                            |

| VPEW                  | Read/Write and Row Erase opera                                                                      | itions                     | VDDMIN                        |           | VDDMAX                        | V                   |                                                                            |

| VPBE                  | Bulk Erase operations                                                                               |                            | 2.7                           | _         | VDDMAX                        | V                   |                                                                            |

| Iddi                  | Current on VDD, Idle                                                                                |                            | —                             | —         | 1.0                           | mA                  |                                                                            |

| IDDP                  | Current on VDD, Programming                                                                         |                            | —                             | _         | 3.0                           | mA                  |                                                                            |

|                       | VPP                                                                                                 |                            |                               |           |                               |                     |                                                                            |

| IPP                   | Current on MCLR/VPP                                                                                 |                            | _                             | _         | 600                           | μA                  |                                                                            |

| Vінн                  | High voltage on MCLR/VPP for<br>Program/Verify mode entry                                           |                            | 8.0                           | _         | 9.0                           | V                   |                                                                            |

| TVHHR                 | MCLR rise time (VIL to VIHH) for<br>Program/Verify mode entry                                       |                            | _                             | _         | 1.0                           | μs                  |                                                                            |

|                       | I/O pins                                                                                            |                            |                               |           | •                             |                     |                                                                            |

| Viн                   | (ICSPCLK, ICSPDAT, MCLR/VPP) input high level                                                       |                            | 0.8 Vdd                       | _         | _                             | V                   |                                                                            |

| VIL                   | (ICSPCLK, ICSPDAT, MCLR/VPP) input low level                                                        |                            | _                             | _         | 0.2 VDD                       | V                   |                                                                            |

| Vон                   | ICSPDAT output high level                                                                           |                            | Vdd-0.7<br>Vdd-0.7<br>Vdd-0.7 | _         | _                             | V                   | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 2 mA, VDD = 1.8V |

| Vol                   | ICSPDAT output low level                                                                            |                            | _                             | _         | Vss+0.6<br>Vss+0.6<br>Vss+0.6 | V                   | IOH = 8 mA, VDD = 5V<br>IOH = 6 mA, VDD = 3.3V<br>IOH = 3 mA, VDD = 1.8V   |

|                       |                                                                                                     | Programming                | Mode Entry                    | y and Exi | t                             |                     |                                                                            |

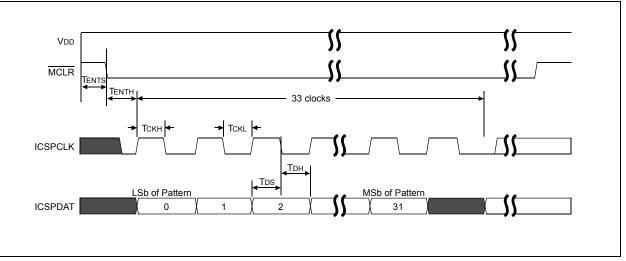

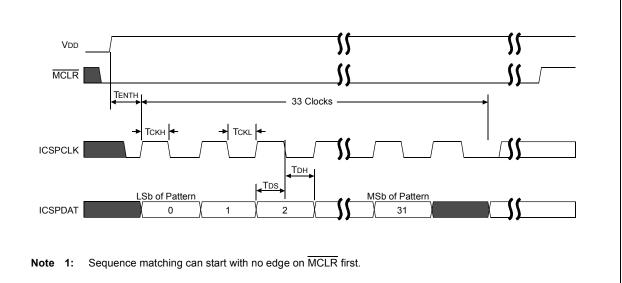

| Tents                 | Programing mode entry setup tim<br>ICSPDAT setup time before VDD                                    |                            | 100                           | _         | _                             | ns                  |                                                                            |

| TENTH                 | Programing mode entry hold time: ICSPCLK,<br>ICSPDAT hold time after VDD or MCLR↑                   |                            | 250                           | —         | _                             | μs                  |                                                                            |

|                       |                                                                                                     | Serial F                   | Program/Vei                   | rify      |                               |                     |                                                                            |

| TCKL                  | Clock Low Pulse Width                                                                               |                            | 100                           | —         | —                             | ns                  |                                                                            |

| Тскн                  | Clock High Pulse Width                                                                              |                            | 100                           |           | —                             | ns                  |                                                                            |

| TDS                   | Data in setup time before clock↓                                                                    |                            | 100                           | —         | -                             | ns                  |                                                                            |

| Трн                   | Data in hold time after clock↓                                                                      |                            | 100                           | —         | -                             | ns                  |                                                                            |

| Тсо                   | Clock↑ to data out valid (during a Read Data command)                                               |                            | 0                             | —         | 80                            | ns                  |                                                                            |

|                       | Clock↓ to data low-impedance (d                                                                     | ,                          |                               |           |                               |                     |                                                                            |

| Tlzd                  | Read Data command)                                                                                  | -                          | 0                             | —         | 80                            | ns                  |                                                                            |

| THZD                  | Clock↓ to data high-impedance (during a Read Data command)                                          |                            | 0                             | _         | 80                            | ns                  |                                                                            |

| TDLY                  | Data input not driven to next clock input (delay required between command/data or command/ command) |                            | 1.0                           | _         | _                             | μs                  |                                                                            |

| TERAB                 | Bulk Erase cycle time                                                                               |                            | —                             | —         | 5                             | ms                  |                                                                            |

| TERAR                 | Row Erase cycle time                                                                                |                            | —                             | —         | 2.5                           | ms                  |                                                                            |

Note 1: Externally timed writes are not supported for Configuration and Calibration bits.

NOTES: