Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1519-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-2: 28-PIN UQFN DIAGRAM FOR PIC16(L)F1512, PIC16(L)F1513, PIC16(L)F1516 AND PIC16(L)F1518

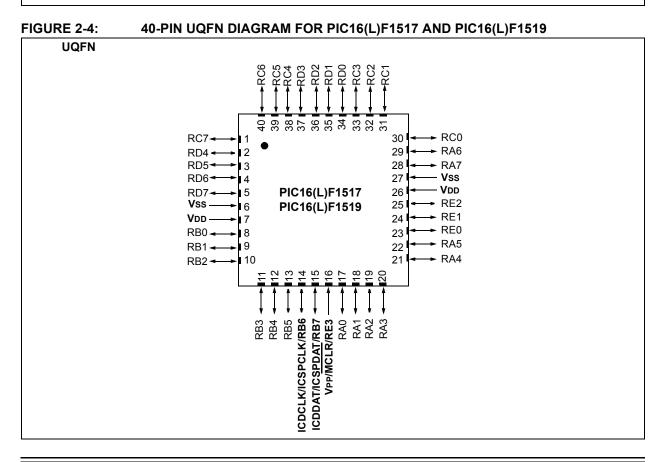

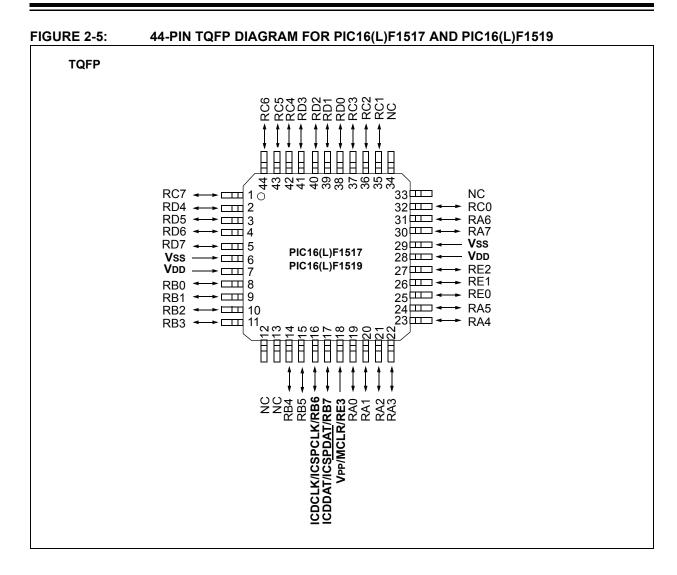

| FIGURE 2-3: | 40-PIN PDIP DIAGRAM F | OR PIC1                        | 6(L)F1517 AND PIC16(L)F1519 |

|-------------|-----------------------|--------------------------------|-----------------------------|

| PDIP        |                       |                                |                             |

|             | Vpp/MCLR/RE3 1        | $\bigcirc$                     | 40 RB7/ICSPDAT/ICDDAT       |

|             | RA0 🔶 2               |                                |                             |

|             | RA1 🗕 🗕 🔤 3           |                                | 38 <b>→</b> RB5             |

|             | RA2 🛶 🗖 4             |                                | 37 <b>→</b> RB4             |

|             | RA3 🛶 🗖 5             |                                | 36 <b>→</b> RB3             |

|             | RA4 🖛 🗕 6             |                                | 35 🗌 🗲 → RB2                |

|             | RA5 🔶 7               |                                | 34 <b>→</b> RB1             |

|             | RE0 🗕 🗕 8             | <u>⊳</u> 6                     | 33 <b>- →</b> RB0           |

|             | RE1 🛶 🕨 🗍 9           | 151                            | 32 - VDD                    |

|             | RE2                   | PIC16(L)F1517<br>PIC16(L)F1519 | 31 <b> </b>                 |

|             | <b>V</b> DD —— 11     | :16(<br>:16(                   | 30 - → RD7                  |

|             | <b>Vss →</b> 12       |                                | 29 🗌 🖛 🕨 RD6                |

|             | RA7 🛶 🗖 13            |                                | 28 🗌 🔸 RD5                  |

|             | RA6 💶 🗖 14            |                                | 27 🗌 🖛 → RD4                |

|             | RC0 🔶 🚺 15            |                                | 26 <b>- →</b> RC7           |

|             | RC1 🗕 🗕 16            |                                | 25 🗌 🛶 RC6                  |

|             | RC2 🗕 ► 🗌 17          |                                | 24 <b>□ ← →</b> RC5         |

|             | RC3 🗕 🏲 🗌 18          |                                | 23 🗌 🖛 RC4                  |

|             | RD0 🗕 ► 🗌 19          |                                | 22 <b>- →</b> RD3           |

|             | RD1 ← ► 20            |                                | 21 RD2                      |

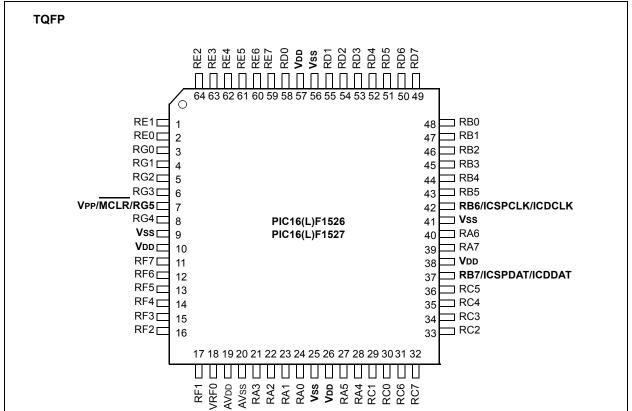

FIGURE 2-7: 64-PIN TQFP DIAGRAM FOR PIC16(L)F1526 AND PIC16(L)F1527

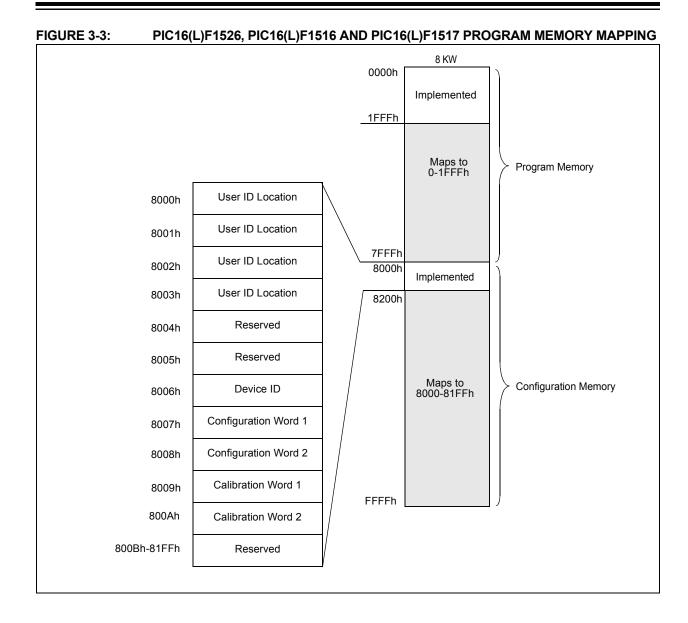

#### 3.1 User ID Location

A user may store identification information (user ID) in four designated locations. The user ID locations are mapped to 8000h-8003h. Each location is 14 bits in length. Code protection has no effect on these memory locations. Each location may be read with code protection enabled or disabled. Note: MPLAB<sup>®</sup> IDE only displays the 7 Least Significant bits (LSb) of each user ID location, the upper bits are not read. It is recommended that only the 7 LSbs be used if MPLAB IDE is the primary tool used to read these addresses.

#### 3.2 Device ID

The device ID word is located at 8006h. This location is read-only and cannot be erased or modified.

#### REGISTER 3-1: DEVICE ID: DEVICE ID REGISTER<sup>(1)</sup>

|         |          | R             | R       | R             | R                  | R   | R     |

|---------|----------|---------------|---------|---------------|--------------------|-----|-------|

|         |          |               |         | DEV           | <8:3>              |     |       |

|         |          | bit 13        |         |               |                    |     | bit 8 |

|         |          |               |         |               |                    |     |       |

| R       | R        | R             | R       | R             | R                  | R   | R     |

|         | DEV<2:0> |               |         |               | REV<4:0>           |     |       |

| bit 7   |          |               |         |               |                    |     | bit 0 |

|         |          |               |         |               |                    |     |       |

| Legend: |          | P = Programma | ble bit | U = Unimpleme | ented bit, read as | ʻ0' |       |

| Legend:           | P = Programmable bit | U = Unimplemented bit, read as '0' |

|-------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit     | '0' = Bit is cleared               |

| -n = Value at POR | '1' = Bit is set     | x = Bit is unknown                 |

bit 13-5 **DEV<8:0>:** Device ID bits

These bits are used to identify the part number.

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision.

Note 1: This location cannot be written.

#### **REGISTER 3-2: CONFIGURATION WORD 1**

|                     |                                                                                                                              | R/P-1                                                                                                                                     | R/P-1                                                                                                                          | R/P-1                                                                                | R/P-1               | R/P-1               | U-1        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------|---------------------|------------|

|                     |                                                                                                                              | FCMEN                                                                                                                                     | IESO                                                                                                                           | CLKOUTEN                                                                             | BORE                | EN<1:0>             | _          |

|                     |                                                                                                                              | bit 13                                                                                                                                    |                                                                                                                                |                                                                                      | •                   |                     | bit 8      |

|                     |                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| R/P-1               | R/P-1                                                                                                                        | R/P-1                                                                                                                                     | R/P-1                                                                                                                          | R/P-1                                                                                | R/P-1               | R/P-1               | R/P-1      |

| CP                  | MCLRE                                                                                                                        | PWRTE                                                                                                                                     | WD <sup>-</sup>                                                                                                                | ΓE<1:0>                                                                              |                     | FOSC<2:0>           |            |

| bit 7               |                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     | bit        |

|                     |                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| Legend:             |                                                                                                                              |                                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| R = Readable bit    |                                                                                                                              | P = Programmat                                                                                                                            | DIE DIT                                                                                                                        |                                                                                      | nted bit, read as ' |                     |            |

| 0' = Bit is cleared | 1                                                                                                                            | '1' = Bit is set                                                                                                                          |                                                                                                                                | -n = value whe                                                                       | n blank or after E  | SUIK Erase          |            |

| bit 13              | 1 = Fail-Safe Clo                                                                                                            | afe Clock Monitor E<br>ock Monitor is enal<br>ock Monitor is disa                                                                         | bled                                                                                                                           |                                                                                      |                     |                     |            |

| bit 12              | 1 = Internal/Exte                                                                                                            | external Switchover<br>ernal Switchover m<br>ernal Switchover m                                                                           | ode is enabled                                                                                                                 |                                                                                      |                     |                     |            |

| bit 11              | 1 = CLKOUT fu                                                                                                                | ock Out Enable bit<br>unction is disabled<br>unction is enabled                                                                           | I/O or oscillato                                                                                                               | r function on CLKO                                                                   | UT pin.             |                     |            |

| bit 10-9            | 11 = BOR enabl<br>10 = BOR enabl                                                                                             | ed during operatio olled by SBOREN                                                                                                        | n and disabled i                                                                                                               | •                                                                                    |                     |                     |            |

| bit 8               | Unimplemente                                                                                                                 | ed: Read as '1'                                                                                                                           |                                                                                                                                |                                                                                      |                     |                     |            |

| bit 7               |                                                                                                                              | ction bit <sup>(2)</sup><br>mory code protect<br>mory code protect                                                                        |                                                                                                                                |                                                                                      |                     |                     |            |

| bit 6               | $\frac{\text{If LVP bit} = 1}{\text{This bit is ig}}$ $\frac{\text{If LVP bit} = 0}{1 = \text{MCLR}}$                        | VPP pin function is                                                                                                                       | MCLR; Weak pul                                                                                                                 | I-up enabled.<br>R internally disabled                                               | t Weak pull-up up   | ider control of WPL | A register |

| bit 5               |                                                                                                                              | -up Timer Enable b<br>abled                                                                                                               |                                                                                                                                |                                                                                      | ,                   |                     |            |

| bit 4-3             | WDTE<1:0>: Wa<br>11 = WDT enab<br>10 = WDT enab                                                                              | atchdog Timer Ena<br>bled<br>bled while running<br>rolled by the SWD                                                                      | and disabled in                                                                                                                |                                                                                      |                     |                     |            |

| bit 2-0             | FOSC<2:0>: Os   111 = ECH: Ex   110 = ECM: Ex   101 = ECL: Ex   100 = INTOSC   011 = EXTRC   010 = HS oscil   001 = XT oscil | cillator Selection b<br>kternal Clock, High<br>xternal Clock, Med<br>(ternal Clock, Low-<br>c oscillator: I/O fund<br>oscillator: RC fund | -Power mode: c<br>ium-Power mode<br>Power mode: or<br>ction on OSC1 p<br>tion on OSC1 p<br>crystal/resonato<br>nator on OSC2 p | e: on CLKIN pin<br>n CLKIN pin<br>bin<br>in<br>r on OSC2 pin and<br>bin and OSC1 pin | OSC1 pin            |                     |            |

|                     | -                                                                                                                            |                                                                                                                                           | -                                                                                                                              | le Power-up Timer.<br>de protection is turr                                          | ned off.            |                     |            |

|                     |                                                                                                                             | R/P-1                                  | R/P-1                     | R/P-1             | R/P-1                | R/P-1        | U-1   |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------|-------------------|----------------------|--------------|-------|--|--|--|

|                     |                                                                                                                             | LVP                                    | DEBUG                     | LPBOR             | BORV                 | STVREN       | _     |  |  |  |

|                     |                                                                                                                             | bit 13                                 |                           |                   |                      |              | bit   |  |  |  |

|                     |                                                                                                                             |                                        |                           |                   |                      |              |       |  |  |  |

| U-1                 | U-1                                                                                                                         | U-1                                    | R/P-1                     | U-1               | U-1                  | R/P-1        | R/P-1 |  |  |  |

| _                   | _                                                                                                                           | _                                      | VCAPEN <sup>(2)</sup>     | _                 | _                    | WRT<         | 1:0>  |  |  |  |

| bit 7               |                                                                                                                             |                                        |                           |                   | I                    | I            | bit   |  |  |  |

|                     |                                                                                                                             |                                        |                           |                   |                      |              |       |  |  |  |

| Legend:             |                                                                                                                             |                                        |                           |                   |                      |              |       |  |  |  |

| R = Readable bit    | t                                                                                                                           | P = Programma                          | ble bit                   | U = Unimpleme     | nted bit, read as '1 |              |       |  |  |  |

| 0' = Bit is cleared | t                                                                                                                           | '1' = Bit is set                       |                           | -n = Value whe    | n blank or after B   | ulk Erase    |       |  |  |  |

|                     |                                                                                                                             |                                        |                           |                   |                      |              |       |  |  |  |

| bit 13              | LVP: Low-Volta                                                                                                              | age Programming                        | Enable bit <sup>(1)</sup> |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | e programming e                        |                           |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | LR/VPP must be u                       | 1 0                       | ning              |                      |              |       |  |  |  |

| bit 12              |                                                                                                                             | rcuit Debugger Mo                      |                           |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | )ebugger disabled<br>)ebugger enabled  |                           | •                 |                      | •            |       |  |  |  |

| bit 11              | LPBOR: Low-F                                                                                                                |                                        | ,                         |                   |                      | -990         |       |  |  |  |

| 2.1                 |                                                                                                                             | r BOR is disabled                      |                           |                   |                      |              |       |  |  |  |

|                     | 0 = Low-Power                                                                                                               | r BOR is enabled                       |                           |                   |                      |              |       |  |  |  |

| bit 10              |                                                                                                                             | out Reset Voltage                      |                           |                   |                      |              |       |  |  |  |

|                     | 1 = Brown-out Reset voltage (VBOR), low trip point selected<br>0 = Brown-out Reset voltage (VBOR), high trip point selected |                                        |                           |                   |                      |              |       |  |  |  |

| h# 0                |                                                                                                                             | <b>U</b>                               | <i>/</i> <b>0 1 1</b>     |                   |                      |              |       |  |  |  |

| bit 9               |                                                                                                                             | k Overflow/Under<br>flow or Underflow  |                           |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | flow or Underflow                      |                           |                   |                      |              |       |  |  |  |

| bit 8-5             | Unimplemented: Read as '1'                                                                                                  |                                        |                           |                   |                      |              |       |  |  |  |

| bit 4               | VCAPEN: Volta                                                                                                               | age Regulator Ca                       | pacitor Enable bi         | ts <sup>(1)</sup> |                      |              |       |  |  |  |

|                     | 0 = VCAP funct                                                                                                              | ionality is enabled                    | d on VCAP pin             |                   |                      |              |       |  |  |  |

|                     | 1 = All VCAP pi                                                                                                             | n functions are di                     | sabled                    |                   |                      |              |       |  |  |  |

| bit 3-2             | Unimplemente                                                                                                                | ed: Read as '1'                        |                           |                   |                      |              |       |  |  |  |

| bit 1-0             |                                                                                                                             | ash Memory Self-                       |                           | bits              |                      |              |       |  |  |  |

|                     |                                                                                                                             | emory (PIC16(L)F<br>ite protection off | <u>1512)</u> :            |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | 0h to 1FFh write-p                     | protected, 200h to        | o 7FFh may be m   | nodified by PMCC     | N control    |       |  |  |  |

|                     | 01 = 000                                                                                                                    | 0h to FFFh write-                      | protected, 400h to        | o 7FFh may be m   | nodified by PMCC     | N control    |       |  |  |  |

|                     |                                                                                                                             | Oh to 7FFh write-                      |                           | resses may be n   | nodified by PMCC     | ON control   |       |  |  |  |

|                     |                                                                                                                             | emory (PIC16(L)F<br>ite protection off | <u>1513)</u> .            |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | 0h to 1FFh write-p                     | protected, 200h to        | o FFFh may be m   | nodified by PMCC     | N control    |       |  |  |  |

|                     |                                                                                                                             | 0h to 7FFh write-p                     | ,                         | ,                 | ,                    |              |       |  |  |  |

|                     |                                                                                                                             | Dh to FFFh write-p<br>mory (PIC16F/LF  |                           | •                 | nodified by PMCO     | N control    |       |  |  |  |

|                     |                                                                                                                             | ite protection off                     | 1310/1317/1320            | 1.                |                      |              |       |  |  |  |

|                     | 10 = 000                                                                                                                    | 0h to 1FFh write-p                     |                           |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | Oh to FFFh write-                      |                           |                   |                      |              |       |  |  |  |

|                     |                                                                                                                             | 0h to 1FFFh write<br>emory (PIC16F/L   | •                         |                   | modified by PINC     | ON control   |       |  |  |  |

|                     |                                                                                                                             | ite protection off                     |                           | <u></u> .         |                      |              |       |  |  |  |

|                     | 10 = 000                                                                                                                    | 0h to 1FFh write-p                     |                           |                   |                      |              |       |  |  |  |

|                     | 01 - 000                                                                                                                    |                                        |                           |                   | a madified by DN     | ICON control |       |  |  |  |

|                     |                                                                                                                             | 0h to 1FFFh write<br>0h to 3FFFh write |                           |                   |                      |              |       |  |  |  |

#### REGISTER 3-3: CONFIGURATION WORD 2

2: Applies to PIC16F151X/152X devices only. On PIC16LF151X/152X, the VCAPEN bit is unimplemented.

#### 4.3 **Program/Verify Commands**

The PIC16(L)F151X/152X 10 implements programming commands; each six bits in length. The commands are summarized in Table 4-1.

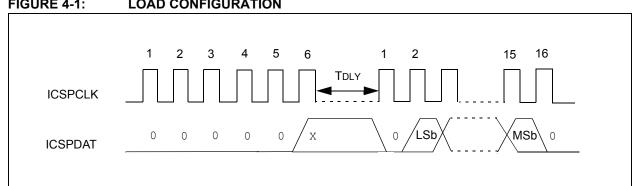

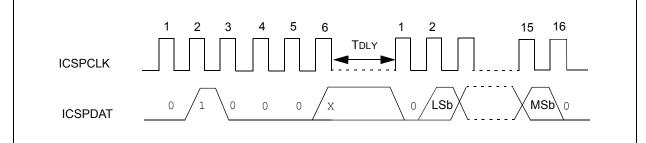

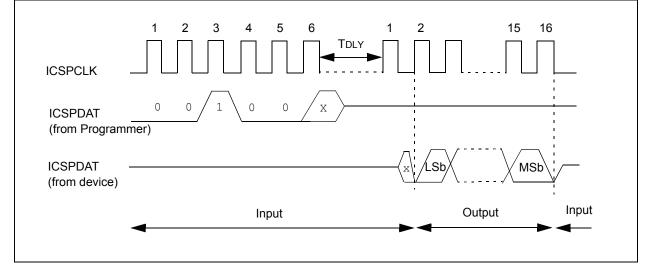

Commands that have data associated with them are specified to have a minimum delay of TDLY between the command and the data. After this delay 16 clocks are required to either clock in or clock out the 14-bit data word. The first clock is for the Start bit and the last clock is for the Stop bit.

#### **TABLE 4-1: COMMAND MAPPING**

| Command                            |   |      |        | Маррі | Data/Note |     |     |                  |

|------------------------------------|---|------|--------|-------|-----------|-----|-----|------------------|

|                                    |   | Bina | ary (M | Sb I  | LSb)      | Hex |     |                  |

| Load Configuration                 | Х | 0    | 0      | 0     | 0         | 0   | 00h | 0, data (14), 0  |

| Load Data For Program Memory       | Х | 0    | 0      | 0     | 1         | 0   | 02h | 0, data (14), 0  |

| Read Data From Program Memory      | Х | 0    | 0      | 1     | 0         | 0   | 04h | 0, data (14), 0  |

| Increment Address                  | Х | 0    | 0      | 1     | 1         | 0   | 06h | —                |

| Reset Address                      | Х | 1    | 0      | 1     | 1         | 0   | 16h | —                |

| Begin Internally Timed Programming | х | 0    | 1      | 0     | 0         | 0   | 08h | —                |

| Begin Externally Timed Programming | Х | 1    | 1      | 0     | 0         | 0   | 18h | —                |

| End Externally Timed Programming   | Х | 0    | 1      | 0     | 1         | 0   | 0Ah | —                |

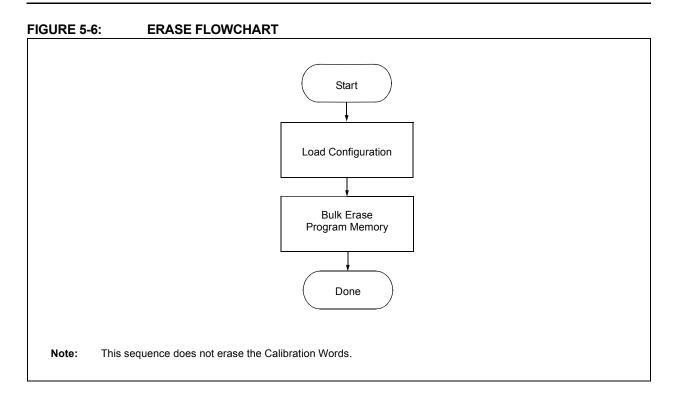

| Bulk Erase Program Memory          | Х | 0    | 1      | 0     | 0         | 1   | 09h | Internally Timed |

| Row Erase Program Memory           | х | 1    | 0      | 0     | 0         | 1   | 11h | Internally Timed |

#### 4.3.1 LOAD CONFIGURATION

The Load Configuration command is used to access the configuration memory (User ID Locations, Configuration Words, Calibration Words). The Load Configuration command sets the address to 8000h and loads the data latches with one word of data (see Figure 4-1).

After issuing the Load Configuration command, use the Increment Address command until the proper address to be programmed is reached. The address is then programmed by issuing either the Begin Internally Timed Programming or Begin Externally Timed Programming command.

Note: Externally timed writes are not supported for Configuration and Calibration bits. Any externally timed write to the Configuration or Calibration Word will have no effect on the targeted word.

The only way to get back to the program memory (address 0) is to exit Program/Verify mode or issue the Reset Address command after the configuration memory has been accessed by the Load Configuration command.

#### FIGURE 4-1: LOAD CONFIGURATION

#### 4.3.2 LOAD DATA FOR PROGRAM MEMORY

The Load Data for Program Memory command is used to load one 14-bit word into the data latches. The word programs into program memory after the Begin Internally Timed Programming or Begin Externally Timed Programming command is issued (see Figure 4-2).

#### FIGURE 4-2: LOAD DATA FOR PROGRAM MEMORY

#### 4.3.3 READ DATA FROM PROGRAM MEMORY

The Read Data from Program Memory command will transmit data bits out of the program memory map currently accessed, starting with the second rising edge of the clock input. The ICSPDAT pin will go into Output mode on the first falling clock edge, and it will revert to Input mode (high-impedance) after the 16th falling edge of the clock. If the program memory is code-protected  $(\overline{CP})$ , the data will be read as zeros (see Figure 4-3).

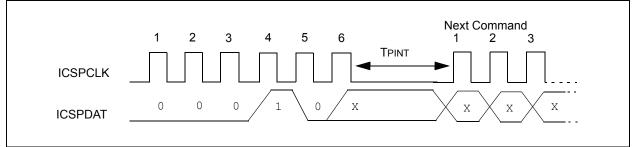

#### 4.3.6 BEGIN INTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. An internal timing mechanism executes the write. The user must allow for the program cycle time, TPINT, for the programming to complete.

The End Externally Timed Programming command is not needed when the Begin Internally Timed Programming is used to start the programming.

The program memory address that is being programmed is not erased prior to being programmed.

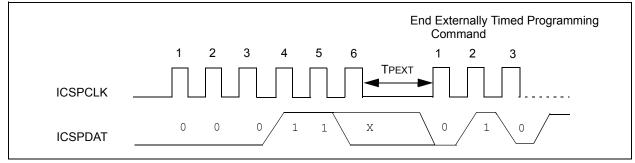

#### 4.3.7 BEGIN EXTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. To complete the programming the End Externally Timed Programming command must be sent in the specified time window defined by TPEXT (see Figure 4-7).

Externally timed writes are not supported for Configuration and Calibration bits. Any externally timed write to the Configuration or Calibration Word will have no effect on the targeted word.

#### FIGURE 4-7: BEGIN EXTERNALLY TIMED PROGRAMMING

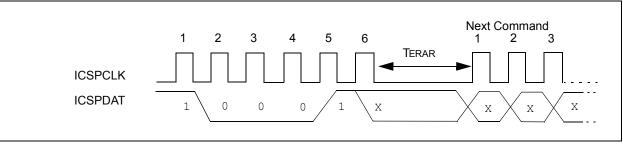

#### 4.3.10 ROW ERASE PROGRAM MEMORY

The Row Erase Program Memory command will erase an individual row. Refer to Table 4-2 for row sizes of specific devices and the PC bits used to address them. If the program memory is code-protected the Row Erase Program Memory command will be ignored. When the address is 8000h-8008h the Row Erase Program Memory command will only erase the user ID locations regardless of the setting of the CP Configuration bit.

After receiving the Row Erase Program Memory command the erase will not complete until the time interval, TERAR, has expired.

#### TABLE 4-2:PROGRAMMING ROW SIZE AND LATCHES

| Devices            | PC     | Row Size | Number of Latches |

|--------------------|--------|----------|-------------------|

| PIC16(L)F151X/152X | <15:5> | 32       | 32                |

#### FIGURE 4-10: ROW ERASE PROGRAM MEMORY

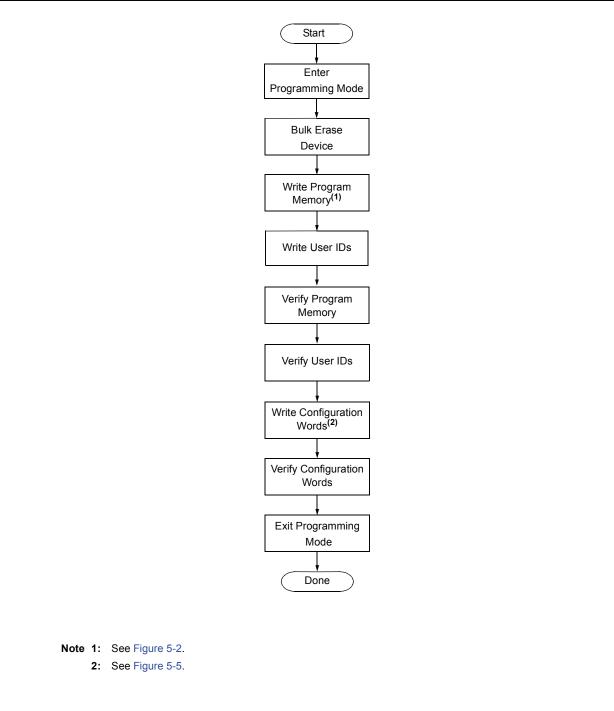

### 5.0 PROGRAMMING ALGORITHMS

The devices use internal latches to temporarily store the 14-bit words used for programming. Refer to Table 4-2 for specific latch information. The data latches allow the user to write the program words with a single Begin Externally Timed Programming or Begin Internally Timed Programming command. The Load Program Data or the Load Configuration command is used to load a single data latch. The data latch will hold the data until the Begin Externally Timed Programming or Begin Internally Timed Programming or Begin Internally Timed Programming command is given.

The data latches are aligned with the LSbs of the address. The PC's address at the time the Begin Externally Timed Programming or Begin Internally Timed Programming command is given will determine which location(s) in memory are written. Writes cannot cross the physical boundary. For example, with the PIC16F1527, attempting to write from address 0002h-0009h will result in data being written to 0008h-000Fh.

If more than the maximum number of data latches are written without a Begin Externally Timed Programming or Begin Internally Timed Programming command, the data in the data latches will be overwritten. The following figures show the recommended flowcharts for programming.

### 8.0 ELECTRICAL SPECIFICATIONS

Refer to device specific data sheet for absolute maximum ratings.

#### TABLE 8-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY MODE

| AC/DC C | HARACTERISTICS                                                                   |                               | Standard C<br>Production |                               | <b>J Conditions</b><br>25°C | ;                                                                          |                     |

|---------|----------------------------------------------------------------------------------|-------------------------------|--------------------------|-------------------------------|-----------------------------|----------------------------------------------------------------------------|---------------------|

| Sym.    | Characteristics                                                                  |                               | Min.                     | Тур.                          | Max.                        | Units                                                                      | Conditions/Comments |

|         |                                                                                  | Supply Volt                   | ages and C               | urrents                       |                             |                                                                            |                     |

| Vdd     | Supply Voltage                                                                   | PIC16F151X<br>PIC16F152X      | 2.3                      | _                             | 5.5                         | V                                                                          |                     |

|         | (VDDMIN, VDDMAX)                                                                 | PIC16LF151X<br>PIC16LF152X    | 1.8                      | —                             | 3.6                         | V                                                                          |                     |

| VPEW    | Read/Write and Row Erase opera                                                   | itions                        | VDDMIN                   |                               | VDDMAX                      | V                                                                          |                     |

| VPBE    | Bulk Erase operations                                                            |                               | 2.7                      | _                             | VDDMAX                      | V                                                                          |                     |

| Iddi    | Current on VDD, Idle                                                             |                               | —                        | —                             | 1.0                         | mA                                                                         |                     |

| IDDP    | Current on VDD, Programming                                                      |                               | —                        | _                             | 3.0                         | mA                                                                         |                     |

|         | VPP                                                                              |                               |                          |                               |                             |                                                                            |                     |

| IPP     | Current on MCLR/VPP                                                              |                               | _                        | _                             | 600                         | μA                                                                         |                     |

| Vінн    | High voltage on MCLR/VPP for<br>Program/Verify mode entry                        |                               | 8.0                      | _                             | 9.0                         | V                                                                          |                     |

| TVHHR   | MCLR rise time (VIL to VIHH) for<br>Program/Verify mode entry                    |                               | _                        | _                             | 1.0                         | μs                                                                         |                     |

|         | I/O pins                                                                         |                               |                          |                               | •                           |                                                                            |                     |

| Viн     | (ICSPCLK, ICSPDAT, MCLR/VPP<br>level                                             | 0.8 Vdd                       | _                        | _                             | V                           |                                                                            |                     |

| VIL     | (ICSPCLK, ICSPDAT, MCLR/VPP                                                      | _                             | _                        | 0.2 VDD                       | V                           |                                                                            |                     |

| Vон     | ICSPDAT output high level                                                        | Vdd-0.7<br>Vdd-0.7<br>Vdd-0.7 | _                        | _                             | V                           | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 2 mA, VDD = 1.8V |                     |

| Vol     | ICSPDAT output low level                                                         | _                             | _                        | Vss+0.6<br>Vss+0.6<br>Vss+0.6 | V                           | IOH = 8 mA, VDD = 5V<br>IOH = 6 mA, VDD = 3.3V<br>IOH = 3 mA, VDD = 1.8V   |                     |

|         |                                                                                  | Programming                   | Mode Entry               | y and Exi                     | t                           |                                                                            |                     |

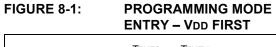

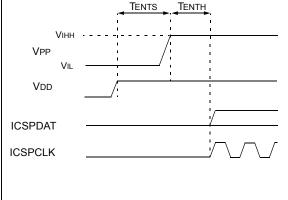

| Tents   | Programing mode entry setup tim<br>ICSPDAT setup time before VDD                 |                               | 100                      | _                             | _                           | ns                                                                         |                     |

| TENTH   | Programing mode entry hold time: ICSPCLK, ICSPDAT hold time after VDD or MCLR↑   |                               | 250                      | —                             | _                           | μs                                                                         |                     |

|         |                                                                                  | Serial F                      | Program/Vei              | rify                          |                             |                                                                            |                     |

| TCKL    | Clock Low Pulse Width                                                            |                               | 100                      | —                             | —                           | ns                                                                         |                     |

| Тскн    | Clock High Pulse Width                                                           |                               | 100                      |                               | —                           | ns                                                                         |                     |

| TDS     | Data in setup time before clock↓                                                 |                               | 100                      | —                             | -                           | ns                                                                         |                     |

| Трн     | Data in hold time after clock↓                                                   |                               | 100                      | —                             | -                           | ns                                                                         |                     |

| Тсо     | Clock↑ to data out valid (during a Read Data command)                            |                               | 0                        | —                             | 80                          | ns                                                                         |                     |

|         | Clock↓ to data low-impedance (d                                                  | uring a                       |                          |                               |                             |                                                                            |                     |

| Tlzd    | Read Data command)                                                               | -                             | 0                        | —                             | 80                          | ns                                                                         |                     |

| THZD    | Clock↓ to data high-impedance (<br>Read Data command)                            | -                             | 0                        | _                             | 80                          | ns                                                                         |                     |

| TDLY    | Data input not driven to next clock<br>required between command/data<br>command) |                               | 1.0                      | _                             | _                           | μs                                                                         |                     |

| TERAB   | Bulk Erase cycle time                                                            |                               | —                        | —                             | 5                           | ms                                                                         |                     |

| TERAR   | Row Erase cycle time                                                             |                               | —                        | —                             | 2.5                         | ms                                                                         |                     |

Note 1: Externally timed writes are not supported for Configuration and Calibration bits.

#### TABLE 8-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY

| AC/DC CHARACTERISTICS |                                                           | Standard Operating Conditions<br>Production tested at 25°C |      |          |          |                                       |  |

|-----------------------|-----------------------------------------------------------|------------------------------------------------------------|------|----------|----------|---------------------------------------|--|

| Sym.                  | Characteristics                                           | Min.                                                       | Тур. | Max.     | Units    | Conditions/Comments                   |  |

| TPINT                 | Internally timed programming operation time               |                                                            |      | 2.5<br>5 | ms<br>ms | Program memory<br>Configuration Words |  |

| TPEXT                 | Externally timed programming pulse                        | 1.0                                                        | —    | 2.1      | ms       | Note 1                                |  |

| TDIS                  | Time delay from program to compare<br>(HV discharge time) | 300                                                        | —    | —        | μs       |                                       |  |

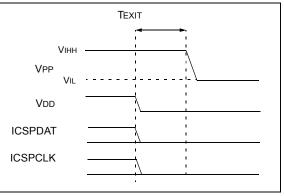

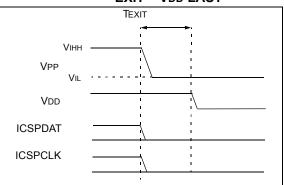

| TEXIT                 | Time delay when exiting Program/Verify mode               | 1                                                          | —    |          | μS       |                                       |  |

Note 1: Externally timed writes are not supported for Configuration and Calibration bits.

#### 8.1 AC Timing Diagrams

#### FIGURE 8-2:

PROGRAMMING MODE ENTRY – VPP FIRST

### FIGURE 8-3:

#### PROGRAMMING MODE EXIT – VPP LAST

FIGURE 8-4:

#### PROGRAMMING MODE EXIT – VDD LAST

### APPENDIX A: REVISION HISTORY

### **Revision A (08/2010)**

Original release of this document.

#### Revision B (09/2011)

Added PIC16(L)F1512/1513 devices; Added new Figures 3-1 and 3-2; Updated Registers 3-1, 3-2 and 3-3 to new format; Updated Register 3-3 to add 2 kW and 4 kW Flash memory; Added Notes to Examples 7-1 to 7-4; Updated Table 8-1; Other minor corrections.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2009

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010-2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-61341-635-8

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.