Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            | • 11                                                                       |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 28x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1519t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.2 Pin Utilization

Five pins are needed for ICSP $^{\text{TM}}$  programming. The pins are listed in Table 1-1 and Table 1-2.

TABLE 1-1: PIN DESCRIPTIONS DURING PROGRAMMING – PIC16(L)F1526 AND PIC16(L)F1527

| Pin Name     | During Programming  |                  |                                              |  |  |

|--------------|---------------------|------------------|----------------------------------------------|--|--|

| Pili Name    | Function            | Pin Type         | Pin Description                              |  |  |

| RB6          | ICSPCLK             | I                | Clock Input – Schmitt Trigger Input          |  |  |

| RB7          | ICSPDAT             | I/O              | Data Input/Output – Schmitt Trigger Input    |  |  |

| RG5/MCLR/VPP | Program/Verify mode | P <sup>(1)</sup> | Program Mode Select/Programming Power Supply |  |  |

| VDD          | Vdd                 | Р                | Power Supply                                 |  |  |

| Vss          | Vss                 | Р                | Ground                                       |  |  |

**Legend:** I = Input, O = Output, P = Power

Note 1: The programming high voltage is internally generated. To activate the Program/Verify mode, high voltage needs to be applied to MCLR input. Since the MCLR is used for a level source, MCLR does not draw any significant current.

TABLE 1-2: PIN DESCRIPTIONS DURING PROGRAMMING – PIC16(L)F1512, PIC16(L)F1513, PIC16(L)F1516, PIC16(L)F1517, PIC16(L)F1518 and PIC16(L)F1519

| Din Nome     | During Programming  |                  |                                              |  |  |

|--------------|---------------------|------------------|----------------------------------------------|--|--|

| Pin Name     | Function            | Pin Type         | Pin Description                              |  |  |

| RB6          | ICSPCLK             | I                | Clock Input – Schmitt Trigger Input          |  |  |

| RB7          | ICSPDAT             | I/O              | Data Input/Output – Schmitt Trigger Input    |  |  |

| RE3/MCLR/VPP | Program/Verify mode | P <sup>(1)</sup> | Program Mode Select/Programming Power Supply |  |  |

| VDD          | VDD                 | Р                | Power Supply                                 |  |  |

| Vss          | Vss                 | Р                | Ground                                       |  |  |

**Legend:** I = Input, O = Output, P = Power

Note 1: The programming high voltage is internally generated. To activate the Program/Verify mode, high voltage needs to be applied to MCLR input. Since the MCLR is used for a level source, MCLR does not draw any significant current.

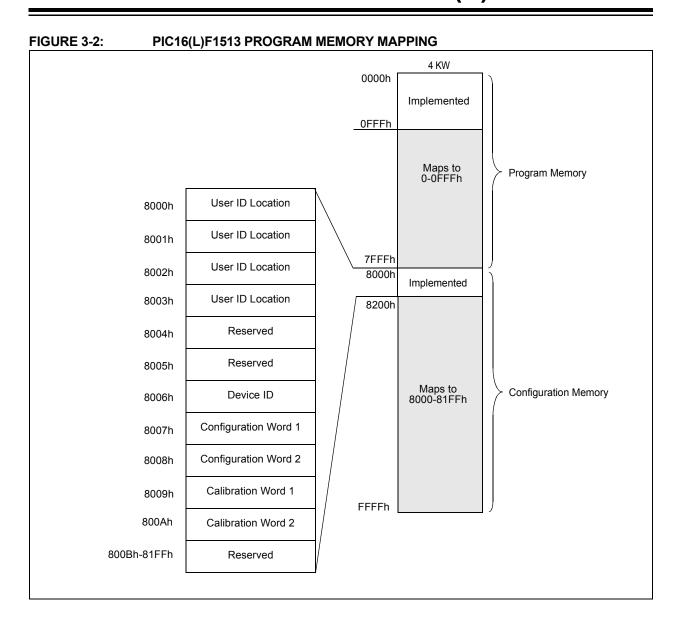

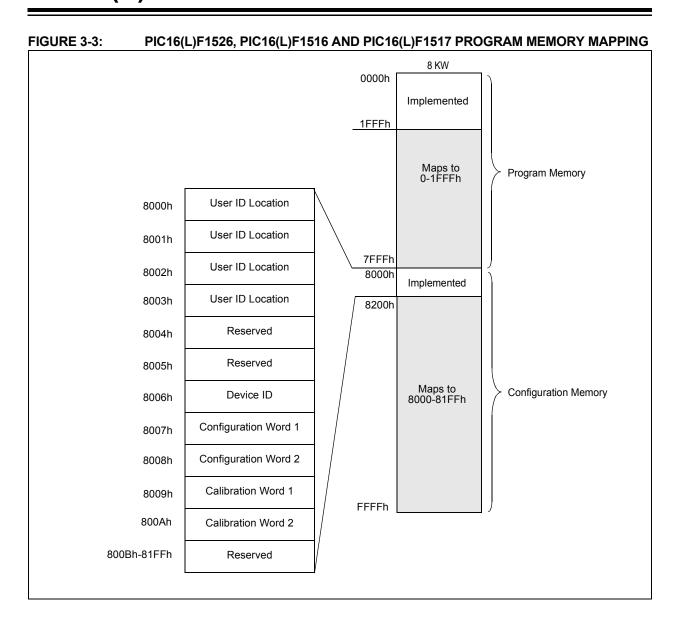

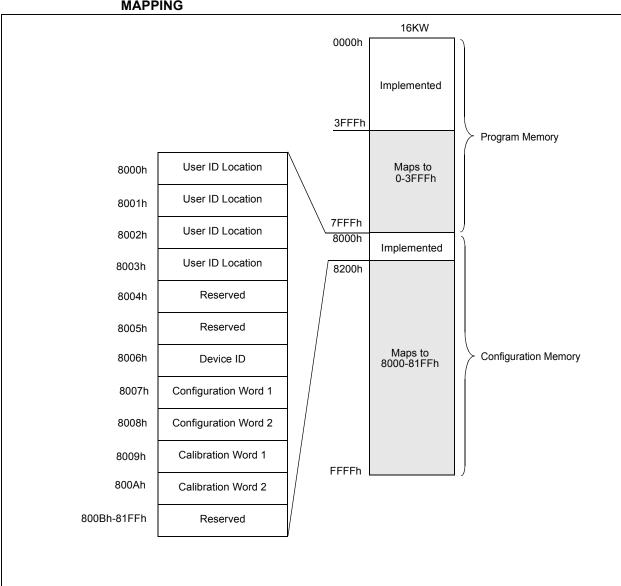

FIGURE 3-4: PIC16(L)F1527, PIC16(L)F1518 AND PIC16(L)F1519 PROGRAM MEMORY MAPPING

### **REGISTER 3-2: CONFIGURATION WORD 1**

| R/P-1  | R/P-1 | R/P-1    | R/P-1 | R/P-1  | U-1 |     |

|--------|-------|----------|-------|--------|-----|-----|

| FCMEN  | IESO  | CLKOUTEN | BORE  | N<1:0> | _   |     |

| bit 13 |       |          |       |        | bit | t 8 |

| R/P-1 | R/P-1 | R/P-1 | R/P-1     | R/P-1 | R/P-1     | R/P-1 | R/P-1 |

|-------|-------|-------|-----------|-------|-----------|-------|-------|

| CP    | MCLRE | PWRTE | WDTE<1:0> |       | FOSC<2:0> |       |       |

| bit 7 |       |       |           |       |           |       | bit 0 |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '1

'0' = Bit is cleared '1' = Bit is set -n = Value when blank or after Bulk Erase

bit 13 FCMEN: Fail-Safe Clock Monitor Enable bit

1 = Fail-Safe Clock Monitor is enabled

0 = Fail-Safe Clock Monitor is disabled

bit 12 IESO: Internal External Switchover bit

1 = Internal/External Switchover mode is enabled 0 = Internal/External Switchover mode is disabled

bit 11 CLKOUTEN: Clock Out Enable bit

1 = CLKOUT function is disabled. I/O or oscillator function on CLKOUT pin.

0 = CLKOUT function is enabled on CLKOUT pin

bit 10-9 **BOREN<1:0>:** Brown-out Reset Enable bits<sup>(1)</sup>

11 = BOR enabled

10 = BOR enabled during operation and disabled in Sleep

01 = BOR controlled by SBOREN bit of the PCON register

00 = BOR disabled

bit 8 **Unimplemented:** Read as '1'

bit 7 **CP**: Code Protection bit<sup>(2)</sup>

1 = Program memory code protection is disabled

0 = Program memory code protection is enabled

bit 6 MCLRE: MCLR/VPP Pin Function Select bit

If LVP bit = 1:

This bit is ignored.

If LVP bit = 0:

1 =  $\overline{MCLR}/VPP$  pin function is  $\overline{MCLR}$ ; Weak pull-up enabled.

0 = MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of WPUA register.

bit 5 **PWRTE**: Power-up Timer Enable bit<sup>(1)</sup>

1 = PWRT disabled

0 = PWRT enabled

bit 4-3 WDTE<1:0>: Watchdog Timer Enable bit

11 = WDT enabled

10 = WDT enabled while running and disabled in Sleep

01 = WDT controlled by the SWDTEN bit in the WDTCON register

00 = WDT disabled

bit 2-0 FOSC<2:0>: Oscillator Selection bits

111 = ECH: External Clock, High-Power mode: on CLKIN pin

110 = ECM: External Clock, Medium-Power mode: on CLKIN pin

101 = ECL: External Clock, Low-Power mode: on CLKIN pin

100 = INTOSC oscillator: I/O function on OSC1 pin

011 = EXTRC oscillator: RC function on OSC1 pin

010 = HS oscillator: High-speed crystal/resonator on OSC2 pin and OSC1 pin

001 = XT oscillator: Crystal/resonator on OSC2 pin and OSC1 pin

000 = LP oscillator: Low-power crystal on OSC2 pin and OSC1 pin

Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

2: The entire program memory will be erased when the code protection is turned off.

### **REGISTER 3-3: CONFIGURATION WORD 2**

| R/P-1  | R/P-1 | R/P-1 | R/P-1 | R/P-1  | U-1   |

|--------|-------|-------|-------|--------|-------|

| LVP    | DEBUG | LPBOR | BORV  | STVREN | _     |

| bit 13 |       |       |       |        | bit 8 |

| U-1   | U-1 | U-1 | R/P-1                 | U-1 | U-1 | R/P-1 | R/P-1 |

|-------|-----|-----|-----------------------|-----|-----|-------|-------|

| _     | _   | _   | VCAPEN <sup>(2)</sup> | _   | _   | WRT<  | :1:0> |

| bit 7 |     |     |                       |     |     |       | bit 0 |

| Legend:              |                      |                                           |

|----------------------|----------------------|-------------------------------------------|

| R = Readable bit     | P = Programmable bit | U = Unimplemented bit, read as '1         |

| '0' = Bit is cleared | '1' = Bit is set     | -n = Value when blank or after Bulk Erase |

bit 13 LVP: Low-Voltage Programming Enable bit<sup>(1)</sup>

1 = Low-voltage programming enabled

0 = HV on  $\overline{MCLR}/VPP$  must be used for programming

bit 12 **DEBUG:** In-Circuit Debugger Mode bit

${\tt 1}$  = In-Circuit Debugger disabled, ICSPCLK and ICSPDAT are general purpose I/O pins

0 = In-Circuit Debugger enabled, ICSPCLK and ICSPDAT are dedicated to the debugger

bit 11 LPBOR: Low-Power BOR

1 = Low-Power BOR is disabled

0 = Low-Power BOR is enabled

bit 10 BORV: Brown-out Reset Voltage Selection bit

1 = Brown-out Reset voltage (VBOR), low trip point selected

0 = Brown-out Reset voltage (VBOR), high trip point selected

bit 9 STVREN: Stack Overflow/Underflow Reset Enable bit

1 = Stack Overflow or Underflow will cause a Reset

0 = Stack Overflow or Underflow will not cause a Reset

bit 8-5 **Unimplemented:** Read as '1'

bit 4

VCAPEN: Voltage Regulator Capacitor Enable bits<sup>(1)</sup>

0 = VCAP functionality is enabled on VCAP pin

1 = All VCAP pin functions are disabled

bit 3-2 Unimplemented: Read as '1'

bit 1-0 WRT<1:0>: Flash Memory Self-Write Protection bits

2 kW Flash memory (PIC16(L)F1512):

11 = Write protection off

10 = 000h to 1FFh write-protected, 200h to 7FFh may be modified by PMCON control

01 = 000h to FFFh write-protected, 400h to 7FFh may be modified by PMCON control

00 = 000h to 7FFh write-protected, no addresses may be modified by PMCON control

4 kW Flash memory (PIC16(L)F1513):

11 = Write protection off

10 = 000h to 1FFh write-protected, 200h to FFFh may be modified by PMCON control

01 = 000h to 7FFh write-protected, 800h to FFFh may be modified by PMCON control

00 = 000h to FFFh write-protected, no addresses may be modified by PMCON control

8 kW Flash memory (PIC16F/LF1516/1517/1526):

11 = Write protection off

10 = 000h to 1FFh write-protected, 200h to 1FFFh may be modified by PMCON control

01 = 000h to FFFh write-protected, 1000h to 1FFFh may be modified by PMCON control

00 = 000h to 1FFFh write-protected, no addresses may be modified by PMCON control

16 kW Flash memory (PIC16F/LF1518/1519/1527):

11 = Write protection off

10 = 000h to 1FFh write-protected, 200h to 3FFFh may be modified by PMCON control

01 = 000h to 1FFFh write-protected, 2000h to 3FFFh may be modified by PMCON control

00 = 000h to 3FFFh write-protected, no addresses may be modified by PMCON control

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

Applies to PIC16F151X/152X devices only. On PIC16LF151X/152X, the VCAPEN bit is unimplemented.

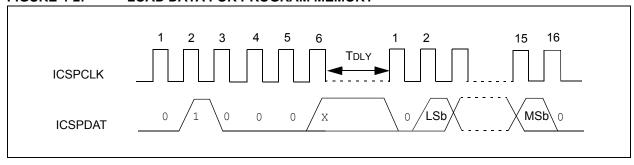

# 4.3.2 LOAD DATA FOR PROGRAM MEMORY

The Load Data for Program Memory command is used to load one 14-bit word into the data latches. The word programs into program memory after the Begin Internally Timed Programming or Begin Externally Timed Programming command is issued (see Figure 4-2).

FIGURE 4-2: LOAD DATA FOR PROGRAM MEMORY

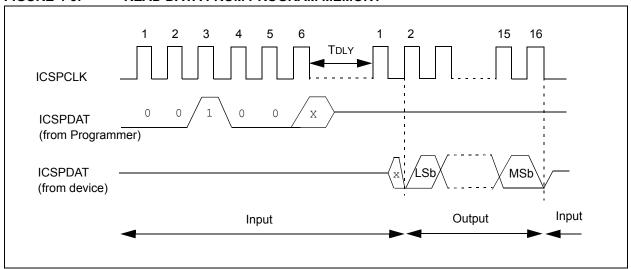

## 4.3.3 READ DATA FROM PROGRAM MEMORY

The Read Data from Program Memory command will transmit data bits out of the program memory map currently accessed, starting with the second rising edge of the clock input. The ICSPDAT pin will go into Output mode on the first falling clock edge, and it will revert to Input mode (high-impedance) after the 16th falling edge of the clock. If the program memory is code-protected  $(\overline{CP})$ , the data will be read as zeros (see Figure 4-3).

FIGURE 4-3: READ DATA FROM PROGRAM MEMORY

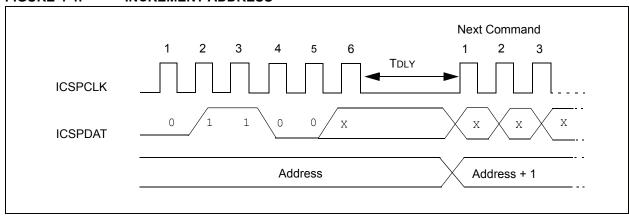

### 4.3.4 INCREMENT ADDRESS

The address is incremented when this command is received. It is not possible to decrement the address. To reset this counter, the user must use the Reset Address command or exit Program/Verify mode and reenter it. If the address is incremented from address 7FFFh, it will wrap-around to location 0000h. If the address is incremented from FFFFh, it will wrap-around to location 8000h.

FIGURE 4-4: INCREMENT ADDRESS

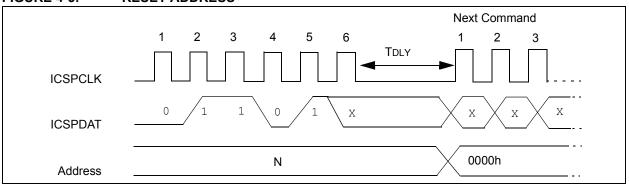

### 4.3.5 RESET ADDRESS

The Reset Address command will reset the address to 0000h, regardless of the current value. The address is used in program memory or the configuration memory.

FIGURE 4-5: RESET ADDRESS

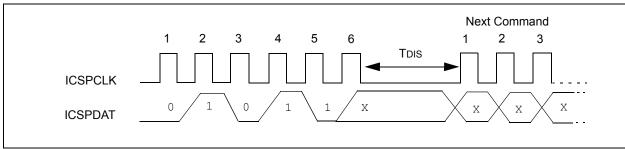

# 4.3.8 END EXTERNALLY TIMED PROGRAMMING

This command is required after a Begin Externally Timed Programming command is given. This command must be sent within the time window specified by TPEXT after the Begin Externally Timed Programming command is sent.

After sending the End Externally Timed Programming command, an additional delay (TDIS) is required before sending the next command. This delay is longer than the delay ordinarily required between other commands (see Figure 4-8).

### FIGURE 4-8: END EXTERNALLY TIMED PROGRAMMING

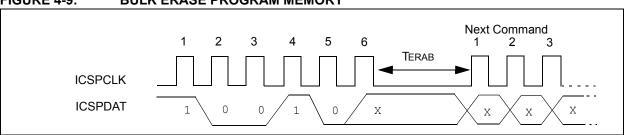

### 4.3.9 BULK ERASE PROGRAM MEMORY

The Bulk Erase Program Memory command performs two different functions dependent on the current state of the address.

Address 0000h-7FFFh:

Program Memory is erased Configuration Words are erased

Address 8000h-8008h:

Program Memory is erased Configuration Words are erased User ID Locations are erased

A Bulk Erase Program Memory command should not be issued when the address is greater than 8008h.

After receiving the Bulk Erase Program Memory command the erase will not complete until the time interval, TERAB, has expired.

### FIGURE 4-9: BULK ERASE PROGRAM MEMORY

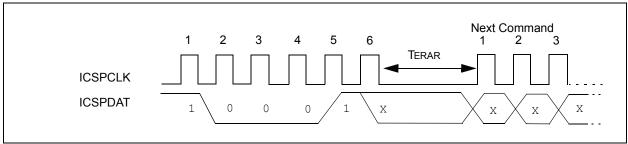

#### 4.3.10 **ROW ERASE PROGRAM MEMORY**

The Row Erase Program Memory command will erase an individual row. Refer to Table 4-2 for row sizes of specific devices and the PC bits used to address them. If the program memory is code-protected the Row Erase Program Memory command will be ignored. When the address is 8000h-8008h the Row Erase Program Memory command will only erase the user ID locations regardless of the setting of the CP Configuration bit.

After receiving the Row Erase Program Memory command the erase will not complete until the time interval, TERAR, has expired.

**TABLE 4-2:** PROGRAMMING ROW SIZE AND LATCHES

| Devices            | PC     | Row Size | Number of Latches |

|--------------------|--------|----------|-------------------|

| PIC16(L)F151X/152X | <15:5> | 32       | 32                |

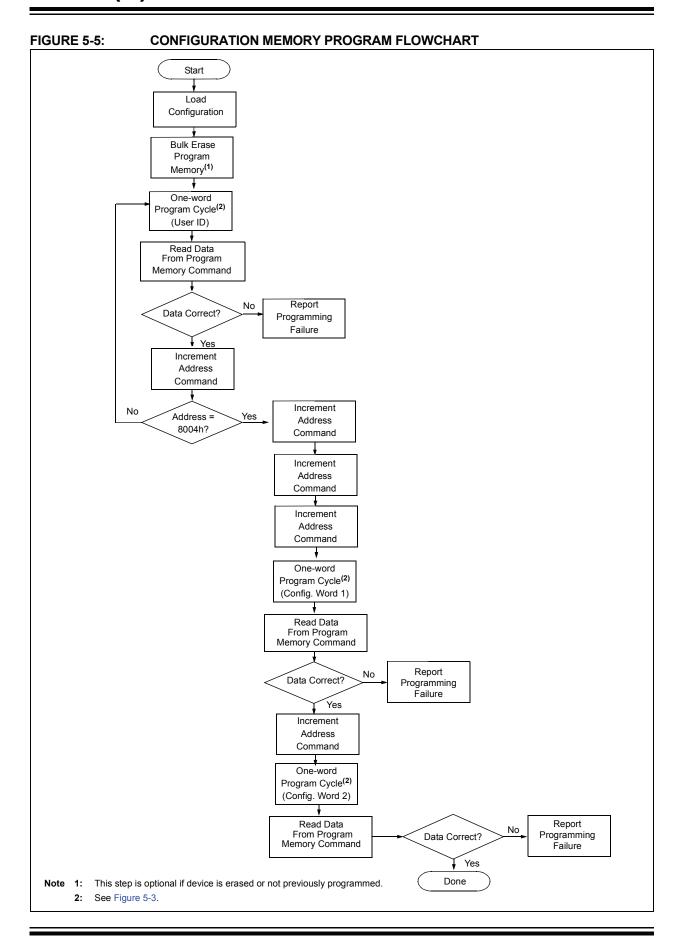

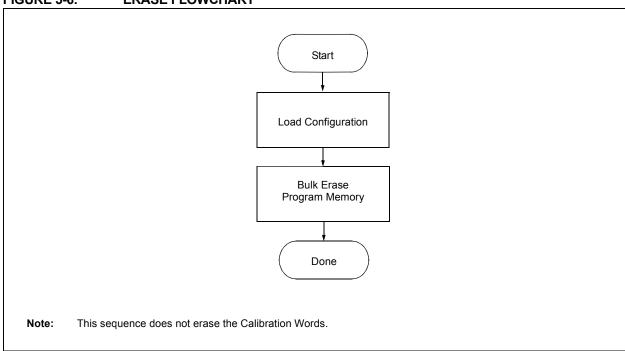

### 5.0 PROGRAMMING ALGORITHMS

The devices use internal latches to temporarily store the 14-bit words used for programming. Refer to Table 4-2 for specific latch information. The data latches allow the user to write the program words with a single Begin Externally Timed Programming or Begin Internally Timed Programming command. The Load Program Data or the Load Configuration command is used to load a single data latch. The data latch will hold the data until the Begin Externally Timed Programming or Begin Internally Timed Programming command is given.

The data latches are aligned with the LSbs of the address. The PC's address at the time the Begin Externally Timed Programming or Begin Internally Timed Programming command is given will determine which location(s) in memory are written. Writes cannot cross the physical boundary. For example, with the PIC16F1527, attempting to write from address 0002h-0009h will result in data being written to 0008h-000Fh.

If more than the maximum number of data latches are written without a Begin Externally Timed Programming or Begin Internally Timed Programming command, the data in the data latches will be overwritten. The following figures show the recommended flowcharts for programming.

### FIGURE 5-6: ERASE FLOWCHART

### 6.0 CODE PROTECTION

Code protection is controlled using the  $\overline{\text{CP}}$  bit in Configuration Word 1. When code protection is enabled, all program memory locations (0000h-7FFFh) read as all '0'. Further programming is disabled for the program memory (0000h-7FFFh).

The user ID locations and Configuration Words can be programmed and read out regardless of the code protection settings.

### 6.1 Program Memory

Code protection is enabled by programming the  $\overline{CP}$  bit in Configuration Word 1 register to '0'.

The only way to disable code protection is to use the Bulk Erase Program Memory command.

### 7.0 HEX FILE USAGE

In the hex file there are two bytes per program word stored in the Intel<sup>®</sup> INHX32 hex format. Data is stored LSB first, MSB second. Because there are two bytes per word, the addresses in the hex file are 2x the address in program memory. (Example: Configuration Word 1 is stored at 8007h on the PIC16(L)F151X/152X. In the hex file this will be referenced as 1000Eh-1000Fh).

### 7.1 Configuration Word

To allow portability of code, it is strongly recommended that the programmer is able to read the Configuration Words and user ID locations from the hex file. If the Configuration Words information was not present in the hex file, a simple warning message may be issued. Similarly, while saving a hex file, Configuration Words and user ID information should be included.

### 7.2 Device ID and Revision

If a device ID is present in the hex file at 1000Ch-1000Dh (8006h on the part), the programmer should verify the device ID (excluding the revision) against the value read from the part. On a mismatch condition the programmer should generate a warning message.

# EXAMPLE 7-1: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION DISABLED PIC16F1527, BLANK DEVICE

PIC16F1527 Sum of Memory addresses 0000h-3FFFh<sup>(1)</sup> C000h

Configuration Word 1<sup>(2)</sup> 3FFFh

Configuration Word 1 mask<sup>(3)</sup> 3EFFh

Configuration Word 2<sup>(2)</sup> 3FFFh

Configuration Word 2 mask<sup>(3)</sup> 3E13h

Checksum = C000h + (3FFFh and 3EFFh) + (3FFFh and 3E13h)

= C000h + 3EFFh + 3E13h

= 3D12h

**Note 1:** Sum of memory addresses = (Total number of program memory address locations) x (3FFFh) = C000h, truncated to 16 bits.

2: Configuration Word 1 and 2 = all bits are '1'; thus, code-protect is disabled.

3: Configuration Word 1 and 2 Mask = all bits are set to '1', except for unimplemented bits that are '0'.

# EXAMPLE 7-2: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION DISABLED PIC16LF1527, 00AAh AT FIRST AND LAST ADDRESS

PIC16LF1527 Sum of Memory addresses 0000h-3FFFh<sup>(1)</sup>

Configuration Word 1<sup>(2)</sup>

Configuration Word 1 mask<sup>(3)</sup>

Configuration Word 2<sup>(2)</sup>

Configuration Word 2 mask<sup>(4)</sup>

3E93h

Checksum = 4156h + (3FFFh and 3EFFh) + (3FFFh and 3E03h)

= 4156h + 3EFFh + 3E03h

= BE58h

**Note 1:** Total number of Program memory address locations: 3FFFh + 1 = 4000h. Then, 4000h - 2 = 3FFEh. Thus, [(3FFEh x 3FFFh) + (2 x 00AAh)] = 4156h, truncated to 16 bits.

- 2: Configuration Word 1 and 2 = all bits are '1'; thus, code-protect is disabled.

- **3:** Configuration Word 1 Mask = all Configuration Word bits are set to '1', except for unimplemented bits that are '0'.

- **4:** On the PIC16LF1527 device, the VCAPEN bit is not implemented in Configuration Word 2; Thus, all unimplemented bits are '0'.

# 7.3.2 PROGRAM CODE PROTECTION ENABLED

With the program code protection enabled, the checksum is computed in the following manner: The Least Significant nibble of each user ID is used to create a 16-bit value. The masked value of user ID location 8000h is the Most Significant nibble. This sum of user IDs is summed with the Configuration Words (all unimplemented Configuration bits are masked to '0').

EXAMPLE 7-3: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION ENABLED PIC16F1527, BLANK DEVICE

| PIC16F1527 | Configuration Word             | 1 <sup>(2)</sup> 3F7Fh                                    |

|------------|--------------------------------|-----------------------------------------------------------|

|            | Configuration Word             | 1 mask <sup>(3)</sup> 3EFFh                               |

|            | Configuration Word             | 2 <sup>(2)</sup> 3FFFh                                    |

|            | Configuration Word 2           | 2 mask <sup>(3)</sup> 3E13h                               |

|            | User ID (8000h) <sup>(1)</sup> | 0006h                                                     |

|            | User ID (8001h) <sup>(1)</sup> | 0007h                                                     |

|            | User ID (8002h) <sup>(1)</sup> | 0001h                                                     |

|            | User ID (8003h) <sup>(1)</sup> | 0002h                                                     |

|            | Sum of User IDs(4)             | = (0006h and 000Fh) << 12 + (0007h and 000Fh) << 8 +      |

|            |                                | (0001h and 000Fh) << 4 + (0002h and 000Fh)                |

|            |                                | = 6000h + 0700h + 0010h + 0002h                           |

|            |                                | = 6712h                                                   |

|            | Checksum                       | = (3F7Fh and 3EFFh) + (3FFFh and 3E13h) + Sum of User IDs |

|            |                                | = 3E7Fh +3713h + 6712h                                    |

|            |                                | = DCA4h                                                   |

|            |                                |                                                           |

- Note 1: User ID values in this example are random values.

- 2: Configuration Word 1 and 2 = all bits are '1' except the code-protect enable bit.

- **3:** Configuration Word 1 and 2 Mask = all Configuration Word bits are set to '1', except for unimplemented bits which read '0'.

- 4: << = shift left, thus the LSb of the first user ID value is the MSb of the sum of user IDs and so on, until the LSb of the last user ID value becomes the LSb of the sum of user IDs.

#### **EXAMPLE 7-4:** CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION ENABLED PIC16LF1527, 00AAh AT FIRST AND LAST ADDRESS

| PIC16LF1527  | Configuration Word             | 1 <sup>(2)</sup>           | 3F7Fh                           |

|--------------|--------------------------------|----------------------------|---------------------------------|

|              | Configuration Word             | 1 mask <sup>(3)</sup>      | 3EFFh                           |

|              | Configuration Word             | 2 <sup>(2)</sup>           | 3FFFh                           |

|              | Configuration Word             | 2 mask <sup>(3), (5)</sup> | 3E03h                           |

|              | User ID (8000h) <sup>(1)</sup> |                            | 000Eh                           |

|              | User ID (8001h) <sup>(1)</sup> |                            | 0008h                           |

|              | User ID (8002h) <sup>(1)</sup> |                            | 0005h                           |

|              | User ID (8003h) <sup>(1)</sup> |                            | 0008h                           |

|              | Sum of User IDs(4)             | = (000Eh and 000Fh) << 12  | + (0008h and 000Fh) << 8 +      |

|              |                                | (0005h and 000Fh) << 4 +   | · (0008h and 000Fh)             |

|              |                                | = E000h + 0800h + 0050h +  | 0008h                           |

|              |                                | = E858h                    |                                 |

|              | Checksum                       | = (3F7Fh and 3EFFh) + (3FF | Fh and 3E03h) + Sum of User IDs |

|              |                                | = 3E7Fh +3E03h + E858h     |                                 |

|              |                                | = 64DAh                    |                                 |

| Note 1: User | ID values in this exam         | ole are random values.     |                                 |

- User ID values in this example are random values.

- 2: Configuration Word 1 and 2 = all bits are '1' except the code-protect enable bit.

- 3: Configuration Word 1 and 2 Mask = all Configuration Word bits are set to '1', except for unimplemented bits which read '0'.

- 4: << = shift left, thus the LSb of the first user ID value is the MSb of the sum of user IDs and so on, until the LSb of the last user ID value becomes the LSb of the sum of user IDs.

- 5: On the PIC16LF1527 device, the VCAPEN bit is not implemented in Configuration Word 2; thus, all unimplemented bits are '0'.

### 8.0 ELECTRICAL SPECIFICATIONS

Refer to device specific data sheet for absolute maximum ratings.

TABLE 8-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY MODE

| AC/DC C    | HARACTERISTICS                                                             |                               | Standard (<br>Production |                               | Conditions<br>25°C                               | 1                                                                          |                     |

|------------|----------------------------------------------------------------------------|-------------------------------|--------------------------|-------------------------------|--------------------------------------------------|----------------------------------------------------------------------------|---------------------|

| Sym.       | Characteristics                                                            |                               | Min.                     | Тур.                          | Max.                                             | Units                                                                      | Conditions/Comments |

|            |                                                                            | Supply Volt                   | ages and C               | urrents                       |                                                  |                                                                            |                     |

| VDD        | Supply Voltage                                                             | PIC16F151X<br>PIC16F152X      | 2.3                      | -                             | 5.5                                              | ٧                                                                          |                     |

|            | (VDDMIN, VDDMAX)                                                           | PIC16LF151X<br>PIC16LF152X    | 1.8                      | _                             | 3.6                                              | V                                                                          |                     |

| VPEW       | Read/Write and Row Erase opera                                             | tions                         | VDDMIN                   |                               | VDDMAX                                           | V                                                                          |                     |

| VPBE       | Bulk Erase operations                                                      |                               | 2.7                      | _                             | VDDMAX                                           | V                                                                          |                     |

| Iddi       | Current on VDD, Idle                                                       |                               | _                        | _                             | 1.0                                              | mA                                                                         |                     |

| IDDP       | Current on VDD, Programming                                                |                               | _                        | _                             | 3.0                                              | mA                                                                         |                     |

|            | VPP                                                                        |                               |                          |                               |                                                  |                                                                            |                     |

| IPP        | Current on MCLR/VPP                                                        |                               | _                        | _                             | 600                                              | μА                                                                         |                     |

| VIHH       | High voltage on MCLR/VPP for Program/Verify mode entry                     |                               | 8.0                      | _                             | 9.0                                              | V                                                                          |                     |

| TVHHR      | MCLR rise time (VIL to VIHH) for Program/Verify mode entry                 | _                             | _                        | 1.0                           | μS                                               |                                                                            |                     |

|            | I/O pins                                                                   |                               |                          |                               |                                                  |                                                                            |                     |

| VIH        | (ICSPCLK, ICSPDAT, MCLR/VPP level                                          | 0.8 VDD                       | _                        | _                             | V                                                |                                                                            |                     |

| VIL        | (ICSPCLK, ICSPDAT, MCLR/VPP                                                | _                             | _                        | 0.2 VDD                       | V                                                |                                                                            |                     |

| Vон        | ICSPDAT output high level                                                  | VDD-0.7<br>VDD-0.7<br>VDD-0.7 | _                        | _                             | V                                                | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 2 mA, VDD = 1.8V |                     |

| Vol        | ICSPDAT output low level                                                   | _                             | _                        | Vss+0.6<br>Vss+0.6<br>Vss+0.6 | V                                                | IOH = 8 mA, VDD = 5V<br>IOH = 6 mA, VDD = 3.3V<br>IOH = 3 mA, VDD = 1.8V   |                     |

|            |                                                                            | Programming                   | Mode Entry               | and Exi                       | t                                                |                                                                            | L                   |

| TENTS      | Programing mode entry setup tim ICSPDAT setup time before VDD              |                               | 100                      | _                             | _                                                | ns                                                                         |                     |

| TENTH      | Programing mode entry hold time ICSPDAT hold time after VDD or N           | //CLR↑                        | 250                      |                               | _                                                | μS                                                                         |                     |

|            |                                                                            | Serial F                      | Program/Vei              | rify                          |                                                  |                                                                            |                     |

| TCKL       | Clock Low Pulse Width                                                      |                               | 100                      | _                             | <u> </u>                                         | ns                                                                         |                     |

| ТСКН       | Clock High Pulse Width                                                     |                               | 100                      | _                             | <del>  -</del>                                   | ns                                                                         |                     |

| TDS<br>TDH | Data in setup time before clock↓  Data in hold time after clock↓           |                               | 100<br>100               |                               | <del>  -</del>                                   | ns                                                                         |                     |

| I DH       | Clock↑ to data out valid (during a                                         |                               |                          |                               | <del>                                     </del> | ns                                                                         |                     |

| Tco        | Read Data command)                                                         |                               | 0                        | _                             | 80                                               | ns                                                                         |                     |

| TLZD       | Clock↓ to data low-impedance (during a Read Data command)                  |                               | 0                        | _                             | 80                                               | ns                                                                         |                     |

| THZD       | Clock↓ to data high-impedance (o<br>Read Data command)                     | -                             | 0                        | _                             | 80                                               | ns                                                                         |                     |

| TDLY       | Data input not driven to next clock required between command/data command) |                               | 1.0                      | _                             |                                                  | μS                                                                         |                     |

| TERAB      | Bulk Erase cycle time                                                      |                               | _                        |                               | 5                                                | ms                                                                         |                     |

| TERAR      | Row Erase cycle time                                                       |                               | _                        | _                             | 2.5                                              | ms                                                                         |                     |

Note 1: Externally timed writes are not supported for Configuration and Calibration bits.

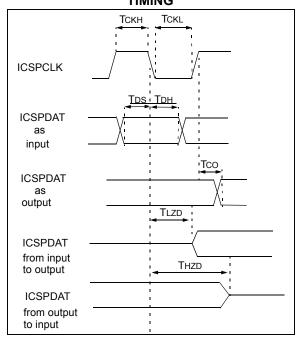

FIGURE 8-5: CLOCK AND DATA TIMING

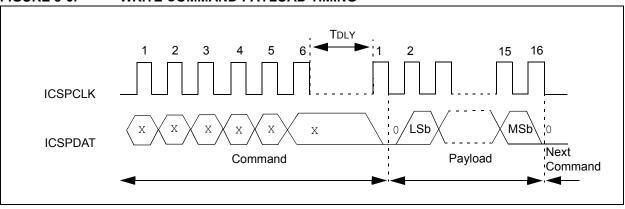

FIGURE 8-6: WRITE COMMAND-PAYLOAD TIMING

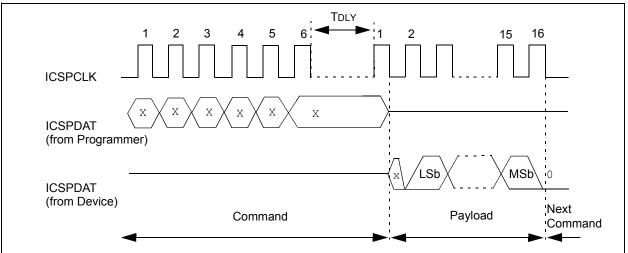

FIGURE 8-7: READ COMMAND-PAYLOAD TIMING

NOTES: