Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48 MIPS                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                          |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | ОТР                                                             |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t622-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 18.1. Endpoint Addressing                                                                                                                  | 116                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 18.2. USB Transceiver                                                                                                                      |                                                                                                                            |

| 18.3. USB Register Access                                                                                                                  |                                                                                                                            |

| 18.4. USB Clock Configuration                                                                                                              |                                                                                                                            |

| 18.5. FIFO Management                                                                                                                      |                                                                                                                            |

| 18.5.1. FIFO Split Mode                                                                                                                    |                                                                                                                            |

| 18.5.2. FIFO Double Buffering                                                                                                              |                                                                                                                            |

| 18.5.1. FIFO Access                                                                                                                        |                                                                                                                            |

| 18.6. Function Addressing                                                                                                                  |                                                                                                                            |

| 18.7. Function Configuration and Control                                                                                                   |                                                                                                                            |

| 18.8. Interrupts                                                                                                                           |                                                                                                                            |

| 18.9. The Serial Interface Engine                                                                                                          | 136                                                                                                                        |

| 18.10. Endpoint0                                                                                                                           |                                                                                                                            |

| 18.10.1. Endpoint0 SETUP Transactions                                                                                                      |                                                                                                                            |

| 18.10.2. Endpointo IN Transactions                                                                                                         |                                                                                                                            |

| 18.10.3. Endpoint0 OUT Transactions                                                                                                        |                                                                                                                            |

| 18.11. Configuring Endpoints1-2                                                                                                            |                                                                                                                            |

| 18.12. Controlling Endpoints1-2 IN                                                                                                         | 141                                                                                                                        |

| 18.12.1. Endpoints1-2 IN Interrupt or Bulk Mode                                                                                            |                                                                                                                            |

| 18.12.2. Endpoints1-2 IN Isochronous Mode                                                                                                  |                                                                                                                            |

| 18.13. Controlling Endpoints1-2 OUT.                                                                                                       |                                                                                                                            |

| 18.13.1. Endpoints1-2 OUT Interrupt or Bulk Mode                                                                                           |                                                                                                                            |

| 18.13.2. Endpoints1-2 OUT Isochronous Mode                                                                                                 |                                                                                                                            |

|                                                                                                                                            |                                                                                                                            |

|                                                                                                                                            |                                                                                                                            |

| 19. SMBus                                                                                                                                  | 149                                                                                                                        |

| 19. SMBus                                                                                                                                  | <b> 149</b><br>150                                                                                                         |

| 19. SMBus                                                                                                                                  | <b> 149</b><br>150<br>150                                                                                                  |

| <ul> <li><b>19. SMBus</b></li> <li>19.1. Supporting Documents</li> <li>19.2. SMBus Configuration</li> <li>19.3. SMBus Operation</li> </ul> | <b> 149</b><br>150<br>150<br>150                                                                                           |

| <ul> <li>19. SMBus.</li> <li>19.1. Supporting Documents</li></ul>                                                                          | <b> 149</b><br>150<br>150<br>150<br>151                                                                                    |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | <b>149</b><br>150<br>150<br>150<br>151<br>151                                                                              |

| <ul> <li>19. SMBus.</li> <li>19.1. Supporting Documents.</li> <li>19.2. SMBus Configuration.</li> <li>19.3. SMBus Operation</li></ul>      | <b>149</b><br>150<br>150<br>150<br>151<br>151<br>151                                                                       |

| <ul> <li>19. SMBus.</li> <li>19.1. Supporting Documents</li></ul>                                                                          | <b>149</b><br>150<br>150<br>150<br>151<br>151<br>151<br>151                                                                |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152                                                                |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152                                                                |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>152                                                  |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>152<br>152                                           |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>152<br>152<br>152<br>156<br>156                                           |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>152<br>156<br>156<br>156                             |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>152<br>152<br>152<br>156<br>156<br>156<br>158                             |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>156<br>156<br>158<br>158<br>161                      |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>156<br>156<br>156<br>158<br>161<br>162               |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>156<br>156<br>156<br>158<br>161<br>162<br>162        |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>156<br>156<br>158<br>158<br>161<br>162<br>162<br>163 |

| <ul> <li>19. SMBus</li></ul>                                                                                                               | 149<br>150<br>150<br>150<br>151<br>151<br>151<br>151<br>152<br>152<br>156<br>156<br>156<br>156<br>161<br>162<br>163<br>164 |

| SFR Definition 22.4. SPI0DAT: SPI0 Data                                | . 198 |

|------------------------------------------------------------------------|-------|

| SFR Definition 23.1. CKCON: Clock Control                              | . 203 |

| SFR Definition 23.2. TCON: Timer Control                               |       |

| SFR Definition 23.3. TMOD: Timer Mode                                  | . 209 |

| SFR Definition 23.4. TL0: Timer 0 Low Byte                             | . 210 |

| SFR Definition 23.5. TL1: Timer 1 Low Byte                             |       |

| SFR Definition 23.6. TH0: Timer 0 High Byte                            | . 211 |

| SFR Definition 23.7. TH1: Timer 1 High Byte                            |       |

| SFR Definition 23.8. TMR2CN: Timer 2 Control                           |       |

| SFR Definition 23.9. TMR2RLL: Timer 2 Reload Register Low Byte         |       |

| SFR Definition 23.10. TMR2RLH: Timer 2 Reload Register High Byte       |       |

| SFR Definition 23.11. TMR2L: Timer 2 Low Byte                          |       |

| SFR Definition 23.12. TMR2H Timer 2 High Byte                          | . 217 |

| SFR Definition 23.13. TMR3CN: Timer 3 Control                          |       |

| SFR Definition 23.14. TMR3RLL: Timer 3 Reload Register Low Byte        |       |

| SFR Definition 23.15. TMR3RLH: Timer 3 Reload Register High Byte       |       |

| SFR Definition 23.16. TMR3L: Timer 3 Low Byte                          |       |

| SFR Definition 23.17. TMR3H Timer 3 High Byte                          |       |

| SFR Definition 24.1. PCA0CN: PCA Control                               |       |

| SFR Definition 24.2. PCA0MD: PCA Mode                                  |       |

| SFR Definition 24.3. PCA0PWM: PCA PWM Configuration                    |       |

| SFR Definition 24.4. PCA0CPMn: PCA Capture/Compare Mode                |       |

| SFR Definition 24.5. PCA0L: PCA Counter/Timer Low Byte                 |       |

| SFR Definition 24.6. PCA0H: PCA Counter/Timer High Byte                |       |

| SFR Definition 24.7. PCA0CPLn: PCA Capture Module Low Byte             |       |

| SFR Definition 24.8. PCA0CPHn: PCA Capture Module High Byte            |       |

| C2 Register Definition 25.1. C2ADD: C2 Address                         | . 244 |

| C2 Register Definition 25.2. DEVICEID: C2 Device ID                    |       |

| C2 Register Definition 25.3. REVID: C2 Revision ID                     |       |

| C2 Register Definition 25.4. DEVCTL: C2 Device Control                 |       |

| C2 Register Definition 25.5. EPCTL: EPROM Programming Control Register |       |

| C2 Register Definition 25.6. EPDAT: C2 EPROM Data                      |       |

| C2 Register Definition 25.7. EPSTAT: C2 EPROM Status                   |       |

| C2 Register Definition 25.8. EPADDRH: C2 EPROM Address High Byte       |       |

| C2 Register Definition 25.9. EPADDRL: C2 EPROM Address Low Byte        |       |

| C2 Register Definition 25.10. CRC0: CRC Byte 0                         |       |

| C2 Register Definition 25.11. CRC1: CRC Byte 1                         |       |

| C2 Register Definition 25.12. CRC2: CRC Byte 2                         |       |

| C2 Register Definition 25.13. CRC3: CRC Byte 3                         | . 251 |

|                                                                        |       |

## SFR Definition 8.3. SP: Stack Pointer

| Bit          | 7           | 6                         | 5 | 4 | 3        | 2 | 1 | 0 |  |  |

|--------------|-------------|---------------------------|---|---|----------|---|---|---|--|--|

| Name SP[7:0] |             |                           |   |   |          |   |   |   |  |  |

| Туре         |             | R/W                       |   |   |          |   |   |   |  |  |

| Reset        | 0           | 0                         | 0 | 0 | 0        | 1 | 1 | 1 |  |  |

| SFR Ac       | dress = 0x8 | 1                         |   |   |          |   |   |   |  |  |

| Bit          | Name        |                           |   |   | Function |   |   |   |  |  |

| 7.0          | 0.01-01     | <b>0</b> , 1 <b>D</b> ; ( |   |   |          |   |   |   |  |  |

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

## SFR Definition 8.4. ACC: Accumulator

| Bit   | 7                 | 6               | 5          | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------------|-----------------|------------|---|---|---|---|---|--|

| Name  | ACC[7:0]          |                 |            |   |   |   |   |   |  |

| Туре  | R/W               |                 |            |   |   |   |   |   |  |

| Reset | 0                 | 0 0 0 0 0 0 0 0 |            |   |   |   |   |   |  |

|       | U<br>Hress - NyFi | 0. Bit-Addres   | U<br>sable | 0 | 0 | 0 | 0 |   |  |

SFR Address = 0xE0; Bit-Addressable

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

## SFR Definition 8.5. B: B Register

| Bit   | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------|---|---|---|---|---|---|---|--|

| Name  | B[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W    |   |   |   |   |   |   |   |  |

| Reset | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xF0; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

## SFR Definition 14.1. PCON: Power Control

| -     |   |      | -    | -   |   |   |   |   |

|-------|---|------|------|-----|---|---|---|---|

| Bit   | 7 | 6    | 5    | 4   | 3 | 2 | 1 | 0 |

| Name  |   | STOP | IDLE |     |   |   |   |   |

| Туре  |   |      | R/W  | R/W |   |   |   |   |

| Reset | 0 | 0    | 0    | 0   | 0 | 0 | 0 | 0 |

SFR Address = 0x87

| Bit | Name    | Function                                                                                                                                                                                                                                                               |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.                                                                                                                                                                                                                                             |

|     |         | These are general purpose flags for use under software control.                                                                                                                                                                                                        |

| 1   | STOP    | <ul><li>Stop Mode Select.</li><li>Setting this bit will place the CIP-51 in stop mode. This bit will always be read as 0.</li><li>1: CPU goes into stop mode (internal oscillator stopped).</li></ul>                                                                  |

| 0   | IDLE    | IDLE: Idle Mode Select.<br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts,<br>Serial Ports, and Analog Peripherals are still active.) |

## 15.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 15.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset.

**Important Note:** If the V<sub>DD</sub> monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the V<sub>DD</sub> monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the V<sub>DD</sub> monitor and configuring it as a reset source from a disabled state is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- 2. If necessary, wait for the V<sub>DD</sub> monitor to stabilize (see Table 6.4 for the V<sub>DD</sub> Monitor turn-on time).

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 15.2 for V<sub>DD</sub> monitor timing; note that the power-on-reset delay is not incurred after a V<sub>DD</sub> monitor reset. See Table 6.4 for complete electrical characteristics of the V<sub>DD</sub> monitor.

82

## SFR Definition 15.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|---------|--------|--------|--------|--------|--------|--------|

| Name  | VDMEN  | VDDSTAT |        |        |        |        |        |        |

| Туре  | R/W    | R       | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies  | Varies | Varies | Varies | Varies | Varies | Varies |

SFR Address = 0xFF

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 15.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. See Table 6.4 for the minimum V <sub>DD</sub> Monitor turn-on time.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.<br>1: $V_{DD}$ is above the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5:0 | Unused  | Unused. Read = Varies; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 15.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 6.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 15.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the MCD time-out, a reset will be generated. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

### 15.5. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "24.4. Watchdog Timer Mode" on page 235; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

#### 16.6.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 16.1, "RC Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in  $k\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

#### Equation 16.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>) / RC = 1.23(10<sup>3</sup>) / [246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 16.6, the required XFCN setting is 010b.

#### 16.6.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 16.1, "C Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and V<sub>DD</sub> = the MCU power supply in Volts.

$$f = (KF)/(C \times V_{DD})$$

#### Equation 16.2. C Mode Oscillator Frequency

For example: Assume  $V_{DD} = 3.0$  V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 16.6 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

## SFR Definition 17.3. XBR2: Port I/O Crossbar Register 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|-------|---|---|---|---|---|---|---|-------|

| Name  |   |   |   |   |   |   |   | URT1E |

| Туре  | R | R | R | R | R | R | R | R/W   |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

SFR Address = 0xE3

| Bit | Name   | Function                                                                         |  |  |  |  |  |

|-----|--------|----------------------------------------------------------------------------------|--|--|--|--|--|

| 7:1 | Unused | Unused. Read = 0000000b; Write = Don't Care.                                     |  |  |  |  |  |

| 0   | URT1E  | UART1 I/O Output Enable Bit.                                                     |  |  |  |  |  |

|     |        | 0: UART1 I/O unavailable at Port pins.<br>1: UART1 TX1, RX1 routed to Port pins. |  |  |  |  |  |

## 17.5. Port Match

Port match functionality allows system events to be triggered by a logic value change on P0 or P1. A software controlled value stored in the PnMATCH registers specifies the expected or normal logic values of P0 and P1. A Port mismatch event occurs if the logic levels of the Port's input pins no longer match the software controlled value. This allows Software to be notified if a certain change or pattern occurs on P0 or P1 input pins regardless of the XBRn settings.

The PnMASK registers can be used to individually select which P0 and P1 pins should be compared against the PnMATCH registers. A Port mismatch event is generated if (P0 & P0MASK) does not equal (P0MATCH & P0MASK) or if (P1 & P1MASK) does not equal (P1MATCH & P1MASK).

A Port mismatch event may be used to generate an interrupt or wake the device from a low power mode, such as IDLE or SUSPEND. See the Interrupts and Power Options chapters for more details on interrupt and wake-up sources.

Suspend Interrupt Service Routine (ISR) should perform application-specific configuration tasks such as disabling appropriate peripherals and/or configuring clock sources for low power modes. See Section "16.3. Programmable Internal High-Frequency (H-F) Oscillator" on page 89 for more details on internal oscillator configuration, including the Suspend mode feature of the internal oscillator.

USB0 exits Suspend mode when any of the following occur: (1) Resume signaling is detected or generated, (2) Reset signaling is detected, or (3) a device or USB reset occurs. If suspended, the internal oscillator will exit Suspend mode upon any of the above listed events.

**Resume Signaling:** USB0 will exit Suspend mode if Resume signaling is detected on the bus. A Resume interrupt will be generated upon detection if enabled (RESINTE = 1). Software may force a Remote Wakeup by writing 1 to the RESUME bit (POWER.2). When forcing a Remote Wakeup, software should write RESUME = 0 to end Resume signaling 10-15 ms after the Remote Wakeup is initiated (RESUME = 1).

**ISO Update:** When software writes 1 to the ISOUP bit (POWER.7), the ISO Update function is enabled. With ISO Update enabled, new packets written to an ISO IN endpoint will not be transmitted until a new Start-Of-Frame (SOF) is received. If the ISO IN endpoint receives an IN token before a SOF, USB0 will transmit a zero-length packet. When ISOUP = 1, ISO Update is enabled for all ISO endpoints.

**USB Enable:** USB0 is disabled following a Power-On-Reset (POR). USB0 is enabled by clearing the USBINH bit (POWER.4). Once written to 0, the USBINH can only be set to 1 by one of the following: (1) a Power-On-Reset (POR), or (2) an asynchronous USB0 reset generated by writing 1 to the USBRST bit (POWER.3).

Software should perform all USB0 configuration before enabling USB0. The configuration sequence should be performed as follows:

- 1. Select and enable the USB clock source.

- 2. Reset USB0 by writing USBRST= 1.

- 3. Configure and enable the USB Transceiver.

- 4. Perform any USB0 function configuration (interrupts, Suspend detect).

- 5. Enable USB0 by writing USBINH = 0.

### USB Register Definition 18.9. FRAMEL: USB0 Frame Number Low

| Bit   | 7              | 6                           | 5            | 4              | 3            | 2          | 1    | 0 |  |  |  |

|-------|----------------|-----------------------------|--------------|----------------|--------------|------------|------|---|--|--|--|

| Nam   | е              | FRMEL[7:0]                  |              |                |              |            |      |   |  |  |  |

| Туре  | 9              |                             |              | F              | 2            |            |      |   |  |  |  |

| Rese  | et 0           | 0                           | 0            | 0              | 0            | 0          | 0    | 0 |  |  |  |

| USB F | Register Addro | ess = 0x0C                  |              |                |              |            |      |   |  |  |  |

| Bit   | Name           | ne Function                 |              |                |              |            |      |   |  |  |  |

| 7:0   | FRMEL[7:0]     | 7:0] Frame Number Low Bits. |              |                |              |            |      |   |  |  |  |

|       |                | This register               | contains bit | s 7-0 of the l | ast received | frame numb | oer. |   |  |  |  |

## USB Register Definition 18.10. FRAMEH: USB0 Frame Number High

| Bit   | 7 | 6 | 5 | 4 | 3 | 2          | 1 | 0 |  |

|-------|---|---|---|---|---|------------|---|---|--|

| Name  |   |   |   |   |   | FRMEH[2:0] |   |   |  |

| Туре  | R | R | R | R | R | R          |   |   |  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 0 0      |   |   |  |

USB Register Address = 0x0D

| Bit | Name       | Function                                                            |

|-----|------------|---------------------------------------------------------------------|

| 7:3 | Unused     | Unused. Read = 00000b. Write = don't care.                          |

| 2:0 | FRMEH[2:0] | Frame Number High Bits.                                             |

|     |            | This register contains bits 10-8 of the last received frame number. |

#### 18.8. Interrupts

The read-only USB0 interrupt flags are located in the USB registers shown in USB Register Definition 18.11 through USB Register Definition 18.13. The associated interrupt enable bits are located in the USB registers shown in USB Register Definition 18.14 through USB Register Definition 18.16. A USB0 interrupt is generated when any of the USB interrupt flags is set to 1. The USB0 interrupt is enabled via the EIE1 SFR (see Section "12. Interrupts" on page 60).

Important Note: Reading a USB interrupt flag register resets all flags in that register to 0.

5. Hardware sets the SUEND bit (E0CSR.4) because a control transfer ended before firmware sets the DATAEND bit (E0CSR.3).

The E0CNT register (USB Register Definition 18.11) holds the number of received data bytes in the Endpoint0 FIFO.

Hardware will automatically detect protocol errors and send a STALL condition in response. Firmware may force a STALL condition to abort the current transfer. When a STALL condition is generated, the STSTL bit will be set to 1 and an interrupt generated. The following conditions will cause hardware to generate a STALL condition:

- 1. The host sends an OUT token during a OUT data phase after the DATAEND bit has been set to 1.

- 2. The host sends an IN token during an IN data phase after the DATAEND bit has been set to 1.

- 3. The host sends a packet that exceeds the maximum packet size for Endpoint0.

- 4. The host sends a non-zero length DATA1 packet during the status phase of an IN transaction.

Firmware sets the SDSTL bit (E0CSR.5) to 1.

#### 18.10.1. Endpoint0 SETUP Transactions

All control transfers must begin with a SETUP packet. SETUP packets are similar to OUT packets, containing an 8-byte data field sent by the host. Any SETUP packet containing a command field of anything other than 8 bytes will be automatically rejected by USB0. An Endpoint0 interrupt is generated when the data from a SETUP packet is loaded into the Endpoint0 FIFO. Software should unload the command from the Endpoint0 FIFO, decode the command, perform any necessary tasks, and set the SOPRDY bit to indicate that it has serviced the OUT packet.

#### 18.10.2. Endpoint0 IN Transactions

When a SETUP request is received that requires USB0 to transmit data to the host, one or more IN requests will be sent by the host. For the first IN transaction, firmware should load an IN packet into the Endpoint0 FIFO, and set the INPRDY bit (E0CSR.1). An interrupt will be generated when an IN packet is transmitted successfully. Note that no interrupt will be generated if an IN request is received before firmware has loaded a packet into the Endpoint0 FIFO. If the requested data exceeds the maximum packet size for Endpoint0 (as reported to the host), the data should be split into multiple packets; each packet should be of the maximum packet size excluding the last (residual) packet. If the requested data is an integer multiple of the maximum packet size for Endpoint0, the last data packet should be a zero-length packet signaling the end of the transfer. Firmware should set the DATAEND bit to 1 after loading into the Endpoint0 FIFO the last data packet for a transfer.

Upon reception of the first IN token for a particular control transfer, Endpoint0 is said to be in Transmit Mode. In this mode, only IN tokens should be sent by the host to Endpoint0. The SUEND bit (E0CSR.4) is set to 1 if a SETUP or OUT token is received while Endpoint0 is in Transmit Mode.

Endpoint0 will remain in Transmit Mode until any of the following occur:

- 1. USB0 receives an Endpoint0 SETUP or OUT token.

- 2. Firmware sends a packet less than the maximum Endpoint0 packet size.

- 3. Firmware sends a zero-length packet.

Firmware should set the DATAEND bit (E0CSR.3) to 1 when performing (2) and (3) above.

The SIE will transmit a NAK in response to an IN token if there is no packet ready in the IN FIFO (INPRDY = 0).

#### 19.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 19.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 19.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

#### 19.4.2.1. Software ACK Generation

When the EHACK bit in register SMB0ADM is cleared to 0, the firmware on the device must detect incoming slave addresses and ACK or NACK the slave address and incoming data bytes. As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

#### 19.4.2.2. Hardware ACK Generation

When the EHACK bit in register SMB0ADM is set to 1, automatic slave address recognition and ACK generation is enabled. More detail about automatic slave address recognition can be found in Section 19.4.3. As a receiver, the value currently specified by the ACK bit will be automatically sent on the bus during the ACK cycle of an incoming data byte. As a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. The ACKRQ bit is not used when hardware ACK generation is enabled. If a received slave address is NACKed by hardware, further slave events will be ignored until the next START is detected, and no interrupt will be generated.

Table 19.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 19.5 for SMBus status decoding using the SMB0CN register.

#### 19.5.3. Write Sequence (Slave)

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

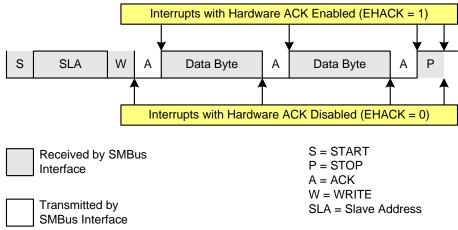

The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 19.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 19.7. Typical Slave Write Sequence

# Table 19.6. SMBus Status Decoding With Hardware ACK Generation Enabled (EHACK = 1)(Continued)

|                            | Va     | lue    | es F                | Rea                                  | d                                      |                                                                                       |                                                 |      | lues<br>Vrit                                 |     | itus<br>ected                  |   |      |

|----------------------------|--------|--------|---------------------|--------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------|------|----------------------------------------------|-----|--------------------------------|---|------|

| Mode                       | Status | Vector | ACKRQ               | ARBLOST                              | ACK                                    | Current SMbus State                                                                   | Typical Response Options                        | STA  | STO                                          | ACK | Next Status<br>Vector Expected |   |      |

|                            |        |        | 0                   | 0                                    | х                                      | A slave address + R/W was                                                             | If Write, Set ACK for first data byte.          | 0    | 0                                            | 1   | 0000                           |   |      |

|                            |        | ~      | received; ACK sent. | If Read, Load SMB0DAT with data byte | 0                                      | 0                                                                                     | Х                                               | 0100 |                                              |     |                                |   |      |

|                            | 0010   |        |                     | Lost arbitration as master;          | If Write, Set ACK for first data byte. | 0                                                                                     | 0                                               | 1    | 0000                                         |     |                                |   |      |

| iver                       |        |        | 0                   | 1                                    | Х                                      | slave address + R/W received;<br>ACK sent.                                            | If Read, Load SMB0DAT with data byte            | 0    | 0                                            | Х   | 0100                           |   |      |

| ece                        |        |        |                     |                                      |                                        |                                                                                       | Reschedule failed transfer                      | 1    | 0                                            | Х   | 1110                           |   |      |

| Slave Receiver             | 000    | 1      | 0                   | 0                                    | х                                      | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver. | Clear STO.                                      | 0    | 0                                            | Х   | _                              |   |      |

|                            |        |        | 0                   | 1                                    | Х                                      | Lost arbitration while attempt-<br>ing a STOP.                                        | No action required (transfer complete/aborted). | 0    | 0                                            | 0   | _                              |   |      |

|                            | 000    | 0      |                     |                                      | 0                                      | 0                                                                                     | V                                               |      | Set ACK for next data byte;<br>Read SMB0DAT. | 0   | 0                              | 1 | 0000 |

|                            | 000    | 00000  |                     | 0                                    | ^                                      | A slave byte was received.                                                            | Set NACK for next data byte;<br>Read SMB0DAT.   | 0    | 0                                            | 0   | 0000                           |   |      |

| n                          | 001    | 0      | 0                   | 1                                    | х                                      | Lost arbitration while attempt-                                                       | Abort failed transfer.                          | 0    | 0                                            | Х   | —                              |   |      |

| ditio                      | 001    | Ŭ      | Ũ                   | •                                    | ~                                      | ing a repeated START.                                                                 | Reschedule failed transfer.                     | 1    | 0                                            | Х   | 1110                           |   |      |

| Con                        | 000    | 1      | 0                   | 1                                    | х                                      | Lost arbitration due to a                                                             | Abort failed transfer.                          | 0    | 0                                            | Х   | —                              |   |      |

| rror                       |        | 1      | U                   |                                      | ~                                      | detected STOP.                                                                        | Reschedule failed transfer.                     | 1    | 0                                            | Х   | 1110                           |   |      |

| <b>Bus Error Condition</b> | 000    | 0      | 0                   | 1                                    | х                                      | Lost arbitration while transmit-                                                      | Abort failed transfer.                          | 0    | 0                                            | Х   | —                              |   |      |

| â                          | ā      |        | J                   | '                                    | ~                                      | ting a data byte as master.                                                           | Reschedule failed transfer.                     | 1    | 0                                            | Х   | 1110                           |   |      |

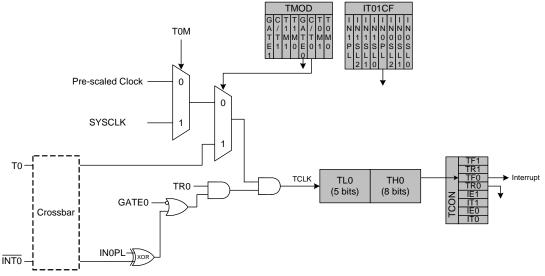

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT1 is used with Timer 1; the INT1 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 12.7).

Figure 23.1. T0 Mode 0 Block Diagram

#### 23.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 23.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 in the TCON register is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "12.3. INT0 and INT1 External Interrupt Sources" on page 69 for details on the external input signals INT0 and INT1).

## SFR Definition 23.9. TMR2RLL: Timer 2 Reload Register Low Byte

| Bit   | 7                  | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------------|-----|---|---|---|---|---|---|

| Name  | TMR2RLL[7:0]       |     |   |   |   |   |   |   |

| Туре  |                    | R/W |   |   |   |   |   |   |

| Reset | 0                  | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR A | SFR Address = 0xCA |     |   |   |   |   |   |   |

| Bit   | Name Function      |     |   |   |   |   |   |   |

| Dit | Name         | i uncuon                                                    |

|-----|--------------|-------------------------------------------------------------|

| 7:0 | TMR2RLL[7:0] | Timer 2 Reload Register Low Byte.                           |

|     |              | TMR2RLL holds the low byte of the reload value for Timer 2. |

## SFR Definition 23.10. TMR2RLH: Timer 2 Reload Register High Byte

| Bit   | 7              | 6                                                            | 5                                  | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|----------------|--------------------------------------------------------------|------------------------------------|----|---|---|---|---|--|--|--|

| Nam   | e              | TMR2RLH[7:0]                                                 |                                    |    |   |   |   |   |  |  |  |

| Туре  | 9              |                                                              |                                    | R/ | W |   |   |   |  |  |  |

| Rese  | et 0           | 0                                                            | 0                                  | 0  | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0xCE | 3                                                            |                                    |    |   |   |   |   |  |  |  |

| Bit   | Name           | Name Function                                                |                                    |    |   |   |   |   |  |  |  |

| 7:0   | TMR2RLH[7:0    | ] Timer 2 F                                                  | Timer 2 Reload Register High Byte. |    |   |   |   |   |  |  |  |

|       |                | TMR2RLH holds the high byte of the reload value for Timer 2. |                                    |    |   |   |   |   |  |  |  |

## SFR Definition 23.11. TMR2L: Timer 2 Low Byte

| Bit   | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------------|---|---|---|---|---|---|---|--|

| Name  | TMR2L[7:0]        |   |   |   |   |   |   |   |  |

| Туре  | R/W               |   |   |   |   |   |   |   |  |

| Reset | : 0 0 0 0 0 0 0 0 |   |   |   |   |   | 0 |   |  |

#### SFR Address = 0xCC

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

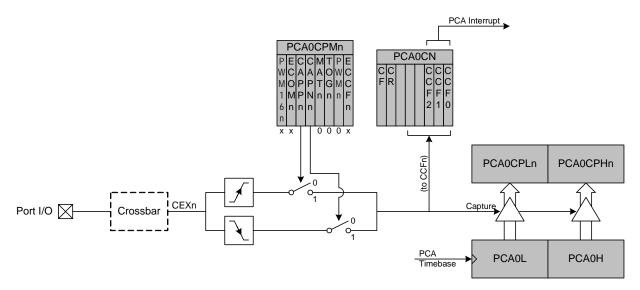

Figure 24.4. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

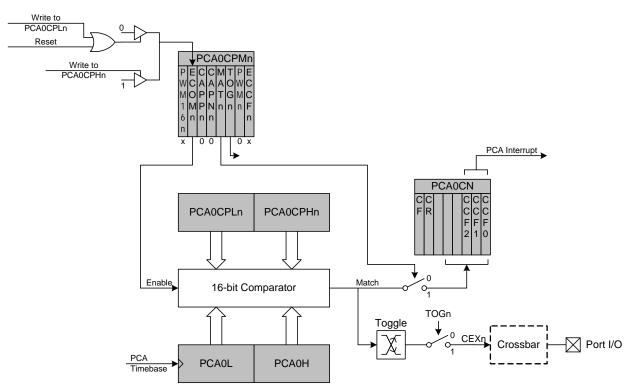

#### 24.3.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 24.6. PCA High-Speed Output Mode Diagram

#### 24.3.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 24.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

Note: A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

### Equation 24.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register. Note that the MATn bit should normally be set to 0 in this mode. If the MATn bit is set to 1, the CCFn flag for the channel will be set when the 16-bit PCA0 counter and the 16-bit capture/compare register for the channel are equal.

A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

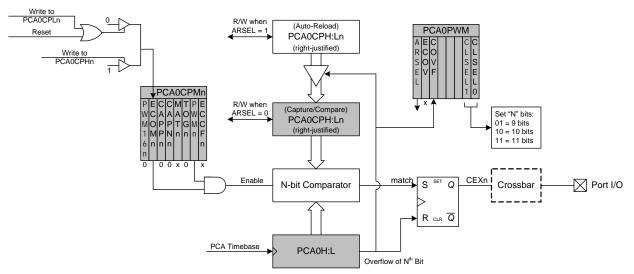

Figure 24.9. PCA 9, 10 and 11-Bit PWM Mode Diagram

#### 24.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8/9/10/11-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 24.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

$$Duty Cycle = \frac{(65536 - PCA0CPn)}{65536}$$

#### Equation 24.4. 16-Bit PWM Duty Cycle

Using Equation 24.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

## 25. C2 Interface

C8051T622/3 and C8051T326/7 devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow EPROM programming and in-system debugging with the production part installed in the end application. The C2 interface operates using only two pins: a bi-directional data signal (C2D), and a clock input (C2CK). See the C2 Interface Specification for details on the C2 protocol.

### 25.1. C2 Interface Registers

The following describes the C2 registers necessary to perform EPROM programming functions through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

## C2 Register Definition 25.1. C2ADD: C2 Address

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | C2ADD[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |