Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk20dn512vll10     |

|----------------------------|----------------------------------------------------------------------------|

| Supplier Device Package    | 100-LQFP (14x14)                                                           |

| Package / Case             | 100-LQFP                                                                   |

| Mounting Type              | Surface Mount                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Oscillator Type            | Internal                                                                   |

| Data Converters            | A/D 33x16b; D/A 1x12b                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| RAM Size                   | 128K x 8                                                                   |

| EEPROM Size                | -                                                                          |

| Program Memory Type        | FLASH                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Number of I/O              | 66                                                                         |

| Peripherals                | DMA, I²S, LVD, POR, PWM, WDT                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Speed                      | 100MHz                                                                     |

| Core Size                  | 32-Bit Single-Core                                                         |

| Core Processor             | ARM® Cortex®-M4                                                            |

| Product Status             | Active                                                                     |

| Details                    |                                                                            |

# 1 Ordering parts

## 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to freescale.com and perform a part number search for the following device numbers: PK20 and MK20.

### 2 Part identification

## 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

## 2.2 Format

Part numbers for this device have the following format:

Q K## A M FFF R T PP CC N

## 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description          | Values                                                                                     |

|-------|----------------------|--------------------------------------------------------------------------------------------|

| Q     | Qualification status | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul> |

| K##   | Kinetis family       | • K20                                                                                      |

| А     | Key attribute        | <ul> <li>D = Cortex-M4 w/ DSP</li> <li>F = Cortex-M4 w/ DSP and FPU</li> </ul>             |

| М     | Flash memory type    | <ul> <li>N = Program flash only</li> <li>X = Program flash and FlexMemory</li> </ul>       |

## **3.1.1 Example**

This is an example of an operating requirement:

| Symbol   | Description               | Min. | Max. | Unit |

|----------|---------------------------|------|------|------|

| $V_{DD}$ | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

# 3.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

## 3.2.1 Example

This is an example of an operating behavior:

| Symbol          | Description                                  | Min. | Max. | Unit |

|-----------------|----------------------------------------------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μΑ   |

## 3.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

## 3.3.1 Example

This is an example of an attribute:

| Symbol | Description                     | Min. | Max. | Unit |

|--------|---------------------------------|------|------|------|

| CIN_D  | Input capacitance: digital pins | _    | 7    | pF   |

# 4 Ratings

## 4.1 Thermal handling ratings

| Symbol           | Description                   | Min.        | Max. | Unit | Notes |

|------------------|-------------------------------|-------------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | <b>-</b> 55 | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _           | 260  | °C   | 2     |

- 1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

- Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 4.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    | _    | 1     |

<sup>1.</sup> Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 4.3 ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105°C      | -100  | +100  | mA   | 3     |

- 1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

- 2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

- 3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

# 4.4 Voltage and current operating ratings

# 5.2 Nonswitching electrical specifications

## 5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol                             | Description                                                                                             | Min.                   | Max.                 | Unit | Notes |

|------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------|----------------------|------|-------|

| $V_{DD}$                           | Supply voltage                                                                                          | 1.71                   | 3.6                  | V    |       |

| $V_{DDA}$                          | Analog supply voltage                                                                                   | 1.71                   | 3.6                  | V    |       |

| $V_{\rm DD} - V_{\rm DDA}$         | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                               | -0.1                   | 0.1                  | V    |       |

| V <sub>SS</sub> – V <sub>SSA</sub> | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                               | -0.1                   | 0.1                  | V    |       |

| V <sub>BAT</sub>                   | RTC battery supply voltage                                                                              | 1.71                   | 3.6                  | V    |       |

| V <sub>IH</sub>                    | Input high voltage                                                                                      |                        |                      |      |       |

|                                    | • 2.7 V ≤ V <sub>DD</sub> ≤ 3.6 V                                                                       | $0.7 \times V_{DD}$    | _                    | V    |       |

|                                    | • 1.7 V ≤ V <sub>DD</sub> ≤ 2.7 V                                                                       | $0.75 \times V_{DD}$   | _                    | V    |       |

| V <sub>IL</sub>                    | Input low voltage                                                                                       |                        |                      |      |       |

|                                    | • 2.7 V ≤ V <sub>DD</sub> ≤ 3.6 V                                                                       | _                      | $0.35 \times V_{DD}$ | V    |       |

|                                    | • 1.7 V ≤ V <sub>DD</sub> ≤ 2.7 V                                                                       | _                      | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>                   | Input hysteresis                                                                                        | 0.06 × V <sub>DD</sub> | _                    | V    |       |

| I <sub>ICDIO</sub>                 | Digital pin negative DC injection current — single pin                                                  | _                      |                      | _    | 1     |

|                                    | • V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                               | -5                     | _                    | mA   |       |

| I <sub>ICAIO</sub>                 | Analog <sup>2</sup> , EXTAL, and XTAL pin DC injection current — single pin                             |                        |                      |      | 3     |

|                                    |                                                                                                         | -5                     |                      | mA   |       |

|                                    | • V <sub>IN</sub> < V <sub>SS</sub> -0.3V (Negative current injection)                                  | -5                     | _                    |      |       |

|                                    | • V <sub>IN</sub> > V <sub>DD</sub> +0.3V (Positive current injection)                                  | _                      | +5                   |      |       |

| I <sub>ICcont</sub>                | Contiguous pin DC injection current —regional limit,                                                    |                        |                      |      |       |

|                                    | includes sum of negative injection currents or sum of positive injection currents of 16 contiguous pins |                        |                      |      |       |

|                                    | Negative current injection                                                                              | -25                    | _                    | mA   |       |

|                                    | Positive current injection                                                                              | _                      | +25                  |      |       |

|                                    | ·                                                                                                       |                        |                      |      |       |

| V <sub>ODPU</sub>                  | Open drain pullup voltage level                                                                         | $V_{DD}$               | $V_{DD}$             | V    | 4     |

| $V_{RAM}$                          | V <sub>DD</sub> voltage required to retain RAM                                                          | 1.2                    | _                    | V    |       |

| $V_{RFVBAT}$                       | V <sub>BAT</sub> voltage required to retain the VBAT register file                                      | $V_{POR\_VBAT}$        | _                    | V    |       |

- All 5 V tolerant digital I/O pins are internally clamped to V<sub>SS</sub> through an ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> is less than V<sub>DIO\_MIN</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>DIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICDIO</sub>I.

- 2. Analog pins are defined as pins that do not have an associated general purpose I/O port function. Additionally, EXTAL and XTAL are analog pins.

- 3. All analog pins are internally clamped to  $V_{SS}$  and  $V_{DD}$  through ESD protection diodes. If  $V_{IN}$  is less than  $V_{AIO\_MIN}$  or greater than  $V_{AIO\_MAX}$ , a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as  $R=(V_{AIO\_MIN}-V_{IN})/II_{ICAIO}I$ . The positive injection current limiting resistor is calculated as  $R=(V_{IN}-V_{AIO\_MAX})/II_{ICAIO}I$ . Select the larger of these two calculated resistances if the pin is exposed to positive and negative injection currents.

- 4. Open drain outputs must be pulled to VDD.

# Table 6. Power consumption operating behaviors (continued)

| Symbol                | Description                                                                | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------|------|------|------|------|-------|

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks enabled   | _    | 1.71 | _    | mA   | 7     |

| I <sub>DD_VLPW</sub>  | Very-low-power wait mode current at 3.0 V — all peripheral clocks disabled | _    | 0.77 | _    | mA   | 8     |

| I <sub>DD_STOP</sub>  | Stop mode current at 3.0 V                                                 |      |      |      |      |       |

|                       | • @ -40 to 25°C                                                            | _    | 0.74 | 1.41 | mA   |       |

|                       | • @ 70°C                                                                   | _    | 2.45 | 11.5 | mA   |       |

|                       | • @ 105°C                                                                  | _    | 6.61 | 30   | mA   |       |

| I <sub>DD_VLPS</sub>  | Very-low-power stop mode current at 3.0 V                                  |      |      |      |      |       |

|                       | • @ –40 to 25°C                                                            | _    | 83   | 435  | μΑ   |       |

|                       | • @ 70°C                                                                   | _    | 425  | 2000 | μA   |       |

|                       | • @ 105°C                                                                  | _    | 1280 | 4000 | μΑ   |       |

| I <sub>DD_LLS</sub>   | Low leakage stop mode current at 3.0 V                                     |      |      |      |      | 9     |

|                       | • @ -40 to 25°C                                                            | _    | 4.58 | 19.9 | μΑ   |       |

|                       | • @ 70°C                                                                   | _    | 30.6 | 105  | μΑ   |       |

|                       | • @ 105°C                                                                  | _    | 137  | 500  | μΑ   |       |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current at 3.0 V                              |      |      |      |      | 9     |

|                       | • @ -40 to 25°C                                                            | _    | 3.0  | 23   | μΑ   |       |

|                       | • @ 70°C                                                                   | _    | 18.6 | 43   | μΑ   |       |

|                       | • @ 105°C                                                                  | _    | 84.9 | 230  | μΑ   |       |

| I <sub>DD_VLLS2</sub> | Very low-leakage stop mode 2 current at 3.0 V                              |      |      |      |      |       |

|                       | • @ –40 to 25°C                                                            | _    | 2.2  | 5.4  | μA   |       |

|                       | • @ 70°C                                                                   | _    | 9.3  | 35   | μA   |       |

|                       | • @ 105°C                                                                  | _    | 41.4 | 128  | μΑ   |       |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current at 3.0 V                              |      |      |      |      |       |

|                       | • @ –40 to 25°C                                                            | _    | 2.1  | 9    | μΑ   |       |

|                       | • @ 70°C                                                                   | _    | 7.6  | 28   | μΑ   |       |

|                       | • @ 105°C                                                                  | _    | 33.5 | 95.5 | μΑ   |       |

| I <sub>DD_VBAT</sub>  | Average current with RTC and 32kHz disabled at 3.0 V                       |      |      |      |      |       |

|                       | • @ -40 to 25°C                                                            | _    | 0.19 | 0.22 | μA   |       |

|                       | • @ 70°C                                                                   | _    | 0.49 | 0.64 | μA   |       |

|                       | • @ 105°C                                                                  |      | 2.2  | 3.2  | μA   |       |

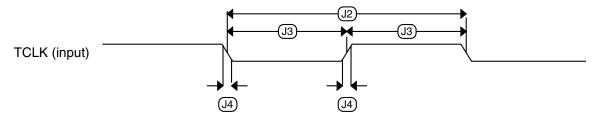

Figure 5. Test clock input timing

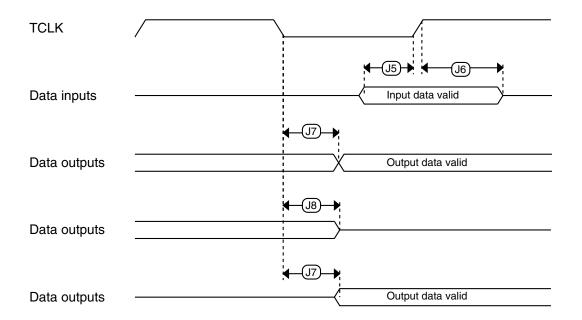

Figure 6. Boundary scan (JTAG) timing

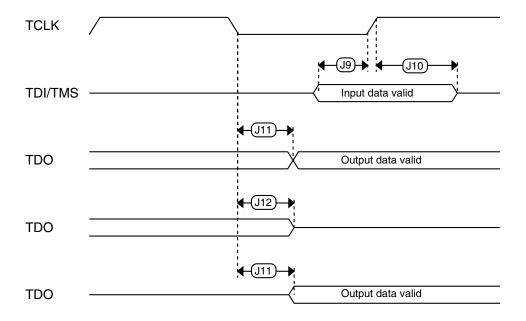

**Figure 7. Test Access Port timing**

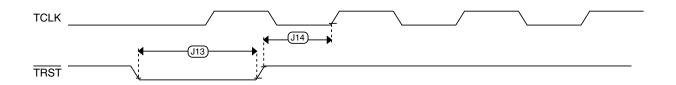

Figure 8. TRST timing

# 6.2 System modules

There are no specifications necessary for the device's system modules.

## 6.3 Clock modules

# 6.3.1 MCG specifications

Table 15. MCG specifications

| Symbol                   | Description                                                                         |                                                          | Min.                            | Тур.      | Max.              | Unit              | Notes |

|--------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------|-----------|-------------------|-------------------|-------|

| f <sub>ints_ft</sub>     |                                                                                     | frequency (slow clock) —<br>nominal VDD and 25 °C        | _                               | 32.768    | _                 | kHz               |       |

| f <sub>ints_t</sub>      | Internal reference trimmed                                                          | frequency (slow clock) — user                            | 31.25                           | _         | 39.0625           | kHz               |       |

| $\Delta_{fdco\_res\_t}$  | Resolution of trimr<br>frequency at fixed<br>using SCTRIM and                       | _                                                        | ± 0.3                           | ± 0.6     | %f <sub>dco</sub> | 1                 |       |

| $\Delta f_{dco\_res\_t}$ |                                                                                     | ned average DCO output<br>voltage and temperature —<br>y | _                               | ± 0.2     | ± 0.5             | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco\_t}$      |                                                                                     | rimmed average DCO output tage and temperature           | _                               | +0.5/-0.7 | ± 3               | %f <sub>dco</sub> | 1,    |

| $\Delta f_{dco\_t}$      | Total deviation of t<br>frequency over fixe<br>range of 0–70°C                      | _                                                        | ± 0.3                           | ± 3       | %f <sub>dco</sub> | 1                 |       |

| f <sub>intf_ft</sub>     | Internal reference frequency (fast clock) — factory trimmed at nominal VDD and 25°C |                                                          | _                               | 4         | _                 | MHz               |       |

| f <sub>intf_t</sub>      | Internal reference frequency (fast clock) — user trimmed at nominal VDD and 25 °C   |                                                          | 3                               | _         | 5                 | MHz               |       |

| f <sub>loc_low</sub>     | Loss of external clock minimum frequency — RANGE = 00                               |                                                          | (3/5) x<br>f <sub>ints_t</sub>  | _         | _                 | kHz               |       |

| f <sub>loc_high</sub>    | Loss of external clock minimum frequency — RANGE = 01, 10, or 11                    |                                                          | (16/5) x<br>f <sub>ints_t</sub> | _         | _                 | kHz               |       |

|                          |                                                                                     | F                                                        | LL                              |           |                   |                   |       |

| f <sub>fII_ref</sub>     | FLL reference free                                                                  | uency range                                              | 31.25                           | _         | 39.0625           | kHz               |       |

| f <sub>dco</sub>         | DCO output frequency range                                                          | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>         | 20                              | 20.97     | 25                | MHz               | 2, 3  |

|                          |                                                                                     | Mid range (DRS=01)  1280 × f <sub>fll_ref</sub>          | 40                              | 41.94     | 50                | MHz               |       |

|                          |                                                                                     | Mid-high range (DRS=10) $1920 \times f_{\rm fil\_ref}$   | 60                              | 62.91     | 75                | MHz               |       |

|                          |                                                                                     | High range (DRS=11)  2560 × f <sub>fll_ref</sub>         | 80                              | 83.89     | 100               | MHz               |       |

| f <sub>dco_t_DMX32</sub> | DCO output frequency                                                                | Low range (DRS=00)  732 × f <sub>fll ref</sub>           | _                               | 23.99     | _                 | MHz               | 4, 5  |

|                          |                                                                                     | Mid range (DRS=01)                                       | _                               | 47.97     | _                 | MHz               |       |

|                          |                                                                                     | Mid-high range (DRS=10) $2197 \times f_{fil\_ref}$       | _                               | 71.99     | _                 | MHz               |       |

|                          |                                                                                     | High range (DRS=11)  2929 × f <sub>fll_ref</sub>         | _                               | 95.98     | _                 | MHz               |       |

4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

#### NOTE

The 32 kHz oscillator works in low power mode by default and cannot be moved into high power/gain mode.

#### 6.3.3 32 kHz oscillator electrical characteristics

This section describes the module electrical characteristics.

# 6.3.3.1 32 kHz oscillator DC electrical specifications Table 18. 32kHz oscillator DC electrical specifications

| Symbol                       | Description                                   | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>BAT</sub>             | Supply voltage                                | 1.71 | _    | 3.6  | V    |

| R <sub>F</sub>               | Internal feedback resistor                    | _    | 100  | _    | ΜΩ   |

| C <sub>para</sub>            | Parasitical capacitance of EXTAL32 and XTAL32 | _    | 5    | 7    | pF   |

| V <sub>pp</sub> <sup>1</sup> | Peak-to-peak amplitude of oscillation         | _    | 0.6  | _    | V    |

<sup>1.</sup> When a crystal is being used with the 32 kHz oscillator, the EXTAL32 and XTAL32 pins should only be connected to required oscillator components and must not be connected to any other devices.

# 6.3.3.2 32 kHz oscillator frequency specifications Table 19. 32 kHz oscillator frequency specifications

| Symbol                  | Description                               | Min. | Тур.   | Max.      | Unit | Notes |

|-------------------------|-------------------------------------------|------|--------|-----------|------|-------|

| f <sub>osc_lo</sub>     | Oscillator crystal                        | _    | 32.768 | _         | kHz  |       |

| t <sub>start</sub>      | Crystal start-up time                     | _    | 1000   |           | ms   | 1     |

| f <sub>ec_extal32</sub> | Externally provided input clock frequency | _    | 32.768 | _         | kHz  | 2     |

| V <sub>ec_extal32</sub> | Externally provided input clock amplitude | 700  | _      | $V_{BAT}$ | mV   | 2, 3  |

- 1. Proper PC board layout procedures must be followed to achieve specifications.

- This specification is for an externally supplied clock driven to EXTAL32 and does not apply to any other clock input. The oscillator remains enabled and XTAL32 must be left unconnected.

- The parameter specified is a peak-to-peak value and V<sub>IH</sub> and V<sub>IL</sub> specifications do not apply. The voltage of the applied clock must be within the range of V<sub>SS</sub> to V<sub>BAT</sub>.

# 6.4 Memories and memory interfaces

## 6.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

## 6.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

Table 20. NVM program/erase timing specifications

| Symbol                    | Description                              | Min. | Тур. | Max. | Unit | Notes |

|---------------------------|------------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub>       | Longword Program high-voltage time       | _    | 7.5  | 18   | μs   |       |

| t <sub>hversscr</sub>     | Sector Erase high-voltage time           | _    | 13   | 113  | ms   | 1     |

| t <sub>hversblk256k</sub> | Erase Block high-voltage time for 256 KB | _    | 104  | 904  | ms   | 1     |

<sup>1.</sup> Maximum time based on expectations at cycling end-of-life.

# 6.4.1.2 Flash timing specifications — commands Table 21. Flash command timing specifications

| Symbol                  | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-------------------------|-----------------------------------------------|------|------|------|------|-------|

|                         | Read 1s Block execution time                  |      |      |      |      |       |

| t <sub>rd1blk256k</sub> | 256 KB program/data flash                     | _    | _    | 1.7  | ms   |       |

| t <sub>rd1sec2k</sub>   | Read 1s Section execution time (flash sector) | _    | _    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>     | Program Check execution time                  | _    | _    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                  | _    | _    | 30   | μs   | 1     |

| t <sub>pgm4</sub>       | Program Longword execution time               | _    | 65   | 145  | μs   |       |

|                         | Erase Flash Block execution time              |      |      |      |      | 2     |

| t <sub>ersblk256k</sub> | 256 KB program/data flash                     | _    | 122  | 985  | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time             | _    | 14   | 114  | ms   | 2     |

|                         | Program Section execution time                |      |      |      |      |       |

| t <sub>pgmsec512</sub>  | 512 bytes flash                               | _    | 2.4  | _    | ms   |       |

| t <sub>pgmsec1k</sub>   | 1 KB flash                                    | _    | 4.7  | _    | ms   |       |

| t <sub>pgmsec2k</sub>   | 2 KB flash                                    | _    | 9.3  | _    | ms   |       |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time             |      | _    | 1.8  | ms   |       |

| t <sub>rdonce</sub>     | Read Once execution time                      | _    | _    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>    | Program Once execution time                   | _    | 65   | _    | μs   |       |

| t <sub>ersall</sub>     | Erase All Blocks execution time               | _    | 250  | 2000 | ms   | 2     |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time     | _    | _    | 30   | μs   | 1     |

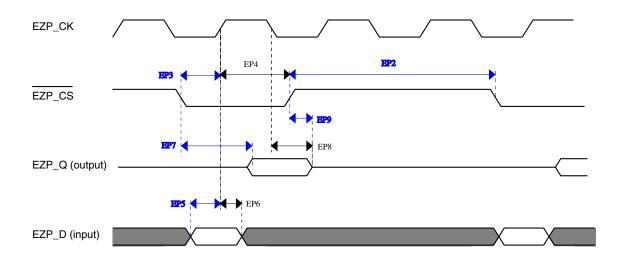

| Table 24. | EzPort switching specifica | tions (conti | nued) |

|-----------|----------------------------|--------------|-------|

| 4!        |                            | NA:          |       |

| Num  | Description                                  | Min.                    | Max.                | Unit |

|------|----------------------------------------------|-------------------------|---------------------|------|

| EP1a | EZP_CK frequency of operation (READ command) | _                       | f <sub>SYS</sub> /8 | MHz  |

| EP2  | EZP_CS negation to next EZP_CS assertion     | 2 x t <sub>EZP_CK</sub> | _                   | ns   |

| EP3  | EZP_CS input valid to EZP_CK high (setup)    | 5                       | _                   | ns   |

| EP4  | EZP_CK high to EZP_CS input invalid (hold)   | 5                       | _                   | ns   |

| EP5  | EZP_D input valid to EZP_CK high (setup)     | 2                       | _                   | ns   |

| EP6  | EZP_CK high to EZP_D input invalid (hold)    | 5                       | _                   | ns   |

| EP7  | EZP_CK low to EZP_Q output valid             | _                       | 16                  | ns   |

| EP8  | EZP_CK low to EZP_Q output invalid (hold)    | 0                       | _                   | ns   |

| EP9  | EZP_CS negation to EZP_Q tri-state           | _                       | 12                  | ns   |

Figure 9. EzPort Timing Diagram

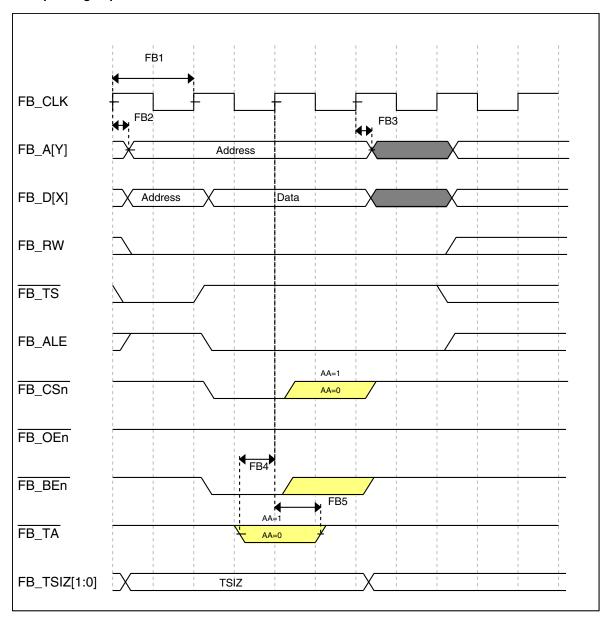

# 6.4.3 Flexbus switching specifications

All processor bus timings are synchronous; input setup/hold and output delay are given in respect to the rising edge of a reference clock, FB\_CLK. The FB\_CLK frequency may be the same as the internal system bus frequency or an integer divider of that frequency.

Figure 11. FlexBus write timing diagram

# 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

# 6.6 Analog

Table 28. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

| Symbol             | Description               | Conditions <sup>1</sup> .    | Min.         | Typ. <sup>2</sup> | Max.         | Unit             | Notes                   |

|--------------------|---------------------------|------------------------------|--------------|-------------------|--------------|------------------|-------------------------|

|                    | ADC                       | • ADLPC = 1, ADHSC = 0       | 1.2          | 2.4               | 3.9          | MHz              | t <sub>ADACK</sub> = 1/ |

|                    | asynchronous clock source | • ADLPC = 1, ADHSC = 1       | 2.4          | 4.0               | 6.1          | MHz              | f <sub>ADACK</sub>      |

| f <sub>ADACK</sub> |                           | • ADLPC = 0, ADHSC = 0       | 3.0          | 5.2               | 7.3          | MHz              |                         |

|                    |                           | • ADLPC = 0, ADHSC = 1       | 4.4          | 6.2               | 9.5          | MHz              |                         |

|                    | Sample Time               | See Reference Manual chapter | for sample t | imes              | 1            |                  |                         |

| TUE                | Total unadjusted          | 12-bit modes                 | _            | ±4                | ±6.8         | LSB <sup>4</sup> | 5                       |

|                    | error                     | <12-bit modes                | _            | ±1.4              | ±2.1         |                  |                         |

| DNL                | Differential non-         | 12-bit modes                 | _            | ±0.7              | -1.1 to +1.9 | LSB <sup>4</sup> | 5                       |

|                    | linearity                 |                              |              |                   | -0.3 to 0.5  |                  |                         |

|                    |                           | • <12-bit modes              | _            | ±0.2              |              |                  |                         |

| INL                | Integral non-             | 12-bit modes                 | _            | ±1.0              | -2.7 to +1.9 | LSB <sup>4</sup> | 5                       |

|                    | linearity                 |                              |              |                   | -0.7 to +0.5 |                  |                         |

|                    |                           | <12-bit modes                | _            | ±0.5              |              |                  |                         |

| $E_FS$             | Full-scale error          | 12-bit modes                 | _            | -4                | -5.4         | LSB <sup>4</sup> | V <sub>ADIN</sub> =     |

|                    |                           | <12-bit modes                | _            | -1.4              | -1.8         |                  | V <sub>DDA</sub>        |

| E <sub>Q</sub>     | Quantization              | 16-bit modes                 |              | -1 to 0           | _            | LSB <sup>4</sup> | 5                       |

| •                  | error                     | ≤13-bit modes                | _            | _                 | ±0.5         |                  |                         |

| ENOB               | Effective number          | 16-bit differential mode     |              |                   |              |                  | 6                       |

|                    | of bits                   | • Avg = 32                   | 12.8         | 14.5              | _            | bits             |                         |

|                    |                           | • Avg = 4                    | 11.9         | 13.8              | _            | bits             |                         |

|                    |                           | 16-bit single-ended mode     |              |                   |              |                  |                         |

|                    |                           | • Avg = 32                   | 10.0         | 10.0              |              | hita             |                         |

|                    |                           | • Avg = 4                    | 12.2<br>11.4 | 13.9<br>13.1      | _            | bits             |                         |

|                    | Signal-to-noise           | See ENOB                     |              |                   |              | bits             |                         |

| SINAD              | plus distortion           | OCC ENOB                     | 6.02         | 2 × ENOB +        | 1.76         | dB               |                         |

| THD                | Total harmonic            | 16-bit differential mode     |              |                   |              |                  | 7                       |

|                    | distortion                | • Avg = 32                   | _            | -94               | _            | dB               |                         |

|                    |                           | 16-bit single-ended mode     |              | 0.5               |              | ٩D               |                         |

|                    |                           | • Avg = 32                   | _            | -85               | _            | dB               |                         |

| SFDR               | Spurious free             | 16-bit differential mode     |              |                   |              |                  | 7                       |

|                    | dynamic range             | • Avg = 32                   | 82           | 95                | -            | dB               |                         |

|                    |                           | 16-bit single-ended mode     | 70           |                   |              | 15               |                         |

|                    | 1                         |                              | 78           | 90                | _            | dB               |                         |

Table 30. 16-bit ADC with PGA characteristics (continued)

| Symbol | Description                           | Conditions            | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes                                       |

|--------|---------------------------------------|-----------------------|------|-------------------|------|------|---------------------------------------------|

| SFDR   | Spurious free                         | • Gain=1              | 85   | 105               | _    | dB   | 16-bit                                      |

|        | dynamic range                         | • Gain=64             | 53   | 88                | _    | dB   | differential<br>mode,<br>Average=32,        |

|        |                                       |                       |      |                   |      |      | f <sub>in</sub> =100Hz                      |

| ENOB   | Effective number                      | • Gain=1, Average=4   | 11.6 | 13.4              | _    | bits | 16-bit                                      |

|        | of bits                               | • Gain=1, Average=8   | 8.0  | 13.6              | _    | bits | differential<br>mode,f <sub>in</sub> =100Hz |

|        |                                       | • Gain=64, Average=4  | 7.2  | 9.6               | _    | bits |                                             |

|        |                                       | • Gain=64, Average=8  | 6.3  | 9.6               | _    | bits |                                             |

|        |                                       | • Gain=1, Average=32  | 12.8 | 14.5              | _    | bits |                                             |

|        |                                       | • Gain=2, Average=32  | 11.0 | 14.3              | _    | bits |                                             |

|        |                                       | • Gain=4, Average=32  | 7.9  | 13.8              | _    | bits |                                             |

|        |                                       | • Gain=8, Average=32  | 7.3  | 13.1              | _    | bits |                                             |

|        |                                       | • Gain=16, Average=32 | 6.8  | 12.5              | _    | bits |                                             |

|        |                                       | • Gain=32, Average=32 | 6.8  | 11.5              | _    | bits |                                             |

|        |                                       | • Gain=64, Average=32 | 7.5  | 10.6              | _    | bits |                                             |

| SINAD  | Signal-to-noise plus distortion ratio | See ENOB              | 6.02 | × ENOB +          | 1.76 | dB   |                                             |

- 1. Typical values assume  $V_{DDA}$  =3.0V, Temp=25°C,  $f_{ADCK}$ =6MHz unless otherwise stated.

- 2. This current is a PGA module adder, in addition to ADC conversion currents.

- 3. Between IN+ and IN-. The PGA draws a DC current from the input terminals. The magnitude of the DC current is a strong function of input common mode voltage (V<sub>CM</sub>) and the PGA gain.

- 4. Gain =  $2^{PGAG}$

- 5. After changing the PGA gain setting, a minimum of 2 ADC+PGA conversions should be ignored.

- 6. Limit the input signal swing so that the PGA does not saturate during operation. Input signal swing is dependent on the PGA reference voltage and gain setting.

## 6.6.2 CMP and 6-bit DAC electrical specifications

Table 31. Comparator and 6-bit DAC electrical specifications

| Symbol            | Description                                     | Min.                  | Тур. | Max.     | Unit |

|-------------------|-------------------------------------------------|-----------------------|------|----------|------|

| $V_{DD}$          | Supply voltage                                  | 1.71                  | _    | 3.6      | V    |

| I <sub>DDHS</sub> | Supply current, High-speed mode (EN=1, PMODE=1) | _                     | _    | 200      | μΑ   |

| I <sub>DDLS</sub> | Supply current, low-speed mode (EN=1, PMODE=0)  | _                     | _    | 20       | μΑ   |

| V <sub>AIN</sub>  | Analog input voltage                            | V <sub>SS</sub> - 0.3 | _    | $V_{DD}$ | V    |

| V <sub>AIO</sub>  | Analog input offset voltage                     | _                     | _    | 20       | mV   |

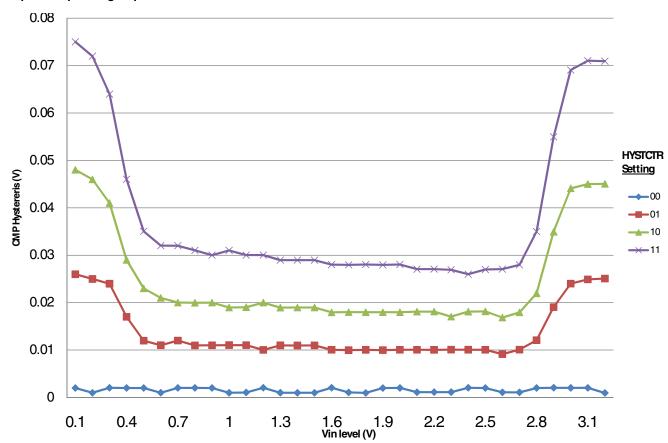

Figure 15. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=0)

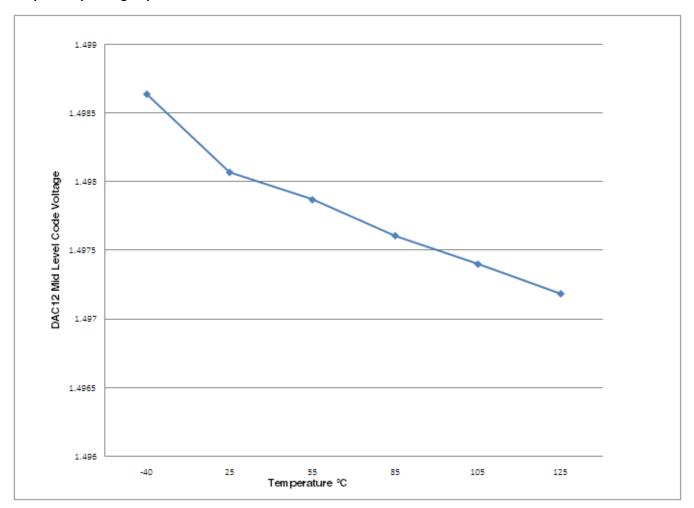

Figure 18. Offset at half scale vs. temperature

## 6.6.4 Voltage reference electrical specifications

Table 34. VREF full-range operating requirements

| Symbol         | Description             | Min.                                      | Max. | Unit | Notes |

|----------------|-------------------------|-------------------------------------------|------|------|-------|

| $V_{DDA}$      | Supply voltage          | 1.71 3.6                                  |      | V    |       |

| T <sub>A</sub> | Temperature             | Operating temperature range of the device |      | °C   |       |

| C <sub>L</sub> | Output load capacitance | 100                                       |      | nF   | 1, 2  |

- C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

- 2. The load capacitance should not exceed +/-25% of the nominal specified C<sub>L</sub> value over the operating temperature range of the device.

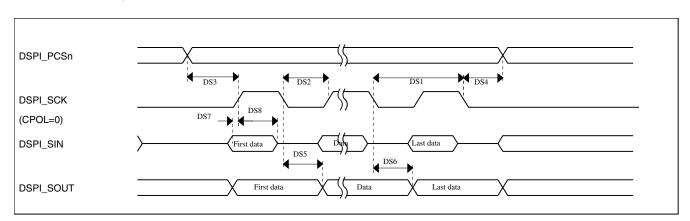

## 6.8.6 DSPI switching specifications (full voltage range)

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

|     | Operating voltage                   | 1.71                          | 3.6                      | V    | 1     |

|     | Frequency of operation              | _                             | 12.5                     | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 4 x t <sub>BUS</sub>          | _                        | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | _                             | 8.5                      | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -1.2                          | _                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 19.1                          | _                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | _                        | ns   |       |

Table 42. Master mode DSPI timing (full voltage range)

- 2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

- 3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

Figure 21. DSPI classic SPI timing — master mode

Table 43. Slave mode DSPI timing (full voltage range)

| Num | Description            | Min. | Max. | Unit |

|-----|------------------------|------|------|------|

|     | Operating voltage      | 1.71 | 3.6  | V    |

|     | Frequency of operation | _    | 6.25 | MHz  |

The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

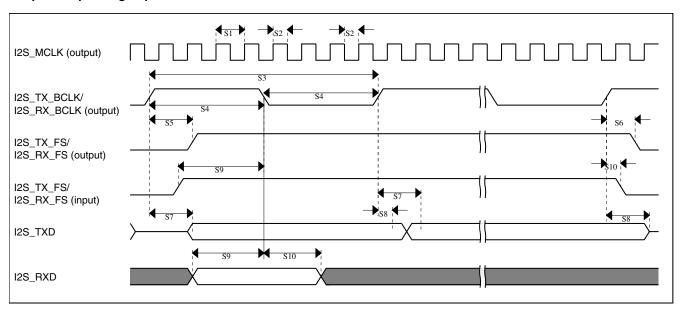

Figure 29. I2S/SAI timing — master modes

Table 51. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                 | Min. | Max. | Unit        |

|------|----------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                              | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                     | 250  | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)           | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before I2S_TX_BCLK/I2S_RX_BCLK | 30   | _    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after I2S_TX_BCLK/I2S_RX_BCLK   | 3    | _    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                  | _    | 63   | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                | 0    | _    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                               | 30   | _    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                 | 2    | _    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup> | _    | 72   | ns          |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

| 100<br>LQFP | Pin Name          | Default                              | ALT0                                 | ALT1              | ALT2      | ALT3                            | ALT4         | ALT5    | ALT6            | ALT7 | EzPort |

|-------------|-------------------|--------------------------------------|--------------------------------------|-------------------|-----------|---------------------------------|--------------|---------|-----------------|------|--------|

| 54          | PTB1              | ADC0_SE9/<br>ADC1_SE9/<br>TSI0_CH6   | ADC0_SE9/<br>ADC1_SE9/<br>TSI0_CH6   | PTB1              | I2C0_SDA  | FTM1_CH1                        |              |         | FTM1_QD_<br>PHB |      |        |

| 55          | PTB2              | ADC0_SE12/<br>TSI0_CH7               | ADC0_SE12/<br>TSI0_CH7               | PTB2              | 12C0_SCL  | UARTO_RTS_b                     |              |         | FTM0_FLT3       |      |        |

| 56          | PTB3              | ADC0_SE13/<br>TSI0_CH8               | ADC0_SE13/<br>TSI0_CH8               | PTB3              | I2C0_SDA  | UARTO_CTS_<br>b/<br>UARTO_COL_b |              |         | FTM0_FLT0       |      |        |

| 57          | PTB9              | DISABLED                             |                                      | PTB9              | SPI1_PCS1 | UART3_CTS_b                     |              | FB_AD20 |                 |      |        |

| 58          | PTB10             | ADC1_SE14                            | ADC1_SE14                            | PTB10             | SPI1_PCS0 | UART3_RX                        |              | FB_AD19 | FTM0_FLT1       |      |        |

| 59          | PTB11             | ADC1_SE15                            | ADC1_SE15                            | PTB11             | SPI1_SCK  | UART3_TX                        |              | FB_AD18 | FTM0_FLT2       |      |        |

| 60          | VSS               | VSS                                  | VSS                                  |                   |           |                                 |              |         |                 |      |        |

| 61          | VDD               | VDD                                  | VDD                                  |                   |           |                                 |              |         |                 |      |        |

| 62          | PTB16             | TSI0_CH9                             | TSI0_CH9                             | PTB16             | SPI1_SOUT | UARTO_RX                        |              | FB_AD17 | EWM_IN          |      |        |

| 63          | PTB17             | TSI0_CH10                            | TSI0_CH10                            | PTB17             | SPI1_SIN  | UARTO_TX                        |              | FB_AD16 | EWM_OUT_b       |      |        |

| 64          | PTB18             | TSI0_CH11                            | TSI0_CH11                            | PTB18             | CAN0_TX   | FTM2_CH0                        | I2S0_TX_BCLK | FB_AD15 | FTM2_QD_<br>PHA |      |        |

| 65          | PTB19             | TSI0_CH12                            | TSI0_CH12                            | PTB19             | CAN0_RX   | FTM2_CH1                        | I2S0_TX_FS   | FB_OE_b | FTM2_QD_<br>PHB |      |        |

| 66          | PTB20             | DISABLED                             |                                      | PTB20             | SPI2_PCS0 |                                 |              | FB_AD31 | CMP0_OUT        |      |        |

| 67          | PTB21             | DISABLED                             |                                      | PTB21             | SPI2_SCK  |                                 |              | FB_AD30 | CMP1_OUT        |      |        |

| 68          | PTB22             | DISABLED                             |                                      | PTB22             | SPI2_SOUT |                                 |              | FB_AD29 | CMP2_OUT        |      |        |

| 69          | PTB23             | DISABLED                             |                                      | PTB23             | SPI2_SIN  | SPI0_PCS5                       |              | FB_AD28 |                 |      |        |

| 70          | PTC0              | ADC0_SE14/<br>TSI0_CH13              | ADC0_SE14/<br>TSI0_CH13              | PTC0              | SPI0_PCS4 | PDB0_EXTRG                      |              | FB_AD14 | 12S0_TXD1       |      |        |

| 71          | PTC1/<br>LLWU_P6  | ADC0_SE15/<br>TSI0_CH14              | ADC0_SE15/<br>TSI0_CH14              | PTC1/<br>LLWU_P6  | SPI0_PCS3 | UART1_RTS_b                     | FTM0_CH0     | FB_AD13 | 12S0_TXD0       |      |        |

| 72          | PTC2              | ADC0_SE4b/<br>CMP1_IN0/<br>TSI0_CH15 | ADC0_SE4b/<br>CMP1_IN0/<br>TSI0_CH15 | PTC2              | SPI0_PCS2 | UART1_CTS_b                     | FTM0_CH1     | FB_AD12 | I2S0_TX_FS      |      |        |

| 73          | PTC3/<br>LLWU_P7  | CMP1_IN1                             | CMP1_IN1                             | PTC3/<br>LLWU_P7  | SPI0_PCS1 | UART1_RX                        | FTM0_CH2     | CLKOUT  | I2S0_TX_BCLK    |      |        |

| 74          | VSS               | VSS                                  | VSS                                  |                   |           |                                 |              |         |                 |      |        |

| 75          | VDD               | VDD                                  | VDD                                  |                   |           |                                 |              |         |                 |      |        |

| 76          | PTC4/<br>LLWU_P8  | DISABLED                             |                                      | PTC4/<br>LLWU_P8  | SPI0_PCS0 | UART1_TX                        | FTM0_CH3     | FB_AD11 | CMP1_OUT        |      |        |

| 77          | PTC5/<br>LLWU_P9  | DISABLED                             |                                      | PTC5/<br>LLWU_P9  | SPI0_SCK  | LPTMR0_ALT2                     | 12S0_RXD0    | FB_AD10 | CMP0_OUT        |      |        |

| 78          | PTC6/<br>LLWU_P10 | CMP0_IN0                             | CMP0_IN0                             | PTC6/<br>LLWU_P10 | SPI0_SOUT | PDB0_EXTRG                      | I2S0_RX_BCLK | FB_AD9  | I2S0_MCLK       |      |        |

| 79          | PTC7              | CMP0_IN1                             | CMP0_IN1                             | PTC7              | SPI0_SIN  | USB_SOF_<br>OUT                 | I2S0_RX_FS   | FB_AD8  |                 |      |        |

| 80          | PTC8              | ADC1_SE4b/<br>CMP0_IN2               | ADC1_SE4b/<br>CMP0_IN2               | PTC8              |           |                                 | I2S0_MCLK    | FB_AD7  |                 |      |        |

| 81          | PTC9              | ADC1_SE5b/<br>CMP0_IN3               | ADC1_SE5b/<br>CMP0_IN3               | PTC9              |           |                                 | I2S0_RX_BCLK | FB_AD6  | FTM2_FLT0       |      |        |

How to Reach Us:

Home Page: freescale.com

Web Support:

freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. Cortex-M4 is the trademark of ARM Limited.

© 2012–2013Freescale Semiconductor, Inc.

Document Number: K20P100M100SF2V2

Rev. 3 06/2013