Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

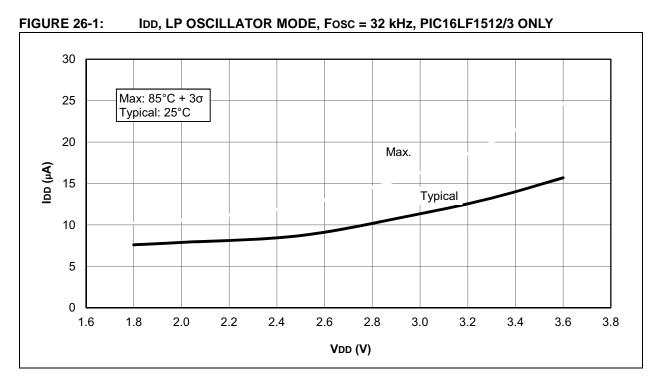

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

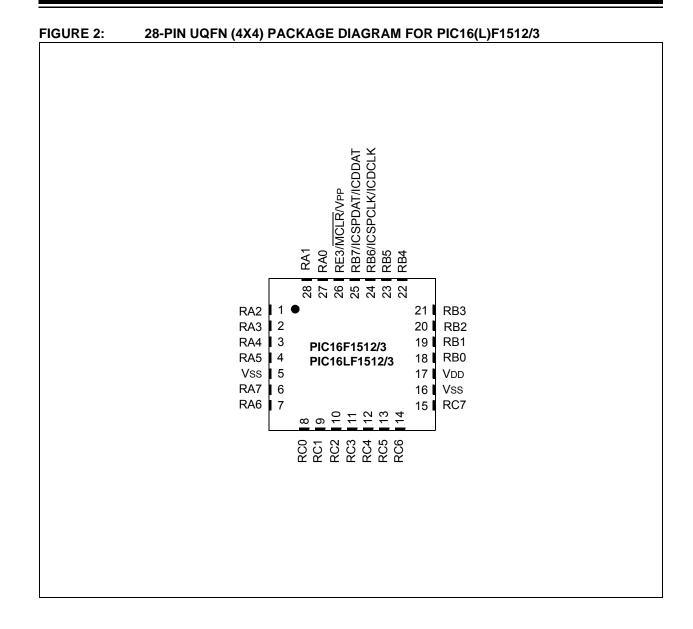

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1512-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1512/3

# 4.5 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 11.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

## REGISTER 4-3: DEVICEID: DEVICE ID REGISTER

|       |          | R      | R | R   | R        | R | R     |

|-------|----------|--------|---|-----|----------|---|-------|

|       |          |        |   | DEV | <8:3>    |   |       |

|       |          | bit 13 |   |     |          |   |       |

|       |          |        |   |     |          |   |       |

| R     | R        | R      | R | R   | R        | R | R     |

|       | DEV<2:0> |        |   |     | REV<4:0> |   |       |

| bit 7 |          |        |   |     |          |   | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '1'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | P = Programmable bit                                  |

|                      |                      |                                                       |

## bit 13-5 **DEV<8:0>:** Device ID bits

| Device      | DEVICEID<13:0> Values |          |  |  |  |  |  |

|-------------|-----------------------|----------|--|--|--|--|--|

| Device      | DEV<8:0>              | REV<4:0> |  |  |  |  |  |

| PIC16F1512  | 01 0111 000           | x xxxx   |  |  |  |  |  |

| PIC16F1513  | 01 0110 010           | x xxxx   |  |  |  |  |  |

| PIC16LF1512 | 01 0111 001           | x xxxx   |  |  |  |  |  |

| PIC16LF1513 | 01 0111 010           | x xxxx   |  |  |  |  |  |

#### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision (see Table under DEV<8:0> above).

# 6.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

# REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | -   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

| Legend:          |                         |                                            |                                                                 |

|------------------|-------------------------|--------------------------------------------|-----------------------------------------------------------------|

| HC = Bit is cle  | ared by hardwa          | are                                        | HS = Bit is set by hardware                                     |

| R = Readable     | bit                     | W = Writable bit                           | U = Unimplemented bit, read as '0'                              |

| u = Bit is unch  | anged                   | x = Bit is unknown                         | -m/n = Value at POR and BOR/Value at all other Resets           |

| '1' = Bit is set |                         | '0' = Bit is cleared                       | q = Value depends on condition                                  |

| bit 7            | STKOVE. St              | ack Overflow Eleg bit                      |                                                                 |

| DIL 7            |                         | ack Overflow Flag bit<br>Overflow occurred |                                                                 |

|                  |                         | Overflow has not occurred                  | or cleared by firmware                                          |

| bit 6            |                         | ack Underflow Flag bit                     |                                                                 |

|                  |                         | Underflow occurred                         |                                                                 |

|                  | 0 = A Stack             | Underflow has not occurred                 | d or cleared by firmware                                        |

| bit 5            | Unimplemen              | ted: Read as '0'                           |                                                                 |

| bit 4            | RWDT: Watc              | hdog Timer Reset Flag bit                  |                                                                 |

|                  |                         | •                                          | ccurred or set to '1' by firmware                               |

|                  |                         | dog Timer Reset has occur                  | red (cleared by hardware)                                       |

| bit 3            |                         | LR Reset Flag bit                          |                                                                 |

|                  |                         | Reset has not occurred or                  |                                                                 |

| h:# 0            |                         | · ·                                        | '0' in hardware when a MCLR Reset occurs)                       |

| bit 2            |                         | struction Flag bit                         |                                                                 |

|                  |                         |                                            | xecuted or set to '1' by firmware<br>uted (cleared by hardware) |

| bit 1            |                         | -on Reset Status bit                       |                                                                 |

|                  |                         | r-on Reset occurred                        |                                                                 |

|                  |                         |                                            | e set in software after a Power-on Reset occurs)                |

| bit 0            |                         | -out Reset Status bit                      |                                                                 |

|                  | 1 = No Brow             | n-out Reset occurred                       |                                                                 |

|                  | 0 = A Brown-<br>occurs) | out Reset occurred (must l                 | be set in software after a Power-on Reset or Brown-out Rese     |

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|-------|---------|--------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF  | INTF   | IOCIF  | 69                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   | PS<2:0> |        |        | 159                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE | CCP1IE  | TMR2IE | TMR1IE | 70                  |

| PIE2       | OSFIE   |        | —      | -      | BCLIE | —       |        | CCP2IE | 71                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF | CCP1IF  | TMR2IF | TMR1IF | 72                  |

| PIR2       | OSFIF   |        | _      |        | BCLIF | —       |        | CCP2IF | 73                  |

## TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by interrupts.

#### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Section 25.0 "Electrical Specifications" for the LFINTOSC tolerances.

#### WDT Operating Modes 10.2

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### WDT CONTROLLED BY SOFTWARE 10.2.3

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-2 for more details.

| TABLE 10-1: WDI OPERATING MODES | TABLE 10-1: | WDT OPERATING MODES |

|---------------------------------|-------------|---------------------|

|---------------------------------|-------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | v      | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 01        | 1      | х              | Active      |

| 01        | 0      | ^              | Disabled    |

| 00        | Х      | Х              | Disabled    |

#### **TABLE 10-2:** WDT CLEARING CONDITIONS

Conditions

#### 10.3 **Time-Out Period**

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 10.4 **Clearing the WDT**

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

#### 10.5 **Operation During Sleep**

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. See Section 3.0 "Memory Organization" and The STATUS register (Register 3-1) for more information.

| Conditions                                              | VVD1                         |

|---------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                          |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                           |                              |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                |                              |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |

wпт

# 11.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/ erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection  $(\overline{CP} = 0)^{(1)}$ , disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

| Note 1: | Code    | protection        | of   | the    | entire  | Fla | sh  |

|---------|---------|-------------------|------|--------|---------|-----|-----|

|         | progra  | m m <u>em</u> ory | ar   | ray i  | s enab  | led | by  |

|         | clearin | g the CP bit      | of C | Config | uration | Wor | ds. |

# 11.1 **PMADRL and PMADRH Registers**

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

## 11.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

# 11.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

See Table 11-1 for Erase Row size and the number of write latches for Flash program memory.

Note: If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash program memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

#### EXAMPLE 11-3: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. 64 bytes of data are loaded, starting at the address in DATA\_ADDR ; 2. Each word of data to be written is made up of two adjacent bytes in DATA\_ADDR, ; stored in little endian format ; 3. A valid starting address (the least significant bits = 00000) is loaded in ADDRH: ADDRL ; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM) ; BCF INTCON,GIE ; Disable ints so required sequences will execute properly ; Bank 3 BANKSEL PMADRH MOVF ADDRH,W ; Load initial address MOVWF PMADRH MOVF ADDRL,W MOVWF PMADRL LOW DATA\_ADDR ; Load initial data address MOVLW MOVWF FSROL ; MOVLW HIGH DATA\_ADDR ; Load initial data address MOVWF FSR0H ; PMCON1,CFGS ; Not configuration space BCF BSF PMCON1,WREN ; Enable writes PMCON1,LWLO ; Only Load Write Latches BSF LOOP MOVIW FSR0++ ; Load first data byte into lower MOVWF PMDATT. ; ; Load second data byte into upper MOVIW FSR0++ MOVWF PMDATH MOVF ; Check if lower bits of address are '00000' PMADRL,W ; Check if we're on the last of 32 addresses XORLW 0x1F ANDLW 0x1F BTFSC STATUS,Z ; Exit if last of 32 words, GOTO START\_WRITE ; MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh MOVWF PMCON2 ; Write AAh BSF ; Set WR bit to begin write PMCON1,WR NOP ; NOP instructions are forced as processor ; loads program memory write latches NOP INCF PMADRL, F ; Still loading latches Increment address GOTO LOOP ; Write next latches START\_WRITE BCF PMCON1,LWLO ; No more loading latches - Actually start Flash program ; memory write MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh ; MOVWF PMCON2 ; Write AAh BSF PMCON1,WR ; Set WR bit to begin write NOP ; NOP instructions are forced as processor writes ; all the program memory write latches simultaneously NOP ; to program memory. ; After NOPs, the processor ; stalls until the self-write process in complete ; after write processor continues with 3rd instruction PMCON1,WREN BCF ; Disable writes BSF INTCON,GIE ; Enable interrupts

| U-1 <sup>(1)</sup> | R/W-0/0                                | R/W-0/0                                | R/W/HC-0/0        | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0            | R/S/HC-0/0                             | R/S/HC-0/0       |

|--------------------|----------------------------------------|----------------------------------------|-------------------|---------------------------|--------------------|----------------------------------------|------------------|

| _                  | CFGS                                   | LWLO                                   | FREE              | WRERR                     | WREN               | WR                                     | RD               |

| bit 7              |                                        |                                        |                   |                           |                    |                                        | bit              |

| Legend:            |                                        |                                        |                   |                           |                    |                                        |                  |

| R = Readable       | bit                                    | W = Writable b                         | bit               | U = Unimpleme             | ented bit, read as | s 'O'                                  |                  |

| S = Bit can on     | ly be set                              | x = Bit is unkn                        | own               | -n/n = Value at           | POR and BOR/       | Value at all other I                   | Resets           |

| '1' = Bit is set   |                                        | '0' = Bit is clea                      | red               | HC = Bit is clea          | ared by hardware   | 9                                      |                  |

| hit 7              | Unimploment                            | ed. Dood oo '1'                        |                   |                           |                    |                                        |                  |

| bit 7              | •                                      | ed: Read as '1'                        |                   |                           |                    |                                        |                  |

| bit 6              | 0                                      | uration Select bi                      |                   | ID Registers              |                    |                                        |                  |

|                    |                                        | lash program me                        |                   | i Di Registers            |                    |                                        |                  |

| bit 5              |                                        | Write Latches Or                       | -                 |                           |                    |                                        |                  |

|                    | 1 = Only the                           | addressed progr                        | am memory write   | e latch is loaded/        | updated on the     | next WR commar                         | ıd               |

|                    |                                        |                                        |                   | h is loaded/updat         | ed and a write of  | all program mem                        | ory write latche |

|                    |                                        | tiated on the nex                      |                   |                           |                    |                                        |                  |

| bit 4              | 0                                      | m Flash Erase E                        |                   |                           |                    | ······································ |                  |

|                    |                                        | an erase operation                     |                   | •                         | ardware cleared    | upon completion)                       | )                |

| bit 3              |                                        | gram/Erase Error                       |                   |                           |                    |                                        |                  |

|                    |                                        |                                        | -                 | or erase sequen           | ce attempt or te   | rmination (bit is s                    | et automatical   |

|                    | ,                                      | et attempt (write                      | ,                 | ,                         |                    | ,                                      |                  |

|                    | 0 = The prog                           | ram or erase ope                       | eration complete  | d normally.               |                    |                                        |                  |

| bit 2              | •                                      | am/Erase Enable                        |                   |                           |                    |                                        |                  |

|                    |                                        | ogram/erase cyc                        |                   |                           |                    |                                        |                  |

| hit 1              | WR: Write Co                           | rogramming/eras                        | ang of program i  | 10511                     |                    |                                        |                  |

| bit 1              |                                        | a program Flash                        | program/erase o   | neration                  |                    |                                        |                  |

|                    |                                        |                                        |                   | leared by hardwa          | are once operatio  | on is complete.                        |                  |

|                    | •                                      | bit can only be s                      |                   | •                         |                    | · · · · ·                              |                  |

|                    | 0 = Program/                           | erase operation                        | to the Flash is c | omplete and inac          | tive.              |                                        |                  |

| bit 0              | RD: Read Cor                           | ntrol bit                              |                   |                           |                    |                                        |                  |

|                    |                                        |                                        | read. Read takes  | s one cycle. RD is        | s cleared in hard  | lware. The RD bit                      | can only be se   |

|                    | •                                      | red) in software.<br>initiate a progra | m Flash read      |                           |                    |                                        |                  |

| Noto 1.            |                                        |                                        | n nash leau.      |                           |                    |                                        |                  |

|                    | nimplemented bit,<br>he WRERR bit is a |                                        | hy hardware whe   | en a program me           | mory write or er   | ase operation is s                     | tarted (WR = 1   |

|                    | he LWLO bit is ian                     | -                                      | -                 |                           | -                  |                                        |                  |

#### DECISTED 44 C. DMCON4, DDOCDAM MEMORY CONTROL 4 DECISTED

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

# PIC16(L)F1512/3

# 12.0 I/O PORTS

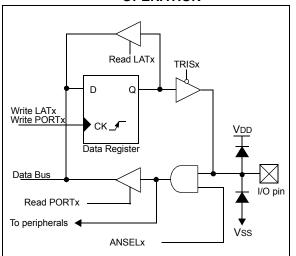

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

# TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC | PORTE |

|---------------|-------|-------|-------|-------|

| PIC16(L)F1512 | •     | •     | •     | ٠     |

| PIC16(L)F1513 | •     | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

## FIGURE 12-1: GENERIC I/O PORT OPERATION

# EXAMPLE 12-1: INITIALIZING PORTA

; This code example illustrates ; initializing the PORTA register. The ; other ports are initialized in the same ; manner.

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

| U-0                                     | U-0                 | U-0             | U-0                                                   | R/W-1/1                            | U-0 | U-0 | U-0   |  |  |  |

|-----------------------------------------|---------------------|-----------------|-------------------------------------------------------|------------------------------------|-----|-----|-------|--|--|--|

| —                                       | —                   | —               | —                                                     | WPUE3                              | —   | —   | —     |  |  |  |

| bit 7                                   | it 7                |                 |                                                       |                                    |     |     | bit 0 |  |  |  |

|                                         |                     |                 |                                                       |                                    |     |     |       |  |  |  |

| Legend:                                 |                     |                 |                                                       |                                    |     |     |       |  |  |  |

| R = Readable bit W = Writable bit       |                     |                 |                                                       | U = Unimplemented bit, read as '0' |     |     |       |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                     | nown            | -n/n = Value at POR and BOR/Value at all other Resets |                                    |     |     |       |  |  |  |

| '1' = Bit is set '0' = Bit is cleared   |                     |                 | ared                                                  |                                    |     |     |       |  |  |  |

| 1.11.77                                 |                     |                 | -1                                                    |                                    |     |     |       |  |  |  |

| bit 7-4                                 | Unimplemen          | ted: Read as 'o | ),                                                    |                                    |     |     |       |  |  |  |

| bit 3                                   | WPUE: Weak          | Pull-up Regist  | er bit                                                |                                    |     |     |       |  |  |  |

|                                         | 1 = Pull-up enabled |                 |                                                       |                                    |     |     |       |  |  |  |

|                                         | 0 = Pull-up dis     | sabled          |                                                       |                                    |     |     |       |  |  |  |

| bit 2-0                                 | Unimplemen          | ted: Read as '  | כי                                                    |                                    |     |     |       |  |  |  |

# **REGISTER 12-17: WPUE: WEAK PULL-UP PORTE REGISTER**<sup>(1,2)</sup>

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Name      | Bit 7 | Bit 6 | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit 0 | Register<br>on Page |  |

|-----------|-------|-------|-------------|-------|-------|-------|------------|-------|---------------------|--|

| A(A)DCON0 |       |       | CHS<4:0>    |       |       |       |            | ADON  | 130, 147            |  |

| CCPxCON   |       | _     | — DCxB<1:0> |       |       |       | CCPxM<3:0> |       |                     |  |

| PORTE     | _     | —     | _           | —     | RE3   | _     | —          | —     | 113                 |  |

| TRISE     |       | _     | _           | _     | (1)   |       | —          |       | 113                 |  |

| WPUE      | _     | _     | _           | _     | WPUE3 | _     | _          |       | 114                 |  |

#### TABLE 12-9: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Unimplemented, read as '1'.

#### TABLE 12-10: SUMMARY OF CONFIGURATION WORD WITH PORTE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|-----------|---------|---------------------|

|         | 13:8 | _       | _       |          | IESO     | CLKOUTEN | BOREN<1:0> |           | —       |                     |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   |            | FOSC<2:0> |         | 37                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTE.

# 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

| Note: | This section of the ADC chapter discusses |

|-------|-------------------------------------------|

|       | legacy operation. If new Capacitive       |

|       | Voltage Divider (CVD) features are        |

|       | needed, refer to Section 16.5 "Hardware   |

|       | Capacitive Voltage Divider (CVD)          |

|       | Module" for more information.             |

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake up the device from Sleep.

|                  |                        |                                   |                 | oon noe n      | LOIOTEIX                    |                  |              |

|------------------|------------------------|-----------------------------------|-----------------|----------------|-----------------------------|------------------|--------------|

| U-0              | R/W-0/0                | R/W-0/0                           | R/W-0/0         | U-0            | U-0                         | U-0              | U-0          |

| _                | Г                      | [RIGSEL<2:0>(                     | ,2)             | —              | —                           | —                | _            |

| bit 7            |                        |                                   |                 |                |                             |                  | bit 0        |

|                  |                        |                                   |                 |                |                             |                  |              |

| Legend:          |                        |                                   |                 |                |                             |                  |              |

| R = Readable     | e bit                  | W = Writable                      | bit             | U = Unimpler   | mented bit, read            | d as '0'         |              |

| u = Bit is uncl  | hanged                 | x = Bit is unkr                   | nown            | -n/n = Value a | at POR and BO               | R/Value at all o | other Resets |

| '1' = Bit is set |                        | '0' = Bit is cle                  | ared            |                |                             |                  |              |

|                  |                        |                                   |                 |                |                             |                  |              |

| bit 7            | Unimpleme              | nted: Read as '                   | 0'              |                |                             |                  |              |

| bit 6-4          | TRIGSEL<2              | :0>: ADC Speci                    | al Event Trigg  | er Source Sele | ction bits <sup>(1,2)</sup> |                  |              |

|                  |                        | rved. Auto-conv                   | ••              |                |                             |                  |              |

|                  |                        | rved. Auto-conv<br>2 Match to PR2 | ersion Triggei  | disabled.      |                             |                  |              |

|                  | 101 - TMR<br>100 = TMR |                                   |                 |                |                             |                  |              |

|                  | 011 = TMR              |                                   |                 |                |                             |                  |              |

|                  | 010 = CCP2             |                                   |                 |                |                             |                  |              |

|                  | 001 = CCP              | 1                                 |                 |                |                             |                  |              |

|                  | 000 = No A             | uto Conversion                    | Trigger Select  | tion bits      |                             |                  |              |

| bit 3-0          | Unimpleme              | nted: Read as '                   | 0'              |                |                             |                  |              |

| Note 1. Th       | io io o rigina os      | lao oonoitivo inr                 | ut for all cour |                |                             |                  |              |

# REGISTER 16-9: AADCON2: HARDWARE CVD CONTROL REGISTER

**Note 1:** This is a rising edge sensitive input for all sources.

**2:** Signal used to set the corresponding interrupt flag.

| U-0              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                        | U-0                                             | U-0            | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------|----------------|------------------|----------------|--------------|

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            | _                                               | —              | ADCONV           | ADST           | G<1:0>       |

| bit 7            | gend:         Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all         = Bit is set       '0' = Bit is cleared         7-3       Unimplemented: Read as '0'         2       ADCONV: ADC Conversion Status bit         1 = Indicates ADC in Conversion Sequence for AADRES1H:AADRES1L         0 = Indicates ADC in Conversion Sequence for AADRES0H:AADRES0L (Also reads GO/DONE = 0) | bit 0                                                                      |                                                 |                |                  |                |              |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                                                 |                |                  |                |              |

| R = Readal       | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable                                                               | oit                                             | U = Unimpler   | nented bit, read | as '0'         |              |

| u = Bit is ur    | nchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x = Bit is unkn                                                            | own                                             | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is s   | et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | '0' = Bit is clea                                                          | ared                                            |                |                  |                |              |

| bit 2<br>bit 1-0 | ADCONV: AI<br>1 = Indicates<br>0 = Indicates<br>GO/DON                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DC Conversion<br>s ADC in Conve<br>s ADC in Conve<br>$\overline{NE} = 0$ ) | Status bit<br>rsion Sequenc<br>rsion Sequenc    |                |                  |                | 0' when      |

|                  | 11 = ADC n<br>10 = ADC n<br>01 = ADC n                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nodule is in con                                                           | version stage<br>uisition stage<br>charge stage | e as GO/DONE   | = 0)             |                |              |

# REGISTER 16-11: AADSTAT: HARDWARE CVD STATUS REGISTER

## REGISTER 16-12: AADPRE: HARDWARE CVD PRE-CHARGE CONTROL REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| —     |         |         |         | ADPRE<6:0> |         |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | Unimplemented: Read as '0'                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0 | ADPRE<6:0>: Pre-charge Time Select bits <sup>(1)</sup>                                                                         |

|         | 111 1111 = Pre-charge for 127 instruction cycles                                                                               |

|         | 111 1110 = Pre-charge for 126 instruction cycles                                                                               |

|         | •                                                                                                                              |

|         | •                                                                                                                              |

|         | <ul> <li>000 0001 = Pre-charge for 1 instruction cycle (Fosc/4)</li> <li>000 0000 = ADC pre-charge time is disabled</li> </ul> |

**Note 1:** When the FRC clock is selected as the conversion clock source, it is also the clock used for the pre-charge and acquisition times.

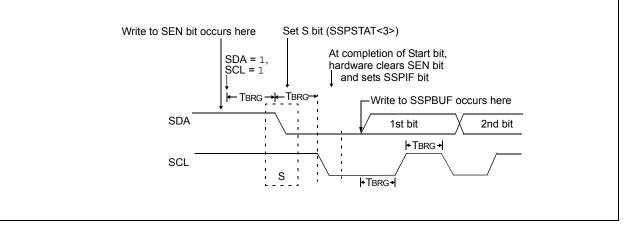

# 20.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN bit of the SSPCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSPSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

# FIGURE 20-26: FIRST START BIT TIMING

## 21.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

## 21.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 21.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

## 21.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| APFCON<br>CCP1CON<br>INTCON | —<br>—<br>GIE | –<br>–<br>PEIE | —<br>DC1B | _                    | _      |        | SSSEL  | CCP2SEL |      |

|-----------------------------|---------------|----------------|-----------|----------------------|--------|--------|--------|---------|------|

|                             | —<br>GIE      |                | DC1B      |                      |        |        | OUGLL  | UUP2SEL | 101  |

| INTCON                      | GIE           | PEIE           |           | DC1B<1:0> CCP1M<3:0> |        |        |        |         |      |

|                             |               |                | TMR0IE    | INTE                 | IOCIE  | TMR0IF | INTF   | IOCIF   | 69   |

| PIE1                        | TMR1GIE       | ADIE           | RCIE      | TXIE                 | SSPIE  | CCP1IE | TMR2IE | TMR1IE  | 70   |

| PIE2                        | OSFIE         | _              |           |                      | BCLIE  | —      | —      | CCP2IE  | 71   |

| PIR1                        | TMR1GIF       | ADIF           | RCIF      | TXIF                 | SSPIF  | CCP1IF | TMR2IF | TMR1IF  | 72   |

| PIR2                        | OSFIF         |                | —         | _                    | BCLIF  | —      | —      | CCP2IF  | 73   |

| PR2                         | Timer2 Perio  | d Register     |           |                      |        |        |        |         | 171* |

| T2CON                       | —             |                | T2OUT     | PS<3:0>              |        | TMR2ON | T2CKP  | S<1:0>  | 173  |

| TMR2                        | Timer2 Modu   | ule Register   |           |                      |        |        |        |         | 171  |

| TRISA                       | TRISA7        | TRISA6         | TRISA5    | TRISA4               | TRISA3 | TRISA2 | TRISA1 | TRISA0  | 103  |

#### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM. \* Page provides register information.

| Name    | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                       | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 249                 |

| INTCON  | GIE                          | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 69                  |

| PIE1    | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 70                  |

| PIR1    | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 72                  |

| RCREG   | EUSART Receive Data Register |        |        |        |        |        |        |        | 242*                |

| RCSTA   | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 248                 |

| SPBRGL  | BRG<7:0>                     |        |        |        |        |        |        |        |                     |

| SPBRGH  | BRG<15:8>                    |        |        |        |        |        |        |        | 250*                |

| TRISC   | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 110                 |

| TXSTA   | CSRC                         | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 247                 |

# TABLE 22-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

#### TABLE 25-4: I/O PORTS (CONTINUED)

| Standaro<br>Param<br>No. | d Operati<br>Sym. | ng Conditions (unless otherwi<br>Characteristic | se stated)<br>Min. | Тур† | Max. | Units | Conditions                                                             |

|--------------------------|-------------------|-------------------------------------------------|--------------------|------|------|-------|------------------------------------------------------------------------|

|                          |                   | Capacitive Loading Specs on                     | Output Pins        |      |      |       |                                                                        |

| D101*                    | COSC2             | OSC2 pin                                        | _                  | _    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |

| D101A*                   | Сю                | All I/O pins                                    | _                  | _    | 50   | pF    |                                                                        |

These parameters are characterized but not tested.

t Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

# 27.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 27.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

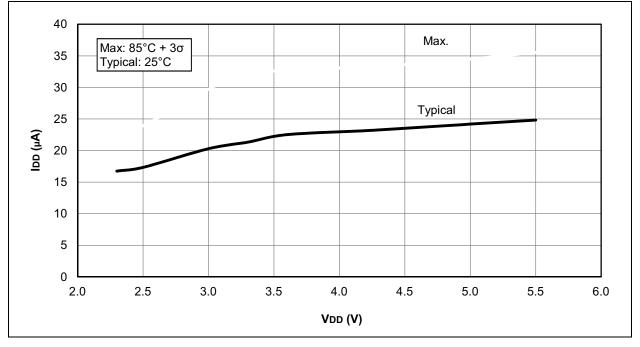

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          |       | INCHES |  |  |  |

|----------------------------|------------------|----------|-------|--------|--|--|--|

| Dimension                  | Dimension Limits |          |       | MAX    |  |  |  |

| Number of Pins             | Ν                | 28       |       |        |  |  |  |

| Pitch                      | е                | .100 BSC |       |        |  |  |  |

| Top to Seating Plane       | Α                | -        | _     | .200   |  |  |  |

| Molded Package Thickness   | A2               | .120     | .135  | .150   |  |  |  |

| Base to Seating Plane      | A1               | .015     | _     | -      |  |  |  |

| Shoulder to Shoulder Width | E                | .290     | .310  | .335   |  |  |  |

| Molded Package Width       | E1               | .240     | .285  | .295   |  |  |  |

| Overall Length             | D                | 1.345    | 1.365 | 1.400  |  |  |  |

| Tip to Seating Plane       | L                | .110     | .130  | .150   |  |  |  |

| Lead Thickness             | С                | .008     | .010  | .015   |  |  |  |

| Upper Lead Width           | b1               | .040     | .050  | .070   |  |  |  |

| Lower Lead Width           | b                | .014     | .018  | .022   |  |  |  |

| Overall Row Spacing §      | eВ               | -        | _     | .430   |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B