Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1512-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Secondary oscillator 32 kHz crystal

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

## 5.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 18.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

## 6.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

## REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | -   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

| Legend:                         |                                       |                                                                            |                                                                 |  |  |  |

|---------------------------------|---------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|

| HC = Bit is cleared by hardware |                                       |                                                                            | HS = Bit is set by hardware                                     |  |  |  |

| R = Readable                    | bit                                   | W = Writable bit                                                           | U = Unimplemented bit, read as '0'                              |  |  |  |

| u = Bit is unch                 | anged                                 | x = Bit is unknown                                                         | -m/n = Value at POR and BOR/Value at all other Resets           |  |  |  |

| '1' = Bit is set                |                                       | '0' = Bit is cleared                                                       | q = Value depends on condition                                  |  |  |  |

| bit 7                           | STKOVE. St                            | ack Overflow Eleg bit                                                      |                                                                 |  |  |  |

| DIL 7                           |                                       | ack Overflow Flag bit<br>Overflow occurred                                 |                                                                 |  |  |  |

|                                 |                                       | Overflow has not occurred                                                  | or cleared by firmware                                          |  |  |  |

| bit 6                           |                                       | ack Underflow Flag bit                                                     |                                                                 |  |  |  |

|                                 |                                       | Underflow occurred                                                         |                                                                 |  |  |  |

|                                 | 0 = A Stack                           | Underflow has not occurred                                                 | d or cleared by firmware                                        |  |  |  |

| bit 5                           | Unimplemen                            | ted: Read as '0'                                                           |                                                                 |  |  |  |

| bit 4                           | RWDT: Watc                            | hdog Timer Reset Flag bit                                                  |                                                                 |  |  |  |

| 1 = A Watche                    |                                       | log Timer Reset has not occurred or set to '1' by firmware                 |                                                                 |  |  |  |

|                                 | 0 = A Watchdog Timer Reset has occurr |                                                                            | red (cleared by hardware)                                       |  |  |  |

| bit 3                           |                                       | LR Reset Flag bit                                                          |                                                                 |  |  |  |

|                                 |                                       | Reset has not occurred or                                                  |                                                                 |  |  |  |

| h:# 0                           |                                       | · ·                                                                        | '0' in hardware when a MCLR Reset occurs)                       |  |  |  |

| bit 2                           |                                       | struction Flag bit                                                         |                                                                 |  |  |  |

|                                 |                                       |                                                                            | xecuted or set to '1' by firmware<br>uted (cleared by hardware) |  |  |  |

| bit 1                           |                                       | -on Reset Status bit                                                       |                                                                 |  |  |  |

| 1 = No Power-on Reset occurred  |                                       |                                                                            |                                                                 |  |  |  |

|                                 |                                       | -on Reset occurred (must be set in software after a Power-on Reset occurs) |                                                                 |  |  |  |

| bit 0                           |                                       |                                                                            |                                                                 |  |  |  |

|                                 | 1 = No Brow                           | n-out Reset occurred                                                       |                                                                 |  |  |  |

|                                 | 0 = A Brown-<br>occurs)               | out Reset occurred (must l                                                 | be set in software after a Power-on Reset or Brown-out Rese     |  |  |  |

## 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- · Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

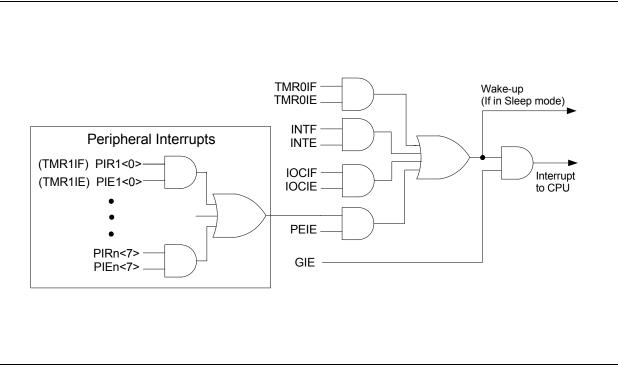

A block diagram of the interrupt logic is shown in Figure 7-1.

## FIGURE 7-1: INTERRUPT LOGIC

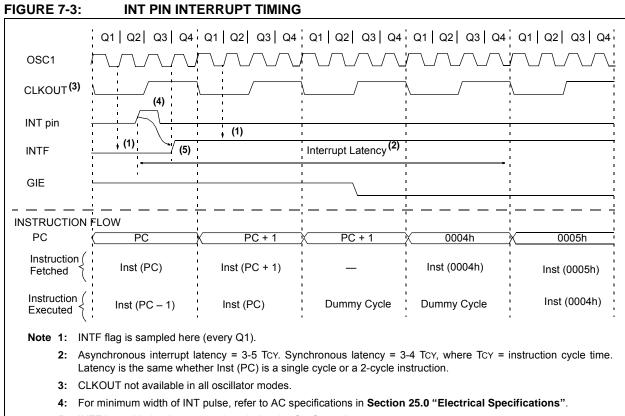

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### EXAMPLE 11-3: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. 64 bytes of data are loaded, starting at the address in DATA\_ADDR ; 2. Each word of data to be written is made up of two adjacent bytes in DATA\_ADDR, ; stored in little endian format ; 3. A valid starting address (the least significant bits = 00000) is loaded in ADDRH: ADDRL ; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM) ; BCF INTCON,GIE ; Disable ints so required sequences will execute properly ; Bank 3 BANKSEL PMADRH MOVF ADDRH,W ; Load initial address MOVWF PMADRH MOVF ADDRL,W MOVWF PMADRL LOW DATA\_ADDR ; Load initial data address MOVLW MOVWF FSROL ; MOVLW HIGH DATA\_ADDR ; Load initial data address MOVWF FSR0H ; PMCON1,CFGS ; Not configuration space BCF BSF PMCON1,WREN ; Enable writes PMCON1,LWLO ; Only Load Write Latches BSF LOOP MOVIW FSR0++ ; Load first data byte into lower MOVWF PMDATT. ; ; Load second data byte into upper MOVIW FSR0++ MOVWF PMDATH MOVF ; Check if lower bits of address are '00000' PMADRL,W ; Check if we're on the last of 32 addresses XORLW 0x1F ANDLW 0x1F BTFSC STATUS,Z ; Exit if last of 32 words, GOTO START\_WRITE ; MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh MOVWF PMCON2 ; Write AAh BSF ; Set WR bit to begin write PMCON1,WR NOP ; NOP instructions are forced as processor ; loads program memory write latches NOP INCF PMADRL, F ; Still loading latches Increment address GOTO LOOP ; Write next latches START\_WRITE BCF PMCON1,LWLO ; No more loading latches - Actually start Flash program ; memory write MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh ; MOVWF PMCON2 ; Write AAh BSF PMCON1,WR ; Set WR bit to begin write NOP ; NOP instructions are forced as processor writes ; all the program memory write latches simultaneously NOP ; to program memory. ; After NOPs, the processor ; stalls until the self-write process in complete ; after write processor continues with 3rd instruction PMCON1,WREN BCF ; Disable writes BSF INTCON,GIE ; Enable interrupts

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELB | —      |        | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 104                 |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 69                  |

| IOCBF  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 117                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 117                 |

| IOCBP  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 117                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 103                 |

## TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

## 16.3 ADC Register Definitions

The following registers are used to control the operation of the ADC.

### REGISTER 16-1: ADCON0: A/D CONTROL REGISTER 0

| U-0             | R/W-0/0                                                                                                                             | R/W-0/0                              | R/W-0/0                                                                                                              | R/W-0/0                                   | R/W-0/0           | R/W-0/0            | R/W-0/0 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------|--------------------|---------|

| —               |                                                                                                                                     |                                      | CHS<4:0>                                                                                                             |                                           |                   | GO/DONE            | ADON    |

| pit 7           |                                                                                                                                     |                                      |                                                                                                                      |                                           |                   |                    | bit     |

| _egend:         |                                                                                                                                     |                                      |                                                                                                                      |                                           |                   |                    |         |

| R = Readable    | bit                                                                                                                                 | W = Writable bi                      | ł                                                                                                                    | II = Unimpleme                            | ented bit, read a | us 'Ω'             |         |

|                 |                                                                                                                                     | x = Bit is unkno                     |                                                                                                                      | •                                         |                   | Value at all other | Ponoto  |

| u = Bit is unch | angeu                                                                                                                               |                                      |                                                                                                                      |                                           | FOR and BOR       | value at all other | Resels  |

| 1' = Bit is set |                                                                                                                                     | '0' = Bit is clear                   | ea                                                                                                                   |                                           |                   |                    |         |

| oit 7           | Unimplemente                                                                                                                        | ed: Read as '0'                      |                                                                                                                      |                                           |                   |                    |         |

| bit 6-2         | 11111 = FVR<br>11110 = Rese<br>11101 = Temp<br>11100 = Rese<br>11011 = VREF<br>11010 = VREF<br>11001 = Rese                         | 8                                    | eference) Buffe<br>el connected.<br>(2)<br>el connected.<br>Reference)<br>Reference) <sup>(3)</sup><br>el connected. | er 1 Output <sup>(1)</sup>                |                   |                    |         |

|                 | 10000 = AN1<br>01111 = AN1<br>01100 = AN1<br>01101 = AN1<br>01100 = AN1<br>01011 = AN1<br>01010 = AN1<br>01001 = AN9<br>01000 = AN8 | 6<br>5<br>4<br>3<br>2<br>1<br>0      |                                                                                                                      |                                           |                   |                    |         |

|                 | 00110 = Rese                                                                                                                        | erved. No channe<br>erved. No channe | l connected.                                                                                                         |                                           |                   |                    |         |

| bit 1           | 1 = A/D conver<br>This bit is a                                                                                                     |                                      | gress. Setting to<br>red by hardwar                                                                                  | nis bit starts an A/<br>re when the A/D c |                   |                    |         |

| oit 0           | <b>ADON:</b> ADC E<br>1 = ADC is ena<br>0 = ADC is disa                                                                             | abled                                |                                                                                                                      |                                           |                   |                    |         |

3: Conversion results for the VREFH selection may contain errors due to noise.

## 20.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

## 20.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

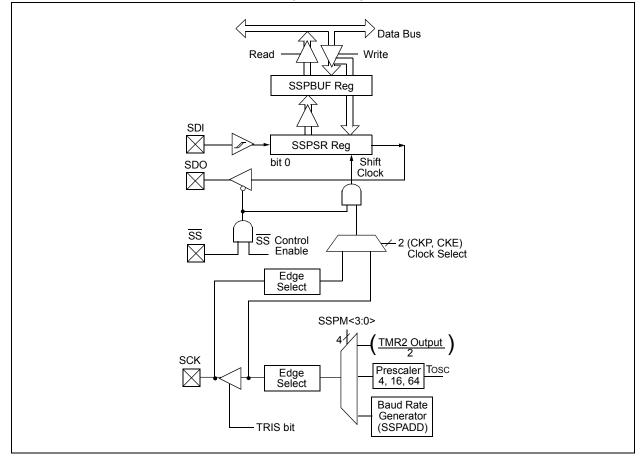

Figure 20-1 is a block diagram of the SPI interface module.

### FIGURE 20-1: MSSP BLOCK DIAGRAM (SPI MODE)

### 20.6.10 SLEEP OPERATION

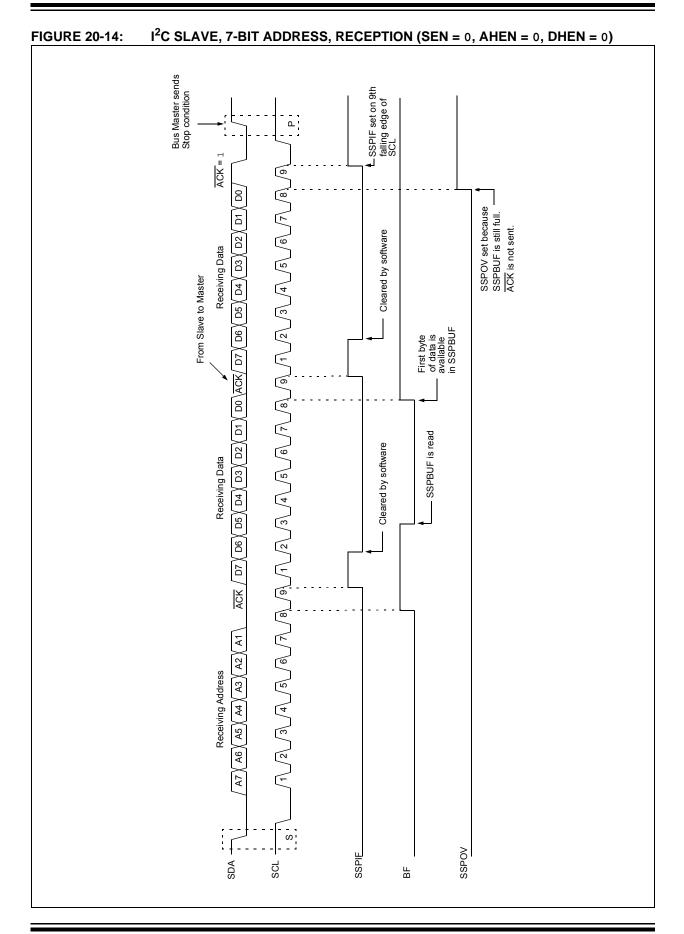

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

### 20.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

## 20.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

### 20.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

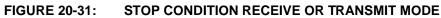

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the I<sup>2</sup>C port to its Idle state (Figure 20-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

## 22.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 22-4 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 22.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 22-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 22.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note 1:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

### 22.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 22.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 22.5.1.2 "Clock Polarity"**.

### 22.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

## 22.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPx-BRGL register pair. The overflow condition will set the RCIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RCREG is read after the overflow occurs but before the fifth rising edge then the fifth rising edge will set the RCIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared then those will be falsely detected as start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCREG to clear RCIF.

- 2. If RCIDL is zero then wait for RCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

### 22.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 22-7), and asynchronously if the device is in Sleep mode (Figure 22-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

## 22.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

## 24.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 24-1 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of four oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 24.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 24-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| n     | FSR or INDF number. (0-1)                                                                                                                                                         |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                       |

### TABLE 24-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-out bit    |

| С     | Carry bit       |

| DC    | Digit carry bit |

| Z     | Zero bit        |

| PD    | Power-down bit  |

| ΜΟΥΨΙ      | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                   |

| Operands:  | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                        |

| Operation: | $\label{eq:states} \begin{array}{l} W \rightarrow INDFn \\ Effective \ address \ is \ determined \ by \\ \bullet \ FSR + 1 \ (preincrement) \\ \bullet \ FSR + 1 \ (predecrement) \\ \bullet \ FSR + k \ (relative \ offset) \\ After \ the \ Move, \ the \ FSR \ value \ will \ be \\ either: \\ \bullet \ FSR + 1 \ (all \ increments) \\ \bullet \ FSR + 1 \ (all \ increments) \\ Unchanged \\ \end{array}$ |

Status Affected:

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

None

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                            |

| Operands:        | None                                                                                                      |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to<br>OPTION_REG register.                                                      |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | OPTION                                                                                                    |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| RESET            | Software Reset                                                                 |

|------------------|--------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                  |

| Operands:        | None                                                                           |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.           |

| Status Affected: | None                                                                           |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |

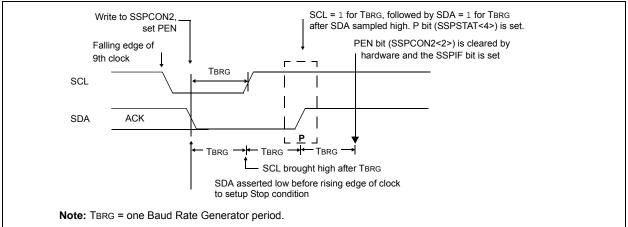

#### **FIGURE 25-3:** POR AND POR REARM WITH SLOW RISING VDD

VDD (V)

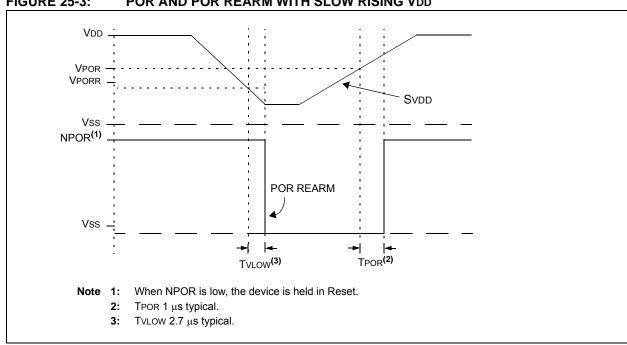

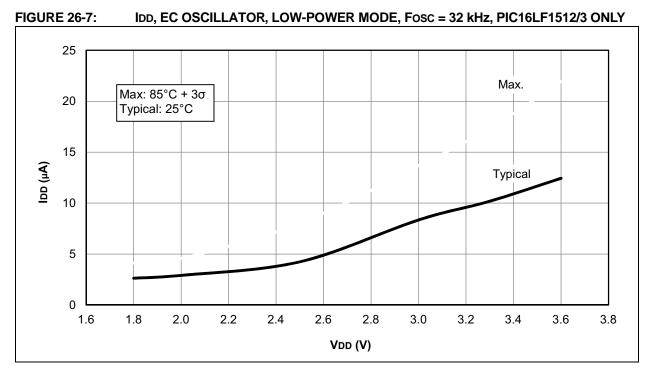

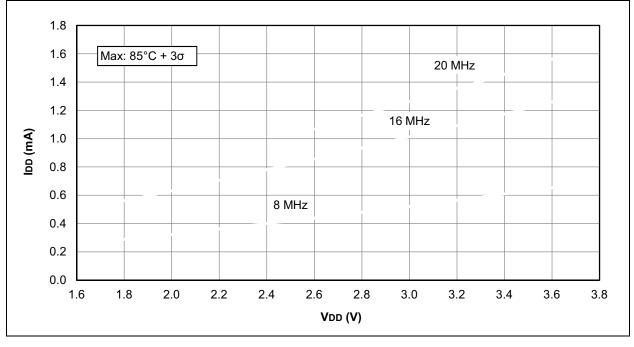

FIGURE 26-8: IDD EC OSCILLATOR, LOW-POWER MODE, Fosc = 32 kHz, PIC16F1512/3 ONLY

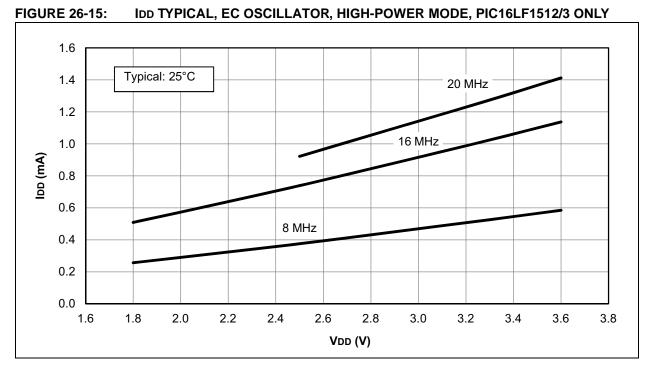

FIGURE 26-16: IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC16LF1512/3 ONLY

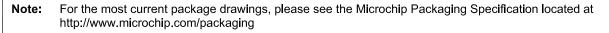

28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 4x4 mm Body [UQFN] With 0.40 mm Contact Length

| Units                      |    | MILLIMETERS |          |      |

|----------------------------|----|-------------|----------|------|

| Dimension Limits           |    | MIN         | NOM      | MAX  |

| Contact Pitch              | E  |             | 0.40 BSC |      |

| Optional Center Pad Width  | W2 |             |          | 2.35 |

| Optional Center Pad Length | T2 |             |          | 2.35 |

| Contact Pad Spacing        | C1 |             | 4.00     |      |

| Contact Pad Spacing        | C2 |             | 4.00     |      |

| Contact Pad Width (X28)    | X1 |             |          | 0.20 |

| Contact Pad Length (X28)   | Y1 |             |          | 0.80 |

| Distance Between Pads      | G  | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2152A

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - X /XX XXX<br>T Tape and Reel Temperature Package Patter                                            | Examples:<br>a) PIC16F1512T - I/SO 301                                                                                                                                                                                           |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                          | Option Range                                                                                                            | <br>Tape and Reel,<br>Industrial temperature,<br>SOIC package<br>b) PIC16F1512 - I/P                                                                                                                                             |  |

| Device:                  | PIC16F1512, PIC16LF1512<br>PIC16F1513, PIC16LF1513                                                                      | Industrial temperature<br>PDIP package<br>c) PIC16F1513 - E/SS                                                                                                                                                                   |  |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                           | Extended temperature,<br>SSOP package                                                                                                                                                                                            |  |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)               |                                                                                                                                                                                                                                  |  |

| Package:                 | MV = Micro Lead Frame (UQFN) 4x4<br>P = Plastic DIP (PDIP)<br>SO = SOIC<br>SP = Skinny Plastic DIP (SPDIP)<br>SS = SSOP | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package |  |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                               | availability with the Tape and Reel option.                                                                                                                                                                                      |  |