#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1512-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-6:PIC16(L)F1512/3 MEMORYMAP (BANK 14)

|              | Bank 14                               |

|--------------|---------------------------------------|

| 700h         | Core Registers<br>(Table 3-2)         |

| 70Bh         |                                       |

| 70Ch<br>710h | Unimplemented<br>Read as '0'          |

| 710n<br>711h | AADCON0                               |

| 711n<br>712h | AADCON1                               |

|              | AADCON1<br>AADCON2                    |

| 713h         | AADCON2<br>AADCON3                    |

| 714h<br>715h | AADSTAT                               |

| -            | AADPRE                                |

| 716h         | AADACQ                                |

| 717h<br>718h | AADAOQ                                |

|              | AADCAP                                |

| 719h<br>71Ah |                                       |

|              | AADRESOL                              |

| 71Bh         | AADRES0H                              |

| 71Ch         | AADRES1L                              |

| 71Dh         | AADRES1H                              |

| 71Eh         |                                       |

| 71Fh         |                                       |

| 720h<br>76Fh | Unimplemented<br>Read as '0'          |

| 770h         |                                       |

| 77Fh         | Common RAM<br>(Accesses<br>70h – 7Fh) |

|              |                                       |

### TABLE 3-7:PIC16(L)F1512/3 MEMORYMAP (BANK 31)

|              | Bank 31                               |

|--------------|---------------------------------------|

| F80h<br>F8Bh | Core Registers<br>(Table 3-2)         |

| F8Ch         | Unimplemented<br>Read as '0'          |

| FE3h         |                                       |

| FE4h         | STATUS_SHAD                           |

| FE5h         | WREG_SHAD                             |

| FE6h         | BSR_SHAD                              |

| FE7h         | PCLATH_SHAD                           |

| FE8h         | FSR0L_SHAD                            |

| FE9h         | FSR0H_SHAD                            |

| FEAh         | FSR1L_SHAD                            |

| FEBh         | FSR1H_SHAD                            |

| FECh         | _                                     |

| FEDh         | STKPTR                                |

| FEEh         | TOSL                                  |

| FEFh         | TOSH                                  |

| FF0h<br>FFFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

|              |                                       |

Legend: = Unimplemented data memory locations, read as '0'.

Legend: = Unimplemented data memory locations, read as '0'.

### 7.6.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 7-2.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| R/W-0/0          | R/W-0/0                                  | R/W-0/0                           | R/W-0/0          | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |

|------------------|------------------------------------------|-----------------------------------|------------------|-----------------|------------------|------------------|-------------|--|--|--|--|

| TMR1GIE          | ADIE                                     | RCIE                              | TXIE             | SSPIE           | CCP1IE           | TMR2IE           | TMR1IE      |  |  |  |  |

| bit 7            | •                                        | •                                 |                  |                 |                  |                  | bit (       |  |  |  |  |

|                  |                                          |                                   |                  |                 |                  |                  |             |  |  |  |  |

| Legend:          |                                          |                                   |                  |                 |                  |                  |             |  |  |  |  |

| R = Readable     |                                          | W = Writable                      |                  | •               | nented bit, read |                  |             |  |  |  |  |

| u = Bit is uncl  | •                                        | x = Bit is unki                   |                  | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is set |                                          | '0' = Bit is cle                  | ared             |                 |                  |                  |             |  |  |  |  |

| bit 7            |                                          | imer1 Gate Inte                   | rrunt Enable k   | sit             |                  |                  |             |  |  |  |  |

|                  |                                          | the Timer1 Gate Inte              | •                |                 |                  |                  |             |  |  |  |  |

|                  |                                          | the Timer1 Gat                    | •                | •               |                  |                  |             |  |  |  |  |

| bit 6            | ADIE: A/D C                              | onverter (ADC)                    | Interrupt Enal   | ble bit         |                  |                  |             |  |  |  |  |

|                  | 1 = Enables the ADC interrupt            |                                   |                  |                 |                  |                  |             |  |  |  |  |

|                  |                                          | the ADC interre                   | •                |                 |                  |                  |             |  |  |  |  |

| bit 5            | RCIE: USART Receive Interrupt Enable bit |                                   |                  |                 |                  |                  |             |  |  |  |  |

|                  |                                          | the USART rec<br>the USART rec    |                  |                 |                  |                  |             |  |  |  |  |

| bit 4            |                                          | T Transmit Inte                   | •                | i+              |                  |                  |             |  |  |  |  |

|                  |                                          | the USART trans                   | •                |                 |                  |                  |             |  |  |  |  |

|                  |                                          | the USART tra                     |                  |                 |                  |                  |             |  |  |  |  |

| bit 3            | SSPIE: Syno                              | chronous Serial                   | Port (MSSP)      | Interrupt Enabl | e bit            |                  |             |  |  |  |  |

|                  |                                          | the MSSP inter                    |                  |                 |                  |                  |             |  |  |  |  |

|                  |                                          | the MSSP inte                     | •                |                 |                  |                  |             |  |  |  |  |

| bit 2            |                                          | CCP1IE: CCP1 Interrupt Enable bit |                  |                 |                  |                  |             |  |  |  |  |

|                  |                                          | the CCP1 inter<br>the CCP1 inter  | •                |                 |                  |                  |             |  |  |  |  |

| bit 1            |                                          | IR2 to PR2 Mat                    | •                | able bit        |                  |                  |             |  |  |  |  |

|                  |                                          | the Timer2 to P                   |                  |                 |                  |                  |             |  |  |  |  |

|                  |                                          | the Timer2 to F                   |                  |                 |                  |                  |             |  |  |  |  |

| bit 0            | TMR1IE: Tin                              | ner1 Overflow Ir                  | nterrupt Enable  | e bit           |                  |                  |             |  |  |  |  |

|                  | 1 = Enables                              | the Timer1 ove                    | rflow interrupt  |                 |                  |                  |             |  |  |  |  |

|                  | ∩ = Disables                             | the Timer1 ove                    | rflow interruint |                 |                  |                  |             |  |  |  |  |

### 16.2 ADC Operation

### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the same instruction that turns on the ADC. |

|-------|----------------------------------------------------------------------------------|

|       |                                                                                  |

|       | Refer to Section 16.2.6 "A/D Conver-                                             |

|       | sion Procedure".                                                                 |

### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger allows periodic ADC measurements without software intervention, using the TRIGSEL bits of the AADCON2 register. When this trigger occurs, the GO/DONE bit is set by hardware from one of the following sources:

- CCP1

- CCP2

- Timer0 Overflow

- · Timer1 Overflow

- Timer2 Match to PR2

### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device          | Source                       |

|-----------------|------------------------------|

| PIC16(L)F1512/3 | CCP1, CCP2, TMR0, TMR1, TMR2 |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 21.0 "Capture/Compare/PWM Modules", Section 17.0 "Timer0 Module", Section 18.0 "Timer1 Module with Gate Control", and Section 19.0 "Timer2 Module" for more information.

| REGISTER         |                                                                                           | R/W-0/0                                                                                          | R/W-0/0          | U-0                  | U-0              | R/W-0/0            | R/W-0/0      |

|------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------|----------------------|------------------|--------------------|--------------|

| ADFM             | N/W-0/0                                                                                   | ADCS<2:0>                                                                                        | R/W-0/U          | 0-0                  | 0-0              |                    | EF<1:0>      |

| bit 7            |                                                                                           | AD00 \2.02                                                                                       |                  |                      |                  |                    | bit C        |

|                  |                                                                                           |                                                                                                  |                  |                      |                  |                    |              |

| Legend:          |                                                                                           |                                                                                                  |                  |                      |                  |                    |              |

| R = Readab       | ole bit                                                                                   | W = Writable bit                                                                                 |                  | U = Unimpler         | nented bit, read | d as '0'           |              |

| u = Bit is un    | changed                                                                                   | x = Bit is unknow                                                                                | wn               | -n/n = Value a       | at POR and BC    | R/Value at all     | other Resets |

| '1' = Bit is s   | et                                                                                        | '0' = Bit is cleare                                                                              | ed               |                      |                  |                    |              |

| bit 7<br>bit 6-4 | 1 = Right-ju<br>loaded<br>0 = Left-jus<br>loaded<br>ADCS<2:0:<br>000 = FOS(<br>001 = FOS( | stified. Six Least Si<br>/2<br>/8                                                                | ignificant bi    | ts of ADRESL a       |                  |                    |              |

|                  | 100 = Fos<br>101 = Fos<br>110 = Fos                                                       | (clock supplied from<br>c/4<br>c/16                                                              |                  |                      |                  |                    |              |

| bit 3-2          | Unimpleme                                                                                 | ented: Read as '0'                                                                               |                  |                      |                  |                    |              |

| bit 1-0          | 00 = VREF<br>01 = Reser<br>10 = VREF                                                      | :0>: A/D Positive \<br>is connected to Vol<br>ved<br>is connected to ext<br>is connected to inte | o<br>ernal VREF+ | - pin <sup>(1)</sup> |                  | ule <sup>(1)</sup> |              |

|                  |                                                                                           | the FVR or the VRE<br>e specification exist                                                      |                  |                      |                  |                    |              |

### REGISTER 16-2: ADCON1: A/D CONTROL REGISTER 1

### 16.5 Hardware Capacitive Voltage Divider (CVD) Module

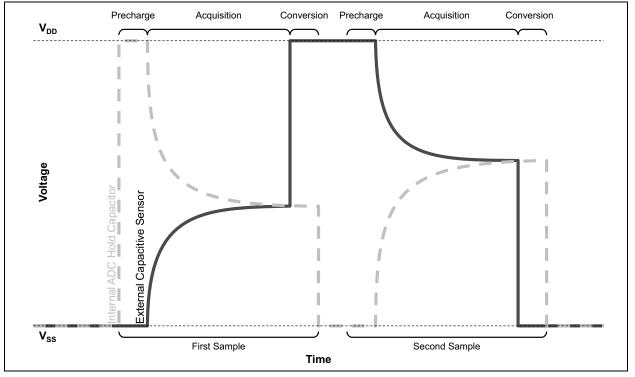

The hardware Capacitive Voltage Divider (CVD) module is a peripheral which allows the user to perform a relative capacitance measurement on any ADC channel using the internal ADC sample and hold capacitance as a reference. This relative capacitance measurement can be used to implement capacitive touch or proximity sensing applications.

The CVD operation begins with the ADC's internal sample and hold capacitor (CHOLD) being disconnected from the path which connects it to the external capacitive sensor node. While disconnected, CHOLD is pre-charged to VDD or VSS while the path to the sensor node is also discharged to VDD or VSS - typically this node is discharged to the level opposite that of CHOLD. When the pre-charge phase is complete, the VDD/Vss bias paths for the two nodes are shut off and CHOLD and the path to the external sensor node are re-connected, at which time the acquisition phase of the CVD operation begins. During acquisition, a capacitive voltage divider is formed between the pre-charged CHOLD and sensor nodes which results in a final voltage level settling on CHOLD which is determined by the capacitances and pre-charge levels of the two nodes involved. After acquisition, the ADC converts the voltage level held on CHOLD. This process is then usually repeated with the selected pre-charge

levels for both the CHOLD and sensor nodes inverted. Figure 16-6 shows the waveform for two inverted CVD measurements, which is also known is differential CVD measurement.

In a typical application, an Analog-to-Digital Converter (ADC) channel is attached to a pad on a Printed Circuit Board (PCB), which is electrically isolated from the end user. A capacitive change is detected on the ADC channel using the CVD conversion method when the end user places a finger over the PCB pad, the developer then can implement software to detect a touch or proximity event or change. Key features of this module include:

- · Automated double sample conversions

- · Two result registers

- · Inversion of second sample

- 7-bit pre-charge timer

- 7-bit acquisition timer

- · Two guard ring output drives

- · Adjustable sample and hold capacitor array

Note: For more information on capacitive voltage divider sensing method refer to the Application Note *AN1478, mTouch<sup>™</sup>* Sensing Solution Acquisition Methods Capacitive Voltage Divider (DS01478).

### FIGURE 16-6: DIFFERENTIAL CVD MEASUREMENT WAVEFORM

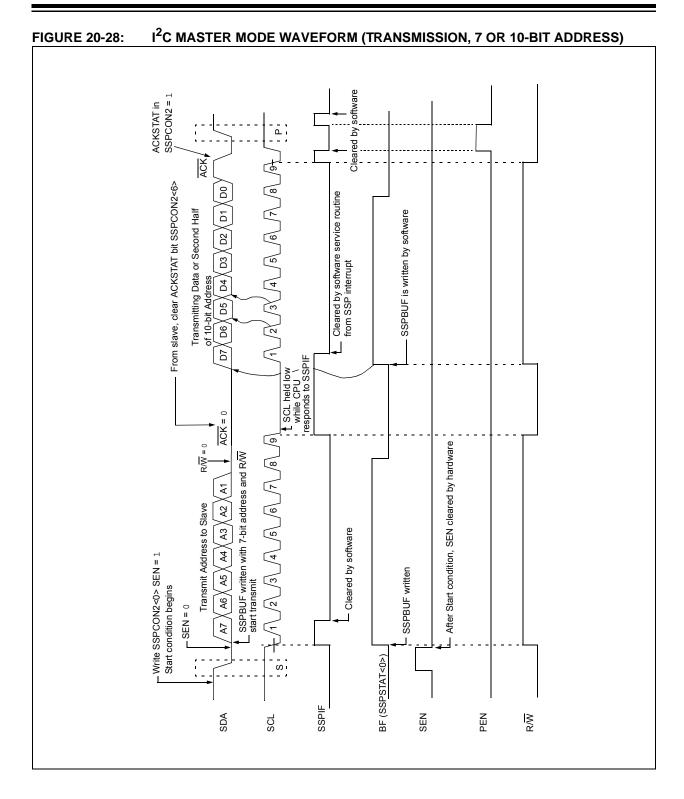

### 20.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overrightarrow{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCL on the bus, the ACKTIM bit of the SSPCON3 register is set. The ACKTIM bit indicates the Acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

### 20.5 I<sup>2</sup>C SLAVE MODE OPERATION

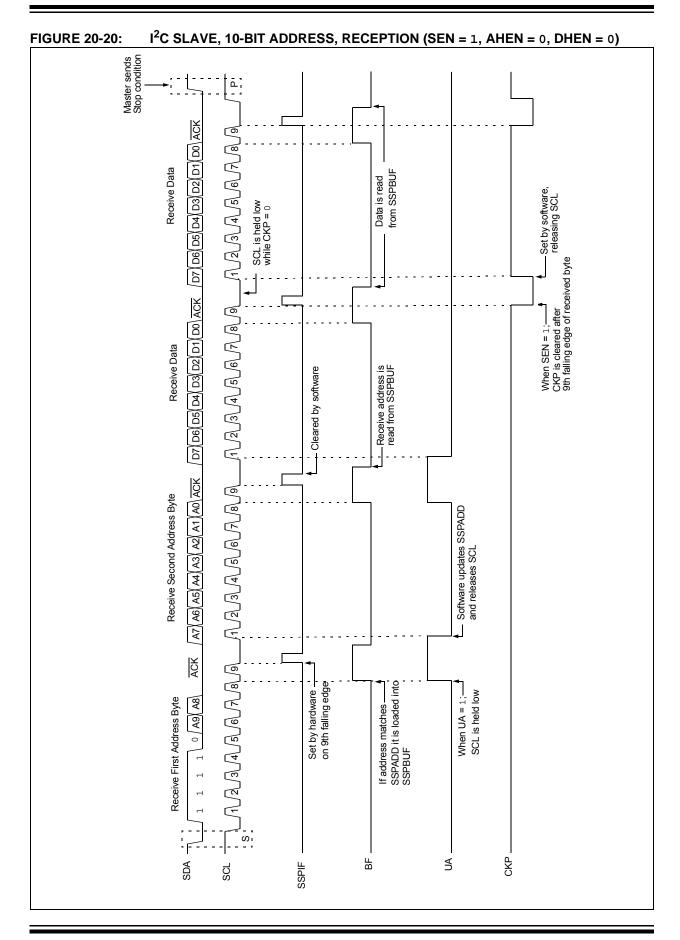

The MSSP Slave mode operates in one of four modes selected in the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPIF additionally getting set upon detection of a Start, Restart, or Stop condition.

### 20.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 20-7) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes Idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 20-6) affects the address matching process. See **Section 20.5.9** "**SSP Mask Register**" for more information.

### 20.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

### 20.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

| Name    | Bit 7      | Bit 6           | Bit 5          | Bit 4          | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|------------|-----------------|----------------|----------------|--------|--------|--------|--------|----------------------------|

| INTCON  | GIE        | PEIE            | TMR0IE         | INTE           | IOCIE  | TMR0IF | INTF   | IOCIF  | 69                         |

| PIE1    | TMR1GIE    | ADIE            | RCIE           | TXIE           | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 70                         |

| PIE2    | OSFIE      | _               | _              | _              | BCLIE  | —      | _      | CCP2IE | 71                         |

| PIR1    | TMR1GIF    | ADIF            | RCIF           | TXIF           | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 72                         |

| PIR2    | OSFIF      | _               | _              | _              | BCLIF  | —      | _      | CCP2IF | 73                         |

| SSPADD  |            |                 |                | ADD<           | :7:0>  |        |        |        | 227                        |

| SSPBUF  | Synchronou | s Serial Port F | Receive Buffer | r/Transmit Reg | gister |        |        |        | 179*                       |

| SSPCON1 | WCOL       | SSPOV           | SSPEN          | CKP            |        | SSPM   | <3:0>  |        | 224                        |

| SSPCON2 | GCEN       | ACKSTAT         | ACKDT          | ACKEN          | RCEN   | PEN    | RSEN   | SEN    | 225                        |

| SSPCON3 | ACKTIM     | PCIE            | SCIE           | BOEN           | SDAHT  | SBCDE  | AHEN   | DHEN   | 226                        |

| SSPMSK  | MSK7       | MSK6            | MSK5           | MSK4           | MSK3   | MSK2   | MSK1   | MSK0   | 227                        |

| SSPSTAT | SMP        | CKE             | D/A            | Р              | S      | R/W    | UA     | BF     | 223                        |

| TRISA   | TRISA7     | TRISA6          | TRISA5         | TRISA4         | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 103                        |

### TABLE 20-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in I<sup>2</sup>C mode. \*

Page provides register information.

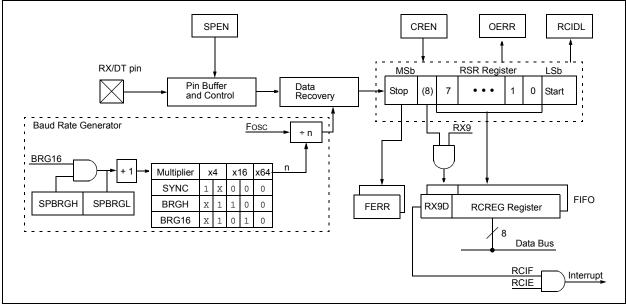

### FIGURE 22-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

### 22.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

### 22.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

### 22.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 22.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |                   |                             |                |            |                             |                    |            |                             |  |  |

|--------|-------------------|-------------------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 20.000 MHz |                               |                             | Fosc           | Fosc = 18.432 MHz |                             |                | : = 16.00  | 0 MHz                       | Fosc = 11.0592 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | _                 | _                             | _                           |                |                   | _                           |                | _          | _                           |                    | _          | _                           |  |  |

| 1200   | 1221              | 1.73                          | 255                         | 1200           | 0.00              | 239                         | 1202           | 0.16       | 207                         | 1200               | 0.00       | 143                         |  |  |

| 2400   | 2404              | 0.16                          | 129                         | 2400           | 0.00              | 119                         | 2404           | 0.16       | 103                         | 2400               | 0.00       | 71                          |  |  |

| 9600   | 9470              | -1.36                         | 32                          | 9600           | 0.00              | 29                          | 9615           | 0.16       | 25                          | 9600               | 0.00       | 17                          |  |  |

| 10417  | 10417             | 0.00                          | 29                          | 10286          | -1.26             | 27                          | 10417          | 0.00       | 23                          | 10165              | -2.42      | 16                          |  |  |

| 19.2k  | 19.53k            | 1.73                          | 15                          | 19.20k         | 0.00              | 14                          | 19.23k         | 0.16       | 12                          | 19.20k             | 0.00       | 8                           |  |  |

| 57.6k  | —                 | _                             | _                           | 57.60k         | 0.00              | 7                           | —              | _          | _                           | 57.60k             | 0.00       | 2                           |  |  |

| 115.2k | —                 | _                             | —                           | _              | _                 | —                           | _              |            | —                           | —                  | _          | —                           |  |  |

### TABLE 22-4: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |  |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | _                | _                             | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |  |  |  |

| 1200   | 1202             | 0.16                          | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |  |  |  |

| 2400   | 2404             | 0.16                          | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | _                | _          | _                           |  |  |  |

| 9600   | 9615             | 0.16                          | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | _                | _          | _                           |  |  |  |

| 10417  | 10417            | 0.00                          | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | —                | _          | _                           |  |  |  |

| 19.2k  | —                | _                             | _                           | —                | _          | _                           | 19.20k            | 0.00       | 2                           | —                | _          | _                           |  |  |  |

| 57.6k  | —                | _                             | —                           | —                | _          | —                           | 57.60k            | 0.00       | 0                           | —                | _          | —                           |  |  |  |

| 115.2k | —                | _                             | _                           | —                | _          | _                           | —                 | _          | _                           | —                | _          | —                           |  |  |  |

|        |                | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                |                    |                             |  |  |

|--------|----------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|--|

| BAUD   | Fosc           | = 20.00                       | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |            |                             | Fosc           | Fosc = 11.0592 MHz |                             |  |  |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |  |

| 300    | —              | _                             | _                           |                   | _          | _                           |                   |            | _                           | _              | —                  | —                           |  |  |

| 1200   | —              | —                             | —                           | —                 | —          | —                           | —                 | —          | —                           | —              | —                  | —                           |  |  |

| 2400   | —              | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | —              | _                  | _                           |  |  |

| 9600   | 9615           | 0.16                          | 129                         | 9600              | 0.00       | 119                         | 9615              | 0.16       | 103                         | 9600           | 0.00               | 71                          |  |  |

| 10417  | 10417          | 0.00                          | 119                         | 10378             | -0.37      | 110                         | 10417             | 0.00       | 95                          | 10473          | 0.53               | 65                          |  |  |

| 19.2k  | 19.23k         | 0.16                          | 64                          | 19.20k            | 0.00       | 59                          | 19.23k            | 0.16       | 51                          | 19.20k         | 0.00               | 35                          |  |  |

| 57.6k  | 56.82k         | -1.36                         | 21                          | 57.60k            | 0.00       | 19                          | 58.82k            | 2.12       | 16                          | 57.60k         | 0.00               | 11                          |  |  |

| 115.2k | 113.64k        | -1.36                         | 10                          | 115.2k            | 0.00       | 9                           | 111.1k            | -3.55      | 8                           | 115.2k         | 0.00               | 5                           |  |  |

| Mnen     | nonic, | Description Cycl                                           | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|----------|--------|------------------------------------------------------------|--------|---------------|------|------|------|----------|-------|

| Operands |        | Description                                                |        | MSb           |      |      | LSb  | Affected | Notes |

|          |        | CONTROL OPERA                                              | TIONS  |               |      |      |      |          |       |

| BRA      | k      | Relative Branch                                            | 2      | 11            | 001k | kkkk | kkkk |          |       |

| BRW      | -      | Relative Branch with W                                     | 2      | 00            | 0000 | 0000 | 1011 |          |       |

| CALL     | k      | Call Subroutine                                            | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CALLW    | -      | Call Subroutine with W                                     | 2      | 00            | 0000 | 0000 | 1010 |          |       |

| GOTO     | k      | Go to address                                              | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| RETFIE   | k      | Return from interrupt                                      | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW    | k      | Return with literal in W                                   | 2      | 11            | 0100 | kkkk | kkkk |          |       |

| RETURN   | -      | Return from Subroutine                                     | 2      | 00            | 0000 | 0000 | 1000 |          |       |

|          |        | INHERENT OPERA                                             | TIONS  |               |      |      |      |          |       |

| CLRWDT   | _      | Clear Watchdog Timer                                       | 1      | 00            | 0000 | 0110 | 0100 | TO, PD   |       |

| NOP      | -      | No Operation                                               | 1      | 00            | 0000 | 0000 | 0000 |          |       |

| OPTION   | -      | Load OPTION_REG register with W                            | 1      | 00            | 0000 | 0110 | 0010 |          |       |

| RESET    | -      | Software device Reset                                      | 1      | 00            | 0000 | 0000 | 0001 |          |       |

| SLEEP    | -      | Go into Standby mode                                       | 1      | 00            | 0000 | 0110 | 0011 | TO, PD   |       |

| TRIS     | f      | Load TRIS register with W                                  | 1      | 00            | 0000 | 0110 | Offf |          |       |

|          |        | C-COMPILER OPT                                             | IMIZED |               |      |      |      |          |       |

| ADDFSR   | n, k   | Add Literal k to FSRn                                      | 1      | 11            | 0001 | 0nkk | kkkk |          |       |

| MOVIW    | n mm   | Move Indirect FSRn to W with pre/post inc/dec              | 1      | 00            | 0000 | 0001 | 0nmm | Z        | 2, 3  |

|          |        | modifier, mm                                               |        |               |      |      |      |          |       |

|          | k[n]   | Move INDFn to W, Indexed Indirect.                         | 1      | 11            | 1111 | 0nkk | kkkk | Z        | 2     |

| MOVWI    | n mm   | Move W to Indirect FSRn with pre/post inc/dec modifier, mm | 1      | 00            | 0000 | 0001 | lnmm |          | 2, 3  |

|          | k[n]   | Move W to INDFn, Indexed Indirect.                         | 1      | 11            | 1111 | 1nkk | kkkk |          | 2     |

### TABLE 24-4: PIC16(L)F1512/3 INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See Table in the MOVIW and MOVWI instruction descriptions.

### 24.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                      |  |  |  |  |

| Operands:        | -32 ≤ k ≤ 31<br>n ∈ [ 0, 1]                                                                   |  |  |  |  |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |  |  |  |  |

| Status Affected: | None                                                                                          |  |  |  |  |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |  |  |  |  |

|                  |                                                                                               |  |  |  |  |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                               |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                               |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |

| ADDLW            | Add literal and W                                                                                             |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                             |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                      |  |  |  |  |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                     |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                     |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ASRF f {,d}                                                                                                                                                                                                        |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                  |  |  |  |  |  |

| Operation:       | $(f<7>) \rightarrow dest<7>$<br>$(f<7:1>) \rightarrow dest<6:0>,$<br>$(f<0>) \rightarrow C,$                                                                                                                                        |  |  |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |  |  |  |  |  |

### ADD W and CARRY bit to f

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                           |  |  |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |  |  |  |  |

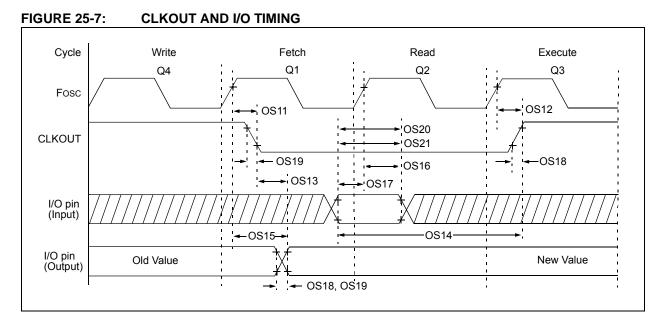

| TABLE 25-8: CLKOUT AND I/O TIMING PARAME |

|------------------------------------------|

|------------------------------------------|

| Standar      | Standard Operating Conditions (unless otherwise stated) |                                                              |               |          |          |       |                              |

|--------------|---------------------------------------------------------|--------------------------------------------------------------|---------------|----------|----------|-------|------------------------------|

| Param<br>No. | Sym.                                                    | Characteristic                                               | Min.          | Тур†     | Max.     | Units | Conditions                   |

| OS11         | TosH2ckL                                                | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              | _             | _        | 70       | ns    | VDD = 3.3-5.0V               |

| OS12         | TosH2ckH                                                | Fosc <sup>↑</sup> to CLKOUT <sup>↑ (1)</sup>                 | _             |          | 72       | ns    | VDD = 3.3-5.0V               |

| OS13         | TckL2ioV                                                | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | _             | _        | 20       | ns    |                              |

| OS14         | TioV2ckH                                                | Port input valid before CLKOUT <sup>(1)</sup>                | Tosc + 200 ns | _        | _        | ns    |                              |

| OS15         | TosH2ioV                                                | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |

| OS16         | TosH2iol                                                | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            | —        | _        | ns    | VDD = 3.3-5.0V               |

| OS17         | TioV2osH                                                | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            | —        | —        | ns    |                              |

| OS18         | TioR                                                    | Port output rise time                                        |               | 40<br>15 | 72<br>32 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS19         | TioF                                                    | Port output fall time                                        |               | 28<br>15 | 55<br>30 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS20*        | Tinp                                                    | INT pin input high or low time                               | 25            | _        | —        | ns    |                              |

| OS21*        | Tioc                                                    | Interrupt-on-change new input level time                     | 25            | —        | —        | ns    |                              |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

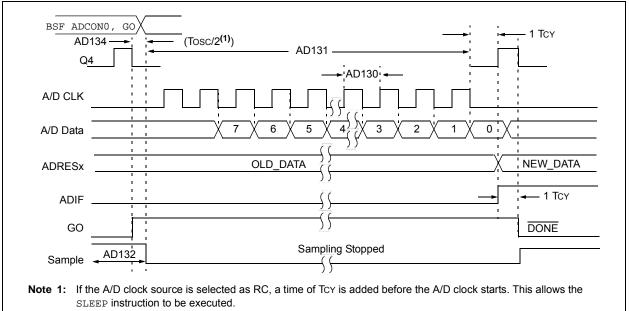

### TABLE 25-13: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym. | Characteristic                                                  | Min. | Тур† | Max. | Units | Conditions                             |

|--------------|------|-----------------------------------------------------------------|------|------|------|-------|----------------------------------------|

| AD130*       | Tad  | A/D Clock Period                                                | 1.0  | -    | 9.0  | μS    | Tosc-based                             |

|              |      | A/D Internal RC Oscillator<br>Period                            | 1.0  | 1.6  | 6.0  | μS    | ADCS<1:0> = 11 (ADRC mode)             |

| AD131        | Тслу | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | -    | 11   | -    | Tad   | Set GO/DONE bit to conversion complete |

| AD132*       | TACQ | Acquisition Time                                                | _    | 5.0  | _    | μS    |                                        |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not † tested.

Note 1: The ADRES register may be read on the following TCY cycle.

#### **FIGURE 25-12:** A/D CONVERSION TIMING (NORMAL MODE)

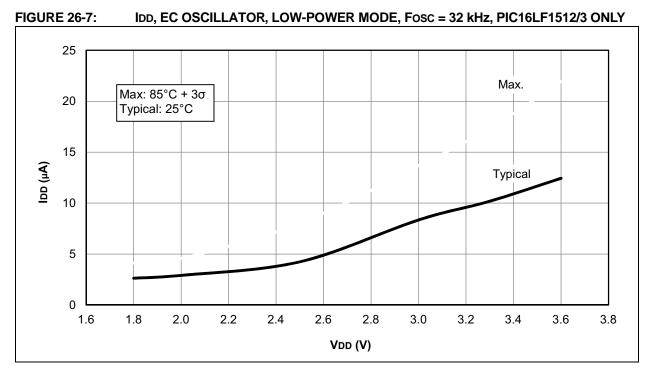

FIGURE 26-8: IDD EC OSCILLATOR, LOW-POWER MODE, Fosc = 32 kHz, PIC16F1512/3 ONLY

### 27.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 27.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>