Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1513-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                           | 7   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Enhanced Mid-range CPU                                                    |     |

| 3.0   | Memory Organization                                                       |     |

| 4.0   | Device Configuration                                                      |     |

| 5.0   | Oscillator Module (With Fail-Safe Clock Monitor)                          |     |

| 6.0   | Resets                                                                    |     |

| 7.0   | Interrupts                                                                |     |

| 8.0   | Power-Down Mode (Sleep)                                                   |     |

| 9.0   | Low Dropout (LDO) Voltage Regulator                                       |     |

| 10.0  | Watchdog Timer (WDT)                                                      |     |

| 11.0  | Flash Program Memory Control                                              | 84  |

| 12.0  | I/O Ports                                                                 | 100 |

| 13.0  | Interrupt-On-Change                                                       |     |

| 14.0  | Fixed Voltage Reference (FVR)                                             | 119 |

| 15.0  | Temperature Indicator Module                                              | 121 |

|       | Analog-to-Digital Converter (ADC) Module                                  |     |

| 17.0  | Timer0 Module                                                             | 157 |

| 18.0  | Timer1 Module with Gate Control                                           | 160 |

| 19.0  | Timer2 Module                                                             |     |

| 20.0  | Master Synchronous Serial Port (MSSP) Module                              | 175 |

| 21.0  | Capture/Compare/PWM Modules                                               | 228 |

| 22.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

| 23.0  | In-Circuit Serial Programming™ (ICSP™)                                    |     |

| 24.0  | Instruction Set Summary                                                   |     |

| 25.0  | Electrical Specifications                                                 |     |

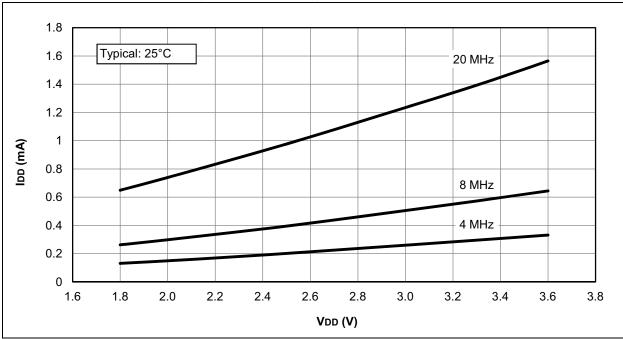

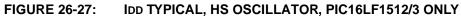

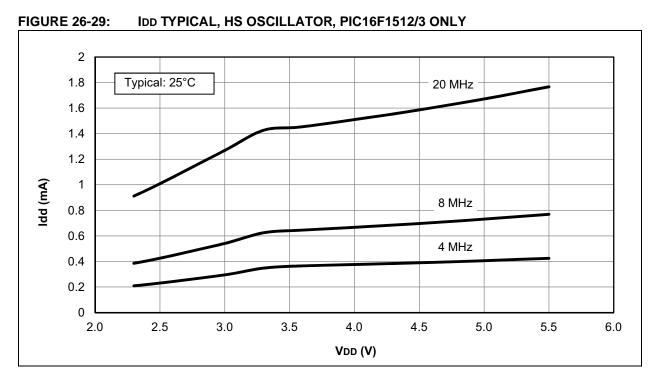

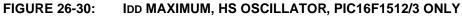

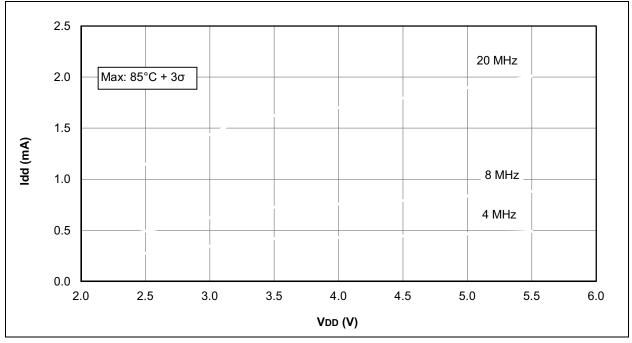

| 26.0  | DC and AC Characteristics Graphs and Charts                               |     |

| 27.0  | Development Support                                                       |     |

|       | Packaging Information                                                     |     |

|       | Aicrochip Website                                                         |     |

|       | omer Change Notification Service                                          |     |

|       | omer Support                                                              |     |

| Produ | uct Identification System                                                 | 360 |

### 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- · 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

Data memory uses a 12-bit address. The upper seven bits of the address define the Bank address and the lower five bits select the registers/RAM in that bank.

### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-8.

|      |         | LOIOTEIKO |  |

|------|---------|-----------|--|

| Addı | esses   | BANKx     |  |

| x00h | or x80h | INDF0     |  |

| x01h | or x81h | INDF1     |  |

| x02h | or x82h | PCL       |  |

| x03h | or x83h | STATUS    |  |

| x04h | or x84h | FSR0L     |  |

| x05h | or x85h | FSR0H     |  |

| x06h | or x86h | FSR1L     |  |

| x07h | or x87h | FSR1H     |  |

| x08h | or x88h | BSR       |  |

| x09h | or x89h | WREG      |  |

| x0Ah | or x8Ah | PCLATH    |  |

| x0Bh | or x8Bh | INTCON    |  |

|      |         |           |  |

TABLE 3-2: CORE REGISTERS

### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

# $INTOSC \longrightarrow for the second seco$

### FIGURE 5-8: TWO-SPEED START-UP

### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

### 6.11 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00-1 110x        |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu-u Ouuu        |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu-u Ouuu        |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu-0 uuuu        |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu-u uuuu        |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00-1 11u0        |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu-u uuuu        |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu-u u0uu        |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu-u uuuu        |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul-u uuuu        |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

### 7.6 Interrupt Control Registers

### 7.6.1 INTCON REGISTER

The INTCON register is a readable and writable register that contains the various enable and flag bits for TMR0 register overflow, interrupt-on-change and external INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R-0/0 |

|---------|---------|---------|---------|---------|---------|---------|-------|

| GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF |

| bit 7   |         |         |         |         |         |         | bit 0 |

|         |         |         |         |         |         |         |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | GIE: Global Interrupt Enable bit                                                                                                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Enables all active interrupts</li><li>0 = Disables all interrupts</li></ul>                                                                                                                                           |

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all active peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                                            |

| bit 5 | <b>TMR0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                                                      |

| bit 4 | INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt                                                                                                      |

| bit 3 | IOCIE: Interrupt-on-Change Interrupt Enable bit<br>1 = Enables the interrupt-on-change<br>0 = Disables the interrupt-on-change                                                                                                    |

| bit 2 | TMR0IF: Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                                                              |

| bit 1 | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur                                                                                                  |

| bit 0 | <ul> <li>IOCIF: Interrupt-on-Change Interrupt Flag bit<sup>(1)</sup></li> <li>1 = When at least one of the interrupt-on-change pins changed state</li> <li>0 = None of the interrupt-on-change pins have changed state</li> </ul> |

|       |                                                                                                                                                                                                                                   |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the interrupt-on-change flags in the IOCBF register have been cleared by software.

### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Section 25.0 "Electrical Specifications" for the LFINTOSC tolerances.

### WDT Operating Modes 10.2

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### WDT CONTROLLED BY SOFTWARE 10.2.3

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-2 for more details.

| TABLE 10-1: WDI OPERATING MODES | TABLE 10-1: | WDT OPERATING MODES |

|---------------------------------|-------------|---------------------|

|---------------------------------|-------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | v      | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ^              | Disabled    |

| 00        | Х      | Х              | Disabled    |

### **TABLE 10-2:** WDT CLEARING CONDITIONS

Conditions

### 10.3 **Time-Out Period**

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

### 10.4 **Clearing the WDT**

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

### 10.5 **Operation During Sleep**

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. See Section 3.0 "Memory Organization" and The STATUS register (Register 3-1) for more information.

| Conditions                                              | VVD1                         |

|---------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                          |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                           |                              |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                |                              |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |

wпт

### TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (CONTINUED)

| ADC Clock           | Period (TAD) | Device Frequency (Fosc)     |                             |                             |                               |                               |

|---------------------|--------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|-------------------------------|

| ADC<br>Clock Source | ADCS<2:0>    | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                         |

| Fosc/16             | 101          | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <sup>(3)</sup>        |

| Fosc/32             | 010          | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>         | 32.0 μs <b><sup>(3)</sup></b> |

| Fosc/64             | 110          | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <b><sup>(3)</sup></b> | 64.0 μs <sup>(3)</sup>        |

| Frc                 | x11          | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup>   |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

**4:** The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock Fosc. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

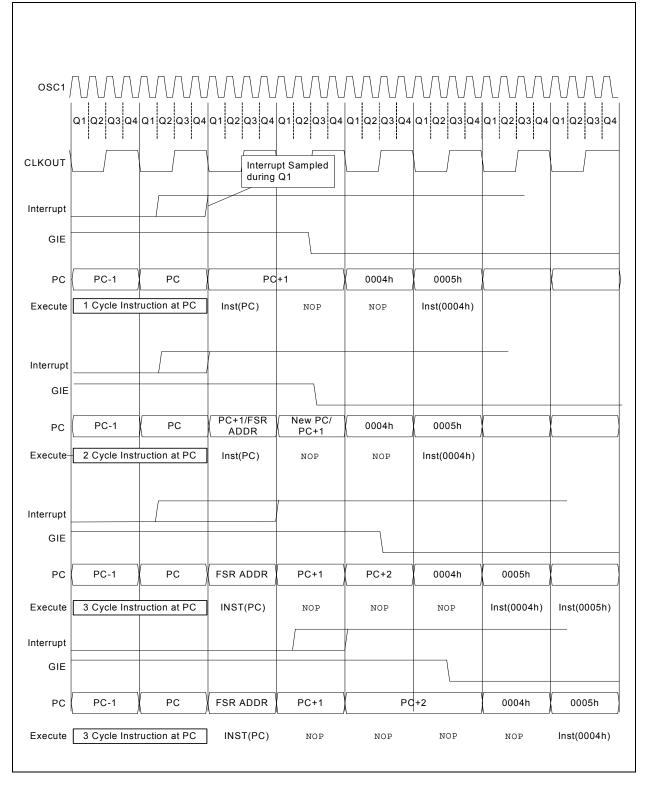

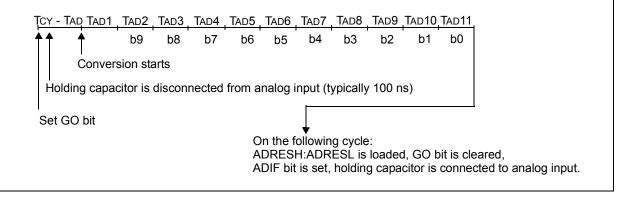

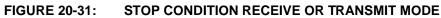

### FIGURE 16-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| REGISTER             |                                                                                                                                                                                                                                                                           | R/W-0/0                                                | R/W-0/0                                                  |                | U-0              | R/W-0/0        | R/W-0/0      |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|----------------|------------------|----------------|--------------|

| ADFM                 | N/W-0/0                                                                                                                                                                                                                                                                   | ADCS<2:0>                                              | N/W-0/0                                                  | 0-0            | 0-0              |                | EF<1:0>      |

| bit 7                |                                                                                                                                                                                                                                                                           | AD00 \2.0/                                             |                                                          |                |                  |                | bit C        |

|                      |                                                                                                                                                                                                                                                                           |                                                        |                                                          |                |                  |                |              |

| Legend:              |                                                                                                                                                                                                                                                                           |                                                        |                                                          |                |                  |                |              |

| R = Readable bit     |                                                                                                                                                                                                                                                                           | W = Writable bit                                       |                                                          | U = Unimpler   | mented bit, read | d as '0'       |              |

| u = Bit is unchanged |                                                                                                                                                                                                                                                                           | x = Bit is unkno                                       | = Bit is unknown -n/n = Value at POR and BOR/Value at al |                |                  | R/Value at all | other Resets |

| '1' = Bit is s       | et                                                                                                                                                                                                                                                                        | '0' = Bit is clear                                     | '0' = Bit is cleared                                     |                |                  |                |              |

| bit 7<br>bit 6-4     | 1 = Right-ju<br>loaded.<br>0 = Left-jus<br>loaded.<br>ADCS<2:02<br>000 = Foso<br>001 = Foso<br>010 = Foso                                                                                                                                                                 | tified. Six Least S<br>.: A/D Conversion<br>c/2<br>c/8 | Significant bi<br>ignificant bit<br>Clock Selec          | ts of ADRESL a | are set to '0' w |                |              |

| bit 3-2              | 100 = Fose<br>101 = Fose<br>110 = Fose<br>111 = Frc                                                                                                                                                                                                                       | c/4<br>c/16                                            | om a dedicat                                             |                |                  |                |              |

| bit 1-0              | ADPREF<1:0>: A/D Positive Voltage Reference Configuration bits<br>00 = VREF is connected to VDD<br>01 = Reserved<br>10 = VREF is connected to external VREF+ pin <sup>(1)</sup><br>11 = VREF is connected to internal Fixed Voltage Reference (FVR) module <sup>(1)</sup> |                                                        |                                                          |                |                  |                |              |

|                      |                                                                                                                                                                                                                                                                           | the FVR or the VR<br>e specification exis              |                                                          |                |                  |                |              |

# REGISTER 16-2: ADCON1: A/D CONTROL REGISTER 1

# 20.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte-oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

## 20.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an Acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

# 20.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of I<sup>2</sup>C communication that have definitions specific to I<sup>2</sup>C. That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips I<sup>2</sup>C specification.

### 20.4.3 SDA AND SCL PINS

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

### 20.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

# TABLE 20-2: I<sup>2</sup>C BUS TERMS

| TABLE 20-2: I-C BUS TERMS |                                                                                                                                                                                                  |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TERM                      | Description                                                                                                                                                                                      |  |  |  |

| Transmitter               | The device which shifts data out onto the bus.                                                                                                                                                   |  |  |  |

| Receiver                  | The device which shifts data in from the bus.                                                                                                                                                    |  |  |  |

| Master                    | The device that initiates a transfer,<br>generates clock signals and<br>terminates a transfer.                                                                                                   |  |  |  |

| Slave                     | The device addressed by the master.                                                                                                                                                              |  |  |  |

| Multi-master              | A bus with more than one device that can initiate data transfers.                                                                                                                                |  |  |  |

| Arbitration               | Procedure to ensure that only one<br>master at a time controls the bus.<br>Winning arbitration ensures that<br>the message is not corrupted.                                                     |  |  |  |

| Synchronization           | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |  |  |  |

| Idle                      | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                     |  |  |  |

| Active                    | Any time one or more master devices are controlling the bus.                                                                                                                                     |  |  |  |

| Addressed<br>Slave        | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |  |  |  |

| Matching<br>Address       | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                               |  |  |  |

| Write Request             | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                             |  |  |  |

| Read Request              | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |  |  |  |

| Clock Stretching          | When a device on the bus hold SCL low to stall communication.                                                                                                                                    |  |  |  |

| Bus Collision             | Any time the SDA line is sampled<br>low by the module while it is<br>outputting and expected high<br>state.                                                                                      |  |  |  |

### 20.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

### 20.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 20.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

### 20.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

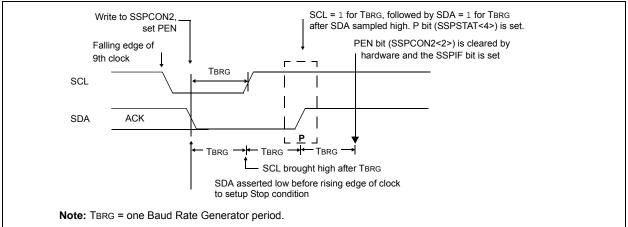

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the I<sup>2</sup>C port to its Idle state (Figure 20-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

# 21.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/ Compare/PWM modules (CCP1 and CCP2).

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

# FIGURE 24-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file registe                                                  | erope<br>76 | erat       | ions             | 0              |

|-----------------------------------------------------------------------------|-------------|------------|------------------|----------------|

| OPCODE                                                                      | d           |            | f (FILE #)       |                |

| d = 0 for destination<br>d = 1 for destination<br>f = 7-bit file register a | f           | SS         |                  |                |

| Bit-oriented file register<br>13 10 9                                       | oper:       |            |                  | 0              |

| · · · · · ·                                                                 | (BIT #      | <b>#</b> ) | f (FILE #)       |                |

| b = 3-bit bit address<br>f = 7-bit file register a                          | addre       | SS         |                  |                |

| Literal and control opera                                                   | ations      | 5          |                  |                |

| General                                                                     |             |            |                  | _              |

| 13<br>OPCODE                                                                | 8 7         |            | k (literal)      | 0              |

|                                                                             |             |            | k (literal)      |                |

| k = 8-bit immediate v                                                       | /alue       |            |                  |                |

| CALL and GOTO instruction                                                   | ns onl      | y          |                  |                |

| 13 11 10                                                                    |             |            |                  | 0              |

| OPCODE                                                                      | ŀ           | k (lit     | eral)            |                |

| k = 11-bit immediate                                                        | value       | è          |                  |                |

| MOVLP instruction only 13                                                   | 7           | 6          |                  | 0              |

| OPCODE                                                                      | 1           |            | k (literal)      |                |

| k = 7-bit immediate v                                                       | alua        |            |                  |                |

| MOVLB instruction only                                                      | aiue        |            |                  |                |

| 13                                                                          |             | 5          | 4                | 0              |

| OPCODE                                                                      |             |            | k (literal)      |                |

| k = 5-bit immediate v                                                       | alue        |            |                  |                |

| BRA instruction only<br>13 9                                                | 8           |            |                  | 0              |

| OPCODE                                                                      |             |            | k (literal)      |                |

| k = 9-bit immediate                                                         | value       |            |                  |                |

| FSR Offset instructions                                                     |             |            |                  |                |

| 13                                                                          | 76          | 5          |                  | 0              |

| OPCODE                                                                      | n           |            | k (literal)      |                |

| n = appropriate FSR<br>k = 6-bit immediate                                  |             |            |                  |                |

|                                                                             |             |            |                  |                |

| FSR Increment instructions                                                  | S           |            | 3 2 1            | 0              |

| FSR Increment instruction                                                   | S           |            | 3 2 1<br>n m (mc | 0<br>ode)      |

| FSR Increment instruction                                                   | _           |            |                  | 0<br>ode)      |

| FSR Increment instruction:<br>13<br>OPCODE<br>n = appropriate FSR           | _           |            |                  | 0<br>ode)<br>0 |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                               |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                    |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                               |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                       |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                 |  |  |

| Status Affected: | Z                                                                                                                                                                        |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1', the<br>result is placed back in register 'f'. |  |  |

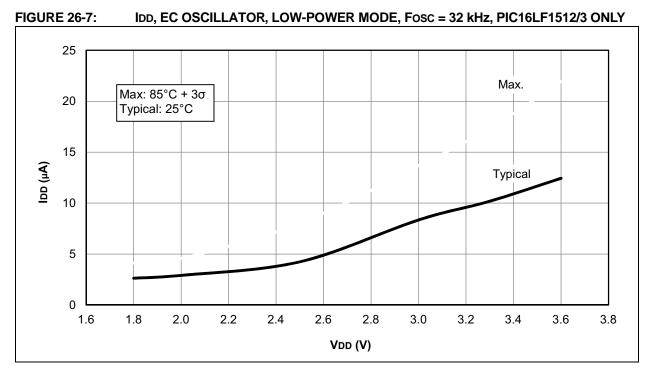

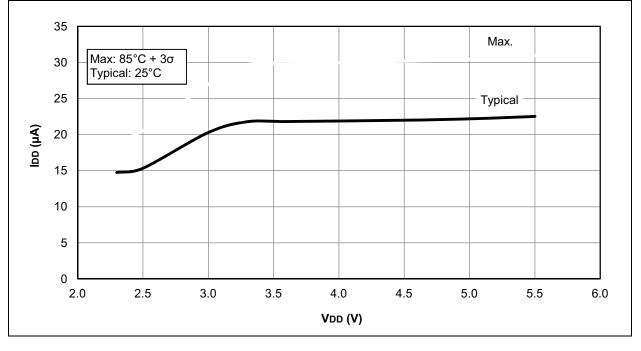

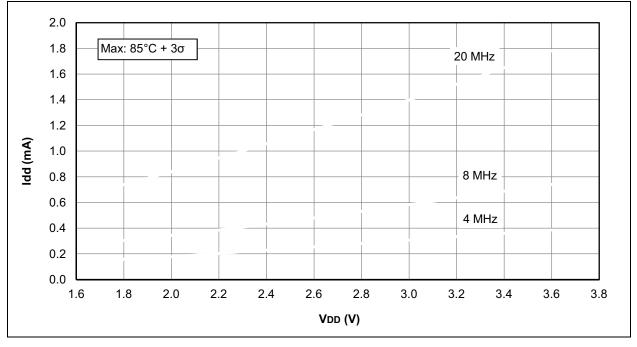

FIGURE 26-8: IDD EC OSCILLATOR, LOW-POWER MODE, Fosc = 32 kHz, PIC16F1512/3 ONLY

# 27.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 27.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 27.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 27.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 27.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 28.2 Package Details

The following sections give the technical details of the packages.

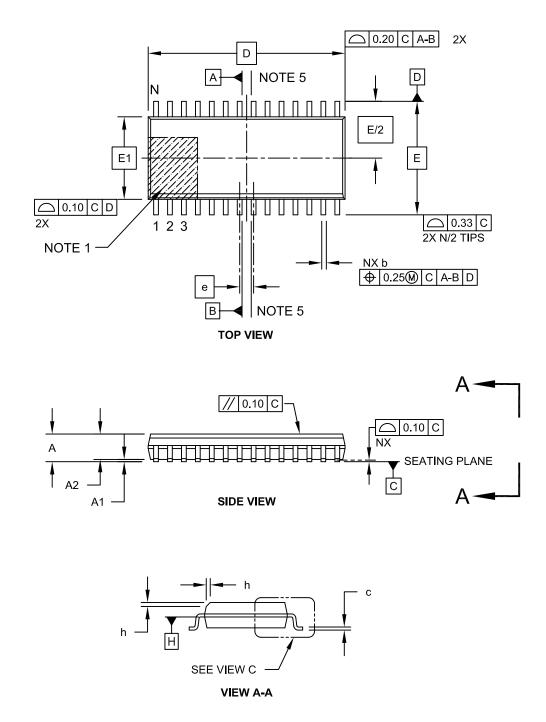

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

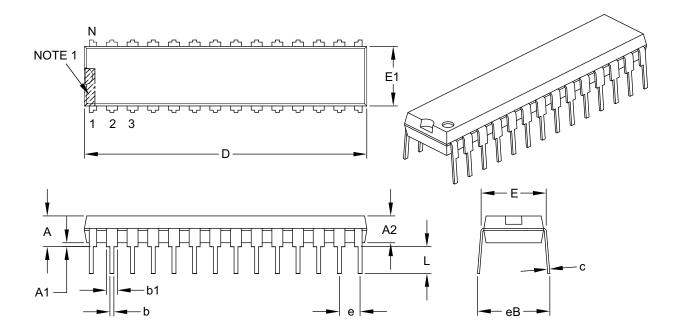

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |  |  |

|----------------------------|------------------|-------|----------|-------|--|--|

| Dimension                  | Dimension Limits |       | NOM      | MAX   |  |  |

| Number of Pins             |                  |       | 28       |       |  |  |

| Pitch                      |                  |       | .100 BSC |       |  |  |

| Top to Seating Plane       | Α                | -     | _        | .200  |  |  |

| Molded Package Thickness   | A2               | .120  | .135     | .150  |  |  |

| Base to Seating Plane      | A1               | .015  | _        | -     |  |  |

| Shoulder to Shoulder Width | E                | .290  | .310     | .335  |  |  |

| Molded Package Width       | E1               | .240  | .285     | .295  |  |  |

| Overall Length             | D                | 1.345 | 1.365    | 1.400 |  |  |

| Tip to Seating Plane       | L                | .110  | .130     | .150  |  |  |

| Lead Thickness             | С                | .008  | .010     | .015  |  |  |

| Upper Lead Width           | b1               | .040  | .050     | .070  |  |  |

| Lower Lead Width           | b                | .014  | .018     | .022  |  |  |

| Overall Row Spacing §      | eВ               | -     | _        | .430  |  |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B