Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1513-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

# $INTOSC \longrightarrow for the second seco$

#### FIGURE 5-8: TWO-SPEED START-UP

#### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

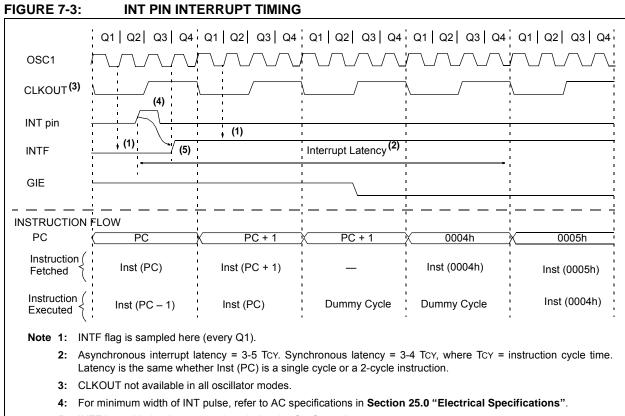

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

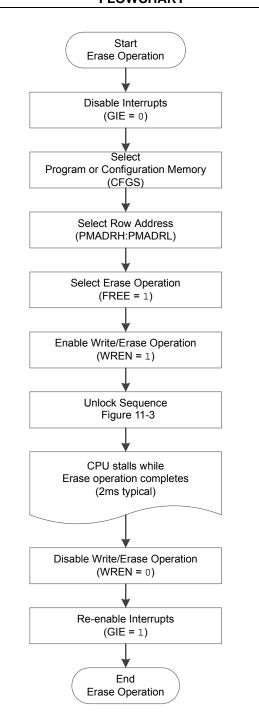

#### 11.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

#### See Example 11-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions immediately following the WR bit set instruction. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

## FIGURE 11-4: FLASH PROGRAM

#### MEMORY ERASE FLOWCHART

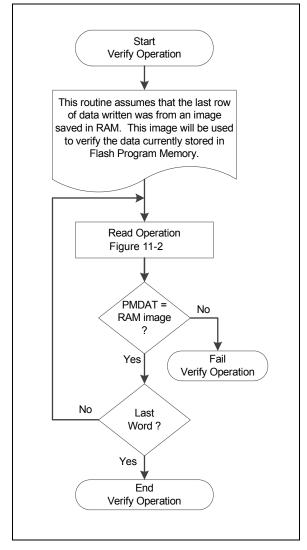

#### 11.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 11-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

#### 12.4 PORTC Registers

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 12-12). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 12-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 12-12) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.4.1 ANSELC REGISTER

The ANSELC register (Register 12-14) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 12.4.2 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 12-7.

| <b>TABLE 12-7:</b> | PORTC OUTPUT PRIORITY |

|--------------------|-----------------------|

|--------------------|-----------------------|

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RC0      | SOSCO<br>RC0                     |

| RC1      | SOSCI<br>CCP2<br>RC1             |

| RC2      | CCP1<br>RC2                      |

| RC3      | SCL<br>SCK<br>RC3 <sup>(2)</sup> |

| RC4      | SDA<br>RC4 <sup>(2)</sup>        |

| RC5      | SDO<br>RC5                       |

| RC6      | CK<br>TX<br>RC6                  |

| RC7      | DT<br>RC7                        |

Note 1: Priority listed from highest to lowest.

**2:** RC3 and RC4 read the  $I^2C$  ST input when  $I^2C$  mode is enabled.

## 14.3 FVR Control Registers

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0        | ) R-q/q                                      | R/W-0/0                                                                                                                                                                                                        | R/W-0/0                                         | U-0                                                                                         | U-0                                          | R/W-0/0 | R/W-0/0      |

|----------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------|---------|--------------|

| FVREN          | I FVRRDY <sup>(1)</sup>                      | TSEN                                                                                                                                                                                                           | TSRNG                                           |                                                                                             | —                                            | ADFV    | R<1:0>       |

| bit 7          |                                              |                                                                                                                                                                                                                |                                                 |                                                                                             |                                              | ·       | bit 0        |

|                |                                              |                                                                                                                                                                                                                |                                                 |                                                                                             |                                              |         |              |

| Legend:        |                                              |                                                                                                                                                                                                                |                                                 |                                                                                             |                                              |         |              |

| R = Reada      | ble bit                                      | W = Writable                                                                                                                                                                                                   | bit                                             | U = Unimpler                                                                                | mented bit, read                             | as '0'  |              |

| u = Bit is u   | nchanged                                     | x = Bit is unkr                                                                                                                                                                                                | nown                                            |                                                                                             | at POR and BOI                               |         | other Resets |

| '1' = Bit is s | set                                          | '0' = Bit is clea                                                                                                                                                                                              | ared                                            | q = Value dep                                                                               | pends on condition                           | ion     |              |

| bit 7          | 0 = Fixed Vo                                 | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                                                                                                                                             | e is disabled                                   | bit                                                                                         |                                              |         |              |

| bit 6          | 0 = Fixed Vo                                 | <b>FVRRDY:</b> Fixed Voltage Reference Ready Flag bit <sup>(1)</sup><br>0 = Fixed Voltage Reference output is not ready or not enabled<br>1 = Fixed Voltage Reference output is ready for use                  |                                                 |                                                                                             |                                              |         |              |

| bit 5          | 0 = Tempera                                  | erature Indicato<br>ture Indicator is<br>ture Indicator is                                                                                                                                                     | s disabled                                      |                                                                                             |                                              |         |              |

| bit 4          | 0 = Vout = V                                 | iperature Indica<br>/DD - 2V⊤ (Low<br>/DD - 4V⊤ (High                                                                                                                                                          | Range)                                          | election bit                                                                                |                                              |         |              |

| bit 3-2        | Unimplemen                                   | ted: Read as '                                                                                                                                                                                                 | 0'                                              |                                                                                             |                                              |         |              |

| bit 1-0        | 00 = ADC Fix<br>01 = ADC Fix<br>10 = ADC Fix | ked Voltage Rei<br>ked Voltage Rei<br>ked Voltage Rei                                                                                                                                                          | ference Perip<br>ference Perip<br>ference Perip | nce Selection I<br>heral output is<br>heral output is<br>heral output is<br>heral output is | off<br>1x (1.024V)<br>2x (2.048V) <b>(2)</b> |         |              |

|                |                                              | <ul> <li>11 = ADC Fixed Voltage Reference Peripheral output is 4x (4.096V)<sup>(2)</sup></li> <li>RRDY is always '1' on PIC16F1512/3 only.</li> <li>red Voltage Reference output cannot exceed VDD.</li> </ul> |                                                 |                                                                                             |                                              |         |              |

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | —     | _     | ADFV  | R<1:0> | 120                 |

TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

#### REGISTER 16-3: ADRES0H: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

|                  |         |                    |         |                | /                | -              |              |

|------------------|---------|--------------------|---------|----------------|------------------|----------------|--------------|

| R/W-x/u          | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|                  |         |                    | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                    |         |                |                  |                | bit 0        |

|                  |         |                    |         |                |                  |                |              |

| Legend:          |         |                    |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable bi    | it      | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkno   | wn      | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clear | ed      |                |                  |                |              |

|                  |         |                    |         |                |                  |                |              |

bit 7-0 **ADRES<9:2>:** ADC Result Register bits Upper eight bits of 10-bit conversion result

### **REGISTER 16-4:** ADRESOL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | S<1:0>  | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits

Lower two bits of 10-bit conversion result

bit 5-0 Reserved: Do not use.

#### FIGURE 16-12: DOUBLE SAMPLE CONVERSION SEQUENCE (ADDSEN = 1 AND ADIPEN = 1)

## 16.7 Register Definitions: Hardware CVD Control

| U-0             | R/W-0/0                                                                                                                                                                                                                                                                                                                                                       | R/W-0/0                                                                                               | R/W-0/0                                                                                                                           | R/W-0/0                   | R/W-0/0           | R/W-0/0            | R/W-0/0 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------|--------------------|---------|

| _               |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       | CHS<4:0>                                                                                                                          |                           |                   | GO/DONE            | ADON    |

| oit 7           |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |                                                                                                                                   |                           |                   |                    | bit (   |

| _egend:         |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |                                                                                                                                   |                           |                   |                    |         |

| R = Readable    | e bit                                                                                                                                                                                                                                                                                                                                                         | W = Writable bi                                                                                       | t                                                                                                                                 | U = Unimpleme             | ented bit, read a | s '0'              |         |

| u = Bit is unc  | hanged                                                                                                                                                                                                                                                                                                                                                        | x = Bit is unkno                                                                                      | wn                                                                                                                                | •                         |                   | Value at all other | Resets  |

| 1' = Bit is set | •                                                                                                                                                                                                                                                                                                                                                             | '0' = Bit is clear                                                                                    |                                                                                                                                   |                           |                   |                    |         |

| 1 - Dit 13 301  |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       | cu                                                                                                                                |                           |                   |                    |         |

| bit 7           | Unimplement                                                                                                                                                                                                                                                                                                                                                   | ted: Read as '0'                                                                                      |                                                                                                                                   |                           |                   |                    |         |

| bit 6-2         | 11111 = FVR<br>11100 = Ress<br>11101 = Tem<br>11000 = Ress<br>10011 = VRE<br>11001 = Ress<br>00100 = Ress<br>10000 = AN1<br>10000 = AN1<br>10000 = AN1<br>01111 = AN1<br>01101 = AN1<br>01101 = AN1<br>01101 = AN1<br>01001 = AN1<br>01010 = AN1<br>01010 = AN3<br>00111 = Ress<br>00100 = Ress<br>00100 = Ress<br>00100 = Ress<br>00100 = AN4<br>00011 = AN3 | 8<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>erved. No channe<br>erved. No channe<br>erved. No channe | eference) Buffe<br>I connected.<br>(3)<br>I connected.<br>Reference)<br>Reference) <sup>(4)</sup><br>I connected.<br>I connected. | r 1 Output <sup>(2)</sup> |                   |                    |         |

|                 | 00010 = AN2<br>00001 = AN1                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |                                                                                                                                   |                           |                   |                    |         |

| bit 1           | 1 = A/D conve<br>This bit is                                                                                                                                                                                                                                                                                                                                  | D Conversion Sta<br>ersion cycle in pro-<br>automatically clea<br>ersion completed/r                  | gress. Setting t<br>ared by hardwa                                                                                                |                           |                   |                    |         |

| bit 0           | ADON: ADC Enable bit<br>1 = ADC is enabled<br>0 = ADC is disabled and consumes no operating current                                                                                                                                                                                                                                                           |                                                                                                       |                                                                                                                                   |                           |                   |                    |         |

| <b>2</b> : S    | See Section 16.6.1<br>See Section 14.0 "<br>See Section 15.0 "                                                                                                                                                                                                                                                                                                | Fixed Voltage Re                                                                                      | eference (FVR)                                                                                                                    | " for more inform         | ation.            |                    |         |

## REGISTER 16-7: AADCON0: HARDWARE CVD CONTROL REGISTER 0<sup>(1)</sup>

4: Conversion results for the VREFH selection may contain errors due to noise.

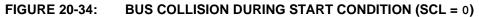

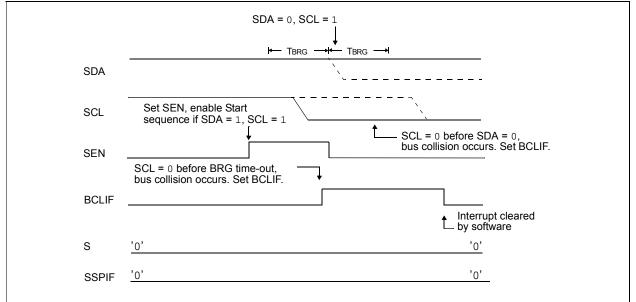

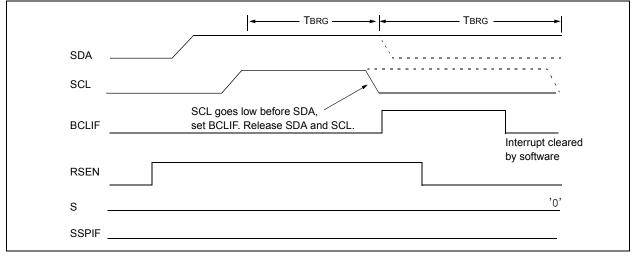

#### FIGURE 20-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

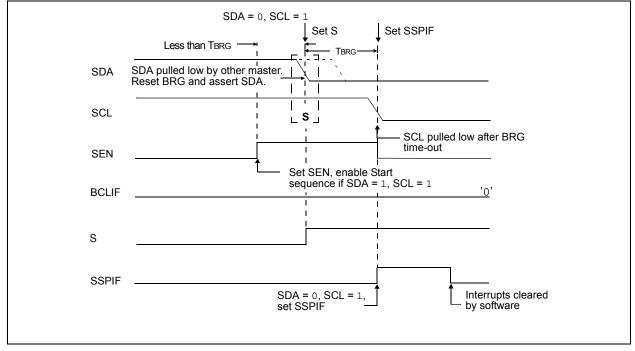

## 20.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 20-35). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 20-36.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 20-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

| R/W-/0           | R/W-0/0                                                                          | R/W-0/0                                                                       | R/W-0/0          | R/W-0/0          | R/W-0/0            | R-1/1             | R/W-0/0 |

|------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------|------------------|--------------------|-------------------|---------|

| CSRC             | TX9                                                                              | TXEN <sup>(1)</sup>                                                           | SYNC             | SENDB            | BRGH               | TRMT              | TX9D    |

| oit 7            |                                                                                  |                                                                               | •                |                  |                    |                   | bit     |

| Legend:          |                                                                                  |                                                                               |                  |                  |                    |                   |         |

| R = Readable     | bit                                                                              | W = Writable b                                                                | it               | U = Unimpleme    | ented bit, read as | 0'                |         |

| u = Bit is unch  | anged                                                                            | x = Bit is unkno                                                              | own              | -n/n = Value at  | POR and BOR/Va     | alue at all other | Resets  |

| '1' = Bit is set |                                                                                  | '0' = Bit is clear                                                            | red              |                  |                    |                   |         |

| bit 7            | <u>Asynchronous</u><br>Don't care<br><u>Synchronous r</u><br>1 = Master n        |                                                                               | rated internally | from BRG)        |                    |                   |         |

| bit 6            | 1 = Selects 9                                                                    | nsmit Enable bit<br>9-bit transmission<br>8-bit transmission                  |                  |                  |                    |                   |         |

| bit 5            |                                                                                  | Transmit Enable bit <sup>(1)</sup><br>ansmit enabled<br>ansmit disabled       |                  |                  |                    |                   |         |

| bit 4            | 1 = Synchron                                                                     | SYNC: EUSART Mode Select bit<br>1 = Synchronous mode<br>0 = Asynchronous mode |                  |                  |                    |                   |         |

| bit 3            | Asynchronous<br>1 = Send Syr                                                     | nc Break on next<br>ak transmission o                                         | transmission (c  | leared by hardwa | are upon completic | on)               |         |

| bit 2            |                                                                                  | ed<br>ed<br>node:                                                             | bit              |                  |                    |                   |         |

| bit 1            | <b>TRMT:</b> Transmit Shift Register Status bit<br>1 = TSR empty<br>0 = TSR full |                                                                               |                  |                  |                    |                   |         |

| bit 0            | TX9D: Ninth b<br>Can be addres                                                   | it of Transmit Dat                                                            |                  |                  |                    |                   |         |

#### **EUSART Control Registers** 22.3

#### 22.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 22.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 22.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 22.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 22.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

## 22.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

### 24.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDFSR FSRn, k                                                                        |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  |                                                                                               |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \to (W)$                                                                                             |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ASRF f {,d}                                                                                                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                  |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                                             |

| Status Affected: | C, Z                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

#### ADD W and CARRY bit to f

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               | BTFSS                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                         | Syntax:<br>Operands: |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                | Operation:           |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 | Status Affected      |

| Status Affected: | None                                                                                                                                                                                                                          | Description:         |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |                      |

| BRW              | Relative Branch with W                                                                                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BRW                                                                                                                                                                                                 |

| Operands:        | None                                                                                                                                                                                                                 |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                                                 |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be $PC + 1 + (W)$ .<br>This instruction is a 2-cycle instruc-<br>tion. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b>)$                                          |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

#### TABLE 25-4: I/O PORTS

Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Sym. | Characteristic                                          | Min.              | Тур† | Max.     | Units | Conditions                                                                 |

|--------------|------|---------------------------------------------------------|-------------------|------|----------|-------|----------------------------------------------------------------------------|

|              | VIL  | Input Low Voltage                                       |                   |      |          |       |                                                                            |

|              |      | I/O PORT:                                               |                   |      |          |       |                                                                            |

| D030         |      | with TTL buffer                                         | _                 | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D030A        |      |                                                         | —                 | —    | 0.15 VDD | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |

| D031         |      | with Schmitt Trigger buffer                             | _                 | _    | 0.2 Vdd  | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |

|              |      | with I <sup>2</sup> C levels                            | —                 | —    | 0.3 Vdd  | V     |                                                                            |

|              |      | with SMBus levels                                       | _                 | _    | 0.8      | V     | $2.7V \leq V\text{DD} \leq 5.5V$                                           |

| D032         |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>                     | _                 | _    | 0.2 VDD  | V     |                                                                            |

| D033         |      | OSC1 (HS mode)                                          | _                 | _    | 0.3 VDD  | V     |                                                                            |

|              | Viн  | Input High Voltage                                      |                   |      |          |       |                                                                            |

|              |      | I/O ports:                                              |                   | _    | _        |       |                                                                            |

| D040         |      | with TTL buffer                                         | 2.0               | _    | _        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D040A        |      |                                                         | 0.25 VDD +<br>0.8 | _    | _        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |

| D041         |      | with Schmitt Trigger buffer                             | 0.8 Vdd           | _    | _        | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |

|              |      | with I <sup>2</sup> C levels                            | 0.7 Vdd           | —    | —        | V     |                                                                            |

|              |      | with SMBus levels                                       | 2.1               | —    | —        | V     | $2.7V \leq V\text{DD} \leq 5.5V$                                           |

| D042         |      | MCLR                                                    | 0.8 Vdd           | _    | _        | V     |                                                                            |

| D043A        |      | OSC1 (HS mode)                                          | 0.7 Vdd           | _    | _        | V     |                                                                            |

| D043B        |      | OSC1 (RC mode)                                          | 0.9 VDD           | _    | _        | V     | VDD > 2.0V (Note 1)                                                        |

|              | lı∟  | Input Leakage Current <sup>(2)</sup>                    |                   |      |          |       |                                                                            |

| D060         |      | I/O ports                                               | —                 | ± 5  | ± 125    | nA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance at 85°C                  |

|              |      |                                                         |                   | ± 5  | ± 1000   | nA    | 125°C                                                                      |

| D061         |      | MCLR <sup>(3)</sup>                                     | —                 | ± 50 | ± 200    | nA    | $Vss \leq V\text{PIN} \leq V\text{DD} \text{ at } 85^\circ\text{C}$        |

|              | IPUR | Weak Pull-up Current                                    |                   |      |          | 1     | Γ                                                                          |

| D070*        |      |                                                         | 25                | 100  | 200      | •     | VDD = 3.3V, $VPIN = VSS$                                                   |

|              | 1/21 | <b>O</b> and the second state of the second <b>(4</b> ) | 25                | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |

| <b>D</b> 000 | Vol  | Output Low Voltage <sup>(4)</sup>                       |                   |      |          |       |                                                                            |

| D080         |      | I/O ports                                               | —                 | _    | 0.6      | v     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |

|              | Voн  | Output High Voltage <sup>(4)</sup>                      | 11                |      | 1        | 1     | 1                                                                          |

| D090         |      | I/O ports                                               | Vdd - 0.7         | _    | _        | v     | ІОН = 3.5 mA, VDD = 5V<br>ІОН = 3 mA, VDD = 3.3V<br>ІОН = 1 mA, VDD = 1.8V |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

**2:** Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

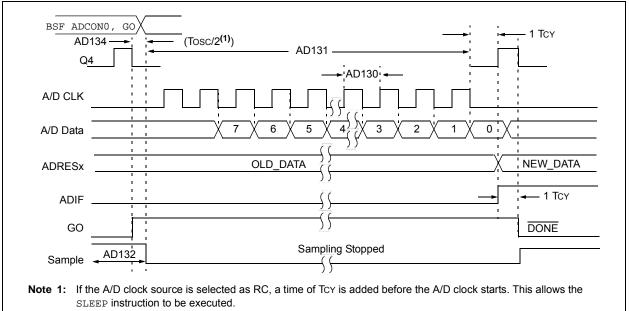

#### TABLE 25-13: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym. | Characteristic                                                  | Min. | Тур† | Max. | Units | Conditions                             |

|--------------|------|-----------------------------------------------------------------|------|------|------|-------|----------------------------------------|

| AD130*       | Tad  | A/D Clock Period                                                | 1.0  | -    | 9.0  | μS    | Tosc-based                             |

|              |      | A/D Internal RC Oscillator<br>Period                            | 1.0  | 1.6  | 6.0  | μS    | ADCS<1:0> = 11 (ADRC mode)             |

| AD131        | Тслу | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | -    | 11   | -    | Tad   | Set GO/DONE bit to conversion complete |

| AD132*       | TACQ | Acquisition Time                                                | _    | 5.0  | _    | μS    |                                        |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not † tested.

Note 1: The ADRES register may be read on the following TCY cycle.

#### **FIGURE 25-12:** A/D CONVERSION TIMING (NORMAL MODE)

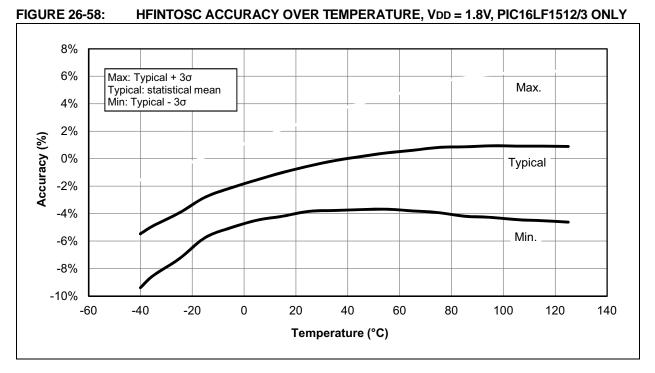

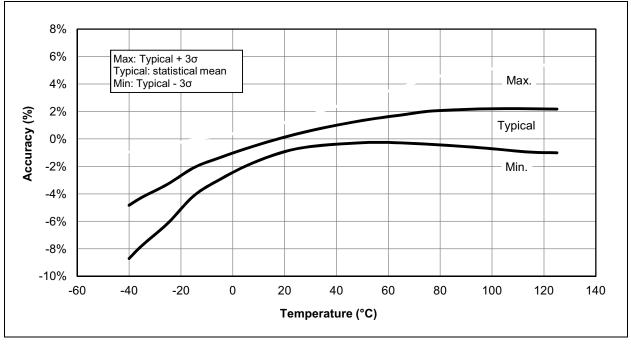

FIGURE 26-59: HFINTOSC ACCURACY OVER TEMPERATURE,  $2.3V \le VDD \le 5.5V$

#### 27.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 27.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>