#### Welcome to E-XFL.COM

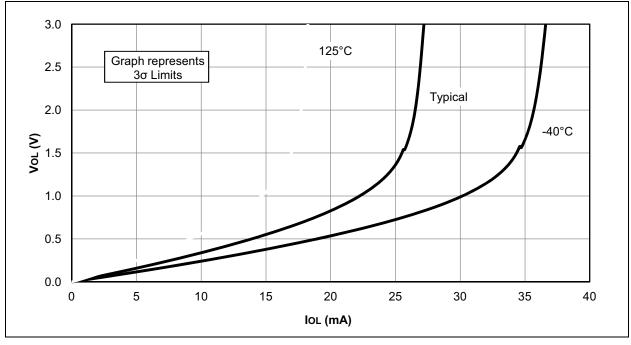

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1513-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 3-3:** PIC16(L)F1512 MEMORY MAP (BANKS 0-7)

|      | BANK 0                        |              | BANK 1                                |      | BANK 2                                |      | BANK 3                                |      | BANK 4                                |      | BANK 5                                |      | BANK 6                                |      | BANK 7                                |

|------|-------------------------------|--------------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|

| 000h |                               | 080h         |                                       | 100h |                                       | 180h |                                       | 200h |                                       | 280h |                                       | 300h |                                       | 380h |                                       |

|      | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2)         |      | Core Registers<br>(Table 3-2)         |      | Core Registers<br>(Table 3-2)         |      | Core Registers<br>(Table 3-2)         |      | Core Registers<br>(Table 3-2)         |      | Core Registers<br>(Table 3-2)         |      | Core Registers<br>(Table 3-2)         |

| 00Bh |                               | 08Bh         |                                       | 10Bh |                                       | 18Bh |                                       | 20Bh |                                       | 28Bh |                                       | 30Bh |                                       | 38Bh |                                       |

| 00Ch | PORTA                         | 08Ch         | TRISA                                 | 10Ch | LATA                                  | 18Ch | ANSELA                                | 20Ch | —                                     | 28Ch | _                                     | 30Ch | —                                     | 38Ch | —                                     |

| 00Dh | PORTB                         | 08Dh         | TRISB                                 | 10Dh | LATB                                  | 18Dh | ANSELB                                | 20Dh | WPUB                                  | 28Dh |                                       | 30Dh | —                                     | 38Dh | —                                     |

| 00Eh | PORTC                         | 08Eh         | TRISC                                 | 10Eh | LATC                                  | 18Eh | ANSELC                                | 20Eh | —                                     | 28Eh | _                                     | 30Eh | —                                     | 38Eh | —                                     |

| 00Fh | _                             | 08Fh         | _                                     | 10Fh |                                       | 18Fh | —                                     | 20Fh | —                                     | 28Fh | _                                     | 30Fh | —                                     | 38Fh | —                                     |

| 010h | PORTE                         | 090h         | TRISE                                 | 110h | _                                     | 190h | —                                     | 210h | WPUE                                  | 290h | —                                     | 310h | —                                     | 390h | —                                     |

| 011h | PIR1                          | 091h         | PIE1                                  | 111h |                                       | 191h | PMADRL                                | 211h | SSPBUF                                | 291h | CCPR1L                                | 311h | —                                     | 391h | —                                     |

| 012h | PIR2                          | 092h         | PIE2                                  | 112h |                                       | 192h | PMADRH                                | 212h | SSPADD                                | 292h | CCPR1H                                | 312h | _                                     | 392h | —                                     |

| 013h | _                             | 093h         | _                                     | 113h |                                       | 193h | PMDATL                                | 213h | SSPMSK                                | 293h | CCP1CON                               | 313h | —                                     | 393h | —                                     |

| 014h | —                             | 094h         | —                                     | 114h | _                                     | 194h | PMDATH                                | 214h | SSPSTAT                               | 294h | —                                     | 314h | —                                     | 394h | IOCBP                                 |

| 015h | TMR0                          | 095h         | OPTION_REG                            | 115h | _                                     | 195h | PMCON1                                | 215h | SSPCON1                               | 295h | —                                     | 315h | —                                     | 395h | IOCBN                                 |

| 016h | TMR1L                         | 096h         | PCON                                  | 116h | BORCON                                | 196h | PMCON2                                | 216h | SSPCON2                               | 296h | -                                     | 316h | —                                     | 396h | IOCBF                                 |

| 017h | TMR1H                         | 097h         | WDTCON                                | 117h | FVRCON                                | 197h | VREGCON <sup>(1)</sup>                | 217h | SSPCON3                               | 297h | —                                     | 317h | —                                     | 397h | —                                     |

| 018h | T1CON                         | 098h         | _                                     | 118h |                                       | 198h | —                                     | 218h | _                                     | 298h | CCPR2L                                | 318h | _                                     | 398h | —                                     |

| 019h | T1GCON                        | 099h         | OSCCON                                | 119h | _                                     | 199h | RCREG                                 | 219h | _                                     | 299h | CCPR2H                                | 319h | _                                     | 399h | _                                     |

| 01Ah | TMR2                          | 09Ah         | OSCSTAT                               | 11Ah | _                                     | 19Ah | TXREG                                 | 21Ah | —                                     | 29Ah | CCP2CON                               | 31Ah | —                                     | 39Ah | —                                     |

| 01Bh | PR2                           | 09Bh         | ADRES0L                               | 11Bh | _                                     | 19Bh | SPBRGL                                | 21Bh | —                                     | 29Bh | —                                     | 31Bh | —                                     | 39Bh | —                                     |

| 01Ch | T2CON                         | 09Ch         | ADRES0H                               | 11Ch | _                                     | 19Ch | SPBRGH                                | 21Ch | _                                     | 29Ch | _                                     | 31Ch | _                                     | 39Ch | _                                     |

| 01Dh | _                             | 09Dh         | ADCON0                                | 11Dh | APFCON                                | 19Dh | RCSTA                                 | 21Dh | _                                     | 29Dh | —                                     | 31Dh | _                                     | 39Dh | _                                     |

| 01Eh | —                             | 09Eh         | ADCON1                                | 11Eh | _                                     | 19Eh | TXSTA                                 | 21Eh | —                                     | 29Eh | —                                     | 31Eh | _                                     | 39Eh | _                                     |

| 01Fh | —                             | 09Fh         | —                                     | 11Fh | —                                     | 19Fh | BAUDCON                               | 21Fh | —                                     | 29Fh | —                                     | 31Fh | —                                     | 39Fh | —                                     |

| 020h | General                       | 0A0h         | General Purpose<br>Register           | 120h |                                       | 1A0h |                                       | 220h |                                       | 2A0h |                                       | 320h |                                       | 3A0h |                                       |

|      | Purpose<br>Register           | 0BFh<br>0C0h | 32 Bytes                              |      | Unimplemented<br>Read as '0'          |

|      | 80 Bytes                      | 00011        | Unimplemented<br>Read as '0'          |      |                                       |      |                                       |      |                                       |      |                                       |      |                                       |      |                                       |

| 06Fh |                               | 0EFh         |                                       | 16Fh |                                       | 1EFh |                                       | 26Fh |                                       | 2EFh |                                       | 36Fh |                                       | 3EFh |                                       |

| 070h | Common RAM                    | 0F0h         | Common RAM<br>(Accesses<br>70h – 7Fh) | 170h | Common RAM<br>(Accesses<br>70h – 7Fh) | 1F0h | Common RAM<br>(Accesses<br>70h – 7Fh) | 270h | Common RAM<br>(Accesses<br>70h – 7Fh) | 2F0h | Common RAM<br>(Accesses<br>70h – 7Fh) | 370h | Common RAM<br>(Accesses<br>70h – 7Fh) | 3F0h | Common RAM<br>(Accesses<br>70h – 7Fh) |

| 07Fh |                               | 0FFh         |                                       | 17Fh |                                       | 1FFh |                                       | 27Fh |                                       | 2FFh |                                       | 37Fh |                                       | 3FFh |                                       |

Legend:= Unimplemented data memory locations, read as '0'.Note1:PIC16F1512 only.

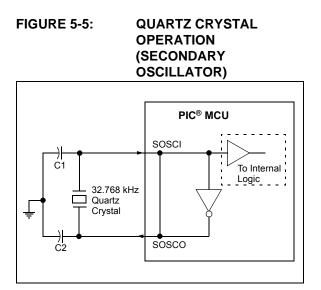

### 5.2.1.4 Secondary Oscillator

The secondary oscillator is a separate crystal oscillator that is associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator can be used as an alternate system clock source and can be selected during run-time using clock switching. Refer to **Section 5.3 "Clock Switching"** for more information.

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949)

- TB097, Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS (DS91097)

- AN1288, Design Practices for Low-Power External Oscillators (DS01288)

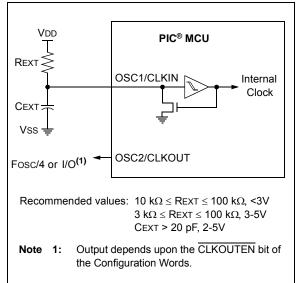

## 5.2.1.5 External RC Mode

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

Figure 5-6 shows the external RC mode connections.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of the external RC components used.

#### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Section 25.0 "Electrical Specifications" for the LFINTOSC tolerances.

#### WDT Operating Modes 10.2

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### WDT CONTROLLED BY SOFTWARE 10.2.3

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-2 for more details.

| TABLE 10-1: WDI OPERATING MODES | TABLE 10-1: | WDT OPERATING MODES |

|---------------------------------|-------------|---------------------|

|---------------------------------|-------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | v      | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 01        | 1      | х              | Active      |

| 01        | 0      | ^              | Disabled    |

| 00        | Х      | Х              | Disabled    |

#### **TABLE 10-2:** WDT CLEARING CONDITIONS

Conditions

#### 10.3 **Time-Out Period**

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 10.4 **Clearing the WDT**

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

#### 10.5 **Operation During Sleep**

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. See Section 3.0 "Memory Organization" and The STATUS register (Register 3-1) for more information.

| Conditions                                              | VVD1                         |  |  |  |

|---------------------------------------------------------|------------------------------|--|--|--|

| WDTE<1:0> = 00                                          |                              |  |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                           | Cleared                      |  |  |  |

| WDTE<1:0> = 10 and enter Sleep                          |                              |  |  |  |

| CLRWDT Command                                          | Cleared                      |  |  |  |

| Oscillator Fail Detected                                |                              |  |  |  |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |  |  |  |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |  |  |  |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |  |  |  |

wпт

# 10.6 Watchdog Control Register

## REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0            | U-0                      | R/W-0/0                                                                                    | R/W-1/1                | R/W-0/0          | R/W-1/1          | R/W-1/1         | R/W-0/0      |  |

|----------------|--------------------------|--------------------------------------------------------------------------------------------|------------------------|------------------|------------------|-----------------|--------------|--|

|                | —                        |                                                                                            |                        | WDTPS<4:02       | >                |                 | SWDTEN       |  |

| oit 7          |                          |                                                                                            |                        |                  |                  |                 | bit          |  |

|                |                          |                                                                                            |                        |                  |                  |                 |              |  |

| _egend:        |                          |                                                                                            |                        |                  |                  |                 |              |  |

| R = Readab     | ole bit                  | W = Writable                                                                               | bit                    | U = Unimpler     | nented bit, read | d as '0'        |              |  |

| u = Bit is un  | changed                  | x = Bit is unki                                                                            | nown                   | -m/n = Value     | at POR and BO    | DR/Value at all | other Resets |  |

| '1' = Bit is s | et                       | '0' = Bit is cle                                                                           | ared                   |                  |                  |                 |              |  |

| bit 7-6        | Unimpleme                | <b>nted:</b> Read as '                                                                     | ٥'                     |                  |                  |                 |              |  |

| bit 5-1        | -                        | Unimplemented: Read as '0'<br>WDTPS<4:0>: Watchdog Timer Period Select bits <sup>(1)</sup> |                        |                  |                  |                 |              |  |

|                |                          | Prescale Rate                                                                              |                        |                  |                  |                 |              |  |

|                |                          | leserved. Result                                                                           | e in minimum           | interval (1·32)  |                  |                 |              |  |

|                | • ·                      |                                                                                            | 5 11 1 11111111111UIII | 11.32)           |                  |                 |              |  |

|                | •                        |                                                                                            |                        |                  |                  |                 |              |  |

|                | •                        |                                                                                            |                        |                  |                  |                 |              |  |

|                | 10011 = R                | eserved. Result                                                                            | s in minimum           | interval (1:32)  |                  |                 |              |  |

|                | 10010 <b>= 1</b>         | :8388608 (2 <sup>23</sup> ) (                                                              | Interval 256s          | nominal)         |                  |                 |              |  |

|                |                          | :4194304 (2 <sup>22</sup> ) (                                                              |                        |                  |                  |                 |              |  |

|                | 10000 = 1                | :2097152 (2 <sup>21</sup> ) (                                                              | Interval 64s n         | ominal)          |                  |                 |              |  |

|                | 01111 = 1                | :1048576 (2 <sup>20</sup> ) (                                                              | Interval 32s n         | ominal)          |                  |                 |              |  |

|                | 01110 = 1                | :524288 (2 <sup>19</sup> ) (Ir<br>:262144 (2 <sup>18</sup> ) (Ir                           | iterval 165 no         | minal)<br>vinal) |                  |                 |              |  |

|                | 01101 = 1<br>01100 = 1   | :131072 (2 <sup>17</sup> ) (Ir                                                             | iterval 4s non         | ninal)           |                  |                 |              |  |

|                |                          | :65536 (Interval                                                                           |                        | ,                |                  |                 |              |  |

|                |                          | :32768 (Interval                                                                           | ,                      | ,                |                  |                 |              |  |

|                | 01001 = 1                | :16384 (Interval                                                                           | 512 ms nomir           | nal)             |                  |                 |              |  |

|                |                          | :8192 (Interval 2                                                                          |                        |                  |                  |                 |              |  |

|                |                          | :4096 (Interval 1                                                                          |                        | -                |                  |                 |              |  |

|                |                          | :2048 (Interval 6<br>:1024 (Interval 3                                                     |                        | ,                |                  |                 |              |  |

|                |                          | :512 (Interval 16                                                                          |                        | )                |                  |                 |              |  |

|                |                          | :256 (Interval 8 i                                                                         | ,                      |                  |                  |                 |              |  |

|                |                          | :128 (Interval 4 ı                                                                         |                        |                  |                  |                 |              |  |

|                |                          | :64 (Interval 2 m                                                                          |                        |                  |                  |                 |              |  |

|                | 00000 = 1                | :32 (Interval 1 m                                                                          | s nominal)             |                  |                  |                 |              |  |

| bit 0          | SWDTEN: S                | Software Enable                                                                            | /Disable for W         | atchdog Timer    | bit              |                 |              |  |

|                | If WDTE<1:               |                                                                                            |                        |                  |                  |                 |              |  |

|                | This bit is ig           |                                                                                            |                        |                  |                  |                 |              |  |

|                | If WDTE<1:               |                                                                                            |                        |                  |                  |                 |              |  |

|                | 1 = WDT is<br>0 = WDT is |                                                                                            |                        |                  |                  |                 |              |  |

|                | If WDTE<1:               |                                                                                            |                        |                  |                  |                 |              |  |

|                | This bit is ig           |                                                                                            |                        |                  |                  |                 |              |  |

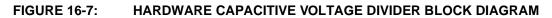

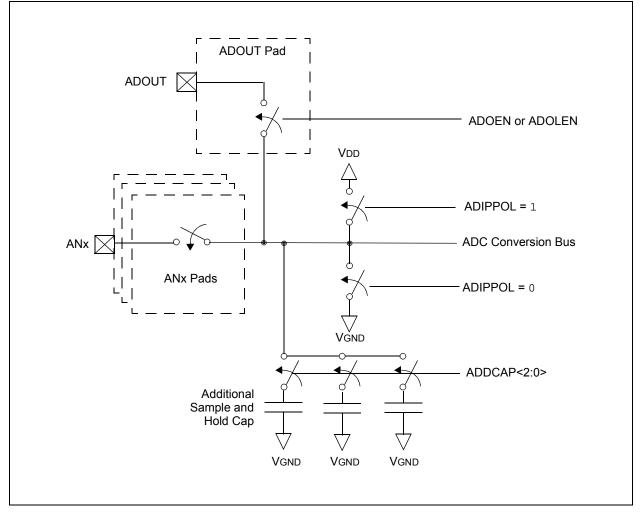

## 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the same instruction that turns on the ADC. |

|-------|----------------------------------------------------------------------------------|

|       |                                                                                  |

|       | Refer to Section 16.2.6 "A/D Conver-                                             |

|       | sion Procedure".                                                                 |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger allows periodic ADC measurements without software intervention, using the TRIGSEL bits of the AADCON2 register. When this trigger occurs, the GO/DONE bit is set by hardware from one of the following sources:

- CCP1

- CCP2

- Timer0 Overflow

- · Timer1 Overflow

- Timer2 Match to PR2

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device          | Source                       |  |  |  |

|-----------------|------------------------------|--|--|--|

| PIC16(L)F1512/3 | CCP1, CCP2, TMR0, TMR1, TMR2 |  |  |  |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 21.0 "Capture/Compare/PWM Modules", Section 17.0 "Timer0 Module", Section 18.0 "Timer1 Module with Gate Control", and Section 19.0 "Timer2 Module" for more information.

| U-0                                   | U-0                                                    | U-0                                                                                               | U-0                                             | U-0            | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|---------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------|------------------|----------------|--------------|

|                                       |                                                        |                                                                                                   | _                                               | —              | ADCONV           | ADST           | G<1:0>       |

| bit 7                                 |                                                        |                                                                                                   |                                                 |                |                  |                | bit C        |

| Legend:                               |                                                        |                                                                                                   |                                                 |                |                  |                |              |

| R = Readal                            | ble bit                                                | W = Writable                                                                                      | oit                                             | U = Unimpler   | nented bit, read | as '0'         |              |

| u = Bit is unchanged x = Bit is un    |                                                        |                                                                                                   | own                                             | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set '0' = Bit is cleared |                                                        |                                                                                                   |                                                 |                |                  |                |              |

| bit 7-3<br>bit 2<br>bit 1-0           | ADCONV: AI<br>1 = Indicates<br>0 = Indicates<br>GO/DON | nted: Read as '<br>DC Conversion<br>s ADC in Conve<br>s ADC in Conve<br>NE = 0)<br>>: ADC Stage S | Status bit<br>rsion Sequenc<br>rsion Sequenc    |                |                  |                | 0' when      |

|                                       | 11 = ADC n<br>10 = ADC n<br>01 = ADC n                 | nodule is in con<br>nodule is in acq<br>nodule is in pre-<br>nodule is not co                     | version stage<br>uisition stage<br>charge stage | e as GO/DONE   | = 0)             |                |              |

## REGISTER 16-11: AADSTAT: HARDWARE CVD STATUS REGISTER

### REGISTER 16-12: AADPRE: HARDWARE CVD PRE-CHARGE CONTROL REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| —     |         |         |         | ADPRE<6:0> |         |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | Unimplemented: Read as '0'                                                                           |

|---------|------------------------------------------------------------------------------------------------------|

| bit 6-0 | ADPRE<6:0>: Pre-charge Time Select bits <sup>(1)</sup>                                               |

|         | 111 1111 = Pre-charge for 127 instruction cycles                                                     |

|         | 111 1110 = Pre-charge for 126 instruction cycles                                                     |

|         | •                                                                                                    |

|         | •                                                                                                    |

|         | 000 0001 = Pre-charge for 1 instruction cycle (Fosc/4)<br>000 0000 = ADC pre-charge time is disabled |

**Note 1:** When the FRC clock is selected as the conversion clock source, it is also the clock used for the pre-charge and acquisition times.

#### 18.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 18.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 18.6.2.3 Timer2 Match PR2 Operation

When Timer2 increments and matches PR2, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 18.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 18-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

#### 18.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 18-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 18-6 for timing details.

#### 18.6.5 TIMER1 GATE VALUE STATUS

When Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 18.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 gate event interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# 18.11 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 18-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 18-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u         | R/W-0/u                                          | R/W-0/u                                                                                            | R/W-0/u                      | R/W-0/u         | R/W-0/u          | U-0            | R/W-0/u      |  |  |  |  |

|-----------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------|-----------------|------------------|----------------|--------------|--|--|--|--|

| TMR             | TMR1CS<1:0>                                      |                                                                                                    | S<1:0>                       | T1OSCEN         | T1SYNC           | _              | TMR10N       |  |  |  |  |

| bit 7           |                                                  | ·                                                                                                  |                              |                 |                  |                | bit 0        |  |  |  |  |

|                 |                                                  |                                                                                                    |                              |                 |                  |                |              |  |  |  |  |

| Legend:         |                                                  |                                                                                                    |                              |                 |                  |                |              |  |  |  |  |

| R = Readab      | le bit                                           | W = Writable I                                                                                     | oit                          | U = Unimplem    | nented bit, read | as '0'         |              |  |  |  |  |

| u = Bit is un   | changed                                          | x = Bit is unkn                                                                                    | own                          | -n/n = Value a  | t POR and BO     | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is se | et                                               | '0' = Bit is clea                                                                                  | ared                         |                 |                  |                |              |  |  |  |  |

| bit 7-6         | 11 = Timer1<br>10 = Timer1<br><u>If T1OS</u>     | <b>0&gt;:</b> Timer1 Cloc<br>clock source is I<br>clock source is I<br><u>CEN = 0</u> :            | LFINTOSC<br>pin or oscillate | or:             |                  |                |              |  |  |  |  |

|                 | <u>If T1OS</u><br>Crystal<br>01 = Timer <b>1</b> | I clock from T10<br><u>CEN = 1</u> :<br>oscillator on SO<br>clock source is s<br>clock source is i | SCI/SOSCO<br>system clock (  | pins<br>(Fosc)  |                  |                |              |  |  |  |  |

| bit 5-4         | T1CKPS<1:0                                       | <b>)&gt;:</b> Timer1 Input                                                                         | t Clock Presca               | ale Select bits |                  |                |              |  |  |  |  |

|                 | 11 = 1:8 Pres<br>10 = 1:4 Pres<br>01 = 1:2 Pres  | scale value                                                                                        |                              |                 |                  |                |              |  |  |  |  |

|                 | 00 = 1:1 Pre                                     | scale value                                                                                        |                              |                 |                  |                |              |  |  |  |  |

| bit 3           | T1OSCEN: L                                       | P Oscillator En                                                                                    | able Control b               | oit             |                  |                |              |  |  |  |  |

|                 |                                                  | ary oscillator circ<br>ary oscillator circ                                                         |                              |                 |                  |                |              |  |  |  |  |

| bit 2           |                                                  | ner1 External C                                                                                    |                              |                 | ontrol bit       |                |              |  |  |  |  |

| 511 -           | TMR1CS<1:                                        |                                                                                                    | look input oyi               |                 |                  |                |              |  |  |  |  |

|                 | 1 = Do not s                                     | 1 = Do not synchronize external clock input                                                        |                              |                 |                  |                |              |  |  |  |  |

|                 | 0 = Synchro                                      | nize external clo                                                                                  | ock input with               | system clock (F | osc)             |                |              |  |  |  |  |

|                 | TMR1CS<1:0                                       | 0>= 0x                                                                                             |                              |                 |                  |                |              |  |  |  |  |

|                 | This bit is ign                                  | ored. Timer1 us                                                                                    | ses the interna              | al clock when T | MR1CS<1:0> =     | 0X.            |              |  |  |  |  |

| bit 1           | Unimplemer                                       | nted: Read as '                                                                                    | י'                           |                 |                  |                |              |  |  |  |  |

| bit 0           | TMR1ON: Ti                                       | mer1 On bit                                                                                        |                              |                 |                  |                |              |  |  |  |  |

|                 | 1 = Enables                                      | -                                                                                                  |                              |                 |                  |                |              |  |  |  |  |

|                 | 0 = Stops Til<br>Clears T                        | mer1                                                                                               |                              |                 |                  |                |              |  |  |  |  |

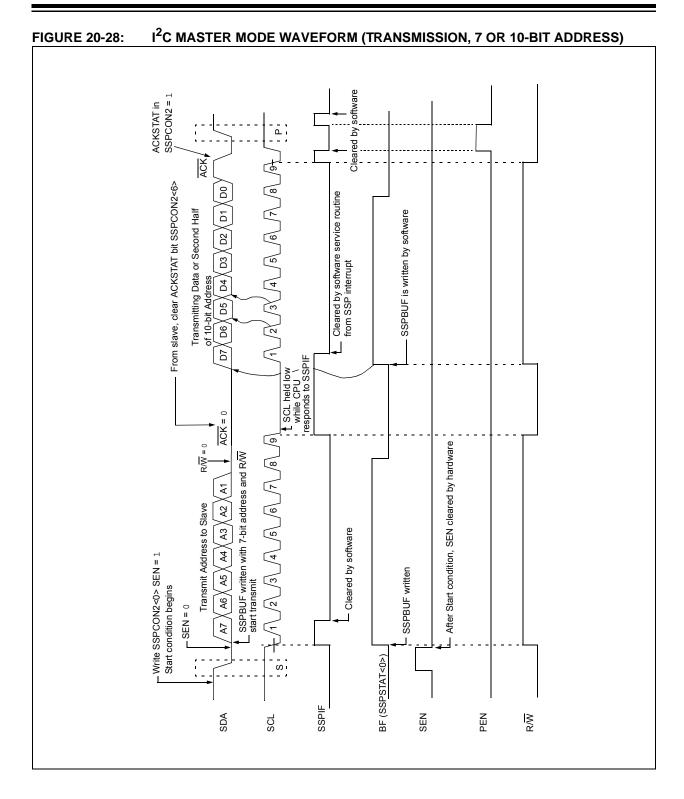

## 20.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overrightarrow{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCL on the bus, the ACKTIM bit of the SSPCON3 register is set. The ACKTIM bit indicates the Acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

## 20.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected in the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 20.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 20-7) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes Idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 20-6) affects the address matching process. See **Section 20.5.9** "**SSP Mask Register**" for more information.

#### 20.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

## 20.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

| Name    | Bit 7      | Bit 6           | Bit 5          | Bit 4          | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|------------|-----------------|----------------|----------------|--------|--------|--------|--------|----------------------------|

| INTCON  | GIE        | PEIE            | TMR0IE         | INTE           | IOCIE  | TMR0IF | INTF   | IOCIF  | 69                         |

| PIE1    | TMR1GIE    | ADIE            | RCIE           | TXIE           | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 70                         |

| PIE2    | OSFIE      | _               | _              | _              | BCLIE  | —      | _      | CCP2IE | 71                         |

| PIR1    | TMR1GIF    | ADIF            | RCIF           | TXIF           | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 72                         |

| PIR2    | OSFIF      | _               | _              | _              | BCLIF  | —      | _      | CCP2IF | 73                         |

| SSPADD  |            |                 |                | ADD<           | :7:0>  |        |        |        | 227                        |

| SSPBUF  | Synchronou | s Serial Port F | Receive Buffer | r/Transmit Reg | gister |        |        |        | 179*                       |

| SSPCON1 | WCOL       | SSPOV           | SSPEN          | CKP            |        | SSPM   | <3:0>  |        | 224                        |

| SSPCON2 | GCEN       | ACKSTAT         | ACKDT          | ACKEN          | RCEN   | PEN    | RSEN   | SEN    | 225                        |

| SSPCON3 | ACKTIM     | PCIE            | SCIE           | BOEN           | SDAHT  | SBCDE  | AHEN   | DHEN   | 226                        |

| SSPMSK  | MSK7       | MSK6            | MSK5           | MSK4           | MSK3   | MSK2   | MSK1   | MSK0   | 227                        |

| SSPSTAT | SMP        | CKE             | D/A            | Р              | S      | R/W    | UA     | BF     | 223                        |

| TRISA   | TRISA7     | TRISA6          | TRISA5         | TRISA4         | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 103                        |

# TABLE 20-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in I<sup>2</sup>C mode. \*

Page provides register information.

## 21.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

## 21.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

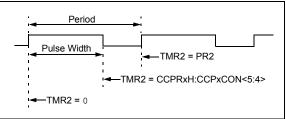

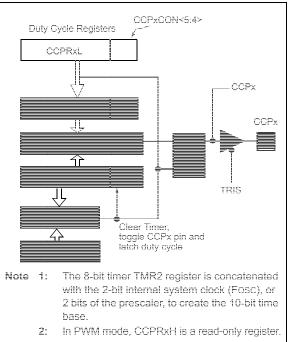

## 21.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 21-3 shows a typical waveform of the PWM signal.

## 21.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- · PR2 registers

- T2CON registers

- CCPRxL registers

- · CCPxCON registers

Figure 21-4 shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinguish control of the CCPx pin.

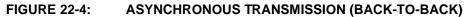

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 249                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 69                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 70                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 72                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 248                 |

| SPBRGL  |                               |        |        | BRG    | <7:0>  |        |        |        | 250*                |

| SPBRGH  |                               |        |        | BRG<   | :15:8> |        |        |        | 250*                |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 110                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        |        |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 247                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for asynchronous transmission.

\* Page provides register information.

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0) | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                         |     |

|-----------------------------------------|-------------------------------------------------------------------------|-----|

| TX/CK pin                               |                                                                         |     |

| bit SREN                                |                                                                         | ʻ0' |

| RCIF bit<br>(Interrupt) ————<br>Read    |                                                                         |     |

| RCREG                                   | agram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |     |

## FIGURE 22-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

# TABLE 22-7: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION RECEPTION

| Name    | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|---------|--------|--------|------------|------------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF  | RCIDL  | _      | SCKP       | BRG16      | _      | WUE    | ABDEN  | 249                 |

| INTCON  | GIE     | PEIE   | TMR0IE | INTE       | IOCIE      | TMR0IF | INTF   | IOCIF  | 69                  |

| PIE1    | TMR1GIE | ADIE   | RCIE   | TXIE       | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 70                  |

| PIR1    | TMR1GIF | ADIF   | RCIF   | TXIF       | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 72                  |

| RCREG   |         |        | EUS    | ART Receiv | e Data Reg | gister |        |        | 242*                |

| RCSTA   | SPEN    | RX9    | SREN   | CREN       | ADDEN      | FERR   | OERR   | RX9D   | 248                 |

| SPBRGL  |         |        |        | BRG        | <7:0>      |        |        |        | 250*                |

| SPBRGH  |         |        |        | BRG<       | :15:8>     |        |        |        | 250*                |

| TRISC   | TRISC7  | TRISC6 | TRISC5 | TRISC4     | TRISC3     | TRISC2 | TRISC1 | TRISC0 | 110                 |

| TXSTA   | CSRC    | TX9    | TXEN   | SYNC       | SENDB      | BRGH   | TRMT   | TX9D   | 247                 |

| TXSTA   | CSRC    | TX9    | TXEN   | SYNC       | SENDB      | BRGH   | TRMT   | TX9D   | 247                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

## TABLE 25-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2,4)</sup>

| PIC16LF1  | 512/3                  | Standard Operating Conditions (unless otherwise stated) |      |       |        |       |            |                                    |  |  |  |  |

|-----------|------------------------|---------------------------------------------------------|------|-------|--------|-------|------------|------------------------------------|--|--|--|--|

| PIC16F151 | 12/3                   |                                                         |      |       |        |       |            |                                    |  |  |  |  |

| Param     | Device Characteristics | Min.                                                    | Turt | Max.  | Max.   | Units | Conditions |                                    |  |  |  |  |

| No.       | Device Characteristics | win.                                                    | Тур† | +85°C | +125°C | Units | Vdd        | Note                               |  |  |  |  |

| D022      |                        | _                                                       | 0.02 | 1.0   | 8.0    | μA    | 1.8        | WDT, BOR, FVR, and SOSC            |  |  |  |  |

|           |                        | —                                                       | 0.03 | 2.0   | 9.0    | μA    | 3.0        | disabled, all Peripherals Inactive |  |  |  |  |

| D022      |                        |                                                         | 0.20 | 3.0   | 11     | μA    | 2.3        | WDT, BOR, FVR, and SOSC            |  |  |  |  |

|           |                        |                                                         | 0.30 | 4.0   | 12     | μA    | 3.0        | disabled, all Peripherals Inactive |  |  |  |  |

|           |                        | —                                                       | 0.40 | 6     | 15     | μA    | 5.0        |                                    |  |  |  |  |

| D023      |                        | —                                                       | 0.30 | 6     | 14     | μA    | 1.8        | LPWDT Current                      |  |  |  |  |

|           |                        | -                                                       | 0.60 | 7     | 17     | μA    | 3.0        |                                    |  |  |  |  |

| D023      |                        | —                                                       | 0.50 | 6     | 15     | μA    | 2.3        | LPWDT Current                      |  |  |  |  |

|           |                        | —                                                       | 0.77 | 7     | 20     | μA    | 3.0        |                                    |  |  |  |  |

|           |                        | —                                                       | 0.85 | 8     | 22     | μA    | 5.0        |                                    |  |  |  |  |

| D023A     |                        | —                                                       | 10   | 28    | 30     | μA    | 1.8        | FVR current                        |  |  |  |  |

|           |                        | —                                                       | 12   | 30    | 33     | μA    | 3.0        |                                    |  |  |  |  |

| D023A     |                        | —                                                       | 18   | 33    | 35     | μA    | 2.3        | FVR current                        |  |  |  |  |

|           |                        | —                                                       | 19   | 36    | 37     | μA    | 3.0        | 1                                  |  |  |  |  |

|           |                        | —                                                       | 20   | 37    | 45     | μA    | 5.0        | 1                                  |  |  |  |  |

| D024      |                        | —                                                       | 8.0  | 17    | 20     | μA    | 3.0        | BOR Current                        |  |  |  |  |

| D024      |                        | —                                                       | 8    | 17    | 30     | μA    | 3.0        | BOR Current                        |  |  |  |  |

|           |                        |                                                         | 9    | 20    | 40     | μA    | 5.0        | 7                                  |  |  |  |  |

| D024A     |                        | _                                                       | 0.80 | 4     | 8      | μA    | 3.0        | LPBOR Current                      |  |  |  |  |

| D024A     |                        | _                                                       | 0.30 | 4     | 14     | μA    | 3.0        | LPBOR Current                      |  |  |  |  |

|           |                        | _                                                       | 0.45 | 8     | 17     | μA    | 5.0        | 1                                  |  |  |  |  |

| D025      |                        | _                                                       | 0.6  | 5     | 9      | μA    | 1.8        | SOSC Current                       |  |  |  |  |

|           |                        | _                                                       | 2.5  | 8.5   | 12     | μA    | 3.0        |                                    |  |  |  |  |

| D025      |                        | —                                                       | 1    | 6     | 10     | μA    | 2.3        | SOSC Current                       |  |  |  |  |

|           |                        | _                                                       | 2.2  | 8.5   | 20     | μA    | 3.0        |                                    |  |  |  |  |

|           |                        | _                                                       | 5.5  | 15    | 25     | μA    | 5.0        |                                    |  |  |  |  |

| D026      |                        | _                                                       | 0.1  | 1.5   | 9      | μA    | 1.8        | A/D Current (Note 3),              |  |  |  |  |

|           |                        | _                                                       | 0.2  | 2.7   | 10     | μA    | 3.0        | no conversion in progress          |  |  |  |  |

| D026      |                        | _                                                       | 0.3  | 4     | 11     | μA    | 2.3        | A/D Current (Note 3),              |  |  |  |  |

|           |                        | _                                                       | 0.35 | 5     | 13     | μΑ    | 3.0        | no conversion in progress          |  |  |  |  |

|           |                        | _                                                       | 0.45 | 8     | 16     | μA    | 5.0        |                                    |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

**3:** A/D oscillator source is FRC.

4: Specification for PIC16F1512/3 devices assumes that Low-Power Sleep mode is selected, when available, via the VREGCON register (see Section 8.2.2 "Peripheral Usage in Sleep" and Register 8-1).

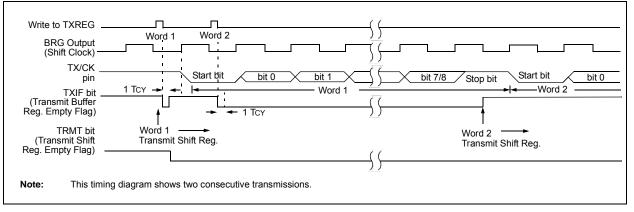

### FIGURE 25-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### TABLE 25-10: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Standa       | rd Operating   | g Conditions (u           | Inless otherwi                                             | se stated)          |                                           |            |        |       |                                    |

|--------------|----------------|---------------------------|------------------------------------------------------------|---------------------|-------------------------------------------|------------|--------|-------|------------------------------------|

| Param<br>No. | Sym.           |                           | Characterist                                               | ic                  | Min.                                      | Тур†       | Max.   | Units | Conditions                         |

| 40*          | Тт0Н           | T0CKI High I              | Pulse Width No Prescaler                                   |                     | 0.5 Tcy + 20                              | —          | _      | ns    |                                    |

|              |                |                           |                                                            | With Pres-<br>caler | 10                                        | —          | —      | ns    |                                    |

| 41*          | TT0L           | T0CKI Low F               | ulse Width                                                 | No Prescaler        | 0.5 Tcy + 20                              | —          | —      | ns    |                                    |

|              |                |                           |                                                            | With Pres-<br>caler | 10                                        | —          | —      | ns    |                                    |

| 42*          | T⊤0P           | T0CKI Period              | ł                                                          | ·                   | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —          | —      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H           | T1CKI High                | Synchronous,                                               | No Prescaler        | 0.5 Tcy + 20                              | —          | _      | ns    |                                    |

|              |                |                           | Synchronous, with Prescaler                                |                     | 15                                        | —          | —      | ns    |                                    |

|              |                |                           | Asynchronous                                               | 6                   | 30                                        | _          | _      | ns    |                                    |

| 46*          | T⊤1L           | T1CKI Low                 | Synchronous,                                               | No Prescaler        | 0.5 Tcy + 20                              | _          | —      | ns    |                                    |

|              |                | Time                      | Synchronous,                                               | with Prescaler      | 15                                        | _          | —      | ns    |                                    |

|              |                |                           | Asynchronous                                               | ;                   | 30                                        | _          | —      | ns    |                                    |

| 47*          | T⊤1P           | T1CKI Input<br>Period     | Synchronous                                                |                     | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —          | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |                |                           | Asynchronous                                               |                     | 60                                        | _          | _      | ns    |                                    |

| 48           | FT1            | Range                     | scillator Input Frequency<br>abled by setting bit T1OSCEN) |                     | 32.4                                      | 32.76<br>8 | 33.1   | kHz   |                                    |

| 49*          | TCKEZT-<br>MR1 | Delay from E<br>Increment | xternal Clock E                                            | Edge to Timer       | 2 Tosc                                    |            | 7 Tosc |       | Timers in Sync<br>mode             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

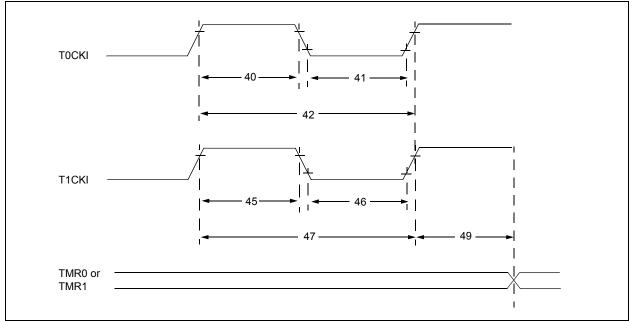

### FIGURE 25-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

## TABLE 25-11: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standa       | rd Opei | ating Conditions (unless |                |                       |      |      |       |                                 |

|--------------|---------|--------------------------|----------------|-----------------------|------|------|-------|---------------------------------|

| Param<br>No. | Sym.    | Characteri               | stic           | Min.                  | Тур† | Max. | Units | Conditions                      |

| CC01*        | TccL    | CCP Input Low Time       | No Prescaler   | 0.5Tcy + 20           | —    | —    | ns    |                                 |

|              |         |                          | With Prescaler | 20                    |      |      | ns    |                                 |

| CC02*        | TccH    | CCP Input High Time      | No Prescaler   | 0.5Tcy + 20           |      |      | ns    |                                 |

|              |         |                          | With Prescaler | 20                    | —    | _    | ns    |                                 |

| CC03*        | TccP    | CCP Input Period         |                | <u>3Tcy + 40</u><br>N | —    | —    | ns    | N = prescale value (1, 4 or 16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## TABLE 25-12: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3)</sup>

## Standard Operating Conditions (unless otherwise stated)

| VDD = 3.     | •    | = 25°C                                            | o olulo | u)   |       |           |                                 |

|--------------|------|---------------------------------------------------|---------|------|-------|-----------|---------------------------------|