#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

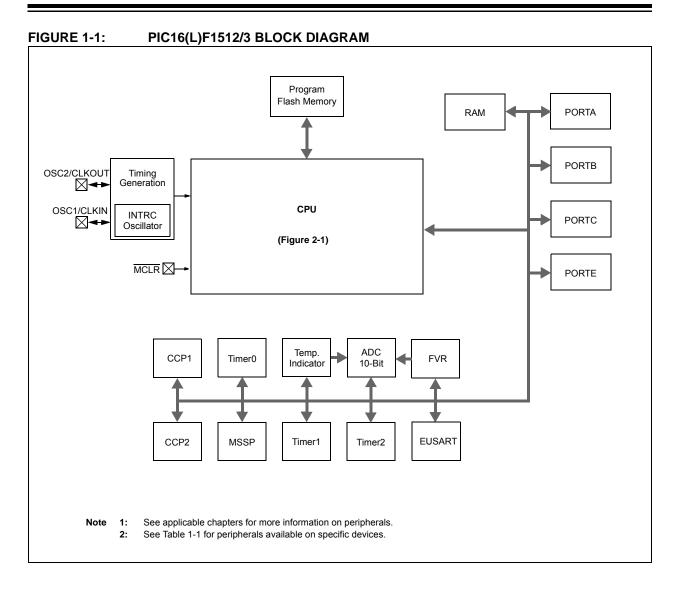

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

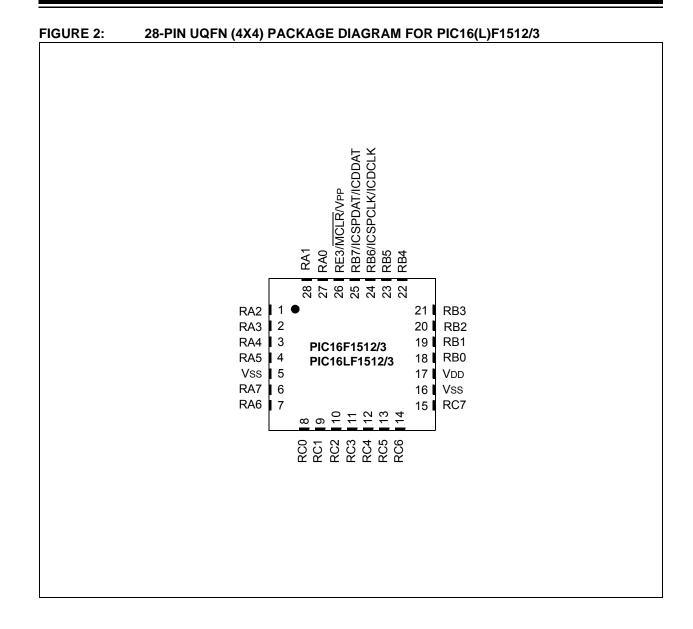

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1513-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

# $INTOSC \longrightarrow for the second seco$

#### FIGURE 5-8: TWO-SPEED START-UP

## 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

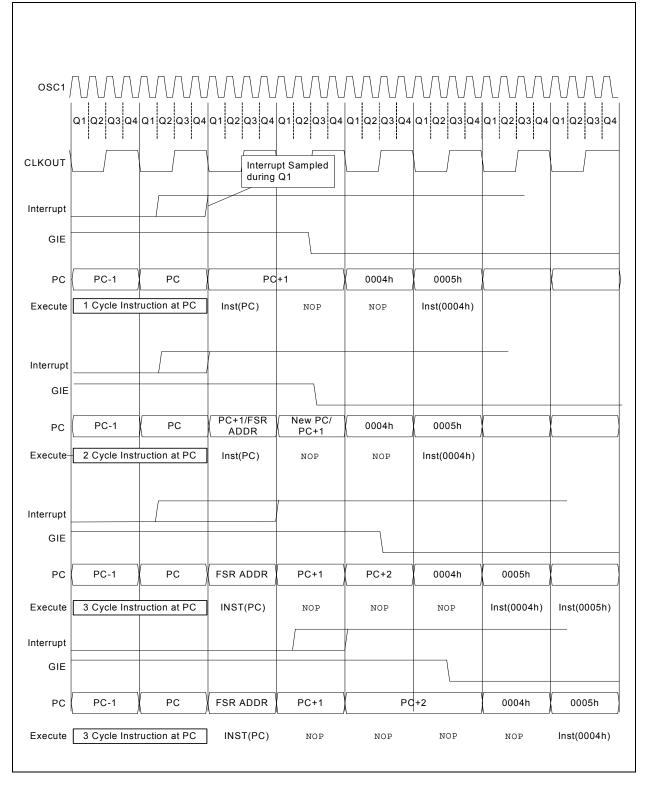

# 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 8.0 "Power-Down Mode (Sleep)" for more details.

# 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

# 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|--------|---------|---------|---------------------|

| ANSELA     |        |        | ANSA5  | _      | ANSA3  | ANSA2  | ANSA1   | ANSA0   | 104                 |

| APFCON     | _      | _      | —      | _      | _      | —      | SSSEL   | CCP2SEL | 101                 |

| LATA       | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1   | LATA0   | 104                 |

| OPTION_REG | WPUEN  | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |         | 159                 |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1     | RA0     | 103                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0  | 103                 |

#### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2    | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|-------------|---------|---------|---------------------|

| CONFIG1 | 13:8 | _       |         | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0.> |         | _       | 37                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | FOSC<2:0>   |         |         | 37                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

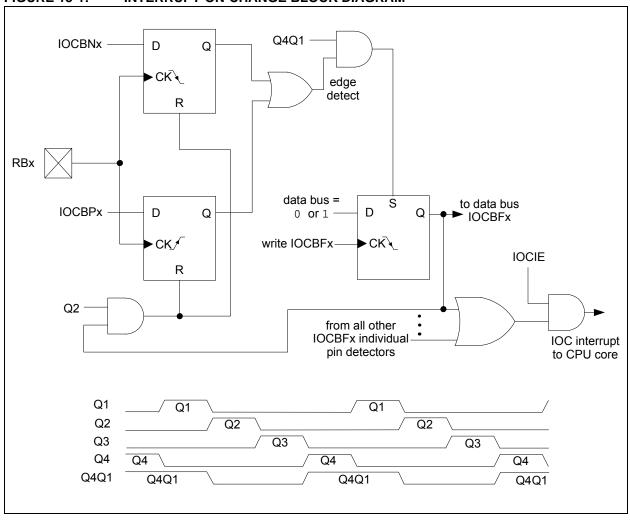

# 12.3 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-7). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 12-6) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

The TRISB register (Register 12-7) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.3.1 ANSELB REGISTER

The ANSELB register (Register 12-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 12.3.2 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority. Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 12-5.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RB0      | RB0                              |

| RB1      | RB1                              |

| RB2      | RB2                              |

| RB3      | CCP2<br>RB3                      |

| RB4      | RB4                              |

| RB5      | RB5                              |

| RB6      | ICDCLK<br>RB6                    |

| RB7      | ICDDAT<br>RB7                    |

## TABLE 12-5: PORTB OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

# **15.4 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

#### TABLE 15-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | _     | _     | ADFVF | R<1:0> | 120                 |

Legend: Shaded cells are unused by the temperature indicator module.

| REGISTER         |                                                                                           | R/W-0/0                                                                                          | R/W-0/0          | U-0                  | U-0              | R/W-0/0            | R/W-0/0      |

|------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------|----------------------|------------------|--------------------|--------------|

| ADFM             | N/W-0/0                                                                                   | ADCS<2:0>                                                                                        | R/W-0/U          | 0-0                  | 0-0              |                    | EF<1:0>      |

| bit 7            |                                                                                           | AD00 \2.02                                                                                       |                  |                      |                  |                    | bit C        |

|                  |                                                                                           |                                                                                                  |                  |                      |                  |                    |              |

| Legend:          |                                                                                           |                                                                                                  |                  |                      |                  |                    |              |

| R = Readab       | ole bit                                                                                   | W = Writable bit                                                                                 |                  | U = Unimpler         | nented bit, read | d as '0'           |              |

| u = Bit is un    | changed                                                                                   | x = Bit is unknow                                                                                | wn               | -n/n = Value a       | at POR and BC    | R/Value at all     | other Resets |

| '1' = Bit is s   | et                                                                                        | '0' = Bit is cleare                                                                              | ed               |                      |                  |                    |              |

| bit 7<br>bit 6-4 | 1 = Right-ju<br>loaded<br>0 = Left-jus<br>loaded<br>ADCS<2:0:<br>000 = FOS0<br>001 = FOS0 | stified. Six Least Si<br>/2<br>/8                                                                | ignificant bi    | ts of ADRESL a       |                  |                    |              |

|                  | 100 = Fos<br>101 = Fos<br>110 = Fos                                                       | (clock supplied from<br>c/4<br>c/16                                                              |                  |                      |                  |                    |              |

| bit 3-2          | Unimpleme                                                                                 | ented: Read as '0'                                                                               |                  |                      |                  |                    |              |

| bit 1-0          | 00 = VREF<br>01 = Reser<br>10 = VREF                                                      | :0>: A/D Positive \<br>is connected to Vol<br>ved<br>is connected to ext<br>is connected to inte | o<br>ernal VREF+ | - pin <sup>(1)</sup> |                  | ule <sup>(1)</sup> |              |

|                  |                                                                                           | the FVR or the VRE<br>e specification exist                                                      |                  |                      |                  |                    |              |

# REGISTER 16-2: ADCON1: A/D CONTROL REGISTER 1

## REGISTER 16-3: ADRES0H: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

|                  |         |                    |         |                                                    | /       | -       |         |  |

|------------------|---------|--------------------|---------|----------------------------------------------------|---------|---------|---------|--|

| R/W-x/u          | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u                                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|                  |         |                    | ADRE    | S<9:2>                                             |         |         |         |  |

| bit 7            |         |                    |         |                                                    |         |         | bit 0   |  |

|                  |         |                    |         |                                                    |         |         |         |  |

| Legend:          |         |                    |         |                                                    |         |         |         |  |

| R = Readable     | bit     | W = Writable bi    | it      | U = Unimplemented bit, read as '0'                 |         |         |         |  |

| u = Bit is unch  | anged   | x = Bit is unkno   | wn      | -n/n = Value at POR and BOR/Value at all other Res |         |         |         |  |

| '1' = Bit is set |         | '0' = Bit is clear | ed      |                                                    |         |         |         |  |

|                  |         |                    |         |                                                    |         |         |         |  |

bit 7-0 **ADRES<9:2>:** ADC Result Register bits Upper eight bits of 10-bit conversion result

# **REGISTER 16-4:** ADRESOL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | S<1:0>  | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits

Lower two bits of 10-bit conversion result

bit 5-0 Reserved: Do not use.

| TABLE 10-3. SOMMART OF REGISTERS ASSOCIATED WITH ADD |              |               |             |        |        |        |        |        |                     |  |

|------------------------------------------------------|--------------|---------------|-------------|--------|--------|--------|--------|--------|---------------------|--|

| Name                                                 | Bit 7        | Bit 6         | Bit 5       | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

| ADCON0                                               | —            |               | CHS<4:0>    |        |        |        |        | ADON   | 130                 |  |

| ADCON1                                               | ADFM         |               | ADCS<2:0> — |        |        |        | ADPRE  | 131    |                     |  |

| ADRES0H                                              | A/D Result I | Register High |             |        |        |        |        |        | 132, 133            |  |

| ADRES0L                                              | A/D Result I | Register Low  |             |        |        |        |        |        | 132, 133            |  |

| ANSELA                                               | —            | _             | ANSA5       | —      | ANSA3  | ANSA2  | ANSA1  | ANSA0  | 104                 |  |

| ANSELB                                               | —            | —             | ANSB5       | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 108                 |  |

| ANSELC                                               | ANSC7        | ANSC6         | ANSC5       | ANSC4  | ANSC3  | ANSC2  | —      | _      | 111                 |  |

| CCP1CON                                              | _            | —             | DC1E        | <1:0>  |        | CCP1   | M<3:0> |        | 236                 |  |

| CCP2CON                                              | _            | _             | DC2E        | <1:0>  |        | CCP2   | M<3:0> |        | 236                 |  |

| FVRCON                                               | FVREN        | FVRRDY        | TSEN        | TSRNG  | —      | —      | ADFV   | ۲<1:0> | 120                 |  |

| INTCON                                               | GIE          | PEIE          | TMR0IE      | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 69                  |  |

| PIE1                                                 | TMR1GIE      | ADIE          | RCIE        | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 70                  |  |

| PIR1                                                 | TMR1GIF      | ADIF          | RCIF        | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 72                  |  |

| TRISA                                                | TRISA7       | TRISA6        | TRISA5      | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 103                 |  |

| TRISB                                                | TRISB7       | TRISB6        | TRISB5      | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 107                 |  |

| TRISC                                                | TRISC7       | TRISC6        | TRISC5      | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 110                 |  |

|                                                      |              |               |             |        |        |        |        |        | t                   |  |

## TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** — = unimplemented read as '0'. Shaded cells are not used for ADC module.

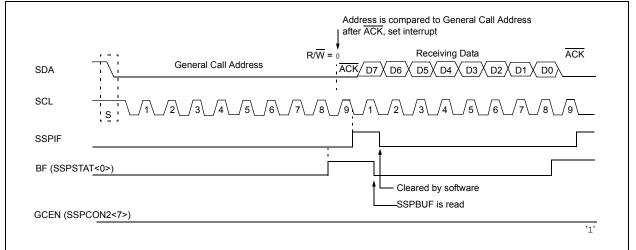

#### 20.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSPCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave

software can read SSPBUF and respond. Figure 20-23 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-Bit mode.

If the AHEN bit of the SSPCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the 8th falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### FIGURE 20-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 20.5.9 SSP MASK REGISTER

An SSP Mask (SSPMSK) register (Register 20-6) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

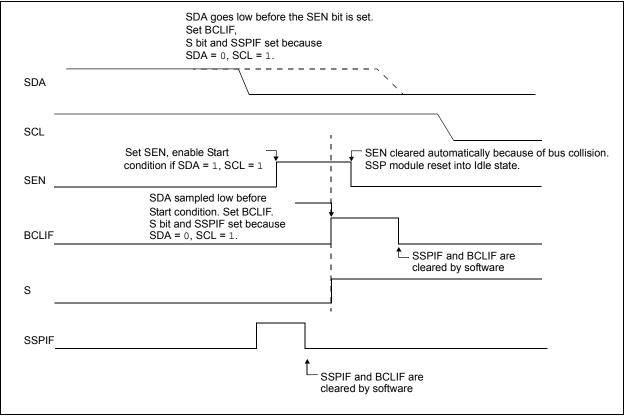

# 20.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 20-32).

- b) SCL is sampled low before SDA is asserted low (Figure 20-33).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 20-32).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 20-34). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

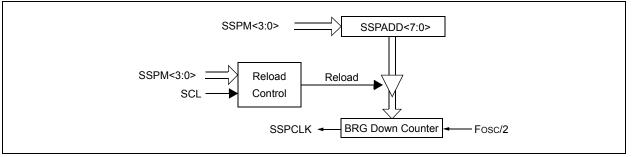

# 20.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPADD register (Register 20-7). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 20-39 triggers the value from SSPADD to be loaded into the BRG counter. This occurs twice for each oscillation of the module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 20-1 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### EQUATION 20-1: BRG CLOCK FREQUENCY

$$FCLOCK = \frac{FOSC}{(SSPADD + 1)(4)}$$

## FIGURE 20-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### TABLE 20-1: MSSP CLOCK RATE W/BRG

| Fosc   | Fosc Fcy BRG Value |     | FCLOCK<br>(2 Rollovers of BRG) |

|--------|--------------------|-----|--------------------------------|

| 16 MHz | 4 MHz              | 09h | 400 kHz <sup>(1)</sup>         |

| 16 MHz | 4 MHz              | 0Ch | 308 kHz                        |

| 16 MHz | 4 MHz              | 27h | 100 kHz                        |

| 4 MHz  | 1 MHz              | 09h | 100 kHz                        |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

| REGISTER<br>R-0/0 | R/W-0/0                        | R/W-0/0                                                                                | R/W-0/0                                                               | R/W-0/0                   | R/W-0/0                                         | R/W-0/0           | R/W-0/0        |  |  |  |  |

|-------------------|--------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|-------------------------------------------------|-------------------|----------------|--|--|--|--|

| ACKTIM            | PCIE                           | SCIE                                                                                   | BOEN                                                                  | SDAHT                     | SBCDE                                           | AHEN              | DHEN           |  |  |  |  |

| bit 7             | 1 012                          | COL                                                                                    | BOLIT                                                                 | 00/111                    | OBOBL                                           | 7.01214           | bit (          |  |  |  |  |

|                   |                                |                                                                                        |                                                                       |                           |                                                 |                   |                |  |  |  |  |

| Legend:           |                                |                                                                                        |                                                                       |                           |                                                 |                   |                |  |  |  |  |

| R = Readab        |                                | W = Writable                                                                           |                                                                       | •                         | mented bit, read                                |                   |                |  |  |  |  |

| u = Bit is un     | 0                              |                                                                                        | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |                           |                                                 |                   |                |  |  |  |  |

| '1' = Bit is se   | et                             | '0' = Bit is cle                                                                       | eared                                                                 |                           |                                                 |                   |                |  |  |  |  |

| bit 7             | ACKTIM: Ac                     | <b>ACKTIM:</b> Acknowledge Time Status bit (I <sup>2</sup> C mode only) <sup>(3)</sup> |                                                                       |                           |                                                 |                   |                |  |  |  |  |

|                   |                                |                                                                                        |                                                                       |                           | e, set on 8 <sup>™</sup> fal<br>g edge of SCL c |                   | CL clock       |  |  |  |  |

| bit 6             | PCIE: Stop (                   | Condition Interr                                                                       | upt Enable bit (                                                      | I <sup>2</sup> C Slave mo | de only)                                        |                   |                |  |  |  |  |

|                   |                                | nterrupt on dete<br>ection interrupt                                                   |                                                                       |                           |                                                 |                   |                |  |  |  |  |

| bit 5             | SCIE: Start (                  | Condition Interr                                                                       | upt Enable bit (                                                      | I <sup>2</sup> C Slave mo | de only)                                        |                   |                |  |  |  |  |

|                   |                                | nterrupt on dete<br>ection interrupt                                                   |                                                                       |                           | ditions                                         |                   |                |  |  |  |  |

| bit 4             | BOEN: Buffe                    | er Overwrite Er                                                                        | able bit                                                              |                           |                                                 |                   |                |  |  |  |  |

|                   | In SPI Slave                   |                                                                                        |                                                                       |                           |                                                 |                   |                |  |  |  |  |

|                   |                                |                                                                                        |                                                                       |                           | te is shifted in i                              |                   |                |  |  |  |  |

|                   |                                | PCON1 register                                                                         |                                                                       |                           | STAT register a                                 | fready set, 55    |                |  |  |  |  |

|                   | <u>In I<sup>2</sup>C Maste</u> | <u>r mode and SF</u><br>is ignored.                                                    |                                                                       |                           | pulled                                          |                   |                |  |  |  |  |

|                   | <u>In I<sup>2</sup>C Slave</u> | mode:                                                                                  |                                                                       |                           |                                                 |                   |                |  |  |  |  |

|                   | of th                          | BUF is updated<br>the SSPOV bit o<br>BUF is only up                                    | nly if the BF bit                                                     | = 0.                      | received addres                                 | s/data byte, ign  | oring the stat |  |  |  |  |

| bit 3             |                                | A Hold Time Se                                                                         |                                                                       |                           |                                                 |                   |                |  |  |  |  |

|                   | 1 = Minimum                    | n of 300 ns hold<br>n of 100 ns hold                                                   | time on SDA                                                           | after the falling         |                                                 |                   |                |  |  |  |  |

| bit 2             |                                |                                                                                        |                                                                       |                           | C Slave mode o                                  | only)             |                |  |  |  |  |

|                   |                                | g edge of SCL,<br>R2 register is se                                                    |                                                                       |                           | e module is outp                                | outting a high st | ate, the BCLI  |  |  |  |  |

|                   |                                | lave bus collisi                                                                       |                                                                       | led                       |                                                 |                   |                |  |  |  |  |

| bit 1             |                                | ess Hold Enab                                                                          | -                                                                     |                           |                                                 |                   |                |  |  |  |  |

|                   |                                | ng the 8th fallin<br>N1 register will                                                  |                                                                       |                           | hing received a<br>be held low.                 | iddress byte; C   | CKP bit of th  |  |  |  |  |

|                   | 0 = Address                    | holding is disa                                                                        | bled                                                                  |                           |                                                 |                   |                |  |  |  |  |

| bit 0             | DHEN: Data                     | Hold Enable b                                                                          | it (I <sup>2</sup> C Slave m                                          | ode only)                 |                                                 |                   |                |  |  |  |  |

|                   | of the S                       | g the 8th falling<br>SPCON1 regis<br>ding is disabled                                  | ter and SCL is                                                        |                           | data byte; slave                                | hardware clea     | irs the CKP b  |  |  |  |  |

|                   | or daisy-chained               |                                                                                        |                                                                       |                           |                                                 |                   |                |  |  |  |  |

|                   | -                              |                                                                                        |                                                                       |                           | dition detection                                | -                 |                |  |  |  |  |

#### REGISTER 20-5: SSPCON3: SSP CONTROL REGISTER 3

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                         |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |

# 25.0 ELECTRICAL SPECIFICATIONS

# 25.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias             | 40°C to +125°C       |

|--------------------------------------------|----------------------|

| Storage temperature                        | 65°C to +150°C       |

| Voltage on pins with respect to Vss        |                      |

| on VDD pin                                 |                      |

| PIC16F1512/3                               | 0.3V to +6.5V        |

| PIC16LF1512/3                              | -0.3V to +4.0V       |

| on MCLR pin                                | -0.3V to +9.0V       |

| on all other pins                          | 0.3V to (VDD + 0.3V) |

| Maximum current                            |                      |

| on Vss pin <sup>(1)</sup>                  |                      |

| -40°C $\leq$ Ta $\leq$ +85°C $\ldots$      | 340 mA               |

| $-40^{\circ}C \leq TA \leq +125^{\circ}C$  | 140 mA               |

| on VDD pin <sup>(1)</sup>                  |                      |

| -40°C $\leq$ Ta $\leq$ +85°C $\ldots$      | 255 mA               |

| $-40^{\circ}C \leq TA \leq +125^{\circ}C$  | 105 mA               |

| on any I/O pin                             | ±25 mA               |

| Clamp current, Ik (VPIN < 0 or VPIN > VDD) | ±20 mA               |

|                                            |                      |

Note 1: Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Section 25.4 "Thermal Considerations" to calculate device specifications.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

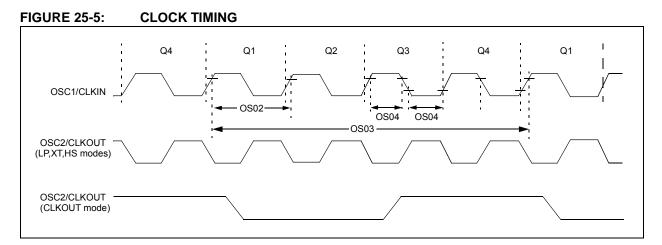

## TABLE 25-6: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Param<br>No. | Sym.  | Characteristic                          | Min. | Тур†   | Max.   | Units | Conditions                     |

|--------------|-------|-----------------------------------------|------|--------|--------|-------|--------------------------------|

| OS01         | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 0.5    | MHz   | EC Oscillator mode (low)       |

|              |       |                                         | DC   | _      | 4      | MHz   | EC Oscillator mode (medium)    |

|              |       |                                         | DC   | _      | 20     | MHz   | EC Oscillator mode (high)      |

|              |       | Oscillator Frequency <sup>(1)</sup>     | —    | 32.768 |        | kHz   | LP Oscillator mode             |

|              |       |                                         | 0.1  | _      | 4      | MHz   | XT Oscillator mode             |

|              |       |                                         | 1    | _      | 4      | MHz   | HS Oscillator mode             |

|              |       |                                         | 1    | _      | 20     | MHz   | HS Oscillator mode, VDD > 2.7V |

|              |       |                                         | DC   | _      | 4      | MHz   | RC Oscillator mode, VDD > 2.0V |

| OS02         | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27   | _      | 8      | μS    | LP Oscillator mode             |

|              |       |                                         | 250  | _      | ×      | ns    | XT Oscillator mode             |

|              |       |                                         | 50   | _      | ×      | ns    | HS Oscillator mode             |

|              |       |                                         | 50   | _      | ×      | ns    | EC Oscillator mode             |

|              |       | Oscillator Period <sup>(1)</sup>        | —    | 30.5   |        | μS    | LP Oscillator mode             |

|              |       |                                         | 250  | _      | 10,000 | ns    | XT Oscillator mode             |

|              |       |                                         | 50   | _      | 1,000  | ns    | HS Oscillator mode             |

|              |       |                                         | 250  | _      | _      | ns    | RC Oscillator mode             |

| OS03         | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 125  | _      | DC     | ns    | Tcy = Fosc/4                   |

| OS04*        | TosH, | External CLKIN High,                    | 2    | _      |        | μS    | LP oscillator                  |

|              | TosL  | External CLKIN Low                      | 100  | —      | —      | ns    | XT oscillator                  |

|              |       |                                         | 20   | —      | —      | ns    | HS oscillator                  |

| OS05*        | TosR, | External CLKIN Rise,                    | 0    | —      | 8      | ns    | LP oscillator                  |

|              | TosF  | External CLKIN Fall                     | 0    | —      | ×      | ns    | XT oscillator                  |

|              |       |                                         | 0    | —      | ×      | ns    | HS oscillator                  |

Standard Operating Conditions (unless otherwise stated)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

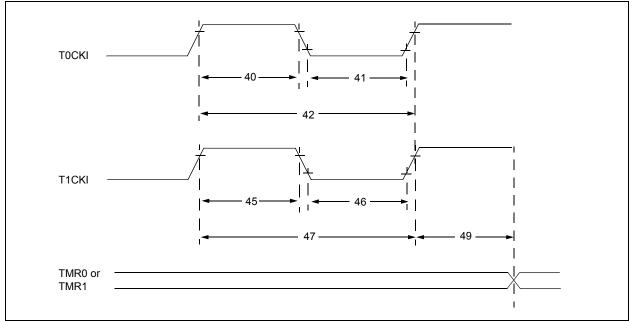

#### FIGURE 25-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### TABLE 25-10: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Standa           | rd Operating   | g Conditions (u                   | Inless otherwi                                          | se stated)   |                                           |            |      |                        |                                    |

|------------------|----------------|-----------------------------------|---------------------------------------------------------|--------------|-------------------------------------------|------------|------|------------------------|------------------------------------|

| Param<br>No.     | Sym.           |                                   | Characterist                                            | ic           | Min.                                      | Тур†       | Max. | Units                  | Conditions                         |

| 40* TT0H T0CKI H |                | T0CKI High I                      | Pulse Width No Prescaler                                |              | 0.5 Tcy + 20                              | —          | _    | ns                     |                                    |

|                  |                | With Pres-<br>caler               |                                                         | 10           | —                                         | —          | ns   |                        |                                    |

| 41*              | TT0L           | T0CKI Low F                       | ulse Width                                              | No Prescaler | 0.5 Tcy + 20                              | —          | —    | ns                     |                                    |

|                  |                |                                   | With Pres-<br>caler                                     |              | 10                                        | —          | —    | ns                     |                                    |

| 42*              | T⊤0P           | T0CKI Period                      | ł                                                       | ·            | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —          | —    | ns                     | N = prescale value<br>(2, 4,, 256) |

| 45*              | T⊤1H           | T1CKI High                        | Synchronous, No Prescaler                               |              | 0.5 Tcy + 20                              | —          | _    | ns                     |                                    |

|                  |                | Time                              | Synchronous,<br>with Prescaler                          |              | 15                                        | —          | —    | ns                     |                                    |

|                  |                |                                   | Asynchronous                                            |              | 30                                        | _          | _    | ns                     |                                    |

| 46*              | T⊤1L           | T1L T1CKI Low<br>Time             | Synchronous, No Prescaler                               |              | 0.5 Tcy + 20                              | _          | —    | ns                     |                                    |

|                  |                |                                   | Synchronous, with Prescaler                             |              | 15                                        | _          | —    | ns                     |                                    |

|                  |                |                                   | Asynchronous                                            |              | 30                                        | _          | —    | ns                     |                                    |

| 47* TT1P         |                | T1CKI Input Synchronous<br>Period |                                                         |              | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —          | _    | ns                     | N = prescale value<br>(1, 2, 4, 8) |

|                  |                |                                   | Asynchronous                                            | 6            | 60                                        | _          | _    | ns                     |                                    |

| 48               | FT1            | Range                             | scillator Input Frequency abled by setting bit T1OSCEN) |              | 32.4                                      | 32.76<br>8 | 33.1 | kHz                    |                                    |

| 49*              | TCKEZT-<br>MR1 | Delay from E<br>Increment         | xternal Clock E                                         | 2 Tosc       |                                           | 7 Tosc     |      | Timers in Sync<br>mode |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.