#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1513-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1512/3

| TABLI | E 1:                     | 2           | 28-PIN ALL    | OCATION TAE | E 1: 28-PIN ALLOCATION TABLE (PIC16(L)F1512/3) |        |                   |           |         |                |  |  |  |  |  |  |  |

|-------|--------------------------|-------------|---------------|-------------|------------------------------------------------|--------|-------------------|-----------|---------|----------------|--|--|--|--|--|--|--|

| 0/1   | 28-Pin SPDIP, SOIC, SSOP | 28-Pin UQFN | ٩/D           | Timers      | ССР                                            | EUSART | MSSP              | Interrupt | Pull-up | Basic          |  |  |  |  |  |  |  |

| RA0   | 2                        | 27          | AN0           | _           | _                                              | _      | SS <sup>(2)</sup> | _         | _       | _              |  |  |  |  |  |  |  |

| RA1   | 3                        | 28          | AN1           | —           |                                                | _      |                   |           | _       | _              |  |  |  |  |  |  |  |

| RA2   | 4                        | 1           | AN2           | —           | _                                              | —      | —                 | _         | —       | —              |  |  |  |  |  |  |  |

| RA3   | 5                        | 2           | AN3/VREF+     | —           |                                                | _      |                   | _         | —       | —              |  |  |  |  |  |  |  |

| RA4   | 6                        | 3           | _             | TOCKI       |                                                | _      | _                 | —         | —       | —              |  |  |  |  |  |  |  |

| RA5   | 7                        | 4           | AN4           | —           |                                                | _      | SS <sup>(1)</sup> | _         | —       | VCAP           |  |  |  |  |  |  |  |

| RA6   | 10                       | 7           | _             | —           | _                                              | —      | —                 | —         | _       | OSC2/CLKOUT    |  |  |  |  |  |  |  |

| RA7   | 9                        | 6           | _             |             | _                                              | —      | —                 | —         | _       | OSC1/CLKIN     |  |  |  |  |  |  |  |

| RB0   | 21                       | 18          | AN12          | _           | _                                              | —      | _                 | INT/IOC   | Y       | _              |  |  |  |  |  |  |  |

| RB1   | 22                       | 19          | AN10          |             | _                                              | —      | —                 | IOC       | Y       |                |  |  |  |  |  |  |  |

| RB2   | 23                       | 20          | AN8           | _           | —                                              | —      | —                 | IOC       | Y       | _              |  |  |  |  |  |  |  |

| RB3   | 24                       | 21          | AN9           |             | CCP2 <sup>(2)</sup>                            | —      | _                 | IOC       | Y       | _              |  |  |  |  |  |  |  |

| RB4   | 25                       | 22          | AN11<br>ADOUT | —           | _                                              | —      | _                 | IOC       | Y       | —              |  |  |  |  |  |  |  |

| RB5   | 26                       | 23          | AN13          | T1G         | _                                              | —      | —                 | IOC       | Y       | —              |  |  |  |  |  |  |  |

| RB6   | 27                       | 24          | ADGRDA        | —           | _                                              | —      | —                 | IOC       | Y       | ICSPCLK/ICDCLK |  |  |  |  |  |  |  |

| RB7   | 28                       | 25          | ADGRDB        | —           |                                                | _      |                   | IOC       | Y       | ICSPDAT/ICDDAT |  |  |  |  |  |  |  |

| RC0   | 11                       | 8           | _             | SOSCO/T1CKI |                                                | _      | _                 | _         | —       | —              |  |  |  |  |  |  |  |

| RC1   | 12                       | 9           | _             | SOSCI       | CCP2 <sup>(1)</sup>                            | —      | —                 | —         | _       | _              |  |  |  |  |  |  |  |

| RC2   | 13                       | 10          | AN14          | _           | CCP1                                           | —      | —                 | —         | _       | _              |  |  |  |  |  |  |  |

| RC3   | 14                       | 11          | AN15          | —           |                                                | —      | SCK/SCL           | _         | _       | _              |  |  |  |  |  |  |  |

| RC4   | 15                       | 12          | AN16          | —           | _                                              | —      | SDI/SDA           | _         | _       | —              |  |  |  |  |  |  |  |

| RC5   | 16                       | 13          | AN17          | —           | _                                              | —      | SDO               | _         | _       | _              |  |  |  |  |  |  |  |

| RC6   | 17                       | 14          | AN18          | —           | —                                              | TX/CK  | —                 | _         | _       | _              |  |  |  |  |  |  |  |

| RC7   | 18                       | 15          | AN19          | —           | _                                              | RX/DT  | _                 |           | —       | _              |  |  |  |  |  |  |  |

| RE3   | 1                        | 26          | —             | —           | —                                              | _      | —                 | —         | Y       | MCLR/Vpp       |  |  |  |  |  |  |  |

| VDD   | 20                       | 17          | —             | —           | —                                              | —      | —                 | —         | _       | _              |  |  |  |  |  |  |  |

| Vss   | 8,19                     | 5,16        | _             |             | _                                              |        | _                 | _         | _       | _              |  |  |  |  |  |  |  |

| NC    | —                        | _           | _             | —           | _                                              | —      | _                 | _         | _       | —              |  |  |  |  |  |  |  |

# TABLE 1:28-PIN ALLOCATION TABLE (PIC16(L)F1512/3)

Note 1: Peripheral pin location selected using APFCON register. Default location.

2: Peripheral pin location selected using APFCON register. Alternate location.

### 11.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

#### FIGURE 11-3:

#### FLASH PROGRAM MEMORY UNLOCK SEQUENCE FLOWCHART

# **11.6** Flash Program Memory Control Registers

#### R/W-x/u R/W-x/u R/W-x/u R/W-x/u R/W-x/u R/W-x/u R/W-x/u R/W-x/u PMDAT<7:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and BOR/Value at all other Resets u = Bit is unchanged x = Bit is unknown '1' = Bit is set '0' = Bit is cleared

#### REGISTER 11-2: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

bit 7-0 **PMDAT<7:0>**: Read/write value for Least Significant bits of program memory

#### REGISTER 11-3: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|--|--|

| —     | —   |         | PMDAT<13:8> |         |         |         |         |  |  |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 11-4: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0    | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |  |

|------------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|

| PMADR<7:0> |             |         |         |         |         |         |         |  |  |  |  |  |

| bit 7      | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 PMADR<7:0>: Specifies the Least Significant bits for program memory address

#### REGISTER 11-5: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| 11.4               | D/M/ 0/0 |                     |         | D/M/ 0/0                           | D/M/ 0/0       |                     | D/M/ 0/0 |  |  |

|--------------------|----------|---------------------|---------|------------------------------------|----------------|---------------------|----------|--|--|

| U-1                | R/W-0/0  | R/W-0/0             | R/W-0/0 | R/W-0/0                            | R/W-0/0        | R/W-0/0             | R/W-0/0  |  |  |

| —                  |          |                     |         | PMADR<14:8>                        |                |                     |          |  |  |

| bit 7              | •        |                     |         |                                    |                |                     | bit 0    |  |  |

|                    |          |                     |         |                                    |                |                     |          |  |  |

| Legend:            |          |                     |         |                                    |                |                     |          |  |  |

| R = Readable bit   |          | W = Writable bit    |         | U = Unimplemented bit, read as '0' |                |                     |          |  |  |

| u = Bit is unchang | ged      | x = Bit is unknow   | /n      | -n/n = Value at F                  | POR and BOR/Va | lue at all other Re | esets    |  |  |

| '1' = Bit is set   |          | '0' = Bit is cleare | d       |                                    |                |                     |          |  |  |

bit 7 Unimplemented: Read as '1'

bit 6-0 **PMADR<14:8>**: Specifies the Most Significant bits for program memory address

| U-1 <sup>(1)</sup> | R/W-0/0                                | R/W-0/0                                | R/W/HC-0/0        | R/W/HC-x/q <sup>(2)</sup>                             | R/W-0/0            | R/S/HC-0/0                             | R/S/HC-0/0       |  |  |

|--------------------|----------------------------------------|----------------------------------------|-------------------|-------------------------------------------------------|--------------------|----------------------------------------|------------------|--|--|

| _                  | CFGS                                   | LWLO                                   | FREE              | WRERR                                                 | WREN               | WR                                     | RD               |  |  |

| bit 7              | •                                      |                                        |                   |                                                       |                    |                                        | bit              |  |  |

| Legend:            |                                        |                                        |                   |                                                       |                    |                                        |                  |  |  |

| R = Readable       | bit                                    | W = Writable b                         | bit               | U = Unimpleme                                         | ented bit, read as | s 'O'                                  |                  |  |  |

| S = Bit can on     | ly be set                              | x = Bit is unkn                        | own               | -n/n = Value at POR and BOR/Value at all other Resets |                    |                                        |                  |  |  |

| '1' = Bit is set   |                                        | '0' = Bit is clea                      | red               | HC = Bit is clea                                      | ared by hardware   | 9                                      |                  |  |  |

| hit 7              | Unimploment                            | ed. Dood oo '1'                        |                   |                                                       |                    |                                        |                  |  |  |

| bit 7              | •                                      | ed: Read as '1'                        |                   |                                                       |                    |                                        |                  |  |  |

| bit 6              | 0                                      | uration Select bi                      |                   | ID Registers                                          |                    |                                        |                  |  |  |

|                    |                                        | lash program me                        |                   | ID Registers                                          |                    |                                        |                  |  |  |

| bit 5              |                                        | Write Latches Or                       | -                 |                                                       |                    |                                        |                  |  |  |

|                    | 1 = Only the                           | addressed progr                        | am memory write   | e latch is loaded/                                    | updated on the     | next WR commar                         | ıd               |  |  |

|                    |                                        |                                        |                   | h is loaded/updat                                     | ed and a write of  | all program mem                        | ory write latche |  |  |

|                    |                                        | tiated on the nex                      |                   |                                                       |                    |                                        |                  |  |  |

| bit 4              | 0                                      | m Flash Erase E                        |                   |                                                       |                    | ······································ |                  |  |  |

|                    |                                        | an erase operation                     |                   | •                                                     | ardware cleared    | upon completion)                       | )                |  |  |

| bit 3              |                                        | gram/Erase Error                       |                   |                                                       |                    |                                        |                  |  |  |

|                    |                                        |                                        | -                 | or erase sequen                                       | ce attempt or te   | rmination (bit is s                    | et automatical   |  |  |

|                    | ,                                      | et attempt (write                      | ,                 | ,                                                     |                    | ,                                      |                  |  |  |

|                    | 0 = The prog                           | ram or erase ope                       | eration complete  | d normally.                                           |                    |                                        |                  |  |  |

| bit 2              | •                                      | am/Erase Enable                        |                   |                                                       |                    |                                        |                  |  |  |

|                    |                                        | ogram/erase cyc                        |                   |                                                       |                    |                                        |                  |  |  |

| hit 1              | WR: Write Co                           | rogramming/eras                        | ang of program i  | 10511                                                 |                    |                                        |                  |  |  |

| bit 1              |                                        | a program Flash                        | program/erase o   | neration                                              |                    |                                        |                  |  |  |

|                    |                                        |                                        |                   | leared by hardwa                                      | are once operatio  | on is complete.                        |                  |  |  |

|                    | •                                      | bit can only be s                      |                   | •                                                     |                    | · · · · ·                              |                  |  |  |

|                    | 0 = Program/                           | erase operation                        | to the Flash is c | omplete and inac                                      | tive.              |                                        |                  |  |  |

| bit 0              | RD: Read Cor                           | ntrol bit                              |                   |                                                       |                    |                                        |                  |  |  |

|                    |                                        |                                        | read. Read takes  | s one cycle. RD is                                    | s cleared in hard  | lware. The RD bit                      | can only be se   |  |  |

|                    | •                                      | red) in software.<br>initiate a progra | m Flash read      |                                                       |                    |                                        |                  |  |  |

| Noto 1.            |                                        |                                        | n nash leau.      |                                                       |                    |                                        |                  |  |  |

|                    | nimplemented bit,<br>he WRERR bit is a |                                        | hy hardware whe   | en a program me                                       | mory write or er   | ase operation is s                     | tarted (WR = 1   |  |  |

|                    | he LWLO bit is ian                     | -                                      | -                 |                                                       | -                  |                                        |                  |  |  |

#### DECISTED 44 C. DMCON4, DDOCDAM MEMORY CONTROL 4 DECISTED

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0   | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|---------|--------|---------|---------------------|

| ANSELA     |        |        | ANSA5  | _      | ANSA3  | ANSA2   | ANSA1  | ANSA0   | 104                 |

| APFCON     | _      | _      | —      | _      | _      | —       | SSSEL  | CCP2SEL | 101                 |

| LATA       | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2   | LATA1  | LATA0   | 104                 |

| OPTION_REG | WPUEN  | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        |         | 159                 |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2     | RA1    | RA0     | 103                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1 | TRISA0  | 103                 |

#### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits   | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3    | Bit 10/2  | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|--------|---------|---------|----------|----------|-------------|-----------|---------|---------|---------------------|

| CONFIG1 | 13:8 — |         | FCMEN   | IESO     | CLKOUTEN | BOREN<1:0.> |           | _       | 37      |                     |

| CONFIGT | 7:0    | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>      | FOSC<2:0> |         |         | 37                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

| U-0             | R/W-0/0    | R/W-0/0                                                                | R/W-0/0       | R/W-0/0            | R/W-0/0            | R/W-0/0            | R/W-0/0 |  |  |  |  |  |

|-----------------|------------|------------------------------------------------------------------------|---------------|--------------------|--------------------|--------------------|---------|--|--|--|--|--|

| _               |            |                                                                        |               | ADACQ<6:0>         |                    |                    |         |  |  |  |  |  |

| bit 7           |            |                                                                        |               |                    |                    |                    | bit     |  |  |  |  |  |

| Legend:         |            |                                                                        |               |                    |                    |                    |         |  |  |  |  |  |

| R = Readab      | le bit     | W = Writable bi                                                        | t             | U = Unimpleme      | ented bit, read as | ·'O'               |         |  |  |  |  |  |

| u = Bit is un   | changed    | x = Bit is unkno                                                       | wn            | -n/n = Value at    | POR and BOR/\      | /alue at all other | Resets  |  |  |  |  |  |

| '1' = Bit is se | et         | '0' = Bit is clear                                                     | ed            |                    |                    |                    |         |  |  |  |  |  |

| hit 7           | Unimalone  | ated. Deed on 'o'                                                      |               |                    |                    |                    |         |  |  |  |  |  |

| bit 7           | •          | nted: Read as '0'                                                      |               | <b>a</b> (1)       |                    |                    |         |  |  |  |  |  |

| bit 6-0         |            | ADACQ<6:0>: Acquisition/Charge Share Time Select bits <sup>(1)</sup>   |               |                    |                    |                    |         |  |  |  |  |  |

|                 | 111 1111 = | Acquisition/charge                                                     | share for 127 | instruction cycles |                    |                    |         |  |  |  |  |  |

|                 | 111 1110 = | Acquisition/charge                                                     | share for 126 | instruction cycles |                    |                    |         |  |  |  |  |  |

|                 | •          |                                                                        |               |                    |                    |                    |         |  |  |  |  |  |

|                 | •          |                                                                        |               |                    |                    |                    |         |  |  |  |  |  |

|                 | •          |                                                                        |               |                    |                    |                    |         |  |  |  |  |  |

|                 | 000 0001 = | 000 0001 = Acquisition/charge share for one instruction cycle (Fosc/4) |               |                    |                    |                    |         |  |  |  |  |  |

|                 |            |                                                                        |               | ne is disabled     |                    |                    |         |  |  |  |  |  |

# REGISTER 16-13: AADACQ: HARDWARE CVD ACQUISITION TIME CONTROL REGISTER

**Note 1:** When the FRC clock is selected as the conversion clock source, it is also the clock used for the pre-charge and acquisition times.

# REGISTER 16-14: AADGRD: HARDWARE CVD GUARD RING CONTROL REGISTER

| R/W-0/0               | R/W-0/0               | R/W-0/0                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-----------------------|-----------------------|-------------------------|-----|-----|-----|-----|-------|

| GRDBOE <sup>(2)</sup> | GRDAOE <sup>(2)</sup> | GRDPOL <sup>(1,2)</sup> |     |     | -   | —   | _     |

| bit 7                 |                       |                         |     | •   |     | •   | bit 0 |

| Legend:                                                                                                                                                                        |                                                                                                                                                   |                            |                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------|--|--|

| R = Readable bit                                                                                                                                                               |                                                                                                                                                   | W = Writable bit           | U = Unimplemented bit, read as '0'                       |  |  |

| u = Bit is unchanged                                                                                                                                                           |                                                                                                                                                   | x = Bit is unknown         | -n/n = Value at POR and BOR/Value at all other<br>Resets |  |  |

| '1' = Bit is                                                                                                                                                                   | set                                                                                                                                               | '0' = Bit is cleared       |                                                          |  |  |

|                                                                                                                                                                                |                                                                                                                                                   |                            |                                                          |  |  |

| bit 7                                                                                                                                                                          | GRDBOE: (                                                                                                                                         | Guard Ring B Output Enable | bit <sup>(2)</sup>                                       |  |  |

| <ul> <li>1 = ADC guard ring output is enabled to ADGRDB pin. Its corresponding TRISx bit must be cle</li> <li>0 = No ADC guard ring function to this pin is enabled</li> </ul> |                                                                                                                                                   |                            |                                                          |  |  |

| bit 6 <b>GRDAOE:</b> Guard Ring A Output Enable bit <sup>(2)</sup>                                                                                                             |                                                                                                                                                   |                            |                                                          |  |  |

| <ul> <li>1 = ADC Guard Ring Output is enabled to ADGRDA pin. Its corresponding TRISx, x bit must be</li> <li>0 = No ADC Guard Ring function is enabled</li> </ul>              |                                                                                                                                                   |                            |                                                          |  |  |

| bit 5                                                                                                                                                                          | bit 5 <b>GRDPOL:</b> Guard Ring Polarity selection bit <sup>(1,2)</sup>                                                                           |                            |                                                          |  |  |

| <ul> <li>1 = ADC guard ring outputs start as digital high during pre-charge stage</li> <li>0 = ADC guard ring outputs start as digital low during pre-charge stage</li> </ul>  |                                                                                                                                                   |                            |                                                          |  |  |

| bit 4-0                                                                                                                                                                        | it 4-0 Unimplemented: Read as '0'                                                                                                                 |                            |                                                          |  |  |

| Note 1:                                                                                                                                                                        | When the ADDSEN = 1 and ADIPEN = 1; the polarity of this output is inverted for the second conversion time. The stored bit value does not change. |                            |                                                          |  |  |

| 2:                                                                                                                                                                             | 2: Guard Ring outputs are maintained while ADON = 1. The ADGRDA output switches polarity at the state the acquisition time.                       |                            |                                                          |  |  |

# 20.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

# 20.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

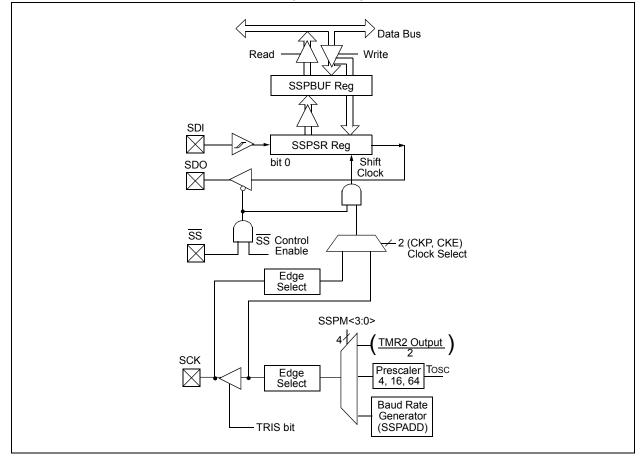

Figure 20-1 is a block diagram of the SPI interface module.

### FIGURE 20-1: MSSP BLOCK DIAGRAM (SPI MODE)

# 20.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

# 20.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 20-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

# 20.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON1<3:0> =<br>0100), the SPI module will reset if the $\overline{SS}$<br>pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable SS pin control.                                                                                      |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPSTAT register must remain clear.                                                                                    |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

# 20.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 20.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared by software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

#### 20.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPCON3 register is set, the BCLIF bit of the PIR register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

### 20.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 20-17 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPIF bit.

- 4. Slave hardware generates an ACK and sets SSPIF.

- 5. SSPIF bit is cleared by user.

- 6. Software reads the received address from SSP-BUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- Note 1: If the master ACKs the clock will be stretched.

ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

#### 20.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPIF interrupt is set.

Figure 20-18 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCL line the CKP bit is cleared and SSPIF interrupt is generated.

- 4. Slave software clears SSPIF.

- 5. Slave software reads ACKTIM bit of SSPCON3 register, and R/W and  $D/\overline{A}$  of the SSPSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets ACKDT bit of the SSPCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPIF.

- 12. Slave loads value to transmit to the master into SSPBUF setting the BF bit.

Note: <u>SSPBUF</u> cannot be loaded until after the <u>ACK</u>.

13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an  $\overline{ACK}$  value on the 9th SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

#### 20.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 20-19 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSPSTAT register is set.

- 4. Slave sends ACK and SSPIF is set.

- 5. Software clears the SSPIF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. Slave loads low address into SSPADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPIF is set.

**Note:** If the low address does not match, SSPIF and UA are still set so that the slave software can set SSPADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPIF.

- 11. Slave reads the received matching address from SSPBUF clearing BF.

- 12. Slave loads high address into SSPADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSPIF is set.

- 14. If SEN bit of SSPCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPIF.

- 16. Slave reads the received byte from SSPBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

# 20.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 20-20 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 20-21 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

# 20.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

# 20.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

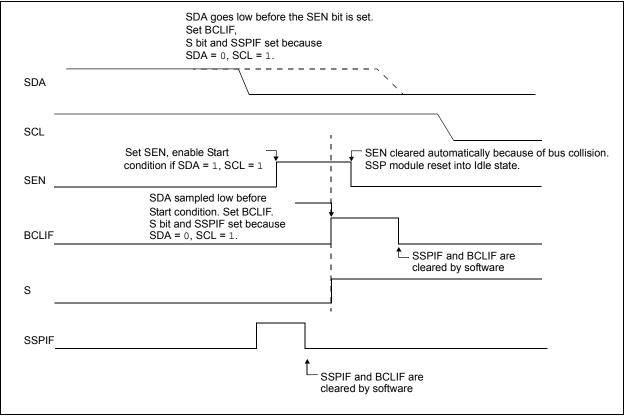

# 20.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

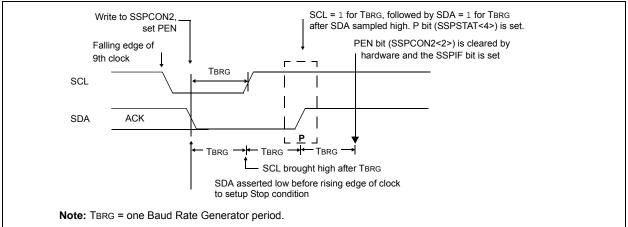

## 20.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the I<sup>2</sup>C port to its Idle state (Figure 20-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

# PIC16(L)F1512/3

# 20.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 20-32).

- b) SCL is sampled low before SDA is asserted low (Figure 20-33).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 20-32).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 20-34). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

# 22.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate.

The Auto-Baud Detect feature (see **22.4.1** "**Auto-Baud Detect**") can be used to compensate for changes in the INTOSC frequency.

There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

### 22.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 22-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 22-5. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 22-5. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 22.4.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

#### TABLE 22-5: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |  |  |

|-------|------|-------------------|------------------|--|--|

| 0     | 0    | Fosc/64           | Fosc/512         |  |  |

| 0     | 1    | Fosc/16           | Fosc/128         |  |  |

| 1     | 0    | Fosc/16           | Fosc/128         |  |  |

| 1     | 1    | Fosc/4            | Fosc/32          |  |  |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

#### XXXXh 0000h **BRG** Value 001Ch Edge #3 Edge #4 Edae #5 - Edge #1 - Edge #2 bit 6 bit 7 RX pin Start bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 Stop bit Auto Cleared Set by User ABDEN bit RCIDI RCIF bit (Interrupt) Read RCREG . SPBRGL XXh 1Ch XXh 00h SPBRGH Note 1: The ABD sequence requires the EUSART module to be configured in Asynchronous mode.

#### FIGURE 22-6: AUTOMATIC BAUD RATE CALIBRATION

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |  |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] TRIS f                                                                                                                                     |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

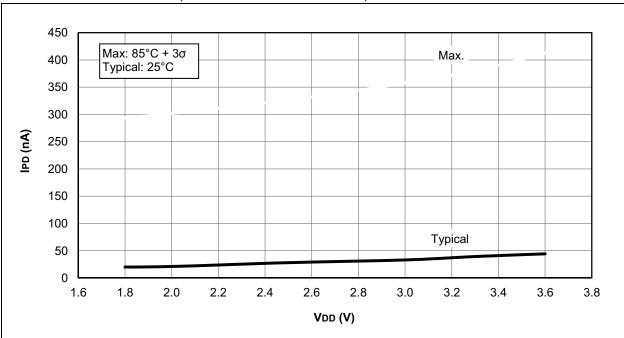

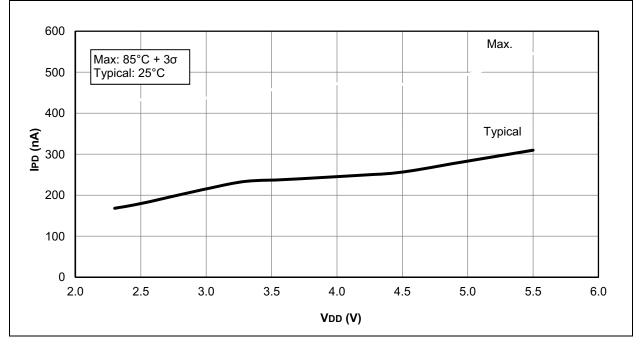

# TABLE 25-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2,4)</sup>

| PIC16LF1512/3                |                        | Standard Operating Conditions (unless otherwise stated) |            |       |        |       |            |                                    |

|------------------------------|------------------------|---------------------------------------------------------|------------|-------|--------|-------|------------|------------------------------------|

| PIC16F151                    |                        |                                                         |            |       |        |       |            |                                    |

| Param Dovice Characteristics |                        | Min                                                     | <b>T</b> 4 | Max.  | Max.   |       | Conditions |                                    |

| No.                          | Device Characteristics | Min.                                                    | Тур†       | +85°C | +125°C | Units | Vdd        | Note                               |

| D022                         |                        | _                                                       | 0.02       | 1.0   | 8.0    | μA    | 1.8        | WDT, BOR, FVR, and SOSC            |

|                              |                        | —                                                       | 0.03       | 2.0   | 9.0    | μA    | 3.0        | disabled, all Peripherals Inactive |

| D022                         |                        |                                                         | 0.20       | 3.0   | 11     | μA    | 2.3        | WDT, BOR, FVR, and SOSC            |

|                              |                        |                                                         | 0.30       | 4.0   | 12     | μA    | 3.0        | disabled, all Peripherals Inacti   |

|                              |                        | —                                                       | 0.40       | 6     | 15     | μA    | 5.0        |                                    |

| D023                         |                        | —                                                       | 0.30       | 6     | 14     | μA    | 1.8        | LPWDT Current                      |

|                              |                        | -                                                       | 0.60       | 7     | 17     | μA    | 3.0        |                                    |

| D023                         |                        | —                                                       | 0.50       | 6     | 15     | μA    | 2.3        | LPWDT Current                      |

|                              |                        | —                                                       | 0.77       | 7     | 20     | μA    | 3.0        |                                    |

|                              |                        | —                                                       | 0.85       | 8     | 22     | μA    | 5.0        |                                    |

| D023A                        |                        | —                                                       | 10         | 28    | 30     | μA    | 1.8        | FVR current                        |

|                              |                        | —                                                       | 12         | 30    | 33     | μA    | 3.0        |                                    |

| D023A                        |                        | —                                                       | 18         | 33    | 35     | μA    | 2.3        | FVR current                        |

|                              |                        | —                                                       | 19         | 36    | 37     | μA    | 3.0        | 1                                  |

|                              |                        | —                                                       | 20         | 37    | 45     | μA    | 5.0        | 1                                  |

| D024                         |                        | —                                                       | 8.0        | 17    | 20     | μA    | 3.0        | BOR Current                        |

| D024                         |                        | —                                                       | 8          | 17    | 30     | μA    | 3.0        | BOR Current                        |

|                              |                        | _                                                       | 9          | 20    | 40     | μA    | 5.0        | 7                                  |

| D024A                        |                        | —                                                       | 0.80       | 4     | 8      | μA    | 3.0        | LPBOR Current                      |

| D024A                        |                        | _                                                       | 0.30       | 4     | 14     | μA    | 3.0        | LPBOR Current                      |

|                              |                        | _                                                       | 0.45       | 8     | 17     | μA    | 5.0        | 1                                  |

| D025                         |                        | _                                                       | 0.6        | 5     | 9      | μA    | 1.8        | SOSC Current                       |

|                              |                        | _                                                       | 2.5        | 8.5   | 12     | μA    | 3.0        |                                    |

| D025                         |                        | —                                                       | 1          | 6     | 10     | μA    | 2.3        | SOSC Current                       |

|                              |                        | _                                                       | 2.2        | 8.5   | 20     | μA    | 3.0        |                                    |

|                              |                        | _                                                       | 5.5        | 15    | 25     | μA    | 5.0        |                                    |

| D026                         |                        | _                                                       | 0.1        | 1.5   | 9      | μA    | 1.8        | A/D Current (Note 3),              |

|                              |                        | _                                                       | 0.2        | 2.7   | 10     | μA    | 3.0        | no conversion in progress          |

| D026                         |                        | _                                                       | 0.3        | 4     | 11     | μA    | 2.3        | A/D Current (Note 3),              |

|                              |                        | _                                                       | 0.35       | 5     | 13     | μΑ    | 3.0        | no conversion in progress          |

|                              |                        | _                                                       | 0.45       | 8     | 16     | μA    | 5.0        |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

**3:** A/D oscillator source is FRC.

4: Specification for PIC16F1512/3 devices assumes that Low-Power Sleep mode is selected, when available, via the VREGCON register (see Section 8.2.2 "Peripheral Usage in Sleep" and Register 8-1).

# PIC16(L)F1512/3

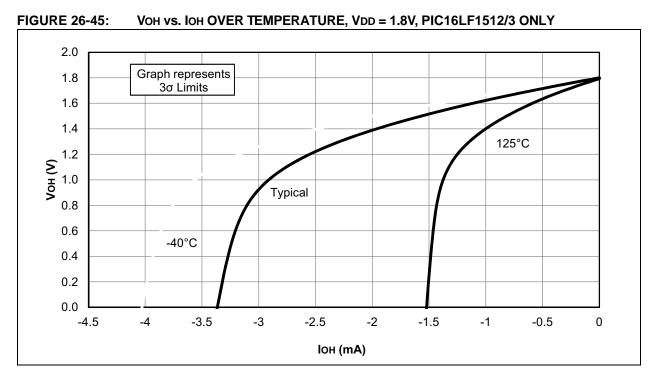

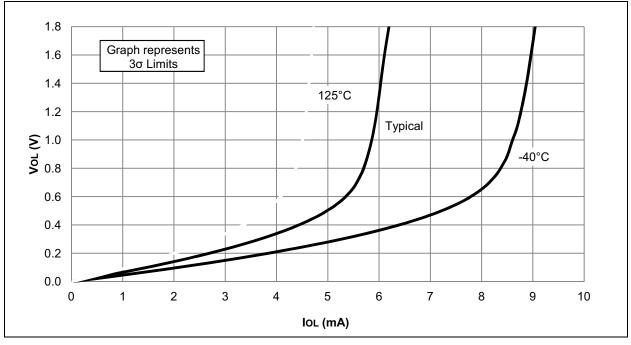

FIGURE 26-46: Vol vs. IoL OVER TEMPERATURE, VDD = 1.8V, PIC16LF1512/3 ONLY

# 27.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 27.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker