Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application energific microcontrollars are angineered to

#### Details

| Decans                  |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                  |

| Applications            | UHF ASK/FSK                                                               |

| Core Processor          | MARC4                                                                     |

| Program Memory Type     | FLASH (4kB)                                                               |

| Controller Series       | MARC4 4-Bit                                                               |

| RAM Size                | 256 x 4                                                                   |

| Interface               | SSI                                                                       |

| Number of I/O           | 11                                                                        |

| Voltage - Supply        | 1.8V ~ 4V                                                                 |

| Operating Temperature   | -40°C ~ 125°C                                                             |

| Mounting Type           | Surface Mount                                                             |

| Package / Case          | 24-LSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package | 24-550                                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/atam862p-tnqy8d |

|                         |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

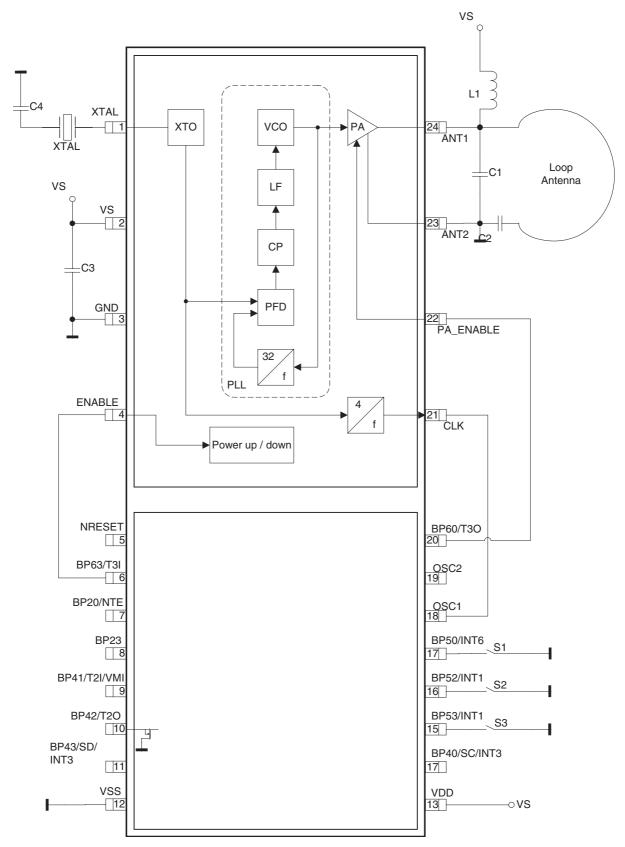

# 6. General Description

The fully-integrated PLL transmitter that allows particularly simple, low-cost RF miniature transmitters to be assembled. The VCO is locked to  $64 \times f_{XTAL}$ , thus, a 13.5672 MHz crystal is needed for a 868.3 MHz transmitter and a 14.2969 MHz crystal for a 915 MHz transmitter. All other PLL and VCO peripheral elements are integrated.

The XTO is a series resonance oscillator so that only one capacitor together with a crystal connected in series to GND are needed as external elements.

The crystal oscillator together with the PLL needs typically < 1 ms until the PLL is locked and the CLK output is stable. A wait time of  $\geq$  4 ms must be used until the CLK is used for the microcontroller and the PA is switched on.

The power amplifier is an open-collector output delivering a current pulse which is nearly independent from the load impedance. The delivered output power is controlled via the connected load impedance.

This output configuration enables a simple matching to any kind of antenna or to 50  $\Omega$  A high power efficiency of  $\eta = P_{out}/(I_{S,PA} \times V_S)$  of 24% for the power amplifier at 868.3 MHz results when an optimized load impedance of  $Z_{Load} = (166 + j226) \Omega$  is used at 3 V supply voltage.

# 7. Functional Description

If ENABLE = L and PA\_ENABLE = L, the circuit is in standby mode consuming only a very small amount of current, so that a lithium cell used as power supply can work for several years.

With ENABLE = H, the XTO, PLL and the CLK driver are switched on. If PA\_ENABLE remains L, only the PLL and the XTO are running and the CLK signal is delivered to the microcontroller. The VCO locks to 64 times the XTO frequency.

With ENABLE = H and PA\_ENABLE = H, the PLL, XTO, CLK driver and the power amplifier are on. With PA\_ENABLE, the power amplifier can be switched on and off, which is used to perform the ASK modulation.

# 7.1 ASK Transmission

The PLL transmitter block is activated by ENABLE = H. PA\_ENABLE must remain L for t  $\ge$  4 ms, then the CLK signal can be taken to clock the microcontroller and the output power can be modulated by means of pin PA\_ENABLE. After transmission, PA\_ENABLE is switched to L and the microcontroller switches back to internal clocking. The ATAM862-8 is switched back to standby mode with ENABLE = L.

## 7.2 FSK Transmission

The PLL transmitter block is activated by ENABLE = H. PA\_ENABLE must remain L for  $t \ge 4$  ms, then the CLK signal can be taken to clock the microcontroller and the power amplifier is switched on with PA\_ENABLE = H. The chip is then ready for FSK modulation. The microcontroller starts to switch on and off the capacitor between the XTAL load capacitor and GND with an open-drain output port, thus changing the reference frequency of the PLL. If the switch is closed, the output frequency is lower than if the switch is open. After transmission PA\_ENABLE is switched to L and the microcontroller switches back to internal clocking. The PLL transmitter block is switched back to standby mode with ENABLE = L.

The accuracy of the frequency deviation with XTAL pulling method is about  $\pm 25\%$  when the following tolerances are considered.

Figure 7-3. ASK Application Circuit

# 8. Absolute Maximum Ratings: RF Part

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol                    | Min.                                                                                         | Max.                                                                                           | Unit                                                   |

|---------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Vs                        |                                                                                              | 5                                                                                              | V                                                      |

| P <sub>tot</sub>          |                                                                                              | 100                                                                                            | mW                                                     |

| Tj                        |                                                                                              | 150                                                                                            | °C                                                     |

| T <sub>stg</sub>          | -55                                                                                          | +125                                                                                           | °C                                                     |

| T <sub>amb</sub>          | -55                                                                                          | +125                                                                                           | °C                                                     |

| V <sub>maxPA_ENABLE</sub> | -0.3                                                                                         | (V <sub>S</sub> + 0.3) <sup>(1)</sup>                                                          | V                                                      |

|                           | V <sub>S</sub><br>P <sub>tot</sub><br>T <sub>j</sub><br>T <sub>stg</sub><br>T <sub>amb</sub> | V <sub>S</sub> P <sub>tot</sub> T <sub>j</sub> T <sub>stg</sub> -55           T <sub>amb</sub> | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

Note: 1. If  $V_{S}$  + 0.3 is higher than 3.7 V, the maximum voltage will be reduced to 3.7 V.

# 9. Thermal Resistance

| Parameters       | Symbol            | Value | Unit |

|------------------|-------------------|-------|------|

| Junction ambient | R <sub>thJA</sub> | 135   | K/W  |

# **10. Electrical Characteristics**

$V_S$  = 2.0 V to 4.0 V,  $T_{amb}$  = -40°C to +125°C unless otherwise specified.

Typical values are given at  $V_s = 3.0$  V and  $T_{amb} = 25^{\circ}$ C. All parameters are referred to GND (Pin 3).

| Parameters     | Test Conditions                                                                                                                                                                      | Symbol                  | Min. | Тур. | Max.     | Unit           |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|----------|----------------|

| Supply current | Power down,<br>V <sub>ENABLE</sub> < 0.25 V, -40°C to 85°C<br>V <sub>PA_ENABLE</sub> < 0.25 V, -85°C to +125°C<br>V <sub>PA_ENABLE</sub> < 0.25 V, 25°C<br>(100% correlation tested) | I <sub>S_Off</sub>      |      | <10  | 350<br>7 | nA<br>μA<br>nA |

| Supply ourrent | Power up, PA off, $V_S = 3 V$<br>$V_{ENABLE} > 1.7 V$ , $V_{PA_ENABLE} < 0.25 V$                                                                                                     | ۱ <sub>S</sub>          |      | 3.6  | 4.6      | mA             |

| Supply current | Power up, $V_S = 3.0 \text{ V}$<br>$V_{ENABLE} > 1.7 \text{ V}$ , $V_{PA\_ENABLE} > 1.7 \text{ V}$                                                                                   | I <sub>S_Transmit</sub> |      | 8.5  | 11       | mA             |

| Output power   | $V_{S} = 3.0$ V, $T_{amb} = 25^{\circ}$ C<br>f = 868.3 MHz, Z <sub>Load</sub> = (166 + j226) Ω                                                                                       | P <sub>Ref</sub>        | 3.5  | 5.5  | 8        | dBm            |

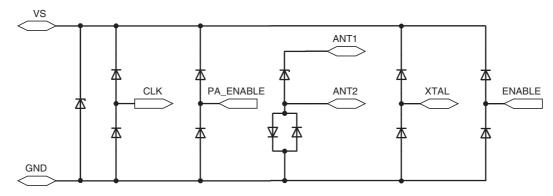

# Figure 18-1. Voltage Monitor

# 18.0.1 Voltage Monitor Control/Status Register

Primary register address: "F"hex

|            | Bit 3 | Bit 2 | Bit 1    | Bit 0 |                    |

|------------|-------|-------|----------|-------|--------------------|

| VMC: Write | VM2   | VM1   | VMO      | VIM   | Reset value: 1111b |

|            |       |       |          |       |                    |

| VMST: Read | -     | -     | Reserved | VMS   | Reset value: xx11b |

VM2: Voltage monitor Mode bit 2

VM1: Voltage monitor Mode bit 1

VM0: Voltage monitor Mode bit 0

# Table 18-1. Voltage Monitor Modes

| Table 10-1. Voltage Monitor Modes |     |     |                                                                                           |  |  |  |  |

|-----------------------------------|-----|-----|-------------------------------------------------------------------------------------------|--|--|--|--|

| VM2                               | VM1 | VMO | Function                                                                                  |  |  |  |  |

| 1                                 | 1   | 1   | Disable voltage monitor                                                                   |  |  |  |  |

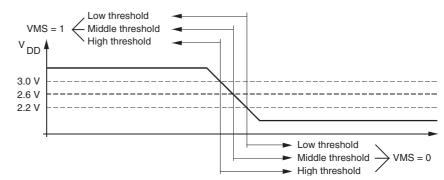

| 1                                 | 1   | 0   | External (VIM input), internal reference threshold (1.3 V), interrupt with negative slope |  |  |  |  |

| 1                                 | 0   | 1   | Not allowed                                                                               |  |  |  |  |

| 1                                 | 0   | 0   | External (VMI input), internal reference threshold (1.3 V), interrupt with positive slope |  |  |  |  |

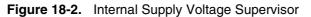

| 0                                 | 1   | 1   | Internal (supply voltage), high threshold (3.0 V), interrupt with negative slope          |  |  |  |  |

| 0                                 | 1   | 0   | Internal (supply voltage), middle threshold (2.6 V), interrupt with negative slope        |  |  |  |  |

| 0                                 | 0   | 1   | Internal (supply voltage), low threshold (2.2 V), interrupt with negative slope           |  |  |  |  |

| 0                                 | 0   | 0   | Not allowed                                                                               |  |  |  |  |

VIM

#### Voltage Interrupt Mask bit

VIM = 0, voltage monitor interrupt is enabled

VIM = 1, voltage monitor interrupt is disabled

VMS

Voltage Monitor Status bit

VMS = 0, the voltage at the comparator input is below  $\ensuremath{\mathsf{V}_{\mathsf{Ref}}}$

VMS = 1, the voltage at the comparator input is above  $V_{Ref}$

# 19. Clock Generation

#### 19.1 Clock Module

The ATAM862-8 contains a clock module with 4 different internal oscillator types: two RC-oscillators, one 4-MHz crystal oscillator and one 32-kHz crystal oscillator. The pins OSC1 and OSC2 are the interface to connect a crystal either to the 4-MHz, or to the 32-kHz crystal oscillator. OSC1 can be used as input for external clocks or to connect an external trimming resistor for the RC-oscillator 2. All necessary circuitry, except the crystal and the trimming resistor, is integrated on-chip. One of these oscillator types or an external input clock can be selected to generate the system clock (SYSCL).

In applications that do not require exact timing, it is possible to use the fully integrated RC-oscillator 1 without any external components. The RC-oscillator 1 center frequency tolerance is better than  $\pm$  50%. The RC-oscillator 2 is a trimmable oscillator whereby the oscillator frequency can be trimmed with an external resistor attached between OSC1 and V<sub>DD</sub>. In this configuration, the RC-oscillator 2 frequency can be maintained stable with a tolerance of  $\pm$  15% over the full operating temperature and voltage range.

The clock module is programmable via software with the clock management register (CM) and the system configuration register (SC). The required oscillator configuration can be selected with the OS1 bit and the OS0 bit in the SC register. A programmable 4-bit divider stage allows the adjustment of the system clock speed. A special feature of the clock management is that an external oscillator may be used and switched on and off via a port pin for the power-down mode. Before the external clock is switched off, the internal RC-oscillator 1 must be selected with the CCS bit and then the SLEEP mode may be activated. In this state an interrupt can wake up the controller with the RC-oscillator, and the external oscillator can be activated and selected by

# Table 21-1. Peripheral Addresses

|          | Port Address | ;         | Name          | Write/ Read | Reset Value | Register Function                        | Modu<br>Type |

|----------|--------------|-----------|---------------|-------------|-------------|------------------------------------------|--------------|

| 1        |              |           | P1DAT         | W/R         | 1xx1b       | Port 1 - data register/input data        | M3           |

| 2        |              |           | P2DAT         | W/R         | 1111b       | Port 2 - data register/pin data          | M2           |

|          | Auxiliary    |           | P2CR          | W           | 1111b       | Port 2 - control register                |              |

| 3        |              |           | SC            | W           | 1x11b       | System configuration register            | M3           |

|          |              |           | CWD           | R           | xxxxb       | Watchdog reset                           | M3           |

|          | Auxiliary    |           | СМ            | W           | 1111b       | Clock management register                | M2           |

| 4        | ·            |           | P4DAT         | W/R         | 1111b       | Port 4 - data register/pin data          | M2           |

|          | Auxiliary    |           | P4CR          | W           | 1111 1111b  | Port 4 - control register (byte)         |              |

| 5        |              |           | P5DAT         | W/R         | 1111b       | Port 5 - data register/pin data          | M2           |

|          | Auxiliary    |           | P5CR          | W           | 1111 1111b  | Port 5 - control register (byte)         |              |

| 6        | - +          |           | P6DAT         | W/R         | 1xx1b       | Port 6 - data register/pin data          | M2           |

|          | Auxiliary    |           | P6CR          | W           | 1111b       | Port 6 - control register (byte)         |              |

| 7        |              |           | T12SUB        | W           | _           | Data to Timer 1/2 subport                | M1           |

|          |              | Subport a | ddress        | 4           |             |                                          | 4            |

|          |              | 0         | T2C           | W           | 0000b       | Timer 2 control register                 | M1           |

|          |              | 1         | T2M1          | W           | 1111b       | Timer 2 mode register 1                  | M1           |

|          |              | 2         | T2M2          | W           | 1111b       | Timer 2 mode register 2                  | M1           |

|          |              | 3         | T2CM          | W           | 0000b       | Timer 2 compare mode register            | M1           |

|          |              | 4         | T2CO1         | W           | 1111b       | Timer 2 compare register 1               | M1           |

|          |              | 5         | T2CO2         | W           | 1111 1111b  | Timer 2 compare register 2 (byte)        | M1           |

|          |              | 6         | _             | _           | _           | Reserved                                 |              |

|          |              | 7         | _             | _           | _           | Reserved                                 |              |

|          |              | 8         | T1C1          | W           | 1111b       | Timer 1 control register 1               | M1           |

|          |              | 9         | T1C2          | W           | x111b       | Timer 1 control register 2               | M1           |

|          |              | A         | WDC           | W           | 1111b       | Watchdog control register                | M1           |

|          |              | B-F       |               |             |             | Reserved                                 |              |

| 8        |              | 2.        | ASW           | W           | 1111b       | Auxiliary/switch register                | ASW          |

| 9        |              |           | STB           | W           | xxxx xxxxb  | Serial transmit buffer (byte)            | M2           |

| U        |              |           | SRB           | R           | xxxx xxxxb  | Serial receive buffer (byte)             |              |

|          | Auxiliary    |           | SIC1          | W           | 1111b       | Serial interface control register 1      |              |

| A        | , taxinar y  |           | SISC          | W/R         | 1x11b       | Serial interface status/control register | M2           |

|          | Auxiliary    |           | SIC2          | W           | 1111b       | Serial interface control register 2      |              |

| В        | Auxiliary    |           | T3SUB         | W/R         | -           | Data to/from Timer 3 subport             | M1           |

| D        |              | Subport a |               | vv/11       |             |                                          | IVII         |

|          |              | 0         | T3M           | W           | 1111b       | Timer 3 mode register                    | M1           |

|          |              | 1         | T3CS          | W           | 1111b       | Timer 3 clock select register            | M1           |

|          |              | 2         | T3CM1         | W           | 0000b       | Timer 3 compare mode register 1          | M1           |

|          |              | 3         | T3CM2         | W           | 0000b       | Timer 3 compare mode register 1          | M1           |

|          |              | 4         | T3C01         | W           | 1111 1111b  | Timer 3 compare register 1 (byte)        | M1           |

|          |              | 4         | T3CP          | R           | xxxx xxxxb  | Timer 3 capture register (byte)          | M1           |

|          |              | 4<br>5    | T3CP<br>T3CO2 | R<br>W      | 1111 1111b  | Timer 3 compare register 2 (byte)        | M1           |

|          | 1            | 5         | 13002         | W           | 1111b       | Reserved                                 | 1/11         |

|          |              |           |               | vv          |             |                                          |              |

| <u> </u> |              | 7-F       |               | 147         | -           | Reserved                                 |              |

| С        |              | T3C       |               | W           | 0000b       | Timer 3 control register                 | M3           |

| <u> </u> |              | T3ST      |               | R           | x000b       | Timer 3 status register                  | M3           |

| D, E     |              | -         |               |             | -           | Reserved                                 |              |

| F        |              | VMC       |               | W           | 1111b       | Voltage monitor control register         | M3           |

|          |              | VMST      |               | R           | xx11b       | Voltage monitor status register          | M3           |

# 34 ATAM862-8

# 22. Bi-directional Ports

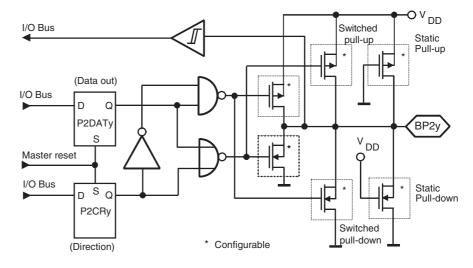

With the exception of Port 1 and Port 6, all other ports (2, 4 and 5) are 4 bits wide. Port 1 and Port 6 have a data width of 2 bits (bit 0 and bit 3). All ports may be used for data input or output. All ports are equipped with Schmitt trigger inputs and a variety of mask options for open-drain, open-source, full-complementary outputs, pull-up and pull-down transistors. All Port Data Registers (PxDAT) are I/O mapped to the primary address register of the respective port address and the Port Control Register (PxCR), to the corresponding auxiliary register.

There are five different directional ports available:

- Port 1 2-bit wide bi-directional port with automatic full bus width direction switching.

- Port 2 4-bit wide bitwise-programmable I/O port.

- Port 5 4-bit wide bitwise-programmable bi-directional port with optional strong pull-ups and programmable interrupt logic.

- Port 4 4-bit wide bitwise-programmable bi-directional port also provides the I/O interface to Timer 2, SSI, voltage monitor input and external interrupt input.

- Port 6 2-bit wide bitwise-programmable bi-directional port also provides the I/O interface to Timer 3 and external interrupt input.

## 22.1 Bi-directional Port 1

In Port 1 the data direction register is not independently software programmable, the direction of the complete port being switched automatically when an I/O instruction occurs (see Figure 22-1 on page 36). The port is switched to output mode via an OUT instruction and to input via an IN instruction. The data written to a port will be stored into the output data latches and appears immediately at the port pin following the OUT instruction. After RESET all output latches are set to "1" and the port is switched to input mode. An IN instruction reads the condition of the associated pins.

Note: Care must be taken when switching the bi-directional port from output to input. The capacitive pin loading at this port in conjunction with the high resistance pull-ups may cause the CPU to read the contents of the output data register rather than the external input state. To avoid this, one of the following programming techniques should be used:

Use two IN-instructions and DROP the first data nibble. The first IN switches the port from output to input and the DROP removes the first invalid nibble. The second IN reads the valid pin state. Use an OUT instruction followed by an IN instruction. Via the OUT instruction, the capacitive load is charged or discharged depending on the optional pull-up/pull-down configuration. Write a "1" for pins with pull-up resistors and a "0" for pins with pull-down resistors.

37

# Figure 22-2. Bi-directional Port 2

## 22.2.1 Port 2 Data Register (P2DAT)

| Bit 3 * | Bit 2  | Bit 1  | Bit 0  |

|---------|--------|--------|--------|

| P2DAT3  | P2DAT2 | P2DAT1 | P2DAT0 |

\* Bit 3 -> MSB, Bit 0 -> LSB

#### 22.2.2 Port 2 Control Register (P2CR)

| Bit 3 | Bit 3 Bit 2 |       | Bit 0 |

|-------|-------------|-------|-------|

| P2CR3 | P2CR2       | P2CR1 | P2CR0 |

Value: 1111b means all pins in input mode

#### Table 22-1. Port 2 Control Register

| Code<br>3 2 1 0 | Function            |

|-----------------|---------------------|

| x x x 1         | BP20 in input mode  |

| x x x 0         | BP20 in output mode |

| x x 1 x         | BP21 in input mode  |

| x x 0 x         | BP21 in output mode |

| x 1 x x         | BP22 in input mode  |

| x 0 x x         | BP22 in output mode |

| 1 x x x         | BP23 in input mode  |

| 0 x x x         | BP23 in output mode |

Primary register address: "2"hex

Reset value: 1111b

Reset value: 1111b

Auxiliary register address: "2"hex

#### 22.12.6 Timer 2 Compare Mode Register (T2CM)

Address: "7"hex - Subaddress: "3"hex

| I    | Bit 3 | Bit 2                                                                                                                                                                                                                                                                                                                                         | Bit 1                                          | Bit 0                                          |                                                                                                                                 |  |  |  |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Tź   | 2OTM  | T2CTM                                                                                                                                                                                                                                                                                                                                         | T2RM                                           | T2IM                                           | Reset value: 0000b                                                                                                              |  |  |  |

|      |       |                                                                                                                                                                                                                                                                                                                                               |                                                |                                                |                                                                                                                                 |  |  |  |

| Т2С  |       | Timer <b>2 O</b> ver<br>T2OTM = 0,<br>T2OTM = 1,                                                                                                                                                                                                                                                                                              | disable overf<br>enable overf<br>flip-flop (TO | flow toggle<br>low toggle, a<br>IG2). If the T | a counter overflow (OVF2) toggles output<br>2OTM bit is set, only a counter overflow can<br>ccept on the Timer 2 output mode 7. |  |  |  |

| T2C  |       | Timer 2 Compare Toggle Mask bit<br>T2CTM = 0, disable compare toggle<br>T2CTM = 1, enable compare toggle, a match of the counter with the compare<br>register toggles output flip-flop (TOG2). In Timer 2 output mode 7 and<br>when the T2CTM bit is set, only a match of the counter with the<br>compare register can generate an interrupt. |                                                |                                                |                                                                                                                                 |  |  |  |

| T2F  | RM    | Timer <b>2 R</b> ese<br>T2RM = 0, di<br>T2RM = 1, e                                                                                                                                                                                                                                                                                           | sable counte                                   | er reset, a m                                  | atch of the counter with the compare register                                                                                   |  |  |  |

| T2II | М     | Timer <b>2 I</b> nter<br>T2IM = 0, dis<br>T2IM = 1, en                                                                                                                                                                                                                                                                                        | able Timer 2                                   | 2 interrupt                                    |                                                                                                                                 |  |  |  |

| Table 22-11. | Timer 2 Toggle Mask Bits |

|--------------|--------------------------|

|--------------|--------------------------|

| Timer 2 Output Mode | T2OTM | T2CTM | Timer 2 Interrupt Source |

|---------------------|-------|-------|--------------------------|

| 1, 2, 3, 4, 5 and 6 | 0     | х     | Compare match (CM2)      |

| 1, 2, 3, 4, 5 and 6 | 1     | х     | Overflow (OVF2)          |

| 7                   | x     | 1     | Compare match (CM2)      |

#### 22.12.7 Timer 2 COmpare Register 1 (T2CO1)

Address: "7"hex - Subaddress: "4"hex

Write cycleBit 3Bit 2Bit 1Bit 0Reset value: 1111b

In prescaler mode the clock is bypassed if the compare register T2CO1 contains 0.

#### 22.12.8 Timer 2 COmpare Register 2 (T2CO2) Byte Write

|       |       |       |       | Address: "7"hex - Subaddress: "5"hex |

|-------|-------|-------|-------|--------------------------------------|

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset value: 1111b                   |

|       |       |       |       | -                                    |

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Reset value: 1111b                   |

|       |       |       |       |                                      |

# 23.6 Timer 3 Registers

# 23.6.1 Timer 3 Mode Register (T3M)

T3M2

Address: "B"hex - Subaddress: "0"hex

Reset value: 1111b

| Bit 3         | Bit 2       | Bit 1          | Bit 0 |

|---------------|-------------|----------------|-------|

| ТЗМЗ          | T3M2        | T3M1           | T3M0  |

|               |             |                |       |

| <b>T</b> 0140 | -           |                |       |

| тзмз          | Timer 3 Mod | e select bit 3 | 3     |

| T3M1 | Timer 3 Mode select bit 1 |

|------|---------------------------|

| T3M0 | Timer 3 Mode select bit 0 |

|      |                           |

## Table 23-1. Timer 3 Mode Select Bits

Timer 3 Mode select bit 2

| Mode | T3M3 | T3M2 | T3M1 | T3M0 | Timer 3 Modes                                                                                                             |

|------|------|------|------|------|---------------------------------------------------------------------------------------------------------------------------|

| 1    | 1    | 1    | 1    | 1    | Timer/counter with a read access                                                                                          |

| 2    | 1    | 1    | 1    | 0    | Timer/counter, external capture and external trigger restart mode (T3I)                                                   |

| 3    | 1    | 1    | 0    | 1    | Timer/counter, internal capture and internal trigger restart mode (TOG2)                                                  |

| 4    | 1    | 1    | 0    | 0    | Timer/counter mode 1 without output<br>(T2O -> T3O)                                                                       |

| 5    | 1    | 0    | 1    | 1    | Timer/counter mode 2 without output<br>(T2O -> T3O)                                                                       |

| 6    | 1    | 0    | 1    | 0    | Burst modulation with Timer 2 (M2)                                                                                        |

| 7    | 1    | 0    | 0    | 1    | Burst modulation with shift register (SO)                                                                                 |

| 8    | 1    | 0    | 0    | 0    | FSK modulation with shift register (SO)                                                                                   |

| 9    | 0    | 1    | 1    | 1    | Pulse-width modulation with shift register (SO) and<br>Timer 2 (TOG2), internal trigger restart (SCO) -><br>counter reset |

| 10   | 0    | 1    | 1    | 0    | Manchester demodulation/pulse-width demodulation <sup>(1)</sup> (T2O -> T3O)                                              |

| 11   | 0    | 1    | 0    | 1    | Biphase demodulation (T2O -> T3O)                                                                                         |

| 12   | 0    | 1    | 0    | 0    | Timer/counter with external capture mode (T3I)                                                                            |

| 13   | 0    | 0    | 1    | 1    | Not allowed                                                                                                               |

| 14   | 0    | 0    | 1    | 0    | Not allowed                                                                                                               |

| 15   | 0    | 0    | 0    | 1    | Not allowed                                                                                                               |

| 16   | 0    | 0    | 0    | 0    | Not allowed                                                                                                               |

Note: 1. In this mode, the SSI can be used only as demodulator (8-bit NRZ rising edge). All other SSI modes are not allowed.

#### 23.6.6 Timer 3 Compare-Mode Register 1 (T3CM1)

Address: "B"hex - Subaddress: "2"hex

|       | Bit 3                                                                                                                                                                                                                                     | Bit 2               | Bit 1           | Bit 0 |                                   |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|-------|-----------------------------------|--|--|

| T3CM1 | T3SM1                                                                                                                                                                                                                                     | T3TM1               | T3RM1           | T3IM1 | Reset value: 0000b                |  |  |

|       | Timer 3 Singl                                                                                                                                                                                                                             | e action <b>M</b> a | sk bit <b>1</b> |       | -                                 |  |  |

| T3SM1 | T3SM1 = 0, disables single-action compare mode<br>T3SM1 = 1, enables single-compare mode. After this bit is set, the compare<br>register (T3CO1) is used until the next compare match.                                                    |                     |                 |       |                                   |  |  |

| T3TM1 | Timer <b>3</b> compare Toggle action <b>M</b> ask bit <b>1</b><br>T3TM1 = 0, disables compare toggle<br>T3TM1 = 1, enables compare toggle. A match of Counter 3 with the compare<br>register (T3CO1) toggles the output flip-flop (TOG3). |                     |                 |       |                                   |  |  |

| T3RM1 |                                                                                                                                                                                                                                           | isables cou         | nter reset. A   |       | Counter 3 with the compare ter 3. |  |  |

| T3IM1 | Timer <b>3 I</b> nterr<br>T3RM1 = 0, d<br>T3RM1 = 1, e                                                                                                                                                                                    | isables Tim         | er 3 interru    |       | 8                                 |  |  |

T3CM1 contains the mask bits for the match event of the Counter 3 compare register 1.

#### 23.6.7 Timer 3 Compare Mode Register 2 (T3CM2)

Address: "B"hex - Subaddress: "3"hex

|           | Bit 3                                                                                                                                                                                                                                     | Bit 2         | Bit 1        | Bit 0      |                             |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|------------|-----------------------------|--|--|

| T3CM2     | T3SM2                                                                                                                                                                                                                                     | T3TM2         | T3RM2        | T3IM2      | Reset value: 0000b          |  |  |

|           |                                                                                                                                                                                                                                           |               |              |            |                             |  |  |

| T3SM2     | Timer <b>3 Single action Mask bit 2</b><br>T3SM2 = 0, disables single-action compare mode<br>T3SM2 = 1, enables single-compare mode. After this bit is set, the compare<br>register (T3CO2) is used until the next compare match.         |               |              |            |                             |  |  |

| T3TM2     | Timer <b>3</b> compare Toggle action <b>M</b> ask bit <b>2</b><br>T3TM2 = 0, disables compare toggle<br>T3TM2 = 1, enables compare toggle. A match of Counter 3 with the compare<br>register (T3CO2) toggles the output flip-flop (TOG3). |               |              |            |                             |  |  |

| T3RM2     | Timer <b>3 R</b> eset <b>M</b> ask bit <b>2</b><br>T3RM2 = 0, disables counter reset<br>T3RM2 = 1, enables counter reset. A match of Counter 3 with the compare<br>register (T3CO2) resets the Counter 3.                                 |               |              |            |                             |  |  |

| T3IM2     | Timer <b>3 I</b> nter<br>T3RM2 = 0, c<br>T3RM2 = 1, e                                                                                                                                                                                     | lisables Tim  | er 3 interru | •          | 0                           |  |  |

| T3CM2 cor | ntains the mas                                                                                                                                                                                                                            | k bits for th | ne match e   | event of C | ounter 3 compare register 2 |  |  |

#### 23.8.5 9-bit Shift Mode (MCL compatible)

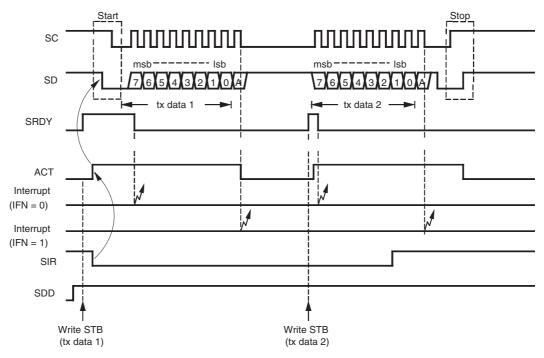

In the 9-bit shift mode, the SSI is able to handle the MCL protocol (described below). It always operates as an MCL master device, i.e., SC is always generated and output by the SSI. Both the MCL start and stop conditions are automatically generated whenever the SSI is activated or deactivated by the SIR bit. In accordance with the MCL protocol, the output data is always changed in the clock low phase and shifted in on the high phase.

Before activating the SSI (SIR = 0) and commencing an MCL dialog, the appropriate data direction for the first word must be set using the SDD control bit. The state of this bit controls the direction of the data port (BP43 or MCL\_SD). Once started, the 8 data bits are, depending on the selected direction, either clocked into or out of the shift register. During the 9th clock period, the port direction is automatically switched over so that the corresponding acknowledge bit can be shifted out or read in. In transmit mode, the acknowledge bit received from the device is captured in the SSI Status Register (TACK) where it can be read by the controller. In receive mode, the state of the acknowledge bit to be returned to the device is predetermined by the SSI Status Register (RACK).

Changing the directional mode (TX/RX) should not be performed during the transfer of an MCL telegram. One should wait until the end of the telegram which can be detected using the SSI interrupt (IFN =1) or by interrogating the ACT status.

Once started, a 9-bit telegram will always run to completion and will not be prematurely terminated by the SIR bit. So, if the SIR bit is set to '1' in telegram, the SSI will complete the current transfer and terminate the dialog with an MCL stop condition.

Figure 23-19. Example of MCL Transmit Dialog

# 23.9 Serial Interface Registers

#### 23.9.1 Serial Interface Control Register 1 (SIC1)

| Bit 3        |                                                                                             | Bit 2 | Bit 1               | Bit 0      |                    |  |  |

|--------------|---------------------------------------------------------------------------------------------|-------|---------------------|------------|--------------------|--|--|

| SIR          |                                                                                             | SCD   | SCS1                | SCS0       | Reset value: 1111b |  |  |

|              | I                                                                                           |       | nterface <b>R</b> e |            |                    |  |  |

| SIR          | SIR = 1, SSI inactive<br>SIR = 0, SSI active                                                |       |                     |            |                    |  |  |

| SCD          | Serial Clock Direction<br>SCD = 1, SC line used as output<br>SCD = 0, SC line used as input |       |                     |            |                    |  |  |

| Note:        | Note: This bit has to be set to "1" during the MCL mode and the Timer 3 mode 10 or 11       |       |                     |            |                    |  |  |

| SCS1<br>SCS0 |                                                                                             |       |                     |            |                    |  |  |

| Note:        |                                                                                             |       |                     |            |                    |  |  |

| Table        | 2_1                                                                                         | Soria |                     | ouroo Sola | act Bito           |  |  |

Auxiliary register address: "9"hex

#### Table 23-4. Serial Clock Source Select Bits

| SCS1 | SCS0 | Internal Clock for SSI |

|------|------|------------------------|

| 1    | 1    | SYSCL/2                |

| 1    | 0    | T1OUT/2                |

| 0    | 1    | POUT/2                 |

| 0    | 0    | TOG2/2                 |

• In transmit mode (SDD = 1) shifting starts only if the transmit buffer has been loaded (SRDY = 1).

• Setting SIR-bit loads the contents of the shift register into the receive buffer (synchronous 8-bit mode only).

• In MCL modes, writing a 0 to SIR generates a start condition and writing a 1 generates a stop condition.

#### 24.1.1 Combination Mode 1: Burst Modulation

| SSI mode 1:                 | 8-bit NRZ and internal data SO output to the Timer 2 modulator stage |

|-----------------------------|----------------------------------------------------------------------|

| Timer 2 mode 1, 2, 3 or 4:  | 8-bit compare counter with 4-bit programmable prescaler and DCG      |

| Timer 2 output mode 3:      | Duty cycle burst generator                                           |

| Figure 24-2. Carrier Freque | ency Burst Modulation with the SSI Internal Data Output              |

#### 24.1.2 Combination Mode 2: Biphase Modulation 1

| SSI mode 1:                | 8-bit shift register internal data output (SO) to the Timer 2 modulator stage     |

|----------------------------|-----------------------------------------------------------------------------------|

| Timer 2 mode 1, 2, 3 or 4: | 8-bit compare counter with 4-bit programmable prescaler                           |

| Timer 2 output mode 4:     | The modulator 2 of Timer 2 modulates the SSI internal data output to Biphase code |

#### Figure 24-3. Biphase Modulation 1

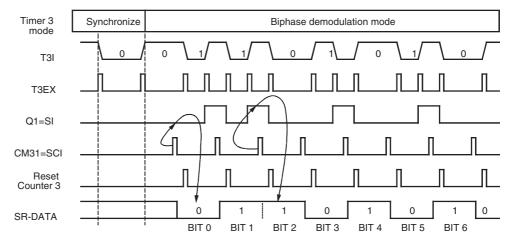

# 24.2.4 Combination Mode 9: Biphase Demodulation

SSI mode 1:

8-bit shift register internal data input (SI) and the internal shift clock (SCI) from the Timer 3

Timer 3 mode 11: Biphase demodulation with Timer 3

In the Biphase demodulation mode the timer works like in the Manchester demodulation mode. The difference is that the bits are decoded with the toggle flip-flop. This flip-flop samples the edge in the middle of the bitframe and the compare register 1 match event shifts the toggle flip-flop output into shift register. Before activating the demodulation the timer and the demodulation stage must be synchronized with the bitstream. The Biphase code timing consists of parts with the half bitlength and the complete bitlength. The synchronization routine must start the demodulator after an interval with the complete bitlength.

The counter can be driven by any internal clock source and the output T3O can be used by Timer 2 in this mode.

#### Figure 24-11. Biphase Demodulation

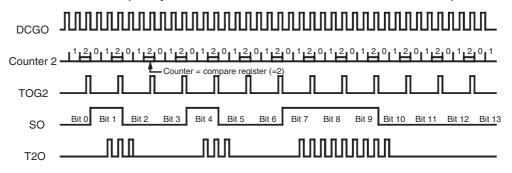

#### 24.4.1 Combination Mode 12: Burst Modulation 2

| SSI mode 1:              | 8-bit shift register internal data output (SO) to the Timer 3                    |

|--------------------------|----------------------------------------------------------------------------------|

| Timer 2 output mode 2:   | 8-bit compare counter and 4-bit prescaler                                        |

| Timer 2 output mode 1/6: | Timer 2 compare match toggles (TOG2) to the SSI                                  |

| Timer 3 mode 7:          | Carrier frequency burst modulation controlled by the internal output (SO) of SSI |

The Timer 3 counter is driven by an internal or external clock source. Its compare- and compare mode registers must be programmed to generate the carrier frequency with the output toggle flip-flop (M3). The internal data output (SO) of the SSI is used to enable and disable the Timer 3 output. The SSI can be supplied with the toggle signal of Timer 2.

#### Figure 24-17. Burst Modulation 2

|             |                                  |                          |                   |               |                 |   |                    |   |                | ההההההה         |       |

|-------------|----------------------------------|--------------------------|-------------------|---------------|-----------------|---|--------------------|---|----------------|-----------------|-------|

| Counter 3   | 2,34,5,01,0,1<br>11 <b>H H</b> I | 2,3,4 <u>5,0</u> ,10,1,2 | 23.4 <u>50101</u> | 50101<br>HHII | 50101<br>HHHIII |   | 50101<br><b>HH</b> |   | 501.01<br>HHHI | 50101<br>HHHIII | 50101 |

| смз1        |                                  |                          |                   |               |                 |   | <br>               |   |                |                 |       |

| СМ32        | [                                |                          |                   | [             |                 | [ |                    |   | [              | [               |       |

| тодз        |                                  |                          |                   |               |                 |   |                    |   |                |                 |       |

| мз 🔟        |                                  |                          |                   |               |                 |   |                    |   |                |                 |       |

| Counter 2/2 | 0                                | 1                        | 2                 | 3             | 1               |   | <br>3              | 0 | <sup>1</sup>   | 2               | 3     |

| тод2        |                                  |                          |                   | [             |                 |   |                    |   |                |                 |       |

| SO          |                                  |                          |                   |               |                 |   |                    |   |                |                 |       |

| ТЗО         |                                  |                          |                   |               |                 |   |                    |   |                |                 |       |

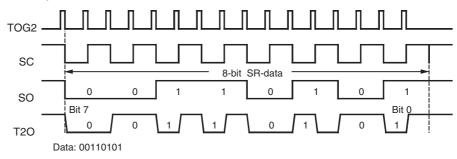

#### 24.4.2 Combination Mode 13: FSK Modulation

| SSI mode 1:              | 8-bit shift register internal data output (SO) to the Timer 3 |

|--------------------------|---------------------------------------------------------------|

| Timer 2 output mode 3:   | 8-bit compare counter and 4-bit prescaler                     |

| Timer 2 output mode 1/6: | Timer 2 4-bit compare match signal (POUT) to the SSI          |

| Timer 3 mode 8:          | FSK modulation with shift register data output (SO)           |

The two compare registers are used to generate two different time intervals. The SSI data output selects which compare register is used for the output frequency generation. A "0" level at the SSI data output enables the compare register 1 and a "1" level enables the compare register 2. The compare- and compare mode registers must be programmed to generate the two frequencies via the output toggle flip-flop. The SSI can be supplied with the toggle signal of Timer 2 or any other clock source. The Timer 3 counter is driven by an internal or external clock source.

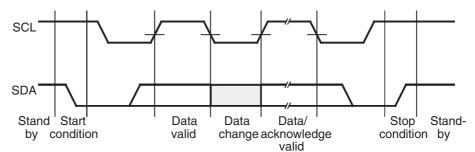

## 24.6 Serial Interface

The EEPROM uses an two-wire serial (TWI) interface to the microcontroller for read and write accesses to the data. It is considered to be a slave in all these applications. That means, the controller has to be the master that initiates the data transfer and provides the clock for transmit and receive operations.

The serial interface is controlled by the microcontroller which generates the serial clock and controls the access via the SCL line and SDA line. SCL is used to clock the data into and out of the device. SDA is a bi-directional line that is used to transfer data into and out of the device. The following protocol is used for the data transfers.

#### 24.6.1 Serial Protocol

- Data states on the SDA line changing only while SCL is low.

- Changes on the SDA line while SCL is high are interpreted as START or STOP condition.

- A START condition is defined as high to low transition on the SDA line while the SCL line is high.

- A STOP condition is defined as low to high transition on the SDA line while the SCL line is high.

- Each data transfer must be initialized with a START condition and terminated with a STOP condition. The START condition wakes the device from standby mode and the STOP condition returns the device to standby mode.

- A receiving device generates an acknowledge (A) after the reception of each byte. This requires an additional clock pulse, generated by the master. If the reception was successful the receiving master or slave device pulls down the SDA line during that clock cycle. If an acknowledge is not detected (N) by the interface in transmit mode, it will terminate further data transmissions and go into receive mode. A master device must finish its read operation by a non-acknowledge and then send a stop condition to bring the device into a known state.

#### Figure 24-20. MCL Protocol

- Before the START condition and after the STOP condition the device is in standby mode and the SDA line is switched as input with pull-up resistor.

- The control byte that follows the START condition determines the following operation. It consists of the 5-bit row address, 2 mode control bits and the READ/NWRITE bit that is used to control the direction of the following transfer. A "0" defines a write access and a "1" a read access.

# 27. DC Operating Characteristics (Continued)

$V_{SS} = 0 \text{ V}, \text{ T}_{amb} = -40^{\circ} \text{ C}$  to  $+125^{\circ} \text{ C}$  unless otherwise specified.

| Parameters                                 | Test Conditions                                                        | Symbol            | Min.               | Тур.        | Max.                | Unit     |

|--------------------------------------------|------------------------------------------------------------------------|-------------------|--------------------|-------------|---------------------|----------|

| Power-on Reset Threshold Volta             | age                                                                    | I                 | 1 I                |             | 1                   |          |

| POR threshold voltage                      | BOT = 1                                                                | V <sub>POR</sub>  | 1.54               | 1.7         | 1.88                | V        |

| POR threshold voltage                      | BOT = 0                                                                | V <sub>POR</sub>  | 1.83               | 2.0         | 2.20                | V        |

| POR hysteresis                             |                                                                        | V <sub>POR</sub>  |                    | 50          |                     | mV       |

| Voltage Monitor Threshold Volta            | age                                                                    |                   |                    |             | 1                   |          |

| VM high threshold voltage                  | $V_{DD} > VM, VMS = 1$                                                 | V <sub>MThh</sub> |                    | 3.0         | 3.35                | V        |

| VM high threshold voltage                  | $V_{DD} < VM, VMS = 0$                                                 | V <sub>MThh</sub> | 2.77               | 3.0         |                     | V        |

| VM middle threshold voltage                | $V_{DD} > VM, VMS = 1$                                                 | V <sub>MThm</sub> |                    | 2.6         | 2.9                 | V        |

| VM middle threshold voltage                | $V_{DD} < VM, VMS = 0$                                                 | V <sub>MThm</sub> | 2.4                | 2.6         |                     | V        |

| VM low threshold voltage                   | $V_{DD} > VM, VMS = 1$                                                 | V <sub>MThl</sub> |                    | 2.2         | 2.44                | V        |

| VM low threshold voltage                   | $V_{DD} < VM, VMS = 0$                                                 | V <sub>MThl</sub> | 2.0                | 2.2         |                     | V        |

| External Input Voltage                     | I                                                                      |                   |                    |             | 1                   |          |

| VMI                                        | $V_{DD} = 3 V, VMS = 1$                                                | V <sub>VMI</sub>  |                    | 1.3         | 1.44                | V        |

| VMI                                        | $V_{DD} = 3 V, VMS = 0$                                                | V <sub>VMI</sub>  | 1.18               | 1.3         |                     | V        |

| All Bi-directional Ports                   | I                                                                      |                   |                    |             | 1                   |          |

| Input voltage LOW                          | V <sub>DD</sub> = 2.0 to 4.0 V                                         | V <sub>IL</sub>   | V <sub>SS</sub>    |             | $0.2 \times V_{DD}$ | V        |

| Input voltage HIGH                         | V <sub>DD</sub> = 2.0 to 4.0 V                                         | V <sub>IH</sub>   | $0.8 	imes V_{DD}$ |             | V <sub>DD</sub>     | V        |

| Input LOW current<br>(switched pull-up)    | $V_{DD} = 2.0 V,$<br>$V_{DD} = 3.0 V, V_{IL} = V_{SS}$                 | I <sub>IL</sub>   | -3<br>-10          | -8<br>-20   | -14<br>-40          | μΑ<br>μΑ |

| Input HIGH current<br>(switched pull-down) | $V_{DD} = 2.0 \text{ V},$<br>$V_{DD} = 3.0 \text{ V}, V_{IH} = V_{DD}$ | I <sub>IH</sub>   | 3<br>10            | 6<br>20     | 14<br>40            | μΑ<br>μΑ |

| Input LOW current<br>(static pull-up)      | $V_{DD} = 2.0 V$<br>$V_{DD} = 3.0 V, V_{IL} = V_{SS}$                  | I <sub>IL</sub>   | -30<br>-80         | -50<br>-160 | -98<br>-320         | μA<br>μA |

| Input LOW current<br>(static pull-down)    | $V_{DD} = 2.0 V$ $V_{DD} = 3.0 V, V_{IH} = V_{DD}$                     | I <sub>IH</sub>   | 20<br>80           | 50<br>160   | 100<br>320          | μΑ<br>μΑ |

| Input leakage current                      | V <sub>IL</sub> = V <sub>SS</sub>                                      | I <sub>IL</sub>   |                    |             | 100                 | nA       |

| Input leakage current                      | $V_{IH} = V_{DD}$                                                      | I <sub>IH</sub>   |                    |             | 100                 | nA       |

| Output LOW current                         | $V_{OL} = 0.2 \times V_{DD}$ $V_{DD} = 2.0 V$ $V_{DD} = 3.0 V$         | I <sub>OL</sub>   | 0.9<br>3           | 1.8<br>5    | 3.6<br>8            | mA<br>mA |

| Output HIGH current                        | $V_{OH} = 0.8 \times V_{DD}$ $V_{DD} = 2.0 V$ $V_{DD} = 3.0 V$         | I <sub>ОН</sub>   | -0.8<br>-3         | -1.7<br>-5  | -3.4<br>-8          | mA<br>mA |

Note: The pin BP20/NTE has a static pull-up resistor during the reset-phase of the microcontroller

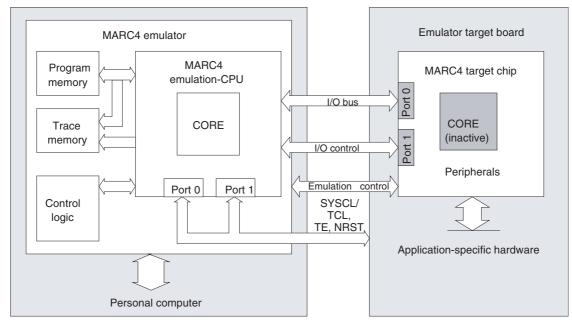

# 30. Emulation

The basic function of emulation is to test and evaluate the customer's program and hardware in real time. This therefore enables the analysis of any timing, hardware or software problem. For emulation purposes, all MARC4 controllers include a special emulation mode. In this mode, the internal CPU core is inactive and the I/O buses are available via Port 0 and Port 1 to allow an external access to the on-chip peripherals. The MARC4 emulator uses this mode to control the peripherals of any MARC4 controller (target chip) and emulates the lost ports for the application.

The MARC4 emulator can stop and restart a program at specified points during execution, making it possible for the applications engineer to view the memory contents and those of various registers during program execution. The designer also gains the ability to analyze the executed instruction sequences and all the I/O activities.

|    | 17.8               | Hardware Interrupts                                                              | 22 |  |  |  |

|----|--------------------|----------------------------------------------------------------------------------|----|--|--|--|

| 18 | Maste              | r Reset                                                                          | 23 |  |  |  |

|    | 18.1               | Power-on Reset and Brown-out Detection                                           | 23 |  |  |  |

| 19 | Voltag             | e Monitor                                                                        | 24 |  |  |  |

| 20 | Clock              | Generation                                                                       | 26 |  |  |  |

|    | 20.1               | Clock Module                                                                     | 26 |  |  |  |

|    | 20.2               | Oscillator Circuits and External Clock Input Stage                               | 27 |  |  |  |

|    | 20.3               | Clock Management                                                                 | 30 |  |  |  |

| 21 | Power              | r-down Modes                                                                     | 31 |  |  |  |

| 22 | Peripheral Modules |                                                                                  |    |  |  |  |

|    | -<br>22.1          | Addressing Peripherals                                                           |    |  |  |  |

| 23 | Bi-dire            | ectional Ports                                                                   | 35 |  |  |  |

|    | 23.1               | Bi-directional Port 1                                                            | 35 |  |  |  |

|    | 23.2               | Bi-directional Port 2                                                            | 36 |  |  |  |

|    | 23.3               | Bi-directional Port 5                                                            | 38 |  |  |  |

|    | 23.4               | Bi-directional Port 4                                                            | 40 |  |  |  |

|    | 23.5               | Bi-directional Port 6                                                            | 41 |  |  |  |

|    | 23.6               | Universal Timer/Counter/ Communication Module (UTCM)                             | 42 |  |  |  |

|    | 23.7               | Timer 1                                                                          | 43 |  |  |  |

|    | 23.8               | Timer 2                                                                          | 47 |  |  |  |

|    | 23.9               | Timer 2 Modes                                                                    | 48 |  |  |  |

|    | 23.10              | Timer 2 Output Modes                                                             | 50 |  |  |  |

|    | 23.11              | Timer 2 Output Signals                                                           | 50 |  |  |  |

|    | 23.12              | 2 Timer 2 Registers                                                              | 53 |  |  |  |

| 24 | 24 Timer 3         |                                                                                  |    |  |  |  |

|    | 24.1               | Features                                                                         | 58 |  |  |  |

|    | 24.2               | Timer/Counter Modes                                                              | 59 |  |  |  |

|    | 24.3               | Timer 3 Modulator/Demodulator Modes                                              | 63 |  |  |  |

|    | 24.4               | Timer 3 Modulator for Carrier Frequency Burst Modulation                         | 66 |  |  |  |

|    | 24.5               | Timer 3 Demodulator for Biphase, Manchester and Pulse-width-modulated<br>Signals | 66 |  |  |  |

|    | 24.6               | Timer 3 Registers                                                                |    |  |  |  |

|    | 24.7               | Timer 3 Capture Register                                                         |    |  |  |  |

|    | 24.8               | Synchronous Serial Interface (SSI)                                               | 72 |  |  |  |