Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

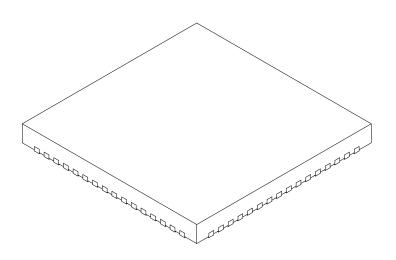

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga006t-i-pt |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2 |        | Pin Number     |                |             |                 |                                                                    |

|-----------|--------|----------------|----------------|-------------|-----------------|--------------------------------------------------------------------|

| Function  | 64-Pin | 80-Pin         | 100-Pin        | I/O         | Input<br>Buffer | Description                                                        |

| AN0       | 16     | 20             | 25             | 1           | ANA             | A/D Analog Inputs.                                                 |

| AN1       | 15     | 19             | 24             | I           | ANA             |                                                                    |

| AN2       | 14     | 18             | 23             | 1           | ANA             |                                                                    |

| AN3       | 13     | 17             | 22             | I           | ANA             |                                                                    |

| AN4       | 12     | 16             | 21             | I           | ANA             |                                                                    |

| AN5       | 11     | 15             | 20             | I           | ANA             |                                                                    |

| AN6       | 17     | 21             | 26             | I           | ANA             |                                                                    |

| AN7       | 18     | 22             | 27             | I           | ANA             |                                                                    |

| AN8       | 21     | 27             | 32             | I           | ANA             | -                                                                  |

| AN9       | 22     | 28             | 33             | I           | ANA             | -                                                                  |

| AN10      | 23     | 29             | 34             | I           | ANA             | -                                                                  |

| AN11      | 24     | 30             | 35             | I           | ANA             |                                                                    |

| AN12      | 27     | 33             | 41             | I           | ANA             | -                                                                  |

| AN13      | 28     | 34             | 42             | I           | ANA             | 1                                                                  |

| AN14      | 29     | 35             | 43             | I           | ANA             | 1                                                                  |

| AN15      | 30     | 36             | 44             | I           | ANA             |                                                                    |

| AVdd      | 19     | 25             | 30             | Р           | _               | Positive Supply for Analog Modules.                                |

| AVss      | 20     | 26             | 31             | Р           | _               | Ground Reference for Analog Modules.                               |

| BCLK1     | 35     | 38             | 48             | 0           | _               | UART1 IrDA <sup>®</sup> Baud Clock.                                |

| BCLK2     | 29     | 35             | 39             | 0           | _               | UART2 IrDA <sup>®</sup> Baud Clock.                                |

| C1IN-     | 12     | 16             | 21             | I           | ANA             | Comparator 1 Negative Input.                                       |

| C1IN+     | 11     | 15             | 20             | I           | ANA             | Comparator 1 Positive Input.                                       |

| C10UT     | 21     | 27             | 32             | 0           | _               | Comparator 1 Output.                                               |

| C2IN-     | 14     | 18             | 23             | I           | ANA             | Comparator 2 Negative Input.                                       |

| C2IN+     | 13     | 17             | 22             | I           | ANA             | Comparator 2 Positive Input.                                       |

| C2OUT     | 22     | 28             | 33             | 0           | _               | Comparator 2 Output.                                               |

| CLKI      | 39     | 49             | 63             | I           | ANA             | Main Clock Input Connection.                                       |

| CLKO      | 40     | 50             | 64             | 0           | _               | System Clock Output.                                               |

| CN0       | 48     | 60             | 74             | I           | ST              | Interrupt-on-Change Inputs.                                        |

| CN1       | 47     | 59             | 73             | I           | ST              |                                                                    |

| CN2       | 16     | 20             | 25             | I           | ST              |                                                                    |

| CN3       | 15     | 19             | 24             | I           | ST              |                                                                    |

| CN4       | 14     | 18             | 23             | I           | ST              | ]                                                                  |

| CN5       | 13     | 17             | 22             | I           | ST              | ]                                                                  |

| CN6       | 12     | 16             | 21             | I           | ST              |                                                                    |

| CN7       | 11     | 15             | 20             | I           | ST              |                                                                    |

| CN8       | 4      | 6              | 10             | I           | ST              |                                                                    |

| CN9       | 5      | 7              | 11             | I           | ST              |                                                                    |

| CN10      | 6      | 8              | 12             | I           | ST              |                                                                    |

| CN11      | 8      | 10             | 14             | I           | ST              |                                                                    |

| CN12      | 30     | 36             | 44             | I           | ST              |                                                                    |

| CN13      | 52     | 66             | 81             | 1           | ST              |                                                                    |

| CN14      | 53     | 67             | 82             | I           | ST              |                                                                    |

| CN15      | 54     | 68             | 83             | I           | ST              |                                                                    |

| CN16      | 55     | 69             | 84             | I           | ST              |                                                                    |

| CN17      | 31     | 39             | 49             | I           | ST              |                                                                    |

| Legend: 1 |        | ut buffor ST - | - Schmitt Tria | aor input k | ouffor ANA      | = Analog level input/output, $I^2C^{TM} = I^2C/SMBus$ input buffer |

#### TABLE 1-2: PIC24FJ128GA010 FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer, ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $l^2C^{TM} = l^2C/SMBus$  input buffer

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

## 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operation with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m+1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction Description |                                                             |  |  |  |  |  |  |

|-------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| ASR                     | Arithmetic shift right source register by one or more bits. |  |  |  |  |  |  |

| SL                      | Shift left source register by one or more bits.             |  |  |  |  |  |  |

| LSR                     | Logical shift right source register by one or more bits.    |  |  |  |  |  |  |

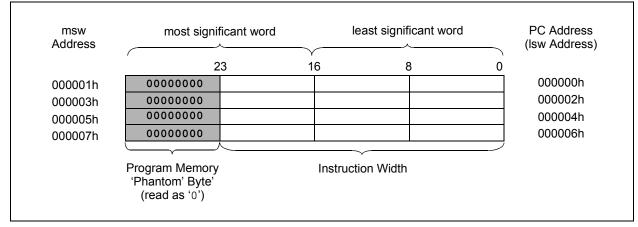

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

## 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h, with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables (IVT), located from 000004h to 0000FFh, and 000100h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. A more detailed discussion of the Interrupt Vector Tables is provided in **Section 7.1 "Interrupt Vector Table**".

## 4.1.3 FLASH CONFIGURATION WORDS

In PIC24FJ128GA010 family devices, the top two words of on-chip program memory are reserved for configuration information. On device Reset, the configuration information is copied into the appropriate Configuration registers. The addresses of the Flash Configuration Word for devices in the PIC24FJ128GA010 family are shown in Table 4-1. Their location in the memory map is shown with the other memory vectors in Figure 4-1.

The Configuration Words in program memory are a compact format. The actual Configuration bits are mapped in several different registers in the configuration memory space. Their order in the Flash Configuration Words do not reflect a corresponding arrangement in the configuration space. Additional details on the device Configuration Words are provided in **Section 24.1** "**Configuration Bits**".

| TABLE 4-1: | FLASH CONFIGURATION    |

|------------|------------------------|

|            | WORDS FOR              |

|            | PIC24FJ128GA010 FAMILY |

|            | DEVICES                |

| Device       | Program<br>Memory<br>(Words) | Configuration<br>Word<br>Addresses |

|--------------|------------------------------|------------------------------------|

| PIC24FJ64GA  | 22,016                       | 00ABFCh:<br>00ABFEh                |

| PIC24FJ96GA  | 32,768                       | 00FFFCh:<br>00FFFEh                |

| PIC24FJ128GA | 44,032                       | 0157FCh:<br>0157FEh                |

## FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

## TABLE 4-15: A/D REGISTER MAP

| IADLL 4   | -15. |        |                      |        |        |        |        |        |          |            |       |       |       |        |        |        |        |               |

|-----------|------|--------|----------------------|--------|--------|--------|--------|--------|----------|------------|-------|-------|-------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7      | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| ADC1BUF0  | 0300 |        |                      |        |        |        |        |        | A/D Data | a Buffer 0 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF1  | 0302 |        |                      |        |        |        |        |        | A/D Data | a Buffer 1 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF2  | 0304 |        |                      |        |        |        |        |        | A/D Data | a Buffer 2 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF3  | 0306 |        | A/D Data Buffer 3 xx |        |        |        |        |        |          |            |       |       | xxxx  |        |        |        |        |               |

| ADC1BUF4  | 0308 |        | A/D Data Buffer 4    |        |        |        |        |        |          |            |       |       | xxxx  |        |        |        |        |               |

| ADC1BUF5  | 030A |        | A/D Data Buffer 5    |        |        |        |        |        |          |            |       | xxxx  |       |        |        |        |        |               |

| ADC1BUF6  | 030C |        |                      |        |        |        |        |        | A/D Data | a Buffer 6 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF7  | 030E |        |                      |        |        |        |        |        | A/D Data | a Buffer 7 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF8  | 0310 |        |                      |        |        |        |        |        | A/D Data | a Buffer 8 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF9  | 0312 |        |                      |        |        |        |        |        | A/D Data | a Buffer 9 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFA  | 0314 |        |                      |        |        |        |        |        | A/D Data | Buffer 10  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFB  | 0316 |        |                      |        |        |        |        |        | A/D Data | Buffer 11  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFC  | 0318 |        |                      |        |        |        |        |        | A/D Data | Buffer 12  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFD  | 031A |        |                      |        |        |        |        |        | A/D Data | Buffer 13  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFE  | 031C |        |                      |        |        |        |        |        | A/D Data | Buffer 14  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFF  | 031E |        |                      | -      |        |        |        |        | A/D Data | Buffer 15  | -     |       | -     | -      |        | -      | -      | xxxx          |

| AD1CON1   | 0320 | ADON   | _                    | ADSIDL | —      | —      | —      | FORM1  | FORM0    | SSRC2      | SSRC1 | SSRC0 | —     | —      | ASAM   | SAMP   | DONE   | 0000          |

| AD1CON2   | 0322 | VCFG2  | VCFG1                | VCFG0  | r      | —      | CSCNA  | _      | —        | BUFS       | —     | SMPI3 | SMPI2 | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000          |

| AD1CON3   | 0324 | ADRC   | _                    | _      | SAMC4  | SAMC3  | SAMC2  | SAMC1  | SAMC0    | ADCS7      | ADCS6 | ADCS5 | ADCS4 | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000          |

| AD1CHS    | 0328 | CH0NB  | _                    |        | —      | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0   | CH0NA      |       | _     |       | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000          |

| AD1PCFG   | 032C | PCFG15 | PCFG14               | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9  | PCFG8    | PCFG7      | PCFG6 | PCFG5 | PCFG4 | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000          |

| AD1CSSL   | 0330 | CSSL15 | CSSL14               | CSSL13 | CSSL12 | CSSL11 | CSSL10 | CSSL9  | CSSL8    | CSSL7      | CSSL6 | CSSL5 | CSSL4 | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000          |

| 1         |      |        |                      |        |        |        |        |        |          |            |       |       |       |        |        |        |        |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'; r = reserved, maintain as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-16: PORTA REGISTER MAP

| File Name | Addr | Bit 15                 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10                 | Bit 9                 | Bit 8 | Bit 7     | Bit 6     | Bit 5                | Bit 4                 | Bit 3                | Bit 2                | Bit 1                | Bit 0                | All<br>Resets |

|-----------|------|------------------------|------------------------|--------|--------|--------|------------------------|-----------------------|-------|-----------|-----------|----------------------|-----------------------|----------------------|----------------------|----------------------|----------------------|---------------|

| TRISA     | 02C0 | TRISA15 <sup>(1)</sup> | TRISA14 <sup>(1)</sup> | _      | _      | -      | TRISA10 <sup>(1)</sup> | TRISA9 <sup>(1)</sup> | _     | TRISA7(2) | TRISA6(2) | TRISA5(2)            | TRISA4 <sup>(2)</sup> | TRISA3(2)            | TRISA2(2)            | TRISA1(2)            | TRISA0(2)            | C6FF          |

| PORTA     | 02C2 | RA15 <sup>(1)</sup>    | RA14 <sup>(1)</sup>    | _      | —      | _      | RA10 <sup>(1)</sup>    | RA9 <sup>(1)</sup>    | —     | RA7       | RA6       | RA5 <sup>(2)</sup>   | RA4 <sup>(2)</sup>    | RA3 <sup>(2)</sup>   | RA2 <sup>(2)</sup>   | RA1 <sup>(2)</sup>   | RA0 <sup>(2)</sup>   | xxxx          |

| LATA      | 02C4 | LATA15 <sup>(1)</sup>  | LATA14 <sup>(1)</sup>  | _      | _      | _      | LATA10 <sup>(1)</sup>  | LATA9 <sup>(1)</sup>  | _     | LATA7     | LATA6     | LATA5 <sup>(2)</sup> | LATA4 <sup>(2)</sup>  | LATA3 <sup>(2)</sup> | LATA2 <sup>(2)</sup> | LATA1 <sup>(2)</sup> | LATA0 <sup>(2)</sup> | xxxx          |

| ODCA      | 06C0 | ODA15 <sup>(1)</sup>   | ODA14 <sup>(1)</sup>   | _      | _      | _      | ODA10 <sup>(1)</sup>   | ODA9 <sup>(1)</sup>   | _     | ODA7      | ODA6      | ODA5 <sup>(2)</sup>  | ODA4 <sup>(2)</sup>   | ODA3 <sup>(2)</sup>  | ODA2 <sup>(2)</sup>  | ODA1 <sup>(2)</sup>  | ODA0 <sup>(2)</sup>  | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 100-pin devices.

Note 1: Implemented in 80-pin and 100-pin devices only.

2: Implemented in 100-pin devices only.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

|   | ; Set up NVMCO | N for row programming operation | ns  |                                       |

|---|----------------|---------------------------------|-----|---------------------------------------|

|   | MOV            | #0x4001, W0                     | ;   |                                       |

|   | MOV            | W0, NVMCON                      | ;   | Initialize NVMCON                     |

|   | ; Set up a poi | nter to the first program memo: | ry  | location to be written                |

|   | ; program memo | ry selected, and writes enabled | d   |                                       |

|   | MOV            | #0x0000, W0                     | ;   |                                       |

|   | MOV            | W0, TBLPAG                      | ;   | Initialize PM Page Boundary SFR       |

|   | MOV            | #0x6000, W0                     | ;   | An example program memory address     |

|   | ; Perform the  | TBLWT instructions to write the | e i | latches                               |

|   | ; 0th_program_ | word                            |     |                                       |

|   | MOV            | #LOW_WORD_0, W2                 | ;   |                                       |

|   | MOV            | <pre>#HIGH_BYTE_0, W3</pre>     | ;   |                                       |

|   | TBLWTL         | W2, [W0]                        | ;   | Write PM low word into program latch  |

|   | TBLWTH         | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | ; 1st_program_ | word                            |     |                                       |

|   | MOV            | #LOW_WORD_1, W2                 | ;   |                                       |

|   |                | #HIGH_BYTE_1, W3                | ;   |                                       |

|   |                | W2, [W0]                        |     | Write PM low word into program latch  |

|   |                | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | ; 2nd_program  | —                               |     |                                       |

|   | MOV            | #LOW_WORD_2, W2                 | ;   |                                       |

|   |                | <pre>#HIGH_BYTE_2, W3</pre>     | ;   |                                       |

|   |                | W2, [W0]                        |     | Write PM low word into program latch  |

|   |                | W3, [W0++]                      | ;   | Write PM high byte into program latch |

|   | •              |                                 |     |                                       |

|   | •              |                                 |     |                                       |

|   | •              | _                               |     |                                       |

| 1 | ; 63rd_program | —                               |     |                                       |

|   | MOV            | #LOW_WORD_31, W2                | ;   |                                       |

|   |                | <pre>#HIGH_BYTE_31, W3</pre>    | ;   |                                       |

|   |                | W2, [W0]                        |     | Write PM low word into program latch  |

| 1 | TRTMLH         | W3, [W0]                        | ;   | Write PM high byte into program latch |

|   |                |                                 |     |                                       |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | ;                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the program/erase sequence      |

| BTSC | NVMCON, #15 | ; and wait for it to be                 |

| BRA  | \$-2        | ; completed                             |

|      |             |                                         |

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to **Section 8. "Interrupts"** (DS39707) in the *"PIC24F Family Reference Manual"* for more information.

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24F CPU. It has the following features:

- Up to 8 processor exceptions and software traps

- 7 user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- · Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of 8 non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FJ128GA010 family devices implement nonmaskable traps and unique interrupts. These are summarized in Table 7-1 and Table 7-2.

### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24F device clears its registers in response to a Reset which forces the PC to zero. The microcontroller then begins program execution at location, 00000h. The user programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| REGISTER         | <i>i</i> - <i>i</i> | INTERRUPT                                    |                  |                  |                 |                 |        |

|------------------|---------------------|----------------------------------------------|------------------|------------------|-----------------|-----------------|--------|

| U-0              | U-0                 | R/W-0                                        | U-0              | U-0              | U-0             | R/W-0           | U-0    |

| —                | —                   | PMPIF                                        | _                | —                | _               | OC5IF           | _      |

| bit 15           |                     |                                              |                  |                  |                 |                 | bit 8  |

|                  |                     |                                              |                  |                  |                 |                 |        |

| R/W-0            | R/W-0               | R/W-0                                        | U-0              | U-0              | U-0             | R/W-0           | R/W-0  |

| IC5IF            | IC4IF               | IC3IF                                        | —                | —                | —               | SPI2IF          | SPF2IF |

| bit 7            |                     |                                              |                  |                  |                 |                 | bit 0  |

|                  |                     |                                              |                  |                  |                 |                 |        |

| Legend:          |                     |                                              |                  |                  |                 |                 |        |

| R = Readabl      |                     | W = Writable                                 |                  | •                | nented bit, rea |                 |        |

| -n = Value at    | POR                 | '1' = Bit is set                             |                  | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

| bit 15-14        | Unimplomon          | ted. Dood on '                               | o'               |                  |                 |                 |        |

| bit 13           | •                   | i <b>ted:</b> Read as 'i<br>llel Master Port |                  | a Status bit     |                 |                 |        |

| DIL 15           |                     | request has occ                              |                  | y Status Dit     |                 |                 |        |

|                  |                     | request has not                              |                  |                  |                 |                 |        |

| bit 12-10        | Unimplemen          | ted: Read as '                               | 0'               |                  |                 |                 |        |

| bit 9            | OC5IF: Output       | ut Compare Ch                                | annel 5 Interr   | upt Flag Status  | s bit           |                 |        |

|                  |                     | request has occ                              |                  |                  |                 |                 |        |

|                  | -                   | request has not                              |                  |                  |                 |                 |        |

| bit 8            | •                   | ted: Read as '                               |                  |                  |                 |                 |        |

| bit 7            | •                   | Capture Channe                               | •                | -lag Status bit  |                 |                 |        |

|                  |                     | request has occ<br>request has not           |                  |                  |                 |                 |        |

| bit 6            | •                   | Capture Channe                               |                  | Flag Status bit  |                 |                 |        |

|                  | •                   | request has occ                              | •                | - 3              |                 |                 |        |

|                  | 0 = Interrupt       | request has not                              | occurred         |                  |                 |                 |        |

| bit 5            | IC3IF: Input C      | Capture Channe                               | el 3 Interrupt I | Flag Status bit  |                 |                 |        |

|                  |                     | request has occ                              |                  |                  |                 |                 |        |

| h:+ 4 0          | •                   | request has not                              |                  |                  |                 |                 |        |

| bit 4-2<br>bit 1 | -                   | ted: Read as '                               |                  | -:+              |                 |                 |        |

|                  |                     | Event Interrup<br>request has occ            | -                | JIL              |                 |                 |        |

|                  |                     | request has not                              |                  |                  |                 |                 |        |

| bit 0            |                     | 2 Fault Interrup                             |                  | oit              |                 |                 |        |

|                  |                     | request has occ                              |                  |                  |                 |                 |        |

|                  | 0 = Interrupt       | request has not                              | occurred         |                  |                 |                 |        |

## REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

## REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0             | U-0                                                               | U-0          | U-0 | U-0                                | U-0     | U-0     | U-0     |  |  |

|-----------------|-------------------------------------------------------------------|--------------|-----|------------------------------------|---------|---------|---------|--|--|

| —               |                                                                   | —            | _   | —                                  | —       | —       | —       |  |  |

| bit 15          | •                                                                 |              |     | •                                  |         |         | bit 8   |  |  |

|                 |                                                                   |              |     |                                    |         |         |         |  |  |

| U-0             | U-0                                                               | U-0          | U-0 | U-0                                | R/W-1   | R/W-0   | R/W-0   |  |  |

| _               |                                                                   | _            |     | _                                  | INT1IP2 | INT1IP1 | INT1IP0 |  |  |

| bit 7           | •                                                                 |              |     | •                                  |         |         | bit 0   |  |  |

|                 |                                                                   |              |     |                                    |         |         |         |  |  |

| Legend:         |                                                                   |              |     |                                    |         |         |         |  |  |

| R = Readable    | bit                                                               | W = Writable | bit | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| -n = Value at F | e at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |              |     |                                    |         |         | nown    |  |  |

#### bit 15-3 Unimplemented: Read as '0'

- INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

bit 2-0

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0              | R/W-1                                                                           | R/W-0                                                                      | R/W-0                                                | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|--|

| _                | CRCIP2                                                                          | CRCIP1                                                                     | CRCIP0                                               | _                | U2ERIP2          | U2ERIP1         | U2ERIP0 |  |  |  |  |  |  |  |

| bit 15           |                                                                                 | •                                                                          | •                                                    |                  |                  | ·               | bit 8   |  |  |  |  |  |  |  |

| U-0              | R/W-1                                                                           | R/W-0                                                                      | R/W-0                                                | U-0              | U-0              | U-0             | U-0     |  |  |  |  |  |  |  |

|                  | U1ERIP2                                                                         | U1ERIP1                                                                    | U1ERIP0                                              | <u> </u>         |                  |                 | 0-0     |  |  |  |  |  |  |  |

| bit 7            | UTERII 2                                                                        | OTEINIT                                                                    | OTENITO                                              |                  |                  |                 | bit C   |  |  |  |  |  |  |  |

|                  |                                                                                 |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

| Legend:          | la hit                                                                          |                                                                            | L:4                                                  |                  | mented bit meet  |                 |         |  |  |  |  |  |  |  |

| R = Readab       |                                                                                 | W = Writable                                                               |                                                      | -                | mented bit, read |                 |         |  |  |  |  |  |  |  |

| -n = Value a     | TPOR                                                                            | '1' = Bit is set                                                           |                                                      | '0' = Bit is cle | eared            | x = Bit is unkr | lown    |  |  |  |  |  |  |  |

| bit 15           | Unimplemen                                                                      | ted: Read as '                                                             | 0'                                                   |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 14-12        | -                                                                               | CRC Generato                                                               |                                                      | ot Priority bits |                  |                 |         |  |  |  |  |  |  |  |

|                  |                                                                                 | 111 = Interrupt is Priority 7 (highest priority interrupt)                 |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  | •                                                                               |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  |                                                                                 |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  | •<br>001 = Interru                                                              | ot is Priority 1                                                           |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  |                                                                                 | ot source is dis                                                           | abled                                                |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 11           | -                                                                               | ted: Read as '                                                             |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 10-8         | -                                                                               | UART2 Erro                                                                 |                                                      | ority bits       |                  |                 |         |  |  |  |  |  |  |  |

|                  |                                                                                 | ot is Priority 7 (                                                         |                                                      | •                |                  |                 |         |  |  |  |  |  |  |  |

|                  | •                                                                               | -                                                                          |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  | •                                                                               |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  | •                                                                               |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  | 001 = Interru                                                                   | ot is Priority 1                                                           |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  | 001 = Interru<br>000 = Interru                                                  | ot is Priority 1<br>ot source is dis                                       | abled                                                |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 7            | 000 = Interru                                                                   |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen                                                     | ot source is dis                                                           | 0'                                                   | prity bits       |                  |                 |         |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                      | ot source is dis<br><b>ted:</b> Read as '                                  | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                      | ot source is dis<br>ted: Read as '<br>•: UART1 Error                       | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                      | ot source is dis<br>ted: Read as '<br>•: UART1 Error                       | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interruj<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interruj<br>•<br>•         | ot source is dis<br>ted: Read as '<br>•: UART1 Error<br>ot is Priority 7 ( | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |  |  |  |

|                  | 000 = Interruj<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interruj<br>001 = Interruj | ot source is dis<br>ted: Read as '<br>•: UART1 Error<br>ot is Priority 7 ( | <sup>0'</sup><br>r Interrupt Pric<br>highest priorit | •                |                  |                 |         |  |  |  |  |  |  |  |

## REGISTER 7-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| REGISTER      | 8-2: CLKDI                                                                                                | V: CLOCK D                                                                                                                                    |                                    | GISTER               |                  |                 |        |

|---------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------|------------------|-----------------|--------|

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                                                         | R/W-0                              | R/W-0                | R/W-0            | R/W-0           | R/W-1  |

| ROI           | DOZE2                                                                                                     | DOZE1                                                                                                                                         | DOZE0                              | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1          | RCDIV0 |

| bit 15        |                                                                                                           |                                                                                                                                               |                                    |                      |                  |                 | bit    |

| U-0           | U-0                                                                                                       | U-0                                                                                                                                           | U-0                                | U-0                  | U-0              | U-0             | U-0    |

|               |                                                                                                           |                                                                                                                                               | 0-0                                |                      |                  |                 |        |

| bit 7         |                                                                                                           |                                                                                                                                               |                                    |                      |                  |                 | bit    |

| Legend:       |                                                                                                           |                                                                                                                                               |                                    |                      |                  |                 |        |

| R = Readabl   | e bit                                                                                                     | W = Writable                                                                                                                                  | bit                                | U = Unimplen         | nented bit, read | 1 as '0'        |        |

| -n = Value at |                                                                                                           | '1' = Bit is set                                                                                                                              |                                    | '0' = Bit is clea    |                  | x = Bit is unkr | าดพท   |

|               |                                                                                                           |                                                                                                                                               |                                    |                      |                  |                 |        |

| bit 14-12     | 111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1 | CPU Periphera                                                                                                                                 |                                    |                      |                  |                 |        |

| bit 11        | 1 = DOZE<2:                                                                                               | E Enable bit <sup>(1</sup><br>:0> bits specify<br>pheral clock ra                                                                             | the CPU per                        | ipheral clock ra     | tio              |                 |        |

| bit 10-8      | RCDIV<2:0>:<br>111 = 31.25 k<br>110 = 125 kH<br>101 = 250 kH                                              | FRC Postscal<br>(Hz (divide-by-64<br>z (divide-by-32<br>z (divide-by-32<br>z (divide-by-16<br>(divide-by-8)<br>(divide-by-4)<br>(divide-by-2) | er Select bits<br>256)<br>4)<br>2) |                      |                  |                 |        |

| bit 7-0       | Unimplemen                                                                                                | ted: Read as '                                                                                                                                | 0'                                 |                      |                  |                 |        |

|               |                                                                                                           |                                                                                                                                               |                                    |                      |                  |                 |        |

## REGISTER 8-2: CLKDIV: CLOCK DIVIDER REGISTER

Note 1: This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

## 10.0 I/O PORTS

| Note: | This data sheet summarizes the features<br>of this group of PIC24F devices. It is not |

|-------|---------------------------------------------------------------------------------------|

|       | intended to be a comprehensive refer-                                                 |

|       | ence source. Refer to Section 12. "I/O                                                |

|       | Ports with Peripheral Pin Select (PPS)"                                               |

|       | (DS39711) in the "PIC24F Family                                                       |

|       | Reference Manual" for more information.                                               |

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

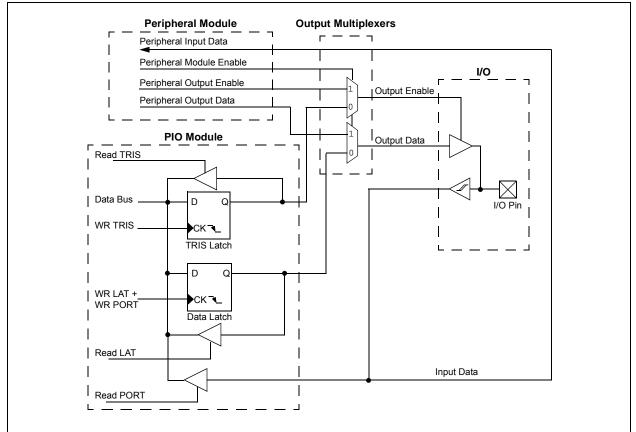

## 10.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless, regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

### FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

NOTES:

## 19.2 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value loaded into the lower half of RCFGCAL is multiplied by four and will either be added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute.

### EQUATION 19-1:

(Ideal Frequency<sup>†</sup> – Measured Frequency) \* 60 = Clocks per Minute

† Ideal Frequency = 32,768 Hz

3. a) If the oscillator is faster then ideal (negative result form Step 2), the RCFGCAL register value needs to be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

b) If the oscillator is slower then ideal (positive result from Step 2), the RCFGCAL register value needs to be positive. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

Divide the number of error clocks per minute by 4 to get the correct CAL value and load the RCFGCAL register with the correct value. (Each 1-bit increment in CAL adds or subtracts 4 pulses). Load the RCFGCAL register with the correct value.

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off or immediately after the rising edge of the seconds pulse.

| Note: | It is up to the user to include in the error  |

|-------|-----------------------------------------------|

|       | value, the initial error of the crystal drift |

|       | due to temperature and drift due to crystal   |

|       | aging.                                        |

## 19.3 Alarm

- Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>, Register 19-3)

- One-time alarm and repeat alarm options are available

### 19.3.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVALH:ALRMVALL should only take place when ALRMEN = 0.

As shown in Figure 19-2, the interval selection of the alarm is configured through the AMASK bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur. The alarm can also be configured to repeat, based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the lower half of the ALCFGRPT register.

When ALCFGRPT = 0.0 and the CHIME (ALCFGRPT<14>) bit = 0, the repeat function is disabled and only a single alarm will occur. The alarm can be repeated up to 255 times by loading the lower half of the ALCFGRPT register with FFh.

After each alarm is issued, the ALCFGRPT register is decremented by one. Once the register has reached '00', the alarm will be issued one last time, after which, the ALRMEN bit will be cleared automatically and the alarm will turn off. Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the ALCFGRPT register reaches '00', it will roll over to FF and continue counting indefinitely when CHIME = 1.

## 19.3.2 ALARM INTERRUPT

At every alarm event an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a trigger clock to other peripherals.

Note: Changing any of the registers, other then the RCFGCAL and ALCFGRPT registers, and the CHIME bit while the alarm is enabled (ALRMEN = 1), can result in a false alarm event leading to a false alarm interrupt. To avoid a false alarm event, the timer and alarm values should only be changed while the alarm is disabled (ALRMEN = 0). It is recommended that the ALCFGRPT register and CHIME bit be changed when RTCSYNC = 0.

NOTES:

## 24.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 32. "High-Level Device Integration" (DS39719) in the "PIC24F Family Reference Manual" for more information.

PIC24FJ128GA010 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

## 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped, starting at program memory location, F80000h. A complete list is shown in Table 24-1. A detailed explanation of the various bit functions is provided in Register 24-1 through Register 24-4.

Note that address, F80000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFFh), which can only be accessed using table reads and table writes.

### 24.1.1 CONSIDERATIONS FOR CONFIGURING PIC24FJ128GA010 FAMILY DEVICES

In PIC24FJ128GA010 family devices, the configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in the two words at the top of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 24-1. These are packed representations of the actual device Configuration bits, whose actual locations are distributed among five locations in configuration space. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

## TABLE 24-1:FLASH CONFIGURATION<br/>WORD LOCATIONS

| Device       | Configuration Word<br>Addresses |         |  |  |  |  |  |

|--------------|---------------------------------|---------|--|--|--|--|--|

|              | 1                               | 2       |  |  |  |  |  |

| PIC24FJ64GA  | 00ABFEh                         | 00ABFCh |  |  |  |  |  |

| PIC24FJ96GA  | 00FFFEh                         | 00FFFCh |  |  |  |  |  |

| PIC24FJ128GA | 0157FEh                         | 0157FCh |  |  |  |  |  |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The Configuration bits are reloaded from the Flash Configuration Word on any device Reset.

The upper byte of both Flash Configuration Words in program memory should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

## **REGISTER 24-2: FLASH CONFIGURATION WORD 2**

| U-1                | U-1                                                                               | U-1                                                                           | U-1                                                                     | U-1                                  | U-1               | U-1               | U-1     |  |  |  |

|--------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------|-------------------|-------------------|---------|--|--|--|

| —                  | _                                                                                 | _                                                                             | —                                                                       |                                      |                   |                   | —       |  |  |  |

| bit 23             | •                                                                                 |                                                                               |                                                                         |                                      |                   | •                 | bit 16  |  |  |  |

|                    |                                                                                   |                                                                               |                                                                         |                                      |                   |                   |         |  |  |  |

| R/PO-1             | U-1                                                                               | U-1                                                                           | U-1                                                                     | U-1                                  | R/PO-1            | R/PO-1            | R/PO-1  |  |  |  |

| IESO               | —                                                                                 | <u> </u>                                                                      | —                                                                       |                                      | FNOSC2            | FNOSC1            | FNOSC0  |  |  |  |

| bit 15 bit         |                                                                                   |                                                                               |                                                                         |                                      |                   |                   |         |  |  |  |

|                    |                                                                                   |                                                                               |                                                                         |                                      |                   |                   |         |  |  |  |

| R/PO-1             | R/PO-1                                                                            | R/PO-1                                                                        | U-1                                                                     | U-1                                  | U-1               | R/PO-1            | R/PO-1  |  |  |  |

| FCKSM1             | FCKSM0                                                                            | OSCIOFCN                                                                      | —                                                                       | —                                    | —                 | POSCMD1           | POSCMD0 |  |  |  |

| bit 7              |                                                                                   |                                                                               |                                                                         |                                      |                   |                   | bit 0   |  |  |  |

|                    |                                                                                   |                                                                               |                                                                         |                                      |                   |                   |         |  |  |  |

| Legend:            |                                                                                   | x = Bit is unkn                                                               |                                                                         |                                      |                   |                   |         |  |  |  |

| R = Reada          |                                                                                   | PO = Program                                                                  |                                                                         | -                                    | nted bit, read as | '0'               |         |  |  |  |

| -n = Value         | when device                                                                       | is unprogramme                                                                | ed                                                                      | '1' = Bit is set                     |                   | '0' = Bit is clea | ared    |  |  |  |

|                    |                                                                                   |                                                                               |                                                                         |                                      |                   |                   |         |  |  |  |

| bit 23-16          | -                                                                                 | nted: Read as '                                                               |                                                                         |                                      |                   |                   |         |  |  |  |

| bit 15             |                                                                                   | al External Swit                                                              |                                                                         |                                      |                   |                   |         |  |  |  |

|                    |                                                                                   | ode (Two-Speed<br>ode (Two-Speed                                              |                                                                         |                                      |                   |                   |         |  |  |  |

| bit 14-11          |                                                                                   | nted: Read as '                                                               | • /                                                                     | ISabled                              |                   |                   |         |  |  |  |

| bit 10-8           | -                                                                                 | >: Initial Oscilla                                                            |                                                                         |                                      |                   |                   |         |  |  |  |

| bit 10-0           |                                                                                   | RC Oscillator wi                                                              |                                                                         | (FRCDIV)                             |                   |                   |         |  |  |  |