Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decans                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-VFQFN Exposed Pad                                                          |

| Supplier Device Package    | 64-VQFN (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga006-i-mr |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

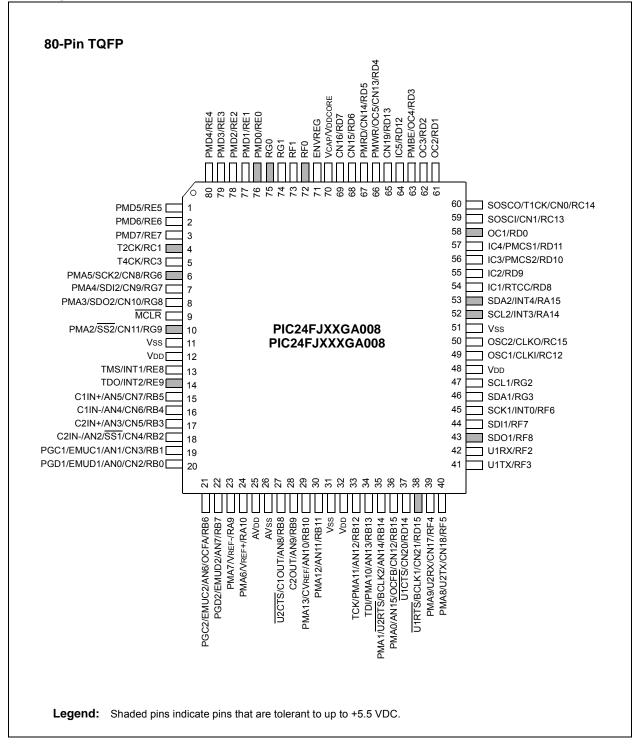

# **Pin Diagrams (Continued)**

#### 2.4 **Voltage Regulator Pins** (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This section applies only to PIC24F J      |

|-------|--------------------------------------------|

|       | devices with an on-chip voltage regulator. |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- · For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to Section 24.2 "On-Chip Voltage Regulator" for details on connecting and using the on-chip regulator.

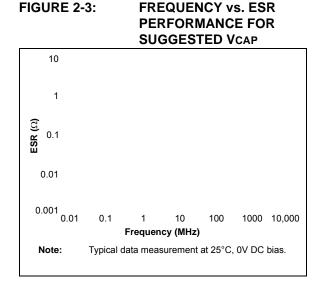

When the regulator is enabled, a low-ESR (<  $5\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10 µF connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specification can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to Section 27.0 "Electrical Characteristics" for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to Section 27.0 "Electrical Characteristics" for information on VDD and VDDCORE.

| TABLE 2-1: | SUITABLE CAPACITOR | EQUIVALENTS            |                |               |              |

|------------|--------------------|------------------------|----------------|---------------|--------------|

| Make       | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range  |

| TDK        | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| TDK        | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Panasonic  | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Panasonic  | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Murata     | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Murata     | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

### TABLE 4-15: A/D REGISTER MAP

| IADLL 4   | -15. |        |                      |        |        |        |        |        |          |            |       |       |       |        |        |        |        |               |

|-----------|------|--------|----------------------|--------|--------|--------|--------|--------|----------|------------|-------|-------|-------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7      | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| ADC1BUF0  | 0300 |        |                      |        |        |        |        |        | A/D Data | a Buffer 0 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF1  | 0302 |        |                      |        |        |        |        |        | A/D Data | a Buffer 1 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF2  | 0304 |        |                      |        |        |        |        |        | A/D Data | a Buffer 2 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF3  | 0306 |        |                      |        |        |        |        |        | A/D Data | a Buffer 3 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF4  | 0308 |        |                      |        |        |        |        |        | A/D Data | a Buffer 4 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF5  | 030A |        |                      |        |        |        |        |        | A/D Data | a Buffer 5 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF6  | 030C |        |                      |        |        |        |        |        | A/D Data | a Buffer 6 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF7  | 030E |        |                      |        |        |        |        |        | A/D Data | a Buffer 7 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF8  | 0310 |        |                      |        |        |        |        |        | A/D Data | a Buffer 8 |       |       |       |        |        |        |        | xxxx          |

| ADC1BUF9  | 0312 |        | A/D Data Buffer 9 xx |        |        |        |        |        |          |            |       |       |       |        |        | xxxx   |        |               |

| ADC1BUFA  | 0314 |        |                      |        |        |        |        |        | A/D Data | Buffer 10  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFB  | 0316 |        |                      |        |        |        |        |        | A/D Data | Buffer 11  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFC  | 0318 |        |                      |        |        |        |        |        | A/D Data | Buffer 12  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFD  | 031A |        |                      |        |        |        |        |        | A/D Data | Buffer 13  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFE  | 031C |        |                      |        |        |        |        |        | A/D Data | Buffer 14  |       |       |       |        |        |        |        | xxxx          |

| ADC1BUFF  | 031E |        |                      | -      |        |        |        |        | A/D Data | Buffer 15  | -     |       | -     | -      |        | -      | -      | xxxx          |

| AD1CON1   | 0320 | ADON   | _                    | ADSIDL | —      | —      | —      | FORM1  | FORM0    | SSRC2      | SSRC1 | SSRC0 | —     | —      | ASAM   | SAMP   | DONE   | 0000          |

| AD1CON2   | 0322 | VCFG2  | VCFG1                | VCFG0  | r      | —      | CSCNA  | _      | —        | BUFS       | —     | SMPI3 | SMPI2 | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000          |

| AD1CON3   | 0324 | ADRC   | _                    | _      | SAMC4  | SAMC3  | SAMC2  | SAMC1  | SAMC0    | ADCS7      | ADCS6 | ADCS5 | ADCS4 | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000          |

| AD1CHS    | 0328 | CH0NB  | _                    |        | —      | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0   | CH0NA      |       | _     |       | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000          |

| AD1PCFG   | 032C | PCFG15 | PCFG14               | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9  | PCFG8    | PCFG7      | PCFG6 | PCFG5 | PCFG4 | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000          |

| AD1CSSL   | 0330 | CSSL15 | CSSL14               | CSSL13 | CSSL12 | CSSL11 | CSSL10 | CSSL9  | CSSL8    | CSSL7      | CSSL6 | CSSL5 | CSSL4 | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000          |

| 1         |      |        |                      |        |        |        |        |        |          |            |       |       |       |        |        |        |        |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'; r = reserved, maintain as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-16: PORTA REGISTER MAP

| File Name | Addr | Bit 15                 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10                 | Bit 9                 | Bit 8 | Bit 7     | Bit 6     | Bit 5                | Bit 4                 | Bit 3                | Bit 2                | Bit 1                | Bit 0                | All<br>Resets |

|-----------|------|------------------------|------------------------|--------|--------|--------|------------------------|-----------------------|-------|-----------|-----------|----------------------|-----------------------|----------------------|----------------------|----------------------|----------------------|---------------|

| TRISA     | 02C0 | TRISA15 <sup>(1)</sup> | TRISA14 <sup>(1)</sup> | _      | _      | -      | TRISA10 <sup>(1)</sup> | TRISA9 <sup>(1)</sup> | _     | TRISA7(2) | TRISA6(2) | TRISA5(2)            | TRISA4 <sup>(2)</sup> | TRISA3(2)            | TRISA2(2)            | TRISA1(2)            | TRISA0(2)            | C6FF          |

| PORTA     | 02C2 | RA15 <sup>(1)</sup>    | RA14 <sup>(1)</sup>    | _      | —      | _      | RA10 <sup>(1)</sup>    | RA9 <sup>(1)</sup>    | —     | RA7       | RA6       | RA5 <sup>(2)</sup>   | RA4 <sup>(2)</sup>    | RA3 <sup>(2)</sup>   | RA2 <sup>(2)</sup>   | RA1 <sup>(2)</sup>   | RA0 <sup>(2)</sup>   | xxxx          |

| LATA      | 02C4 | LATA15 <sup>(1)</sup>  | LATA14 <sup>(1)</sup>  | _      | _      | _      | LATA10 <sup>(1)</sup>  | LATA9 <sup>(1)</sup>  | _     | LATA7     | LATA6     | LATA5 <sup>(2)</sup> | LATA4 <sup>(2)</sup>  | LATA3 <sup>(2)</sup> | LATA2 <sup>(2)</sup> | LATA1 <sup>(2)</sup> | LATA0 <sup>(2)</sup> | xxxx          |

| ODCA      | 06C0 | ODA15 <sup>(1)</sup>   | ODA14 <sup>(1)</sup>   | _      | _      | _      | ODA10 <sup>(1)</sup>   | ODA9 <sup>(1)</sup>   | _     | ODA7      | ODA6      | ODA5 <sup>(2)</sup>  | ODA4 <sup>(2)</sup>   | ODA3 <sup>(2)</sup>  | ODA2 <sup>(2)</sup>  | ODA1 <sup>(2)</sup>  | ODA0 <sup>(2)</sup>  | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 100-pin devices.

Note 1: Implemented in 80-pin and 100-pin devices only.

2: Implemented in 100-pin devices only.

### TABLE 4-17: PORTB REGISTER MAP

| File Name | Addr | Bit 15  | Bit 14  | Bit 13                 | Bit 12                 | Bit 11                 | Bit 10                 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|------------------------|------------------------|------------------------|------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 <sup>(1)</sup> | TRISB12 <sup>(1)</sup> | TRISB11 <sup>(1)</sup> | TRISB10 <sup>(1)</sup> | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13 <sup>(1)</sup>    | RB12 <sup>(1)</sup>    | RB11 <sup>(1)</sup>    | RB10 <sup>(1)</sup>    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13 <sup>(1)</sup>  | LATB12 <sup>(1)</sup>  | LATB11 <sup>(1)</sup>  | LATB10 <sup>(1)</sup>  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB      | 06C6 | ODB15   | ODB14   | ODB13 <sup>(1)</sup>   | ODB12 <sup>(1)</sup>   | ODB11 <sup>(1)</sup>   | ODB10 <sup>(1)</sup>   | ODB9   | ODB8   | ODB7   | ODB6   | ODB5   | ODB4   | ODB3   | ODB2   | ODB1   | ODB0   | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 100-pin devices

Note 1: Unimplemented when JTAG is enabled.

#### TABLE 4-18: PORTC REGISTER MAP

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4                | Bit 3                | Bit 2                | Bit 1                 | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|----------------------|----------------------|----------------------|-----------------------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      | _      | _     | —     | —     | —     | —     | TRISC4(2)            | TRISC3(1)            | TRISC2(2)            | TRISC1 <sup>(1)</sup> | _     | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    |        | _      | _     | _     | _     | _     | _     | RC4 <sup>(2)</sup>   | RC3 <sup>(1)</sup>   | RC2 <sup>(2)</sup>   | RC1 <sup>(1)</sup>    | _     | XXXX          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  |        | _      | _     | _     | _     | _     | _     | LATC4 <sup>(2)</sup> | LATC3 <sup>(1)</sup> | LATC2 <sup>(2)</sup> | LATC1 <sup>(1)</sup>  | _     | XXXX          |

| ODCC      | 06CC | ODC15   | ODC14   | ODC13   | ODC12   |        | _      | _     | _     | _     | _     | _     | ODC4 <sup>(2)</sup>  | ODC3 <sup>(1)</sup>  | ODC2 <sup>(2)</sup>  | ODC1 <sup>(1)</sup>   | _     | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 100-pin devices.

Note 1: Implemented in 80-pin and 100-pin devices only.

2: Implemented in 100-pin devices only

#### TABLE 4-19: PORTD REGISTER MAP

| File Name | Addr | Bit 15                 | Bit 14                | Bit 13                | Bit 12                | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|------------------------|-----------------------|-----------------------|-----------------------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 <sup>(1)</sup> | TRISD14(1)            | TRISD13(1)            | TRISD12(1)            | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15 <sup>(1)</sup>    | RD14 <sup>(1)</sup>   | RD13 <sup>(1)</sup>   | RD12 <sup>(1)</sup>   | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15 <sup>(1)</sup>  | LATD14 <sup>(1)</sup> | LATD13 <sup>(1)</sup> | LATD12 <sup>(1)</sup> | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODD15 <sup>(1)</sup>   | ODD14 <sup>(1)</sup>  | ODD13 <sup>(1)</sup>  | ODD12 <sup>(1)</sup>  | ODD11   | ODD10   | ODD9   | ODD8   | ODD7   | ODD6   | ODD5   | ODD4   | ODD3   | ODD2   | ODD1   | ODD0   | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 100-pin devices.

**Note 1:** Implemented in 80-pin and 100-pin devices only.

#### TABLE 4-27: CRC REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                                                                                                                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|-------------|--------------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CRCCON    | 0640 | _      | _                                                                                                                                   | CSIDL  | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0      | CRCFUL       | CRCMPT | _     | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXOR    | 0642 |        | - <u>CSIDL</u> VWORD4 VWORD3 VWORD2 VWORD1 VWORD0 CRCFUL CRCMPT <u>CRCGO</u> PLEN3 PLEN2 PLEN1 PLEN0<br>CRC XOR Polynomial Register |        |        |        |        |        |             |              |        |       |       |       |       |       |       | 0000          |

| CRCDAT    | 0644 |        |                                                                                                                                     |        |        |        |        | (      | CRC Data Ir | nput Registe | r      |       |       |       |       |       |       | 0000          |

| CRCWDAT   | 0646 |        |                                                                                                                                     |        |        |        |        |        | CRC Resu    | ılt Register |        |       |       |       |       |       |       | 0000          |

|           |      |        |                                                                                                                                     |        |        |        |        |        |             |              |        |       |       |       |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-28: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|-------|-------|--------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _      |        | —      | _      | CM     | VREGS  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP | IDLE  | BOR    | POR   | <sub>xxxx</sub> (1) |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | —      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF    |       | SOSCEN | OSWEN | xxxx(2)             |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _     | _     | _      | _     | 0100                |

| OSCTUN    | 0748 | _      | —      | _      | _      | —      | _      | _      | _      | —       | _     |        |       | TUN   | <5:0> |        |       | 0000                |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-29:NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  |        | —      | _      |       | _     |       | ERASE | _     |       | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | _      |        | —      | -      | _      |        | -     | _     |       |       |       | NVMKE | Y<7:0> |        |        |        | 0000            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

### TABLE 4-30: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|--------|-------|--------|--------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _      |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _     | _      | ADC1MD | 0000          |

| PMD2      | 0772 | _      | —      | _      | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | _      | _     | _     | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD  | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | —      | CMPMD  | RTCCMD | PMPMD | CRCPMD | —     | _     | —      | —      | _     | I2C2MD | _      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

PIC24FJ128GA010 FAMILY

| U-0          | R/W-1                                                                                                                     | R/W-0                                           | R/W-0            | U-0              | R/W-1            | R/W-0            | R/W-0            |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------|------------------|------------------|------------------|------------------|--|--|--|--|

|              | T1IP2                                                                                                                     | T1IP1                                           | T1IP0            | _                | OC1IP2           | OC1IP1           | OC1IP0           |  |  |  |  |

| bit 15       | ·                                                                                                                         | •                                               | ·                |                  |                  |                  | bit              |  |  |  |  |

|              |                                                                                                                           | DAMO                                            |                  |                  |                  | DAALO            |                  |  |  |  |  |

| U-0          | R/W-1<br>IC1IP2                                                                                                           | R/W-0<br>IC1IP1                                 | R/W-0<br>IC1IP0  | U-0              | R/W-1<br>INT0IP2 | R/W-0<br>INT0IP1 | R/W-0<br>INT0IP0 |  |  |  |  |

| <br>bit 7    | ICTIFZ                                                                                                                    | ICTIFT                                          | ICTIFU           | —                | INTUFZ           | INTUFT           | bit              |  |  |  |  |

|              |                                                                                                                           |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

| Legend:      |                                                                                                                           |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

| R = Readab   |                                                                                                                           | W = Writable                                    |                  | -                | mented bit, read | l as '0'         |                  |  |  |  |  |

| -n = Value a | t POR                                                                                                                     | '1' = Bit is se                                 | t                | '0' = Bit is cle | eared            | x = Bit is unkr  | nown             |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                 | ented: Read as                                  | ·0'              |                  |                  |                  |                  |  |  |  |  |

| bit 14-12    | -                                                                                                                         | Timer1 Interrup                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              |                                                                                                                           | upt is Priority 7                               |                  | y interrupt)     |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                                                                             |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | 000 = Interr                                                                                                              | upt source is dis                               | sabled           |                  |                  |                  |                  |  |  |  |  |

| bit 11       | Unimpleme                                                                                                                 | ented: Read as                                  | 0'               |                  |                  |                  |                  |  |  |  |  |

| bit 10-8     | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits                                                              |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                       |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

| bit 7        |                                                                                                                           | upt source is dis<br>ented: Read as '           |                  |                  |                  |                  |                  |  |  |  |  |

|              | -                                                                                                                         |                                                 |                  | rrupt Drigrity h | vito             |                  |                  |  |  |  |  |

| bit 6-4      | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                                                                                        |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              |                                                                                                                           | upt is Priority 1                               | sabled           |                  |                  |                  |                  |  |  |  |  |

| bit 3        |                                                                                                                           | nted: Read as                                   |                  |                  |                  |                  |                  |  |  |  |  |

| bit 2-0      | INT0IP<2:0                                                                                                                | INTOIP<2:0:> External Interrupt 0 Priority bits |                  |                  |                  |                  |                  |  |  |  |  |

|              | 111 = Interr                                                                                                              | upt is Priority 7                               | (highest priorit | ty interrupt)    |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                         |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              |                                                                                                                           |                                                 |                  |                  |                  |                  |                  |  |  |  |  |

|              | 001 = Interr                                                                                                              | upt is priority 1                               |                  |                  |                  |                  |                  |  |  |  |  |

# REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0          | R/W-1                                                      | R/W-0                                                                                     | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|--------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| _            | U1RXIP2                                                    | U1RXIP1                                                                                   | U1RXIP0          | —                | SPI1IP2          | SPI1IP1         | SPI1IP0 |  |  |  |  |  |

| bit 15       |                                                            |                                                                                           |                  |                  |                  |                 | bit     |  |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                                                                     | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|              | SPF1IP2                                                    | SPF1IP1                                                                                   | SPF1IP0          |                  | T3IP2            | T3IP1           | T3IP0   |  |  |  |  |  |

| bit 7        |                                                            |                                                                                           |                  |                  | 1011 2           | 1011 1          | bit     |  |  |  |  |  |

|              |                                                            |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

| Legend:      | 1- 1-14                                                    |                                                                                           | L-:4             |                  |                  | d = = (0)       |         |  |  |  |  |  |

| R = Readab   |                                                            | W = Writable                                                                              |                  | -                | emented bit, rea |                 |         |  |  |  |  |  |

| -n = Value a | IL POR                                                     | '1' = Bit is set                                                                          |                  | '0' = Bit is cle | eareu            | x = Bit is unkr | IOWII   |  |  |  |  |  |

| bit 15       | Unimplemen                                                 | ted: Read as '                                                                            | 0'               |                  |                  |                 |         |  |  |  |  |  |

| bit 14-12    | -                                                          | -: UART1 Rece                                                                             |                  | Priority bits    |                  |                 |         |  |  |  |  |  |

|              | 111 = Interru                                              | pt is Priority 7 (                                                                        | (highest priorit | y interrupt)     |                  |                 |         |  |  |  |  |  |

|              | •                                                          | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>•</li> </ul> |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                         |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              |                                                            | pt source is dis                                                                          | sabled           |                  |                  |                 |         |  |  |  |  |  |

| bit 11       | Unimplemen                                                 | ted: Read as '                                                                            | 0'               |                  |                  |                 |         |  |  |  |  |  |

| bit 10-8     | SPI1IP<2:0>: SPI1 Event Interrupt Priority bits            |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                              |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              |                                                            | pt source is dis                                                                          | abled            |                  |                  |                 |         |  |  |  |  |  |

| bit 7        | Unimplemen                                                 | ted: Read as '                                                                            | 0'               |                  |                  |                 |         |  |  |  |  |  |

| bit 6-4      | SPF1IP<2:0>                                                | SPF1IP<2:0>: SPI1 Fault Interrupt Priority bits                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                         |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              |                                                            | pt source is dis                                                                          | abled            |                  |                  |                 |         |  |  |  |  |  |

| bit 3        | Unimplemen                                                 | ted: Read as '                                                                            | 0'               |                  |                  |                 |         |  |  |  |  |  |

| bit 2-0      | T3IP<2:0>: ⊺                                               | imer3 Interrupt                                                                           | Priority bits    |                  |                  |                 |         |  |  |  |  |  |

|              | 111 = Interru                                              | pt is Priority 7 (                                                                        | (highest priorit | y interrupt)     |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                                                           |                  |                  |                  |                 |         |  |  |  |  |  |

|              | •<br>001 = Interru                                         | pt is Prioritv 1                                                                          |                  |                  |                  |                 |         |  |  |  |  |  |

# REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

### REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0                                                                                                                               | U-0            | U-0              | U-0            | U-0                                | U-0            | U-0                | U-0            |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------|------------------------------------|----------------|--------------------|----------------|--|

| —                                                                                                                                 | —              | —                | —              | —                                  | —              | _                  | —              |  |

| bit 15                                                                                                                            |                |                  |                |                                    |                |                    | bit 8          |  |

|                                                                                                                                   | <b>D</b> 444 4 | <b>D</b> 444 0   | <b>D</b> 444 A |                                    | <b>D</b> 444 4 | <b>D</b> 444 0     | <b>D</b> 444 0 |  |

| U-0                                                                                                                               | R/W-1          | R/W-0            | R/W-0          | U-0                                | R/W-1          | R/W-0              | R/W-0          |  |

| —                                                                                                                                 | AD1IP2         | AD1IP1           | AD1IP0         | —                                  | U1TXIP2        | U1TXIP1            | U1TXIP0        |  |

| bit 7                                                                                                                             |                |                  |                |                                    |                |                    | bit 0          |  |

| Legend:                                                                                                                           |                |                  |                |                                    |                |                    |                |  |

| R = Readabl                                                                                                                       | e bit          | W = Writable     | bit            | U = Unimplemented bit, read as '0' |                |                    |                |  |

| -n = Value at POR                                                                                                                 |                | '1' = Bit is set |                | '0' = Bit is cleared               |                | x = Bit is unknown |                |  |

| bit 15-7                                                                                                                          | Unimplemer     | ted: Read as '   | 0'             |                                    |                |                    |                |  |

| bit 6-4 AD1IP<2:0>: A/D Conversion Complete Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                |                  |                |                                    |                |                    |                |  |

|         | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|---------|------------------------------------------------------------|

|         | •                                                          |

|         | •                                                          |

|         | •                                                          |

|         | 001 = Interrupt is Priority 1                              |

|         | 000 = Interrupt source is disabled                         |

| bit 3   | Unimplemented: Read as '0'                                 |

| bit 2-0 | U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits     |

|         | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|         | •                                                          |

|         |                                                            |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

# 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

#### To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- 2. Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx Control register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPC registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx Status register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx Control register.

#### 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Level 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

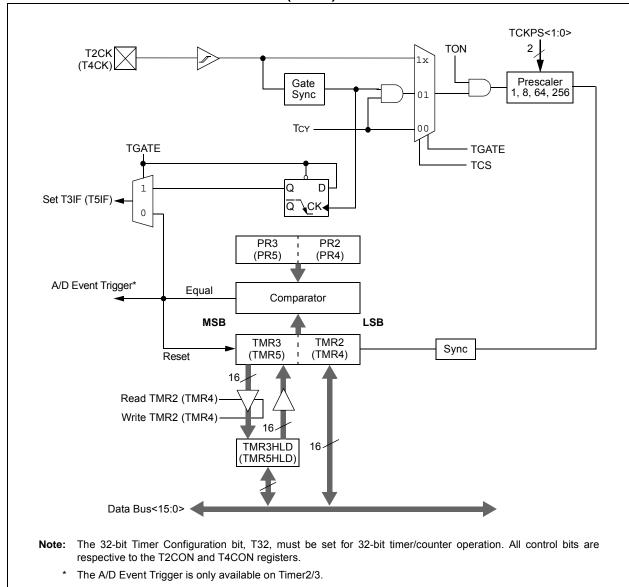

# FIGURE 12-1: TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

# EQUATION 21-1: A/D CONVERSION CLOCK PERIOD<sup>(1)</sup>

TAD = TCY(ADCS + 1) $ADCS = \frac{TAD}{TCY} - 1$

**Note 1:** Based on TCY = TOSC \* 2; Doze mode and PLL are disabled.

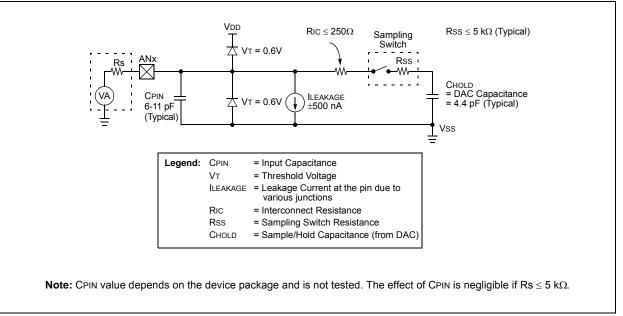

# FIGURE 21-2: 10-BIT A/D CONVERTER ANALOG INPUT MODEL

# REGISTER 22-1: CMCON: COMPARATOR CONTROL REGISTER (CONTINUED)

| bit 5 | <b>C2INV:</b> Comparator 2 Output Inversion bit<br>1 = C2 output is inverted      |

|-------|-----------------------------------------------------------------------------------|

|       | 0 = C2 output is not inverted                                                     |

| bit 4 | C1INV: Comparator 1 Output Inversion bit                                          |

|       | <ul><li>1 = C1 output is inverted</li><li>0 = C1 output is not inverted</li></ul> |

| bit 3 | C2NEG: Comparator 2 Negative Input Configure bit                                  |

|       | 1 = C2IN+ is connected to VIN-                                                    |

|       | 0 = C2IN- is connected to VIN-                                                    |

|       | See Figure 22-1 for the Comparator modes.                                         |

| bit 2 | C2POS: Comparator 2 Positive Input Configure bit                                  |

|       | 1 = C2IN+ is connected to VIN+                                                    |

|       | 0 = CVREF is connected to VIN+                                                    |

|       | See Figure 22-1 for the Comparator modes.                                         |

| bit 1 | C1NEG: Comparator 1 Negative Input Configure bit                                  |

|       | 1 = C1IN+ is connected to VIN-                                                    |

|       | 0 = C1IN- is connected to VIN-                                                    |

|       | See Figure 22-1 for the Comparator modes.                                         |

| bit 0 | C1POS: Comparator 1 Positive Input Configure bit                                  |

|       | 1 = C1IN is connected to VIN+                                                     |

|       | 0 = CVREF is connected to VIN+                                                    |

|       | See Figure 22-1 for the Comparator modes.                                         |

# REGISTER 23-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0        | U-0                                                                                                                                                                                                                                   | U-0                                                                                                                                                             | U-0                                                   | U-0               | U-0             | U-0             | U-0   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|-----------------|-----------------|-------|

| _          | —                                                                                                                                                                                                                                     | _                                                                                                                                                               | _                                                     | _                 | —               | —               | —     |

| bit 15     |                                                                                                                                                                                                                                       |                                                                                                                                                                 |                                                       |                   |                 |                 | bit   |

|            | 5444                                                                                                                                                                                                                                  | <b>D</b> 444 A                                                                                                                                                  |                                                       | <b>D</b> 444 A    |                 |                 |       |

| R/W-0      | R/W-0                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                           | R/W-0                                                 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| CVREN      | CVROE                                                                                                                                                                                                                                 | CVRR                                                                                                                                                            | CVRSS                                                 | CVR3              | CVR2            | CVR1            | CVR0  |

| bit 7      |                                                                                                                                                                                                                                       |                                                                                                                                                                 |                                                       |                   |                 |                 | bit   |

| Legend:    |                                                                                                                                                                                                                                       |                                                                                                                                                                 |                                                       |                   |                 |                 |       |

| R = Reada  | ble bit                                                                                                                                                                                                                               | W = Writable b                                                                                                                                                  | bit                                                   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value | at POR                                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                |                                                       | '0' = Bit is clea | ared            | x = Bit is unkn | iown  |

| bit 6      | 0 = CVREF cir<br>CVROE: Com<br>1 = CVREF vo                                                                                                                                                                                           | rcuit is powered<br>rcuit is powered<br>nparator VREF O<br>oltage level is ou<br>oltage level is di                                                             | down<br>utput Enable I<br>itput on the C <sup>v</sup> | VREF pin          | bin             |                 |       |

| bit 5      | 1 = 0 to 0.62                                                                                                                                                                                                                         | arator VREF Rai<br>5 CVRSRC, with<br>SRC to 0.72 CV                                                                                                             | CVRSRC/24 s                                           | tep size          | ze              |                 |       |

| bit 4      | 1 = Compara                                                                                                                                                                                                                           | CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source: CVRSRC = VREF+ – VREF-<br>0 = Comparator reference source: CVRSRC = AVDD – AVSS |                                                       |                   |                 |                 |       |

| bit 3-0    | $CVR<3:0>: Comparator VREF Value Selection 0 \le CVR<3:0> \le 15 \text{ bits}$ $\frac{When CVRR = 1:}{CVREF = (CVR<3:0>/24) \bullet (CVRSRC)}$ $\frac{When CVRR = 0:}{CVREF = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)}$ |                                                                                                                                                                 |                                                       |                   |                 |                 |       |

# 27.1 DC Characteristics

### TABLE 27-1: OPERATING MIPS vs. VOLTAGE

| VDD Range  | Temp Range     | Max MIPS               |

|------------|----------------|------------------------|

| (in Volts) | (in °C)        | PIC24FJ128GA010 Family |

| 2.0-3.6V   | -40°C to +85°C | 16                     |

### TABLE 27-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol              | Min           | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------|-----|------|------|

| PIC24FJ128GA010 Family:                                                                                                                                                                 |                     |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                    | TJ                  | -40           | _   | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA                  | -40           | —   | +85  | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD                  | Pint + Pi/o W |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                       | Ромах (Тj – Та)/θја |               |     | W    |      |

### TABLE 27-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                              | Symbol | Тур  | Max | Unit | Notes    |

|---------------------------------------------|--------|------|-----|------|----------|

| Package Thermal Resistance, 14x14x1 mm TQFP | θJA    | 50   | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 12x12x1 mm TQFP | θJA    | 69.4 | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 10x10x1 mm TQFP | θJA    | 76.6 | _   | °C/W | (Note 1) |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 27-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

|              |            |                                                                         |         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                   |  |

|--------------|------------|-------------------------------------------------------------------------|---------|------------------------------------------------------|------|-------|-----------------------------------|--|

| Param<br>No. | Sym        | Characteristic                                                          | Min     | Typ <sup>(1)</sup>                                   | Max  | Units | Conditions                        |  |

| Operat       | ing Voltag | e                                                                       |         |                                                      |      |       |                                   |  |

| DC10         | Supply V   | oltage                                                                  |         |                                                      |      |       |                                   |  |

|              | Vdd        |                                                                         | VBOR    | _                                                    | 3.6  | V     | Regulator is enabled              |  |

|              | Vdd        |                                                                         | VDDCORE | —                                                    | 3.6  | V     | Regulator is disabled             |  |

|              | VDDCORE    |                                                                         | 2.0     | —                                                    | 2.75 | V     | Regulator is disabled             |  |

| DC12         | Vdr        | RAM Data Retention<br>Voltage <sup>(2)</sup>                            | 1.5     | —                                                    | -    | V     |                                   |  |

| DC16         | VPOR       | <b>VDD Start Voltage</b><br>to Ensure Internal<br>Power-on Reset Signal | _       | _                                                    | Vss  | V     |                                   |  |

| DC17         | SVDD       | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal     | 0.05    | _                                                    | _    | V/ms  | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |  |

| DC18         | VBOR       | Brown-out Reset<br>Voltage <sup>(3)</sup>                               | 1.9     | 2.2                                                  | 2.5  | V     | Regulator must be enabled         |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** This is the limit to which VDD can be lowered without losing RAM data.

3: Device will operate normally until Brown-out reset occurs even though VDD may be below VDDMIN.

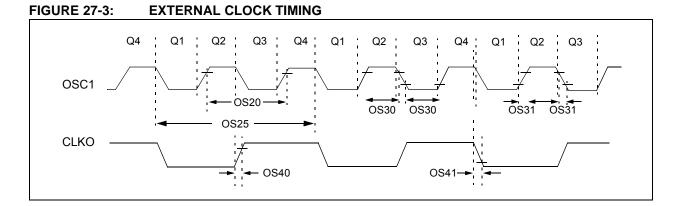

# TABLE 27-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |                     |                          |                                          |

|--------------------|---------------|-------------------------------------------------------------------------|------------------------------------------------------|--------------------|---------------------|--------------------------|------------------------------------------|

| Param<br>No.       | Sym           | Characteristic                                                          | Min                                                  | Typ <sup>(1)</sup> | Мах                 | Units                    | Conditions                               |

| OS10               | Fosc          | External CLKI Frequency<br>(external clocks allowed<br>only in EC mode) | DC<br>3                                              |                    | 32<br>8             | MHz<br>MHz               | EC mode<br>ECPLL mode                    |

|                    |               | Oscillator Frequency                                                    | 3.5<br>3.5<br>10<br>31                               |                    | 10<br>8<br>32<br>33 | MHz<br>MHz<br>MHz<br>kHz | XT mode<br>XTPLL mode<br>HS mode<br>SOSC |

| OS20               | Tosc          | Tosc = 1/Fosc                                                           | —                                                    | —                  | —                   | —                        | See Parameter OS10<br>for Fosc value     |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                   | 62.5                                                 | _                  | DC                  | ns                       |                                          |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                            | 0.45 x Tosc                                          | —                  | —                   | ns                       | EC mode                                  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                           | —                                                    | —                  | 20                  | ns                       | EC mode                                  |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                           | —                                                    | 6                  | 10                  | ns                       |                                          |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                           | —                                                    | 6                  | 10                  | ns                       |                                          |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

**3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

# 28.0 PACKAGING INFORMATION

# 28.1 Package Marking Information

64-Lead TQFP (10x10x1 mm)

80-Lead TQFP (12x12x1 mm)

100-Lead TQFP (12x12x1 mm)

100-Lead TQFP (14x14x1 mm)

Example

### Example

### Example

| Legend: | XXX                                                                               | Customer-specific information                                                                       |  |  |  |  |

|---------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

|         | Y                                                                                 | Year code (last digit of calendar year)                                                             |  |  |  |  |

|         | ΥY                                                                                | Year code (last 2 digits of calendar year)                                                          |  |  |  |  |

|         | WW                                                                                | Week code (week of January 1 is week '01')                                                          |  |  |  |  |

|         | NNN                                                                               | Alphanumeric traceability code                                                                      |  |  |  |  |

|         |                                                                                   | Pb-free JEDEC designator for Matte Tin (Sn)                                                         |  |  |  |  |

|         | *                                                                                 | This package is Pb-free. The Pb-free JEDEC designator (e3)                                          |  |  |  |  |

|         |                                                                                   | can be found on the outer packaging for this package.                                               |  |  |  |  |

| Note:   | In the event the full Microchip part number cannot be marked on one line, it will |                                                                                                     |  |  |  |  |

|         |                                                                                   | d over to the next line, thus limiting the number of available s for customer-specific information. |  |  |  |  |

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |        | MILLIMETERS |          |      |

|------------------------|--------|-------------|----------|------|

| Dimension              | Limits | MIN         | NOM      | MAX  |

| Number of Pins         | Ν      |             | 64       |      |

| Pitch                  | е      | 0.50 BSC    |          |      |

| Overall Height         | А      | 0.80        | 0.90     | 1.00 |

| Standoff               | A1     | 0.00        | 0.02     | 0.05 |

| Contact Thickness      | A3     | 0.20 REF    |          |      |

| Overall Width          | Е      |             | 9.00 BSC |      |

| Exposed Pad Width      | E2     | 5.30        | 5.40     | 5.50 |

| Overall Length         | D      | 9.00 BSC    |          |      |

| Exposed Pad Length     | D2     | 5.30        | 5.40     | 5.50 |

| Contact Width          | b      | 0.20        | 0.25     | 0.30 |

| Contact Length         | L      | 0.30        | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K      | 0.20        | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2

NOTES:

# READER RESPONSE