Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga006-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

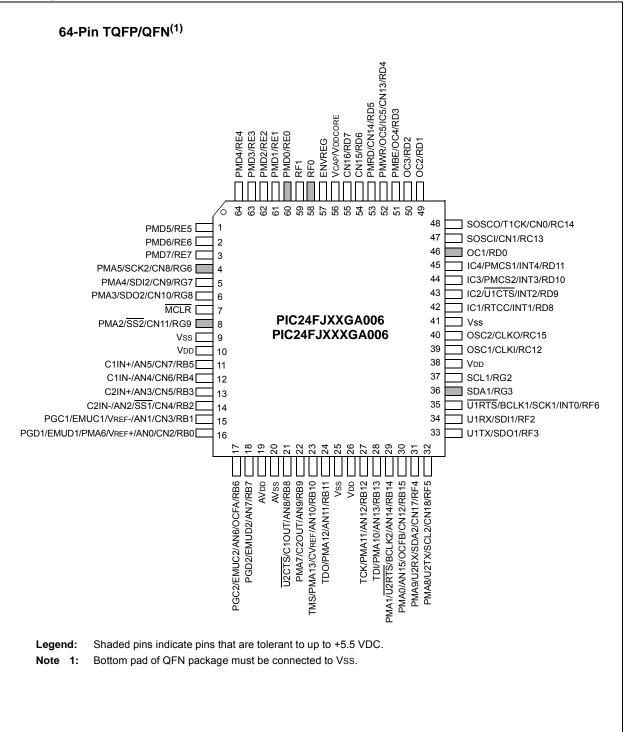

#### **Pin Diagrams**

| Function |        | Pin Number |         |     | Input            | Description                                    |  |

|----------|--------|------------|---------|-----|------------------|------------------------------------------------|--|

| Function | 64-Pin | 80-Pin     | 100-Pin | I/O | Buffer           | Description                                    |  |

| RG0      |        | 75         | 90      | I/O | ST               | PORTG Digital I/O.                             |  |

| RG1      | _      | 74         | 89      | I/O | ST               |                                                |  |

| RG2      | 37     | 47         | 57      | I/O | ST               |                                                |  |

| RG3      | 36     | 46         | 56      | I/O | ST               |                                                |  |

| RG6      | 4      | 6          | 10      | I/O | ST               |                                                |  |

| RG7      | 5      | 7          | 11      | I/O | ST               |                                                |  |

| RG8      | 6      | 8          | 12      | I/O | ST               |                                                |  |

| RG9      | 8      | 10         | 14      | I/O | ST               |                                                |  |

| RG12     | _      | —          | 96      | I/O | ST               |                                                |  |

| RG13     | _      | —          | 97      | I/O | ST               |                                                |  |

| RG14     | _      | —          | 95      | I/O | ST               |                                                |  |

| RG15     | _      | —          | 1       | I/O | ST               |                                                |  |

| RTCC     | 42     | 54         | 68      | 0   | _                | Real-Time Clock Alarm Output.                  |  |

| SCK1     | 35     | 45         | 55      | 0   | _                | SPI1 Serial Clock Output.                      |  |

| SCK2     | 4      | 6          | 10      | I/O | ST               | SPI2 Serial Clock Output.                      |  |

| SCL1     | 37     | 47         | 57      | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output.    |  |

| SCL2     | 32     | 52         | 58      | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output.    |  |

| SDA1     | 36     | 46         | 56      | I/O | l <sup>2</sup> C | I2C1 Data Input/Output.                        |  |

| SDA2     | 31     | 53         | 59      | I/O | l <sup>2</sup> C | I2C2 Data Input/Output.                        |  |

| SDI1     | 34     | 44         | 54      | I   | ST               | SPI1 Serial Data Input.                        |  |

| SDI2     | 5      | 7          | 11      | I   | ST               | SPI2 Serial Data Input.                        |  |

| SDO1     | 33     | 43         | 53      | 0   | _                | SPI1 Serial Data Output.                       |  |

| SDO2     | 6      | 8          | 12      | 0   | _                | SPI2 Serial Data Output.                       |  |

| SOSCI    | 47     | 59         | 73      | I   | ANA              | Secondary Oscillator/Timer1 Clock Input.       |  |

| SOSCO    | 48     | 60         | 74      | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.      |  |

| SS1      | 14     | 18         | 23      | I/O | ST               | Slave Select Input/Frame Select Output (SPI1). |  |

| SS2      | 8      | 10         | 14      | I/O | ST               | Slave Select Input/Frame Select Output (SPI2). |  |

| T1CK     | 48     | 60         | 74      | I   | ST               | Timer1 Clock.                                  |  |

| T2CK     |        | 4          | 6       | I   | ST               | Timer2 External Clock Input.                   |  |

| T3CK     |        | _          | 7       | I   | ST               | Timer3 External Clock Input.                   |  |

| T4CK     | _      | 5          | 8       | I   | ST               | Timer4 External Clock Input.                   |  |

| T5CK     | _      | —          | 9       | I   | ST               | Timer5 External Clock Input.                   |  |

| TCK      | 27     | 33         | 38      | I   | ST               | JTAG Test Clock/Programming Clock Input.       |  |

| TDI      | 28     | 34         | 60      | I   | ST               | JTAG Test Data/Programming Data Input.         |  |

| TDO      | 24     | 14         | 61      | 0   | —                | JTAG Test Data Output.                         |  |

| TMS      | 23     | 13         | 17      | I   | ST               | JTAG Test Mode Select Input.                   |  |

#### TABLE 1-2: PIC24FJ128GA010 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer, ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $l^2C^{TM} = l^2C/SMB$ us input buffer

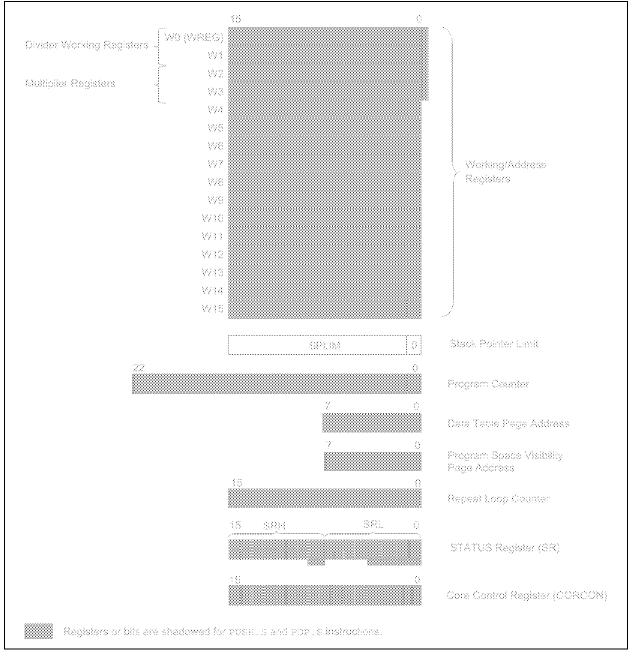

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

# 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused addresses should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is not recommended.

All of the table write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 JTAG Operation

The PIC24F family supports JTAG programming and boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity. Programming can be performed with industry standard JTAG programmers supporting Serial Vector Format (SVF).

### 5.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an onboard bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. See the device programming specification for more information on Enhanced ICSP

### 5.5 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.6 "Programming Operations"** for further details.

# 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or an erase operation, the processor stalls (Waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

Configuration Word values are stored in the last two locations of program memory. Performing a page erase operation on the last page of program memory clears these values and enables code protection. As a result, avoid performing page erase operations on the last page of program memory.

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has NOT expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, will automatically be inserted after the POR and PWRT delay times. The FSCM will not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 100  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay will prevent an oscillator failure trap at a device Reset when the PWRT is disabled.

### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Device Configuration register (see Table 6-2). The RCFGCAL and NVMCON registers are only affected by a POR.

| U-0           | U-0                                | R/W-0                                                                                                  | R/W-0       | R/W-0             | R/W-0            | R/W-0           | R/W-0         |  |  |  |  |

|---------------|------------------------------------|--------------------------------------------------------------------------------------------------------|-------------|-------------------|------------------|-----------------|---------------|--|--|--|--|

| _             | _                                  | AD1IF                                                                                                  | U1TXIF      | U1RXIF            | SPI1IF           | SPF1IF          | T3IF          |  |  |  |  |

| bit 15        | •                                  |                                                                                                        |             |                   |                  |                 | bit           |  |  |  |  |

| DAMA          | DAMO                               | DAMA                                                                                                   |             | DAMA              | DAMA             | DAALO           | DAMA          |  |  |  |  |

| R/W-0         | R/W-0                              | R/W-0                                                                                                  | U-0         | R/W-0             | R/W-0            | R/W-0           | R/W-0         |  |  |  |  |

| T2IF<br>bit 7 | OC2IF                              | IC2IF                                                                                                  | —           | T1IF              | OC1IF            | IC1IF           | INT0IF<br>bit |  |  |  |  |

| Legend:       |                                    |                                                                                                        |             |                   |                  |                 |               |  |  |  |  |

| R = Readabl   | e bit                              | W = Writable                                                                                           | e bit       | U = Unimplen      | nented bit, read | l as '0'        |               |  |  |  |  |

| -n = Value at | POR                                | '1' = Bit is se                                                                                        | t           | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |  |  |  |  |

| bit 15-14     | Unimpleme                          | nted: Read as                                                                                          | 'O'         |                   |                  |                 |               |  |  |  |  |

| bit 13        | -                                  |                                                                                                        |             | ot Flag Status b  | it               |                 |               |  |  |  |  |

|               |                                    | request has or                                                                                         |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | request has no                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| bit 12        |                                    | RT1 Transmitte                                                                                         |             | g Status bit      |                  |                 |               |  |  |  |  |

|               |                                    | request has or                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| hit 11        | •                                  | request has no                                                                                         |             | Natua hit         |                  |                 |               |  |  |  |  |

| bit 11        |                                    | <b>U1RXIF:</b> UART1 Receiver Interrupt Flag Status bit<br>1 = Interrupt request has occurred          |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | request has no                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| bit 10        | SPI1IF: SPI                        | SPI1IF: SPI1 Event Interrupt Flag Status bit                                                           |             |                   |                  |                 |               |  |  |  |  |

|               | 1 = Interrupt request has occurred |                                                                                                        |             |                   |                  |                 |               |  |  |  |  |

|               | -                                  | 0 = Interrupt request has not occurred                                                                 |             |                   |                  |                 |               |  |  |  |  |

| bit 9         |                                    | SPF1IF: SPI1 Fault Interrupt Flag Status bit                                                           |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |             |                   |                  |                 |               |  |  |  |  |

| bit 8         | •                                  | 3 Interrupt Flag                                                                                       |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | request has or                                                                                         |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | request has no                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| bit 7         |                                    | 2 Interrupt Flag                                                                                       |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | = Interrupt request has occurred<br>= Interrupt request has not occurred                               |             |                   |                  |                 |               |  |  |  |  |

|               | •                                  | •                                                                                                      |             |                   | h:+              |                 |               |  |  |  |  |

| bit 6         | -                                  | request has or                                                                                         |             | upt Flag Status   | DIL              |                 |               |  |  |  |  |

|               |                                    | request has no                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| bit 5         |                                    | Capture Chanr                                                                                          |             | lag Status bit    |                  |                 |               |  |  |  |  |

|               |                                    | request has o                                                                                          |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | request has no                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| bit 4         | -                                  | nted: Read as                                                                                          |             |                   |                  |                 |               |  |  |  |  |

| bit 3         |                                    | I Interrupt Flag                                                                                       |             |                   |                  |                 |               |  |  |  |  |

|               |                                    | request has of                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| bit 2         |                                    | •                                                                                                      |             | upt Flag Status   | bit              |                 |               |  |  |  |  |

|               | -                                  | request has o                                                                                          |             | -p                |                  |                 |               |  |  |  |  |

|               | 0 = Interrupt                      | request has no                                                                                         | ot occurred |                   |                  |                 |               |  |  |  |  |

| bit 1         |                                    | Capture Chanr                                                                                          |             | lag Status bit    |                  |                 |               |  |  |  |  |

|               |                                    | request has or                                                                                         |             |                   |                  |                 |               |  |  |  |  |

| hit 0         | •                                  | request has no                                                                                         |             | +                 |                  |                 |               |  |  |  |  |

| bit 0         |                                    | ernal Interrupt C<br>request has or                                                                    | -           | ι                 |                  |                 |               |  |  |  |  |

|               |                                    |                                                                                                        |             |                   |                  |                 |               |  |  |  |  |

#### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

|                           | U-0                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                | U-0                                                                                                                   | U-0                              | U-0           | R/W-0           | U-0    |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------|-----------------|--------|--|--|--|

| _                         | _                                                                                                                                                                                                                                           | PMPIE                                                                                                                                                                                                |                                                                                                                       | —                                | —             | OC5IE           |        |  |  |  |

| bit 15                    |                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                       |                                  |               |                 | bit 8  |  |  |  |

|                           |                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                       |                                  |               |                 |        |  |  |  |

| R/W-0                     | R/W-0                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                | U-0                                                                                                                   | U-0                              | U-0           | R/W-0           | R/W-0  |  |  |  |

| IC5IE                     | IC4IE                                                                                                                                                                                                                                       | IC3IE                                                                                                                                                                                                | —                                                                                                                     | —                                | —             | SPI2IE          | SPF2IE |  |  |  |

| bit 7                     |                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                       |                                  |               |                 | bit    |  |  |  |

| Legend:                   |                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                       |                                  |               |                 |        |  |  |  |

| R = Readabl               | e hit                                                                                                                                                                                                                                       | W = Writable I                                                                                                                                                                                       | nit                                                                                                                   | U = Unimpler                     | nented hit re | o, se pe        |        |  |  |  |

| -n = Value at             |                                                                                                                                                                                                                                             | '1' = Bit is set                                                                                                                                                                                     | JIL                                                                                                                   | '0' = Bit is cle                 |               | x = Bit is unkr | nwn    |  |  |  |

|                           |                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                       |                                  | aleu          |                 |        |  |  |  |

| bit 15-14                 | Unimpleme                                                                                                                                                                                                                                   | nted: Read as 'd                                                                                                                                                                                     | )'                                                                                                                    |                                  |               |                 |        |  |  |  |

| bit 13                    | -                                                                                                                                                                                                                                           | allel Master Port                                                                                                                                                                                    |                                                                                                                       | able bit                         |               |                 |        |  |  |  |

|                           |                                                                                                                                                                                                                                             | request is enab                                                                                                                                                                                      |                                                                                                                       |                                  |               |                 |        |  |  |  |

|                           |                                                                                                                                                                                                                                             | request is not e                                                                                                                                                                                     |                                                                                                                       |                                  |               |                 |        |  |  |  |

| bit 12-10                 | Unimpleme                                                                                                                                                                                                                                   | nted: Read as 'o                                                                                                                                                                                     | )'                                                                                                                    |                                  |               |                 |        |  |  |  |

| bit 9                     |                                                                                                                                                                                                                                             | out Compare Ch                                                                                                                                                                                       |                                                                                                                       | rupt Enable bit                  |               |                 |        |  |  |  |

|                           |                                                                                                                                                                                                                                             | request is enab<br>request is not e                                                                                                                                                                  |                                                                                                                       |                                  |               |                 |        |  |  |  |

| bit 8                     | •                                                                                                                                                                                                                                           | nted: Read as '0                                                                                                                                                                                     |                                                                                                                       |                                  |               |                 |        |  |  |  |

| bit 7                     | IC5IE: Input                                                                                                                                                                                                                                | Capture Channe                                                                                                                                                                                       | el 5 Interrupt                                                                                                        | Enable bit                       |               |                 |        |  |  |  |

|                           |                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |                                                                                                                       | 1 = Interrupt request is enabled |               |                 |        |  |  |  |

|                           | 0 = Interrupt request is not enabled                                                                                                                                                                                                        |                                                                                                                                                                                                      |                                                                                                                       |                                  |               |                 |        |  |  |  |

|                           | IC4IE: Input Capture Channel 4 Interrupt Enable bit                                                                                                                                                                                         |                                                                                                                                                                                                      |                                                                                                                       |                                  |               |                 |        |  |  |  |

| bit 6                     | IC4IE: Input                                                                                                                                                                                                                                | •                                                                                                                                                                                                    |                                                                                                                       | Enable bit                       |               |                 |        |  |  |  |

| bit 6                     | 1 = Interrupt                                                                                                                                                                                                                               | Capture Channe<br>request is enab                                                                                                                                                                    | el 4 Interrupt<br>led                                                                                                 | Enable bit                       |               |                 |        |  |  |  |

|                           | 1 = Interrupt<br>0 = Interrupt                                                                                                                                                                                                              | Capture Channe<br>request is enab<br>request is not e                                                                                                                                                | el 4 Interrupt<br>led<br>nabled                                                                                       |                                  |               |                 |        |  |  |  |

| bit 6<br>bit 5            | 1 = Interrupt<br>0 = Interrupt<br>IC3IE: Input                                                                                                                                                                                              | Capture Channe<br>request is enab<br>request is not e<br>Capture Channe                                                                                                                              | el 4 Interrupt<br>led<br>nabled<br>el 3 Interrupt                                                                     |                                  |               |                 |        |  |  |  |

|                           | 1 = Interrupt<br>0 = Interrupt<br>IC3IE: Input<br>1 = Interrupt                                                                                                                                                                             | Capture Channe<br>request is enab<br>request is not e                                                                                                                                                | el 4 Interrupt<br>led<br>nabled<br>el 3 Interrupt<br>led                                                              |                                  |               |                 |        |  |  |  |

|                           | 1 = Interrupt<br>0 = Interrupt<br><b>IC3IE:</b> Input<br>1 = Interrupt<br>0 = Interrupt                                                                                                                                                     | Capture Channe<br>request is enab<br>request is not e<br>Capture Channe<br>request is enab                                                                                                           | el 4 Interrupt<br>led<br>nabled<br>el 3 Interrupt<br>led<br>nabled                                                    |                                  |               |                 |        |  |  |  |

| bit 5                     | <ol> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>IC3IE: Input</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>Unimplement</li> </ol>                                                                                           | Capture Channe<br>request is enab<br>request is not e<br>Capture Channe<br>request is enab<br>request is not e                                                                                       | el 4 Interrupt<br>led<br>nabled<br>el 3 Interrupt<br>led<br>nabled<br>o'                                              |                                  |               |                 |        |  |  |  |

| bit 5<br>bit 4-2          | 1 = Interrupt<br>0 = Interrupt<br>IC3IE: Input<br>1 = Interrupt<br>0 = Interrupt<br>Unimplemen<br>SPI2IE: SPI2<br>1 = Interrupt                                                                                                             | Capture Channe<br>request is enab<br>request is not e<br>Capture Channe<br>request is enab<br>request is not e<br><b>nted:</b> Read as '0<br>2 Event Interrupt<br>request is enab                    | el 4 Interrupt<br>led<br>nabled<br>el 3 Interrupt<br>led<br>nabled<br>o'<br>: Enable bit<br>led                       |                                  |               |                 |        |  |  |  |

| bit 5<br>bit 4-2<br>bit 1 | <ol> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>IC3IE: Input</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>Unimplement</li> <li>SPI2IE: SPI2</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> </ol>                       | Capture Channe<br>request is enab<br>request is not e<br>Capture Channe<br>request is enab<br>request is not e<br><b>nted:</b> Read as (<br>2 Event Interrupt<br>request is enab<br>request is not e | el 4 Interrupt<br>led<br>nabled<br>el 3 Interrupt<br>led<br>nabled<br>o'<br>Enable bit<br>led<br>nabled               |                                  |               |                 |        |  |  |  |

| bit 5<br>bit 4-2          | <ol> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>IC3IE: Input</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>Unimplement</li> <li>SPI2IE: SPI2</li> <li>1 = Interrupt</li> <li>0 = Interrupt</li> <li>SPF2IE: SPI2</li> </ol> | Capture Channe<br>request is enab<br>request is not e<br>Capture Channe<br>request is enab<br>request is not e<br><b>nted:</b> Read as '0<br>2 Event Interrupt<br>request is enab                    | el 4 Interrupt<br>led<br>nabled<br>el 3 Interrupt<br>led<br>nabled<br>o'<br>Enable bit<br>led<br>nabled<br>Enable bit |                                  |               |                 |        |  |  |  |

#### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0                                | U-0 | U-0 | U-0 | U-0              | U-0              | U-0             | U-0     |

|------------------------------------|-----|-----|-----|------------------|------------------|-----------------|---------|

| —                                  |     | —   | _   | —                | —                | —               | —       |

| bit 15                             | •   |     |     | •                |                  |                 | bit 8   |

|                                    |     |     |     |                  |                  |                 |         |

| U-0                                | U-0 | U-0 | U-0 | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _                                  |     | _   |     | _                | INT1IP2          | INT1IP1         | INT1IP0 |

| bit 7                              | •   |     |     | •                |                  |                 | bit 0   |

|                                    |     |     |     |                  |                  |                 |         |

| Legend:                            |     |     |     |                  |                  |                 |         |

| R = Readable bit W = Writable bit  |     |     | bit | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at POR '1' = Bit is set |     |     |     | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

#### bit 15-3 Unimplemented: Read as '0'

- INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

bit 2-0

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0          | U-0                                                                                                           | U-0                                                                                                                                                                                                          | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0              |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|--------------------|--|--|--|--|

|              | —                                                                                                             | —                                                                                                                                                                                                            | DISSCK          | DISSDO           | MODE16           | SMP             | CKE <sup>(1)</sup> |  |  |  |  |

| oit 15       |                                                                                                               |                                                                                                                                                                                                              |                 |                  |                  |                 | bit                |  |  |  |  |

| R/W-0        | R/W-0                                                                                                         | R/W-0                                                                                                                                                                                                        | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0              |  |  |  |  |

| SSEN         | CKP                                                                                                           | MSTEN                                                                                                                                                                                                        | SPRE2           | SPRE1            | SPRE0            | PPRE1           | PPRE0              |  |  |  |  |

| pit 7        |                                                                                                               |                                                                                                                                                                                                              |                 |                  |                  |                 | bit                |  |  |  |  |

| _egend:      |                                                                                                               |                                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

| R = Readabl  | e bit                                                                                                         | W = Writable                                                                                                                                                                                                 | bit             | U = Unimpler     | mented bit, read | as '0'          |                    |  |  |  |  |

| n = Value at | POR                                                                                                           | '1' = Bit is set                                                                                                                                                                                             | :               | '0' = Bit is cle | ared             | x = Bit is unkn | iown               |  |  |  |  |

| oit 15-13    | Unimplemen                                                                                                    | ted: Read as '                                                                                                                                                                                               | 0'              |                  |                  |                 |                    |  |  |  |  |

| oit 12       | -                                                                                                             |                                                                                                                                                                                                              |                 | er modes only)   |                  |                 |                    |  |  |  |  |

|              |                                                                                                               |                                                                                                                                                                                                              | -               | functions as a   |                  |                 |                    |  |  |  |  |

|              | 0 = Internal S                                                                                                | SPI clock is en                                                                                                                                                                                              | abled           |                  |                  |                 |                    |  |  |  |  |

| bit 11       | DISSDO: Dis                                                                                                   | able SDOx pin                                                                                                                                                                                                | bit             |                  |                  |                 |                    |  |  |  |  |

|              |                                                                                                               |                                                                                                                                                                                                              |                 | the pin functio  | ns as an I/O     |                 |                    |  |  |  |  |

|              |                                                                                                               | n is controlled                                                                                                                                                                                              | •               |                  |                  |                 |                    |  |  |  |  |

| bit 10       |                                                                                                               | ord/Byte Comn                                                                                                                                                                                                |                 |                  |                  |                 |                    |  |  |  |  |

|              | <ul> <li>1 = Communication is word-wide (16 bits)</li> <li>0 = Communication is byte-wide (8 bits)</li> </ul> |                                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

| oit 9        |                                                                                                               | ata Input Sam                                                                                                                                                                                                |                 |                  |                  |                 |                    |  |  |  |  |

| Dit 9        | Master mode                                                                                                   |                                                                                                                                                                                                              | bie i nase bit  |                  |                  |                 |                    |  |  |  |  |

|              | <u>Master mode:</u><br>1 = Input data is sampled at the end of data output time                               |                                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

|              |                                                                                                               | <ul> <li>I = input data is sampled at the end of data output time</li> <li>Input data is sampled at the middle of data output time</li> </ul>                                                                |                 |                  |                  |                 |                    |  |  |  |  |

|              | <u>Slave mode:</u>                                                                                            | cleared when                                                                                                                                                                                                 | SPIx is used i  | n Slave mode.    |                  |                 |                    |  |  |  |  |

| bit 8        |                                                                                                               |                                                                                                                                                                                                              |                 | n olave mode.    |                  |                 |                    |  |  |  |  |

|              |                                                                                                               | <b>CKE:</b> SPIx Clock Edge Select bit <sup>(1)</sup><br>1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)                                                |                 |                  |                  |                 |                    |  |  |  |  |

|              |                                                                                                               | 0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)<br>0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6) |                 |                  |                  |                 |                    |  |  |  |  |

| bit 7        | SSEN: Slave                                                                                                   | Select Enable                                                                                                                                                                                                | bit (Slave mo   | de)              |                  |                 |                    |  |  |  |  |

|              |                                                                                                               | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

|              |                                                                                                               |                                                                                                                                                                                                              |                 | controlled by p  | port function    |                 |                    |  |  |  |  |

| bit 6        |                                                                                                               | Polarity Select                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

|              |                                                                                                               | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                     |                 |                  |                  |                 |                    |  |  |  |  |

| bit 5        |                                                                                                               | ter Mode Enat                                                                                                                                                                                                |                 | e state is a nig | in ievei         |                 |                    |  |  |  |  |

|              | 1 = Master m                                                                                                  |                                                                                                                                                                                                              | DIE DIL         |                  |                  |                 |                    |  |  |  |  |

|              | 0 = Slave mo                                                                                                  |                                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

| bit 4-2      |                                                                                                               | Secondary Pre                                                                                                                                                                                                | escale bits (Ma | aster mode)      |                  |                 |                    |  |  |  |  |

|              |                                                                                                               | dary prescale '                                                                                                                                                                                              | -               | ,                |                  |                 |                    |  |  |  |  |

|              |                                                                                                               | dary prescale 2                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

|              | <br>000 <b>= Seco</b> nd                                                                                      | dary prescale 8                                                                                                                                                                                              | 3:1             |                  |                  |                 |                    |  |  |  |  |

| oit 1-0      | PPRE<1:0>:                                                                                                    | Primary Presc                                                                                                                                                                                                | ale bits (Maste | er mode)         |                  |                 |                    |  |  |  |  |

|              | 11 = Primary                                                                                                  |                                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

|              | 10 = Primary                                                                                                  |                                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

|              | 01 = Primary                                                                                                  |                                                                                                                                                                                                              |                 |                  |                  |                 |                    |  |  |  |  |

|              | 00 = Primary                                                                                                  | DIESCALE 04.                                                                                                                                                                                                 |                 |                  |                  |                 |                    |  |  |  |  |

SPI modes (FRMEN = 1).

Internal Data Bus

Read

# 17.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UBRGx register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt).

- 4. Write data byte to lower byte of UTXxREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

# 17.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 17.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. Serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 17.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header, made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character,

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

### 17.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 17.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 17.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware controlled pins that are associated with the UARTx modules. These two pins allow the UARTx to operate in Simplex and Flow Control mode. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 17.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support the external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

# 17.8 External IrDA Support – IrDA Clock Output

To support the external IrDA encoder and decoder devices, the BCLKx pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. With UEN<1:0> = 11, the BCLKx pin will output the 16x baud clock if the UARTx module is enabled. It can be used to support the IrDA codec chip.

# 17.9 Built-in IrDA Encoder and Decoder

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit UxMODE<12>. When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

### 19.1 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- · Alarm Value Registers

#### 19.1.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 19-1). By writing the RTCVALH byte, the RTCC Pointer value, RTCPTR<1:0>, decrements by one until it reaches '00'. Once it reaches '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 19-1: RTCVAL REGISTER MAPPING

| RTCPTR | RTCC Value Register Window |             |  |  |  |

|--------|----------------------------|-------------|--|--|--|

| <1:0>  | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |

| 00     | MINUTES                    | SECONDS     |  |  |  |

| 01     | WEEKDAY                    | HOURS       |  |  |  |

| 10     | MONTH                      | DAY         |  |  |  |

| 11     |                            | YEAR        |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 19-2).

By writing the ALRMVALH byte, the Alarm Pointer value, ALRMPTR<1:0>, decrements by one until it reaches '00'. Once it reaches '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### TABLE 19-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |  |

|---------|-----------------------------|--------------|--|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |  |

| 11      | _                           | —            |  |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes it will decrement the ALRMPTR<1:0> value. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | not write operations.                    |  |  |  |  |  |

#### 19.1.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL<13>) must be set (refer to Example 19-1).

#### EXAMPLE 19-1: SETTING THE RTCWREN BIT IN MPLAB<sup>®</sup> C30

```

asm volatile("disi #13");

asm volatile("push W1");

asm volatile("push W2");

asm volatile("push W3");

//move the address of NVMKEY into W1

asm volatile("MOV #NVMKEY, W1");