Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 84                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga010-i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2 |        | PIC24FJ128GA010 FAMIL<br>Pin Number |                |             |                 |                                                                    |

|-----------|--------|-------------------------------------|----------------|-------------|-----------------|--------------------------------------------------------------------|

| Function  | 64-Pin | 80-Pin                              | 100-Pin        | I/O         | Input<br>Buffer | Description                                                        |

| AN0       | 16     | 20                                  | 25             | 1           | ANA             | A/D Analog Inputs.                                                 |

| AN1       | 15     | 19                                  | 24             | I           | ANA             |                                                                    |

| AN2       | 14     | 18                                  | 23             | 1           | ANA             |                                                                    |

| AN3       | 13     | 17                                  | 22             | I           | ANA             |                                                                    |

| AN4       | 12     | 16                                  | 21             | I           | ANA             |                                                                    |

| AN5       | 11     | 15                                  | 20             | I           | ANA             |                                                                    |

| AN6       | 17     | 21                                  | 26             | I           | ANA             |                                                                    |

| AN7       | 18     | 22                                  | 27             | I           | ANA             |                                                                    |

| AN8       | 21     | 27                                  | 32             | I           | ANA             | -                                                                  |

| AN9       | 22     | 28                                  | 33             | I           | ANA             | -                                                                  |

| AN10      | 23     | 29                                  | 34             | I           | ANA             | -                                                                  |

| AN11      | 24     | 30                                  | 35             | I           | ANA             |                                                                    |

| AN12      | 27     | 33                                  | 41             | I           | ANA             | -                                                                  |

| AN13      | 28     | 34                                  | 42             | I           | ANA             | 1                                                                  |

| AN14      | 29     | 35                                  | 43             | I           | ANA             | 1                                                                  |

| AN15      | 30     | 36                                  | 44             | I           | ANA             |                                                                    |

| AVdd      | 19     | 25                                  | 30             | Р           | _               | Positive Supply for Analog Modules.                                |

| AVss      | 20     | 26                                  | 31             | Р           | _               | Ground Reference for Analog Modules.                               |

| BCLK1     | 35     | 38                                  | 48             | 0           | _               | UART1 IrDA <sup>®</sup> Baud Clock.                                |

| BCLK2     | 29     | 35                                  | 39             | 0           | _               | UART2 IrDA <sup>®</sup> Baud Clock.                                |

| C1IN-     | 12     | 16                                  | 21             | I           | ANA             | Comparator 1 Negative Input.                                       |

| C1IN+     | 11     | 15                                  | 20             | I           | ANA             | Comparator 1 Positive Input.                                       |

| C10UT     | 21     | 27                                  | 32             | 0           | _               | Comparator 1 Output.                                               |

| C2IN-     | 14     | 18                                  | 23             | I           | ANA             | Comparator 2 Negative Input.                                       |

| C2IN+     | 13     | 17                                  | 22             | I           | ANA             | Comparator 2 Positive Input.                                       |

| C2OUT     | 22     | 28                                  | 33             | 0           | _               | Comparator 2 Output.                                               |

| CLKI      | 39     | 49                                  | 63             | I           | ANA             | Main Clock Input Connection.                                       |

| CLKO      | 40     | 50                                  | 64             | 0           | _               | System Clock Output.                                               |

| CN0       | 48     | 60                                  | 74             | I           | ST              | Interrupt-on-Change Inputs.                                        |

| CN1       | 47     | 59                                  | 73             | I           | ST              |                                                                    |

| CN2       | 16     | 20                                  | 25             | I           | ST              |                                                                    |

| CN3       | 15     | 19                                  | 24             | I           | ST              |                                                                    |

| CN4       | 14     | 18                                  | 23             | I           | ST              | ]                                                                  |

| CN5       | 13     | 17                                  | 22             | I           | ST              | ]                                                                  |

| CN6       | 12     | 16                                  | 21             | I           | ST              |                                                                    |

| CN7       | 11     | 15                                  | 20             | I           | ST              |                                                                    |

| CN8       | 4      | 6                                   | 10             | I           | ST              |                                                                    |

| CN9       | 5      | 7                                   | 11             | I           | ST              |                                                                    |

| CN10      | 6      | 8                                   | 12             | I           | ST              |                                                                    |

| CN11      | 8      | 10                                  | 14             | I           | ST              |                                                                    |

| CN12      | 30     | 36                                  | 44             | I           | ST              |                                                                    |

| CN13      | 52     | 66                                  | 81             | 1           | ST              |                                                                    |

| CN14      | 53     | 67                                  | 82             | I           | ST              |                                                                    |

| CN15      | 54     | 68                                  | 83             | I           | ST              |                                                                    |

| CN16      | 55     | 69                                  | 84             | I           | ST              |                                                                    |

| CN17      | 31     | 39                                  | 49             | I           | ST              |                                                                    |

| Legend:   |        | ut buffor ST -                      | - Schmitt Tria | aor input k | ouffor ANA      | = Analog level input/output, $I^2C^{TM} = I^2C/SMBus$ input buffer |

#### TABLE 1-2: PIC24FJ128GA010 FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer, ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $l^2C^{TM} = l^2C/SMBus$  input buffer

#### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase block containing the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- 6. Repeat Steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY BLOCK

| ; Set u | MOV    | N for block erase operation<br>#0x4042, W0<br>W0, NVMCON | ; | Initialize NVMCON                     |

|---------|--------|----------------------------------------------------------|---|---------------------------------------|

| • Trit  |        | to row to be ERASED                                      | ' | IIIIIIIIZE NVMCON                     |

| , 11110 | MOV    | <pre>#tblpage(PROG_ADDR), W0</pre>                       |   |                                       |

|         |        |                                                          |   |                                       |

|         | MOV    | W0, TBLPAG                                               | ; | Initialize PM Page Boundary SFR       |

|         | MOV    | <pre>#tbloffset(PROG_ADDR), W0</pre>                     | ; | Initialize in-page EA[15:0] pointer   |

|         | TBLWTL | W0, [W0]                                                 | ; | Set base address of erase block       |

|         | DISI   | #5                                                       | ; | Block all interrupts with priority <7 |

|         |        |                                                          | ; | for next 5 instructions               |

|         | MOV    | #0x55, W0                                                |   |                                       |

|         | MOV    | W0, NVMKEY                                               | ; | Write the 55 key                      |

|         | MOV    | #0xAA, W1                                                | ; |                                       |

|         | MOV    | W1, NVMKEY                                               | ; | Write the AA key                      |

|         | BSET   | NVMCON, #WR                                              | ; | Start the erase sequence              |

|         | NOP    |                                                          | ; | Insert two NOPs after the erase       |

|         | NOP    |                                                          | ; | command is asserted                   |

|         |        |                                                          |   |                                       |

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred (note that BOR is also set after a Power-on Reset)

- 0 = A Brown-out Reset has not occurred

- bit 0 POR: Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized W register access | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT time-out                                      | PWRSAV instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | _                       |

| POR (RCON<0>)     | POR                                               | —                       |

TABLE 6-1: RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

#### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 8.0** "Oscillator Configuration" for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time that the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| U-0          | R/W-1                          | R/W-0                                                                                                                    | R/W-0             | U-0              | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |

|--------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|-----------------|----------|--|--|--|--|

|              | CNIP2                          | CNIP1                                                                                                                    | CNIP0             | _                | CMIP2             | CMIP1           | CMIP0    |  |  |  |  |

| bit 15       |                                |                                                                                                                          |                   |                  | ÷                 |                 | bit      |  |  |  |  |

| U-0          | R/W-1                          | R/W-0                                                                                                                    | R/W-0             | U-0              | R/W-1             | R/W-0           | R/W-0    |  |  |  |  |

| _            | MI2C1IP2                       | MI2C1IP1                                                                                                                 | MI2C1IP0          | _                | SI2C1IP2          | SI2C1IP1        | SI2C1IP0 |  |  |  |  |

| bit 7        |                                | _                                                                                                                        |                   |                  |                   |                 | bit      |  |  |  |  |

| Legend:      |                                |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

| R = Readab   | le bit                         | W = Writable                                                                                                             | bit               | U = Unimple      | emented bit, read | 1 as '0'        |          |  |  |  |  |

| -n = Value a |                                | '1' = Bit is set                                                                                                         |                   | '0' = Bit is cl  |                   | x = Bit is unkr | nown     |  |  |  |  |

|              |                                |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

| bit 15       | Unimplemen                     | ted: Read as '                                                                                                           | 0'                |                  |                   |                 |          |  |  |  |  |

| bit 14-12    | CNIP<2:0>:                     | nput Change N                                                                                                            | Iotification Inte | errupt Priority  | bits              |                 |          |  |  |  |  |

|              | 111 = Interru                  | pt is Priority 7 (                                                                                                       | highest priorit   | y interrupt)     |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              | 001 = Interru<br>000 = Interru | pt is Priority 1<br>pt source is dis                                                                                     | abled             |                  |                   |                 |          |  |  |  |  |

| bit 11       |                                | ted: Read as '                                                                                                           |                   |                  |                   |                 |          |  |  |  |  |

| bit 10-8     | -                              |                                                                                                                          |                   | bits             |                   |                 |          |  |  |  |  |

|              |                                | <b>CMIP&lt;2:0&gt;:</b> Comparator Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                   |                  |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              | 001 = Interru                  | pt is Priority 1<br>pt source is dis                                                                                     | abled             |                  |                   |                 |          |  |  |  |  |

| bit 7        |                                | ted: Read as '                                                                                                           |                   |                  |                   |                 |          |  |  |  |  |

| bit 6-4      | -                              | >: Master I2C1                                                                                                           |                   | pt Priority bits | 6                 |                 |          |  |  |  |  |

|              |                                | pt is Priority 7 (                                                                                                       |                   |                  |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              | 001 = Interru                  | pt is Priority 1                                                                                                         |                   |                  |                   |                 |          |  |  |  |  |

|              |                                | pt source is dis                                                                                                         |                   |                  |                   |                 |          |  |  |  |  |

| bit 3        | •                              | ted: Read as '                                                                                                           |                   |                  |                   |                 |          |  |  |  |  |

| bit 2-0      |                                | Slave I2C1 I<br>pt is Priority 7 (                                                                                       |                   | -                |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              | •                              |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              |                                |                                                                                                                          |                   |                  |                   |                 |          |  |  |  |  |

|              |                                | pt is Priority 1<br>pt source is dis                                                                                     |                   |                  |                   |                 |          |  |  |  |  |

#### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0              | R/W-1                                                                           | R/W-0                                                                      | R/W-0                                                | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| _                | CRCIP2                                                                          | CRCIP1                                                                     | CRCIP0                                               | _                | U2ERIP2          | U2ERIP1         | U2ERIP0 |  |  |  |  |

| bit 15           |                                                                                 | •                                                                          | •                                                    |                  |                  | ·               | bit 8   |  |  |  |  |

| U-0              | R/W-1                                                                           | R/W-0                                                                      | R/W-0                                                | U-0              | U-0              | U-0             | U-0     |  |  |  |  |

|                  | U1ERIP2                                                                         | U1ERIP1                                                                    | U1ERIP0                                              | <u> </u>         |                  |                 | 0-0     |  |  |  |  |

| bit 7            | UTERII 2                                                                        | OTEINIT                                                                    | OTENITO                                              |                  |                  |                 | bit C   |  |  |  |  |

|                  |                                                                                 |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |

| Legend:          | la hit                                                                          |                                                                            | L:4                                                  |                  | mented bit meet  |                 |         |  |  |  |  |

| R = Readab       |                                                                                 | W = Writable                                                               |                                                      | -                | mented bit, read |                 |         |  |  |  |  |

| -n = Value a     | TPOR                                                                            | '1' = Bit is set                                                           |                                                      | '0' = Bit is cle | eared            | x = Bit is unkr | lown    |  |  |  |  |

| bit 15           | Unimplemen                                                                      | ted: Read as '                                                             | 0'                                                   |                  |                  |                 |         |  |  |  |  |

| bit 14-12        | -                                                                               | CRC Generato                                                               |                                                      | ot Priority bits |                  |                 |         |  |  |  |  |

|                  |                                                                                 | ot is Priority 7 (                                                         |                                                      | • •              |                  |                 |         |  |  |  |  |

|                  | •                                                                               | , , , , , , , , , , , , , , , , , , ,                                      | 0                                                    | , ,              |                  |                 |         |  |  |  |  |

|                  | •                                                                               |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |

|                  | •<br>001 = Interru                                                              | ot is Priority 1                                                           |                                                      |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                 | ot source is dis                                                           | abled                                                |                  |                  |                 |         |  |  |  |  |

| bit 11           | -                                                                               | ted: Read as '                                                             |                                                      |                  |                  |                 |         |  |  |  |  |

| bit 10-8         | -                                                                               | UART2 Erro                                                                 |                                                      | ority bits       |                  |                 |         |  |  |  |  |

|                  |                                                                                 | ot is Priority 7 (                                                         | •                                                    | •                |                  |                 |         |  |  |  |  |

|                  | •                                                                               |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |

|                  | •                                                                               |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |

|                  | •<br>001 = Interrupt is Priority 1                                              |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |

|                  | 001 = Interru                                                                   | ot is Priority 1                                                           |                                                      |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                 | ot is Priority 1<br>ot source is dis                                       | abled                                                |                  |                  |                 |         |  |  |  |  |

| bit 7            | 000 = Interru                                                                   |                                                                            |                                                      |                  |                  |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen                                                     | ot source is dis                                                           | 0'                                                   | prity bits       |                  |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                      | ot source is dis<br><b>ted:</b> Read as '                                  | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                      | ot source is dis<br>ted: Read as '<br>•: UART1 Error                       | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                      | ot source is dis<br>ted: Read as '<br>•: UART1 Error                       | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interruj<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interruj<br>•<br>•         | ot source is dis<br>ted: Read as '<br>•: UART1 Error<br>ot is Priority 7 ( | <sup>0'</sup><br>r Interrupt Pric                    | •                |                  |                 |         |  |  |  |  |

|                  | 000 = Interruj<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interruj<br>001 = Interruj | ot source is dis<br>ted: Read as '<br>•: UART1 Error<br>ot is Priority 7 ( | <sup>0'</sup><br>r Interrupt Pric<br>highest priorit | •                |                  |                 |         |  |  |  |  |

#### REGISTER 7-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

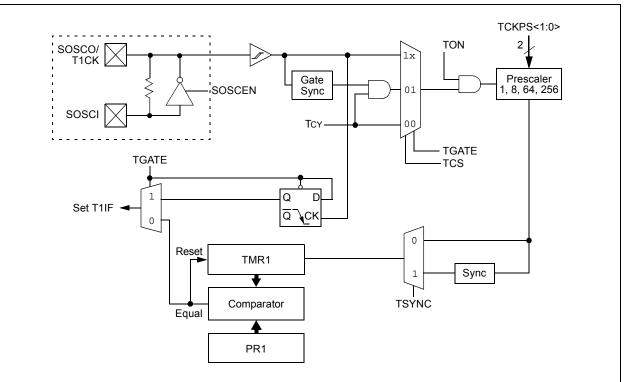

# 11.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 14. "Timers" (DS39704) in the "PIC24F Family Reference Manual" for more information.

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of the external gate signal

Figure 11-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

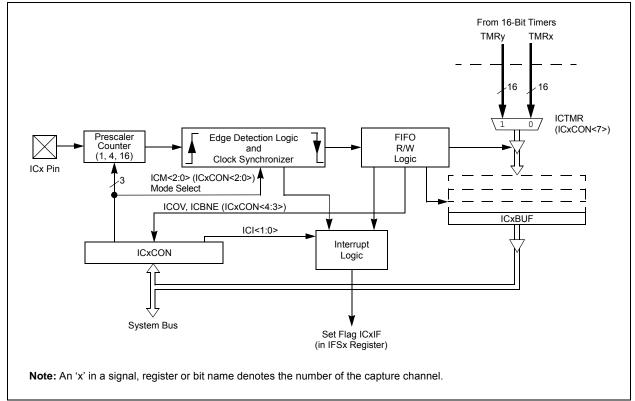

# 13.0 INPUT CAPTURE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 15. "Input Capture" (DS39701) in the "PIC24F Family Reference Manual" for more information.

The input capture module has multiple operating modes, which are selected via the ICxCON register. The operating modes include:

- Capture timer value on every falling edge of input, applied at the ICx pin

- Capture timer value on every rising edge of input, applied at the ICx pin

- Capture timer value on every fourth rising edge of input, applied at the ICx pin

- Capture timer value on every 16th rising edge of input, applied at the ICx pin

- Capture timer value on every rising and every falling edge of input, applied at the ICx pin

- Device wake-up from capture pin during CPU Sleep and Idle modes

The input capture module has a four-level FIFO buffer. The number of capture events required to generate a CPU interrupt can be selected by the user.

### FIGURE 13-1: INPUT CAPTURE BLOCK DIAGRAM

# 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 23. "Serial Peripheral Interface (SPI)" (DS39699) in the "PIC24F Family Reference Manual" for more information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with SPI and SIOP interfaces from Motorola<sup>®</sup>.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPIxBUF register, in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave modes. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- · SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

A block diagram of the module is shown in Figure 15-1 and Figure 15-2.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module. To set up the SPI module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- 2. Write the desired settings to the SPIxCON register with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

# REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ACKDT: Acknowledge Data bit (When operating as an I<sup>2</sup>C master; applicable during master receive.)</li> <li>Value that will be transmitted when the software initiates an Acknowledge sequence.</li> <li>1 = Sends NACK during Acknowledge</li> <li>0 = Sends ACK during Acknowledge</li> </ul>                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit<br/>(When operating as an I<sup>2</sup>C master; applicable during master receive.)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit.<br/>Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <ul> <li>RCEN: Receive Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                                                             |

| bit 2 | <ul> <li>PEN: Stop Condition Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                                                                        |

| bit 1 | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                                                               |

| bit 0 | <ul> <li>SEN: Start Condition Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                                    |

# 17.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UBRGx register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt).

- 4. Write data byte to lower byte of UTXxREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

# 17.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 17.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. Serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 17.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header, made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character,

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

#### 17.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 17.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 17.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware controlled pins that are associated with the UARTx modules. These two pins allow the UARTx to operate in Simplex and Flow Control mode. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 17.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support the external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

# 17.8 External IrDA Support – IrDA Clock Output

To support the external IrDA encoder and decoder devices, the BCLKx pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. With UEN<1:0> = 11, the BCLKx pin will output the 16x baud clock if the UARTx module is enabled. It can be used to support the IrDA codec chip.

# 17.9 Built-in IrDA Encoder and Decoder

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit UxMODE<12>. When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

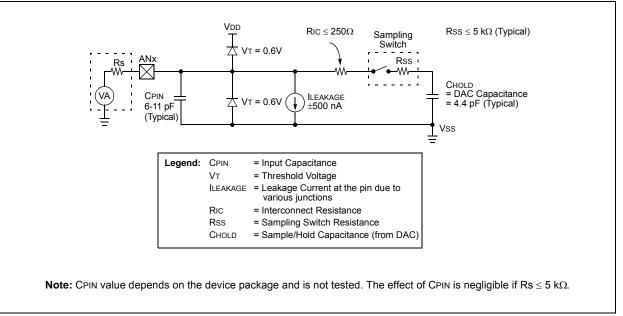

# EQUATION 21-1: A/D CONVERSION CLOCK PERIOD<sup>(1)</sup>

TAD = TCY(ADCS + 1) $ADCS = \frac{TAD}{TCY} - 1$

**Note 1:** Based on TCY = TOSC \* 2; Doze mode and PLL are disabled.

#### FIGURE 21-2: 10-BIT A/D CONVERTER ANALOG INPUT MODEL

#### 24.4 JTAG Interface

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 33. "Programming and Diagnostics" (DS39716) in the "PIC24F Family Reference Manual" for more information.

PIC24FJ128GA010 family devices implement a JTAG interface, which supports boundary scan device testing as well as In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

Refer to the Microchip web site (www.microchip.com) for JTAG support files and additional information.

#### 24.5 Program Verification and Code Protection

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 33. "Programming and Diagnostics" (DS39716) in the "PIC24F Family Reference Manual" for more information.

For all devices in the PIC24FJ128GA010 family, the on-chip program memory space is treated as a single block. Code protection for this block is controlled by one Configuration bit, GCP (Flash Configuration Word 1<13>. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

Write protection is controlled by the GWRP bit (Flash Configuration Word 1<12>. When GWRP is programmed to '0', internal write and erase operations to the program memory are blocked.

#### 24.5.1 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against inadvertent or unwanted changes, or reads in two ways. The primary protection method is the same as that of the shadow registers, which contain a complimentary value that is constantly compared with the actual value. To safeguard against unpredictable events, Configuration bit changes resulting from individual cell level disruptions (such as ESD events) will cause a parity error and trigger a device Configuration Word Mismatch Reset.

The data for the Configuration registers is derived from the Flash Configuration Words in program memory. As a consequence, when the GCP bit is set, the source data for the device configuration is also protected.

#### 24.6 In-Circuit Serial Programming

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 33. "Programming and Diagnostics" (DS39716) in the "PIC24F Family Reference Manual" for more information.

PIC24FJ128GA010 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGCx) and data (PGDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 24.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the In-Circuit Debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the EMUCx (Emulation/Debug Clock) and EMUDx (Emulation/Debug Data) pins.

To use the In-Circuit Debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGCx, PGDx and the EMUDx/EMUCx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|------------------|----------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                                | 2             | 2              | None                     |

|                      | GOTO   | Wn               | Go to Indirect                               | 1             | 2              | None                     |

| INC                  | INC    | f                | f = f + 1                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | f,WREG           | WREG = f + 1                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                  | 1             | 1              | C, DC, N, OV, Z          |

| INC2                 | INC2   | f                | f = f + 2                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | f,WREG           | WREG = f + 2                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | Ws,Wd            | Wd = Ws + 2                                  | 1             | 1              | C, DC, N, OV, Z          |

| IOR                  | IOR    | f                | f = f .IOR. WREG                             | 1             | 1              | N, Z                     |

|                      | IOR    | f,WREG           | WREG = f .IOR. WREG                          | 1             | 1              | N, Z                     |

|                      | IOR    | #lit10,Wn        | Wd = lit10 .IOR. Wd                          | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,Ws,Wd         | Wd = Wb .IOR. Ws                             | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,#lit5,Wd      | Wd = Wb .IOR. lit5                           | 1             | 1              | N, Z                     |

| LNK                  | LNK    | #lit14           | Link Frame Pointer                           | 1             | 1              | None                     |

| LSR                  | LSR    | f                | f = Logical Right Shift f                    | 1             | 1              | C, N, OV, Z              |

| 2010                 | LSR    | f,WREG           | WREG = Logical Right Shift f                 | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Ws,Wd            | Wite S = Logical Right Shift Ws              | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Wb,Wns,Wnd       | Wrd = Logical Right Shift Wb by Wrs          | 1             | 1              | N, Z                     |

|                      |        |                  | Wind = Logical Right Shift Wb by Wils        | 1             | 1              | N, Z                     |

| MOM                  | LSR    | Wb,#lit5,Wnd     | Move f to Wn                                 | 1             | 1              | None                     |

| MOV                  | MOV    | f,Wn             |                                              | 1             | 1              |                          |

|                      | MOV    | [Wns+Slit10],Wnd | Move [Wns+Slit10] to Wnd                     |               |                | None                     |

|                      | MOV    | f                | Move f to f                                  | 1             | 1              | N, Z                     |

|                      | MOV    | f,WREG           | Move f to WREG                               | 1             | 1              | N, Z                     |

|                      | MOV    | #lit16,Wn        | Move 16-Bit Literal to Wn                    | 1             | 1              | None                     |

|                      | MOV.b  | #lit8,Wn         | Move 8-Bit Literal to Wn                     | 1             | 1              | None                     |

|                      | MOV    | Wn,f             | Move Wn to f                                 | 1             | 1              | None                     |

|                      | MOV    | Wns,[Wns+Slit10] | Move Wns to [Wns+Slit10]                     | 1             | 1              |                          |

|                      | MOV    | Wso,Wdo          | Move Ws to Wd                                | 1             | 1              | None                     |

|                      | MOV    | WREG, f          | Move WREG to f                               | 1             | 1              | N, Z                     |

|                      | MOV.D  | Wns,Wd           | Move Double from W(ns):W(ns+1) to Wd         | 1             | 2              | None                     |

|                      | MOV.D  | Ws,Wnd           | Move Double from Ws to W(nd+1):W(nd)         | 1             | 2              | None                     |

| MUL                  | MUL.SS | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Signed(Ws)       | 1             | 1              | None                     |

|                      | MUL.SU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws)     | 1             | 1              | None                     |

|                      | MUL.US | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Signed(Ws)     | 1             | 1              | None                     |

|                      | MUL.UU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(Ws)   | 1             | 1              | None                     |

|                      | MUL.SU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(lit5)   | 1             | 1              | None                     |

|                      | MUL.UU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(lit5) | 1             | 1              | None                     |

|                      | MUL    | f                | W3:W2 = f * WREG                             | 1             | 1              | None                     |

| NEG                  | NEG    | f                | $f = \overline{f} + 1$                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | f,WREG           | WREG = $\overline{f}$ + 1                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | Ws,Wd            | $Wd = \overline{Ws} + 1$                     | 1             | 1              | C, DC, N, OV, Z          |

| NOP                  | NOP    |                  | No Operation                                 | 1             | 1              | None                     |

| -                    | NOPR   |                  | No Operation                                 | 1             | 1              | None                     |

| POP                  | POP    | f                | Pop f from Top-of-Stack (TOS)                | 1             | 1              | None                     |

|                      | POP    | Wdo              | Pop from Top-of-Stack (TOS) to Wdo           | 1             | 1              | None                     |

|                      | POP.D  | Wnd              | Pop from Top-of-Stack (TOS) to W(nd):W(nd+1) | 1             | 2              | None                     |

|                      | POP.S  | mitt             | Pop Shadow Registers                         | 1             | 1              | All                      |

| PUSH                 | PUSH   | f                | Push f to Top-of-Stack (TOS)                 | 1             | 1              | None                     |

| ruan                 | PUSH   |                  | Push Wso to Top-of-Stack (TOS)               | 1             | 1              | None                     |

|                      |        | Wso              | ,                                            |               | 2              |                          |

|                      | PUSH.D | Wns              | Push W(ns):W(ns+1) to Top-of-Stack (TOS)     | 1             | ۷              | None                     |

#### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic | Assembly Syntax |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |

|----------------------|-----------------|-------------|------------------------------|---------------|----------------|--------------------------|--|

| TBLRDL               | TBLRDL          | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |  |

| TBLWTH               | TBLWTH          | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |  |

| TBLWTL               | TBLWTL          | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |  |

| ULNK                 | ULNK            |             | Unlink Frame Pointer         | 1             | 1              | None                     |  |

| XOR                  | XOR             | f           | f = f .XOR. WREG             | 1             | 1              | N, Z                     |  |

|                      | XOR             | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |  |

|                      | XOR             | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |  |

|                      | XOR             | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |  |

|                      | XOR             | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |  |

| ZE                   | ZE              | Ws,Wnd      | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |  |

#### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

|              |       | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |                    |     |       |                              |

|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|------------------------------|

| Param<br>No. | Sym   | Characteristic <sup>(1)</sup>                                                                                                                    | Min | Тур <sup>(2)</sup> | Мах | Units | Conditions                   |

| OS50         | Fplli | PLL Input Frequency<br>Range                                                                                                                     | 3   | _                  | 8   | MHz   | ECPLL, HSPLL, XTPLL<br>modes |

| OS51         | Fsys  | PLL Output Frequency<br>Range                                                                                                                    | 12  | —                  | 32  | MHz   |                              |

| OS52         | Тгоск | PLL Start-up Time<br>(Lock Time)                                                                                                                 | -   | —                  | 2   | ms    |                              |

| OS53         | DCLK  | CLKO Stability (Jitter)                                                                                                                          | -2  | 1                  | +2  | %     |                              |

#### TABLE 27-18: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.0V TO 3.6V)

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 27-19: INTERNAL RC OSCILLATOR SPECIFICATIONS

| AC CHARACTERISTICS<br>Industrial |       |                               | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                         |   |            |  |

|----------------------------------|-------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---|------------|--|

| Param<br>No.                     | Sym   | Characteristic <sup>(1)</sup> | Min                                                                                                                                              | Typ Max Units Condition |   | Conditions |  |

|                                  | TFRC  | FRC Start-up Time             | —                                                                                                                                                | 15                      | — | μs         |  |

|                                  | TLPRC | LPRC Start-up Time            | —                                                                                                                                                | 500                     | — | μs         |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

#### TABLE 27-20: INTERNAL RC OSCILLATOR ACCURACY

| AC CH        | ARACTERISTICS                                | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |     |       |                                      |                  |  |

|--------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------------------------|------------------|--|

| Param<br>No. | Characteristic                               | Min                                                                                                                                                  | Тур | Max | Units | Conditions                           |                  |  |

|              | Internal FRC Accuracy @ 8 MHz <sup>(1)</sup> |                                                                                                                                                      |     |     |       |                                      |                  |  |

| F20          | FRC                                          | -2                                                                                                                                                   |     | +2  | %     | +25°C                                | VDD = 3.0 - 3.6V |  |

|              |                                              | -5                                                                                                                                                   | _   | +5  | %     | $-40^\circ C \le TA \le +85^\circ C$ | VDD = 3.0 - 3.6V |  |

| F21          | LPRC @ 31 kHz <sup>(1)</sup>                 | -15                                                                                                                                                  | _   | +15 | %     | $-40^\circ C \le TA \le +85^\circ C$ | VDD = 3.0 - 3.6V |  |

Note 1: Change of LPRC frequency as VDD changes.

#### 64-Lead QFN (9x9x0.9 mm)

#### Example

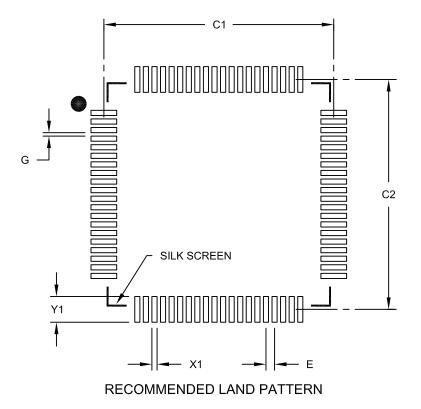

80-Lead Plastic Thin Quad Flatpack (PT) - 12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | MILLIMETERS |          |      |

|--------------------------|----------|-------------|----------|------|

| Dimensior                | n Limits | MIN         | NOM      | MAX  |

| Contact Pitch            | E        |             | 0.50 BSC |      |

| Contact Pad Spacing      | C1       |             | 13.40    |      |

| Contact Pad Spacing      | C2       |             | 13.40    |      |

| Contact Pad Width (X80)  | X1       |             |          | 0.30 |

| Contact Pad Length (X80) | Y1       |             |          | 1.50 |

| Distance Between Pads    | G        | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2092B

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | Ν    | <b>ILLIMETER</b> | S    |

|------------------------|--------|------|------------------|------|

| Dimension              | Limits | MIN  | NOM              | MAX  |

| Number of Pins         | Ν      |      | 64               |      |

| Pitch                  | е      |      | 0.50 BSC         |      |

| Overall Height         | А      | 0.80 | 0.90             | 1.00 |

| Standoff               | A1     | 0.00 | 0.02             | 0.05 |

| Contact Thickness      | A3     |      | 0.20 REF         | -    |

| Overall Width          | Е      |      | 9.00 BSC         |      |

| Exposed Pad Width      | E2     | 5.30 | 5.40             | 5.50 |

| Overall Length         | D      |      | 9.00 BSC         |      |

| Exposed Pad Length     | D2     | 5.30 | 5.40             | 5.50 |

| Contact Width          | b      | 0.20 | 0.25             | 0.30 |

| Contact Length         | L      | 0.30 | 0.40             | 0.50 |

| Contact-to-Exposed Pad | K      | 0.20 | -                | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2

## INDEX

| Α                                       |     |

|-----------------------------------------|-----|

| A/D                                     |     |

| Conversion Timing Requirements          |     |

| Module Specifications                   |     |

| AC                                      |     |

| Characteristics                         | 227 |

| Load Conditions                         |     |

| Temperature and Voltage Specifications  |     |

| Alternate Interrupt Vector Table (AIVT) | 63  |

| Arithmetic Logic Unit (ALU)             | 30  |

| Assembler                               |     |

| MPASM Assembler                         | 214 |

### В

| Block Diagrams                                      |   |

|-----------------------------------------------------|---|

| 10-Bit High-Speed A/D Converter                     | ) |

| 16-Bit Timer1 Module111                             |   |

| 8-Bit Multiplexed Address and Data Application 162  | 2 |

| Accessing Program Memory with                       |   |

| Table Instructions                                  | 3 |

| Addressable Parallel Slave Port                     |   |

| Comparator I/O Operating Modes                      | 9 |

| Comparator Voltage Reference                        |   |

| Connections for On-Chip Voltage Regulator           |   |

| Device Clock                                        | 7 |

| I <sup>2</sup> C                                    | 3 |

| Input Capture119                                    | 9 |

| LCD Control, Byte Mode 162                          | 2 |

| Legacy Parallel Slave Port                          |   |

| Master Mode, Demultiplexed Addressing               | ) |

| Master Mode, Fully Multiplexed Addressing           |   |

| Master Mode, Partially Multiplexed Addressing 161   | 1 |

| Multiplexed Addressing Application                  | 1 |

| Output Compare Module                               | 1 |

| Parallel EEPROM (Up to 15-Bit Address, 16-Bit Data) |   |