Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 84                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga010t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

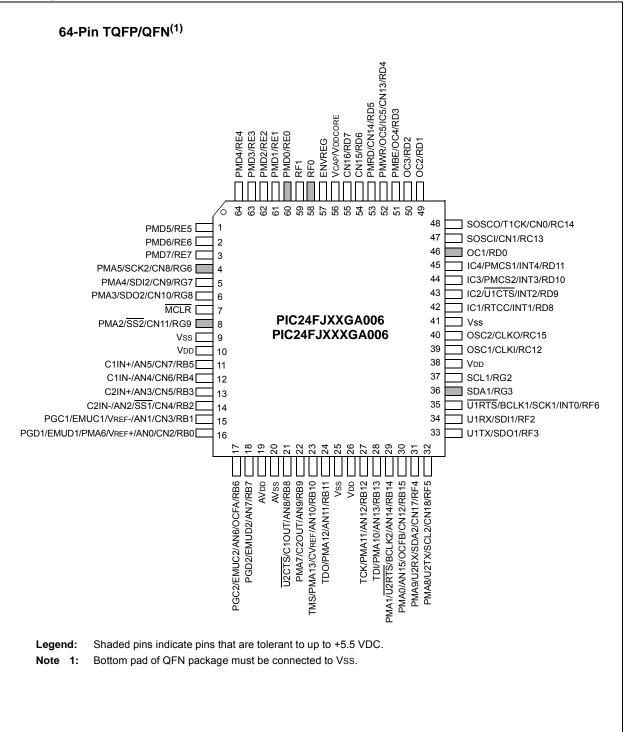

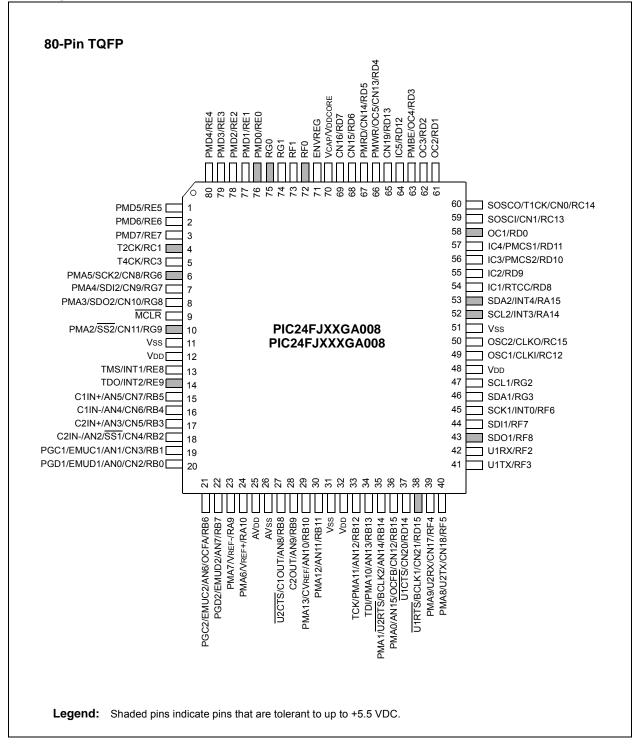

### **Pin Diagrams**

## **Pin Diagrams (Continued)**

| Function | Pin Number |        | 1/0     | Input | Description |                                                                                            |

|----------|------------|--------|---------|-------|-------------|--------------------------------------------------------------------------------------------|

| Function | 64-Pin     | 80-Pin | 100-Pin | I/O   | Buffer      | Description                                                                                |

| PMA0     | 30         | 36     | 44      | I/O   | ST/TTL      | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 29         | 35     | 43      | I/O   | ST/TTL      | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | 8          | 10     | 14      | 0     | _           | Parallel Master Port Address (Demultiplexed Master                                         |

| PMA3     | 6          | 8      | 12      | 0     | —           | modes).                                                                                    |

| PMA4     | 5          | 7      | 11      | 0     | _           |                                                                                            |

| PMA5     | 4          | 6      | 10      | 0     | _           |                                                                                            |

| PMA6     | 16         | 24     | 29      | 0     | _           |                                                                                            |

| PMA7     | 22         | 23     | 28      | 0     | _           |                                                                                            |

| PMA8     | 32         | 40     | 50      | 0     | _           |                                                                                            |

| PMA9     | 31         | 39     | 49      | 0     | _           |                                                                                            |

| PMA10    | 28         | 34     | 42      | 0     | _           |                                                                                            |

| PMA11    | 27         | 33     | 41      | 0     | _           |                                                                                            |

| PMA12    | 24         | 30     | 35      | 0     | _           |                                                                                            |

| PMA13    | 23         | 29     | 34      | 0     | _           |                                                                                            |

| PMBE     | 51         | 63     | 78      | 0     | _           | Parallel Master Port Byte Enable Strobe.                                                   |

| PMCS1    | 45         | 57     | 71      | I/O   | ST/TTL      | Parallel Master Port Chip Select 1 Strobe/Address bit 1                                    |

| PMCS2    | 44         | 56     | 70      | 0     | —           | Parallel Master Port Chip Select 2 Strobe/Address bit 15                                   |

| PMD0     | 60         | 76     | 93      | I/O   | ST/TTL      | Parallel Master Port Data (Demultiplexed Master mode                                       |

| PMD1     | 61         | 77     | 94      | I/O   | ST/TTL      | or Address/Data (Multiplexed Master modes).                                                |

| PMD2     | 62         | 78     | 98      | I/O   | ST/TTL      |                                                                                            |

| PMD3     | 63         | 79     | 99      | I/O   | ST/TTL      |                                                                                            |

| PMD4     | 64         | 80     | 100     | I/O   | ST/TTL      |                                                                                            |

| PMD5     | 1          | 1      | 3       | I/O   | ST/TTL      |                                                                                            |

| PMD6     | 2          | 2      | 4       | I/O   | ST/TTL      |                                                                                            |

| PMD7     | 3          | 3      | 5       | I/O   | ST/TTL      | ]                                                                                          |

| PMRD     | 53         | 67     | 82      | I/O   | ST/TTL      | Parallel Master Port Read Strobe.                                                          |

| PMWR     | 52         | 66     | 81      | I/O   | ST/TTL      | Parallel Master Port Write Strobe.                                                         |

### TABLE 1-2: PIC24FJ128GA010 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer, ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $l^2C^{TM} = l^2C/SMBus$  input buffer

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP

|              |      |        |         | 00111   |         |        |          |          |          |       |          |          |          |         |          |          |          |               |

|--------------|------|--------|---------|---------|---------|--------|----------|----------|----------|-------|----------|----------|----------|---------|----------|----------|----------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| INTCON1      | 0800 | NSTDIS | _       | _       | _       | _      | _        |          | _        |       | _        | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI    | _       | _       | _      | _        | _        | _        | _     | _        | _        | INT4EP   | INT3EP  | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084 | _      | _       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF   | SPF1IF   | T3IF     | T2IF  | OC2IF    | IC2IF    | _        | T1IF    | OC1IF    | IC1IF    | INT0IF   | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF  | INT2IF  | T5IF    | T4IF   | OC4IF    | OC3IF    | _        |       | _        | _        | INT1IF   | CNIF    | CMIF     | MI2C1IF  | SI2C1IF  | 0000          |

| IFS2         | 0088 | _      | _       | PMPIF   | _       | _      | _        | OC5IF    | _        | IC5IF | IC4IF    | IC3IF    |          | -       | _        | SPI2IF   | SPF2IF   | 0000          |

| IFS3         | 008A | _      | RTCIF   | _       | _       | _      | _        | _        | _        |       | INT4IF   | INT3IF   |          |         | MI2C2IF  | SI2C2IF  | _        | 0000          |

| IFS4         | 008C | _      | _       | _       | _       | _      | _        | _        | _        | _     | _        | _        | _        | CRCIF   | U2ERIF   | U1ERIF   | _        | 0000          |

| IEC0         | 0094 | _      | -       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE   | SPF1IE   | T3IE     | T2IE  | OC2IE    | IC2IE    |          | T1IE    | OC1IE    | IC1IE    | INT0IE   | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE  | INT2IE  | T5IE    | T4IE   | OC4IE    | OC3IE    | _        |       | _        | _        | INT1IE   | CNIE    | CMIE     | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098 | _      | _       | PMPIE   | _       | _      | _        | OC5IE    | _        | IC5IE | IC4IE    | IC3IE    |          | -       | _        | SPI2IE   | SPF2IE   | 0000          |

| IEC3         | 009A | _      | RTCIE   | _       | _       | _      | _        | _        | _        |       | INT4IE   | INT3IE   |          |         | MI2C2IE  | SI2C2IE  | _        | 0000          |

| IEC4         | 009C | _      | _       | _       | _       | _      | _        | _        | _        | _     | _        | _        | _        | CRCIE   | U2ERIE   | U1ERIE   | _        | 0000          |

| IPC0         | 00A4 | _      | T1IP2   | T1IP1   | T1IP0   | _      | OC1IP2   | OC1IP1   | OC1IP0   |       | IC1IP2   | IC1IP1   | IC1IP0   | -       | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1         | 00A6 | —      | T2IP2   | T2IP1   | T2IP0   | —      | OC2IP2   | OC2IP1   | OC2IP0   | _     | IC2IP2   | IC2IP1   | IC2IP0   | _       | _        | _        | _        | 4440          |

| IPC2         | 00A8 | —      | U1RXIP2 | U1RXIP1 | U1RXIP0 | —      | SPI1IP2  | SPI1IP1  | SPI1IP0  | _     | SPF1IP2  | SPF1IP1  | SPF1IP0  | _       | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA | —      | _       | _       | _       | —      | _        | _        | _        | _     | AD1IP2   | AD1IP1   | AD1IP0   | _       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC | —      | CNIP2   | CNIP1   | CNIP0   | —      | CMIP2    | CMIP1    | CMIP0    | _     | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4444          |

| IPC5         | 00AE | —      | _       | _       | _       | —      | _        | _        | _        | _     | _        | _        | _        | _       | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC6         | 00B0 | _      | T4IP2   | T4IP1   | T4IP0   | —      | OC4IP2   | OC4IP1   | OC4IP0   | _     | OC3IP2   | OC3IP1   | OC3IP0   | —       | _        | _        | _        | 4440          |

| IPC7         | 00B2 | _      | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2  | U2RXIP1  | U2RXIP0  | _     | INT2IP2  | INT2IP1  | INT2IP0  | _       | T5IP2    | T5IP1    | T5IP0    | 4444          |

| IPC8         | 00B4 | _      | _       | _       | _       | _      | _        | _        | _        | _     | SPI2IP2  | SPI2IP1  | SPI2IP0  | _       | SPF2IP2  | SPF2IP1  | SPF2IP0  | 0044          |

| IPC9         | 00B6 | _      | IC5IP2  | IC5IP1  | IC5IP0  | _      | IC4IP2   | IC4IP1   | IC4IP0   | _     | IC3IP2   | IC3IP1   | IC3IP0   | _       | _        | _        | _        | 4440          |

| IPC10        | 00B8 | _      | _       | _       | _       | _      | _        | _        | _        | _     | OC5IP2   | OC5IP1   | OC5IP0   | _       | _        | _        | _        | 0040          |

| IPC11        | 00BA | -      |         | _       | -       | _      | -        |          | -        |       | PMPIP2   | PMPIP1   | PMPIP0   |         | —        |          | —        | 0040          |

| IPC12        | 00BC | _      | _       | _       | _       | _      | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 | _     | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | _       | _        | _        | _        | 0440          |

| IPC13        | 00BE | _      |         | —       | -       | —      | INT4IP2  | INT4IP1  | INT4IP0  |       | INT3IP2  | INT3IP1  | INT3IP0  |         | —        |          | -        | 0440          |

| IPC15        | 00C2 | _      |         | -       | -       | —      | RTCIP2   | RTCIP1   | RTCIP0   |       | —        | -        |          |         | -        |          | -        | 0400          |

| IPC16        | 00C4 | —      | CRCIP2  | CRCIP1  | CRCIP0  | —      | U2ERIP2  | U2ERIP1  | U2ERIP0  |       | U1ERIP2  | U1ERIP1  | U1ERIP0  | _       | —        |          | _        | 4440          |

| INTTREG      | 00E0 | CPUIRQ |         | VHOLD   | -       | ILR3   | ILR2     | ILR1     | ILR0     |       | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-1: SR: CPU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0             |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   | —   | _   | _   | —   | —   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R-0               | R/W-0            | R/W-0             | R/W-0            | R/W-0            |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- Note 1: See Register 3-1 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

- 2: The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- 3: The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### REGISTER 7-2: CORCON: CORE CONTROL REGISTER

| U-0     | U-0 | U-0           | U-0 | U-0                 | U-0                | U-0 | U-0   |

|---------|-----|---------------|-----|---------------------|--------------------|-----|-------|

| —       | —   | —             | —   | —                   | —                  | —   | —     |

| bit 15  |     |               |     |                     |                    |     | bit 8 |

|         |     |               |     |                     |                    |     |       |

| U-0     | U-0 | U-0           | U-0 | R/C-0               | R/W-0              | U-0 | U-0   |

| —       | —   | —             | —   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | —   | —     |

| bit 7   |     |               |     |                     |                    |     | bit 0 |

|         |     |               |     |                     |                    |     |       |

| Legend: |     | C = Clearable | bit |                     |                    |     |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

|                   |                  |                             |                    |

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: See Register 3-2 for the description of the remaining bit(s) that are not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| U-0          | R/W-1                                                                                     | R/W-0                                  | R/W-0            | U-0              | R/W-1            | R/W-0            | R/W-0            |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------|------------------|------------------|------------------|--|--|--|--|--|--|

|              | T1IP2                                                                                     | T1IP1                                  | T1IP0            | _                | OC1IP2           | OC1IP1           | OC1IP0           |  |  |  |  |  |  |

| bit 15       | ·                                                                                         | •                                      | ·                |                  |                  |                  | bit              |  |  |  |  |  |  |

|              |                                                                                           | DAMO                                   |                  |                  |                  | DAALO            |                  |  |  |  |  |  |  |

| U-0          | R/W-1<br>IC1IP2                                                                           | R/W-0<br>IC1IP1                        | R/W-0<br>IC1IP0  | U-0              | R/W-1<br>INT0IP2 | R/W-0<br>INT0IP1 | R/W-0<br>INT0IP0 |  |  |  |  |  |  |

| <br>bit 7    | ICTIFZ                                                                                    | ICTIFT                                 | ICTIFU           | —                | INTUFZ           | INTUFT           | bit              |  |  |  |  |  |  |

|              |                                                                                           |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

| Legend:      |                                                                                           |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

| R = Readab   |                                                                                           | W = Writable                           |                  | -                | mented bit, read | l as '0'         |                  |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                     | '1' = Bit is se                        | t                | '0' = Bit is cle | eared            | x = Bit is unkr  | nown             |  |  |  |  |  |  |

| bit 15       | Unimpleme                                                                                 | ented: Read as                         | ·0'              |                  |                  |                  |                  |  |  |  |  |  |  |

| bit 14-12    | -                                                                                         | Timer1 Interrup                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              |                                                                                           | upt is Priority 7                      |                  | y interrupt)     |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | 001 = Interr                                                                              | upt is Priority 1                      |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | 000 = Interr                                                                              | upt source is dis                      | sabled           |                  |                  |                  |                  |  |  |  |  |  |  |

| bit 11       | Unimpleme                                                                                 | ented: Read as                         | 0'               |                  |                  |                  |                  |  |  |  |  |  |  |

| bit 10-8     | <b>OC1IP&lt;2:0&gt;:</b> Output Compare Channel 1 Interrupt Priority bits                 |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>.</li> </ul> |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                       |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

| bit 7        |                                                                                           | upt source is dis<br>ented: Read as '  |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | -                                                                                         |                                        |                  | rrupt Drigrity h | vito             |                  |                  |  |  |  |  |  |  |

| bit 6-4      |                                                                                           | : Input Capture (<br>upt is Priority 7 |                  |                  | JIIS             |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        | (nighest phon    | ly interrupt)    |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         | untin Drievitud                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              |                                                                                           | upt is Priority 1<br>upt source is dis | sabled           |                  |                  |                  |                  |  |  |  |  |  |  |

| bit 3        |                                                                                           | nted: Read as                          |                  |                  |                  |                  |                  |  |  |  |  |  |  |

| bit 2-0      | INT0IP<2:0                                                                                | :> External Inter                      | rupt 0 Priority  | bits             |                  |                  |                  |  |  |  |  |  |  |

|              | 111 = Interr                                                                              | upt is Priority 7                      | (highest priorit | ty interrupt)    |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | •                                                                                         |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              |                                                                                           |                                        |                  |                  |                  |                  |                  |  |  |  |  |  |  |

|              | 001 = Interr                                                                              | upt is priority 1                      |                  |                  |                  |                  |                  |  |  |  |  |  |  |

# REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0                               | U-0                                  | U-0              | U-0             | U-0              | U-0                | U-0             | U-0   |  |  |  |  |  |  |

|-----------------------------------|--------------------------------------|------------------|-----------------|------------------|--------------------|-----------------|-------|--|--|--|--|--|--|

| _                                 |                                      | <u> </u>         |                 | <u> </u>         | <u> </u>           | <u> </u>        |       |  |  |  |  |  |  |

| bit 15                            |                                      |                  |                 |                  |                    |                 | bit 8 |  |  |  |  |  |  |

|                                   |                                      |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

| U-0                               | U-0                                  | R/W-0            | R/W-0           | R/W-0            | R/W-0              | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _                                 | —                                    | TUN5             | TUN4            | TUN3             | TUN2               | TUN1            | TUN0  |  |  |  |  |  |  |

| bit 7                             |                                      |                  |                 |                  |                    |                 | bit 0 |  |  |  |  |  |  |

|                                   |                                      |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

| Legend:                           |                                      |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

| R = Readable bit W = Writable bit |                                      |                  | bit             | U = Unimpler     | mented bit, read   | l as '0'        |       |  |  |  |  |  |  |

| -n = Value at POR                 |                                      | '1' = Bit is set |                 | '0' = Bit is cle | ared               | x = Bit is unkr | iown  |  |  |  |  |  |  |

|                                   |                                      |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

| bit 15-6                          | Unimplemen                           | ted: Read as '   | 0'              |                  |                    |                 |       |  |  |  |  |  |  |

| bit 5-0                           | TUN<5:0>: FRC Oscillator Tuning bits |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | 011111 <b>= Ma</b>                   | ximum frequer    | ncy deviation   |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | 011110 =                             |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | •                                    |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | •                                    |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | 000001 =                             |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   |                                      | nter frequency.  | oscillator is r | unning at facto  | ory calibrated fre | equency         |       |  |  |  |  |  |  |

|                                   | 111111 =                             |                  |                 | 9                | ,                  |                 |       |  |  |  |  |  |  |

|                                   | •                                    |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | •                                    |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | •                                    |                  |                 |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | 100001 =<br>100000 = Mi              | nimum frequen    | cy deviation    |                  |                    |                 |       |  |  |  |  |  |  |

|                                   | T00000 - MII                         | innun nequen     | cy ueviation    |                  |                    |                 |       |  |  |  |  |  |  |

#### **Input Capture Registers** 13.1

### REGISTER 13-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0   | R/W-0  | U-0                  | U-0                               | U-0      | U-0                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|--------|----------------------|-----------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —     | ICSIDL | _                    | —                                 | —        | —                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |        |                      |                                   |          |                                                                                                                              | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |        |                      |                                   |          |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R/W-0 | R/W-0  | R-0, HC              | R/W-0, HC                         | R/W-0    | R/W-0                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ICI1  | ICI0   | ICOV                 | ICBNE                             | ICM2     | ICM1                                                                                                                         | ICM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | •      | •                    | · ·                               |          | •                                                                                                                            | bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |        | — ICSIDL       R/W-0 | — ICSIDL —<br>R/W-0 R/W-0 R-0, HC | - ICSIDL | —         ICSIDL         —         —         —           R/W-0         R/W-0         R-0, HC         R/W-0, HC         R/W-0 | —         ICSIDL         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         =         Image: Missing is a first in the instand is a first in the |

| Legend:           | HC = Hardware Clearable bit |                                    |                    |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                              |

|-----------|---------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture x Module Stop in Idle Control bit                                                 |

|           | 1 = Input capture module will Halt in CPU Idle mode                                                     |

|           | 0 = Input capture module will continue to operate in CPU Idle mode                                      |

| bit 12-8  | Unimplemented: Read as '0'                                                                              |

| bit 7     | ICTMR: Input Capture x Timer Select bit <sup>(1)</sup>                                                  |

|           | 1 = TMR2 contents are captured on capture event                                                         |

|           | 0 = TMR3 contents are captured on capture event                                                         |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                  |

|           | 11 = Interrupt on every fourth capture event                                                            |

|           | 10 = Interrupt on every third capture event                                                             |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                   |

| bit 4     |                                                                                                         |

| DIL 4     | ICOV: Input Capture x Overflow Status Flag bit (read-only)<br>1 = Input capture overflow occurred       |

|           | 0 = No input capture overflow occurred                                                                  |

| bit 3     | <b>ICBNE:</b> Input Capture x Buffer Empty Status bit (read-only)                                       |

| Sit 0     | 1 = Input capture buffer is not empty, at least one more capture value can be read                      |

|           | 0 = Input capture buffer is empty                                                                       |

| bit 2-0   | ICM<2:0>: Input Capture x Mode Select bits                                                              |

|           | 111 = Input capture functions as an interrupt pin only when the device is in Sleep or Idle mode (rising |

|           | edge detect only, all other control bits are not applicable)                                            |

|           | 110 = Unused (module is disabled)                                                                       |

|           | 101 = Capture mode, every 16th rising edge<br>100 = Capture mode, every 4th rising edge                 |

|           | 011 = Capture mode, every rising edge                                                                   |

|           | 010 = Capture mode, every falling edge                                                                  |

|           | 001 = Capture mode, every edge (rising and falling); ICI<1:0> does not control interrupt generation     |

|           | for this mode                                                                                           |

|           | 000 = Input capture module is turned off                                                                |

| Note 1:   | Timer selections may vary. Refer to the specific device data sheet for details.                         |

To generate a single output pulse, the following steps are required (these steps assume the timer source is initially turned off, but this is not a requirement for the module operation):

- Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- 2. Calculate time to the rising edge of the output pulse relative to the TMRy start value (0000h).

- 3. Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 4. Write the values computed in Steps 2 and 3 above into the Compare register, OCxR, and the Secondary Compare register, OCxRS, respectively.

- 5. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS, the Secondary Compare register.

- Set the OCM bits to '100' and the OCTSEL (OCxCON<3>) bit to the desired timer source. The OCx pin state will now be driven low.

- 7. Set the TON (TyCON<15>) bit to '1', which enables the compare time base to count.

- 8. Upon the first match between TMRy and OCxR, the OCx pin will be driven high.

- 9. When the incrementing timer, TMRy, matches the Secondary Compare register, OCxRS, the second and trailing edge (high-to-low) of the pulse is driven onto the OCx pin. No additional pulses are driven onto the OCx pin and it remains at low. As a result of the second compare match event, the OCxIF interrupt flag bit is set which will result in an interrupt, if it is enabled, by setting the OCxIE bit. For further information on peripheral interrupts, refer to Section 7.0 "Interrupt Controller".

- 10. To initiate another single pulse output, change the Timer and Compare register settings, if needed, and then issue a write to set the OCM bits to '100'. Disabling and re-enabling of the timer, and clearing the TMRy register are not required, but may be advantageous for defining a pulse from a known event time boundary.

The output compare module does not have to be disabled after the falling edge of the output pulse. Another pulse can be initiated by rewriting the value of the OCxCON register.

# 14.3 Setup for Continuous Output Pulse Generation

When the OCM control bits (OCxCON<2:0>) are set to '101', the selected output compare channel initializes the OCx pin to the low state, and generates output pulses on each and every compare match event.

For the user to configure the module for the generation of a continuous stream of output pulses, the following steps are required (these steps assume the timer source is initially turned off, but this is not a requirement for the module operation):

- 1. Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- 2. Calculate the time to the rising edge of the output pulse relative to the TMRy start value (0000h).

- 3. Calculate the time to the falling edge of the pulse, based on the desired pulse width and the time to the rising edge of the pulse.

- 4. Write the values computed in Step 2 and 3 above, into the Compare register, OCxR, and the Secondary Compare register, OCxRS, respectively.

- 5. Set the Timer Period register, PRy, to a value, equal to or greater than, the value in OCxRS, the Secondary Compare register.

- Set the OCM bits to '101' and the OCTSEL bit to the desired timer source. The OCx pin state will now be driven low.

- Enable the compare time base by setting the TON (TyCON<15>) bit to '1'.

- 8. Upon the first match between TMRy and OCxR, the OCx pin will be driven high.

- 9. When the compare time base, TMRy, matches the Secondary Compare register, OCxRS, the second and trailing edge (high-to-low) of the pulse is driven onto the OCx pin.

- 10. As a result of the second compare match event, the OCxIF interrupt flag bit is set.

- When the compare time base and the value in its respective Period register match, the TMRy register resets to 0x0000 and resumes counting.

- 12. Steps 8 through 11 are repeated and a continuous stream of pulses is generated indefinitely. The OCxIF flag is set on each OCxRS-TMRy compare match event.

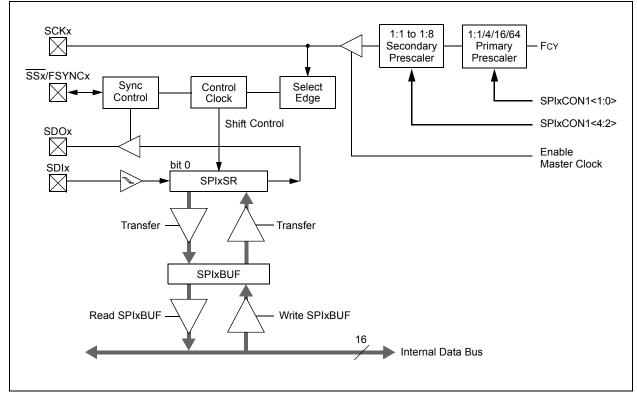

To set up the SPI module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 5. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 6. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- Clear the SPIxIF bit in the respective IFSx register.

- Set the SPIxIE bit in the respective IECx register.

- Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 8. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

### FIGURE 15-1: SPIX MODULE BLOCK DIAGRAM (STANDARD MODE)

Internal Data Bus

Read

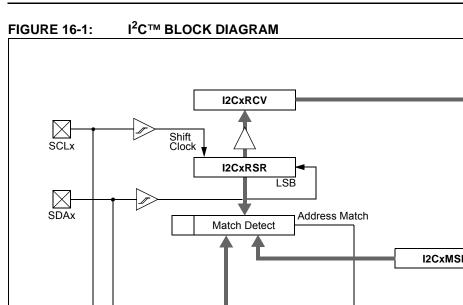

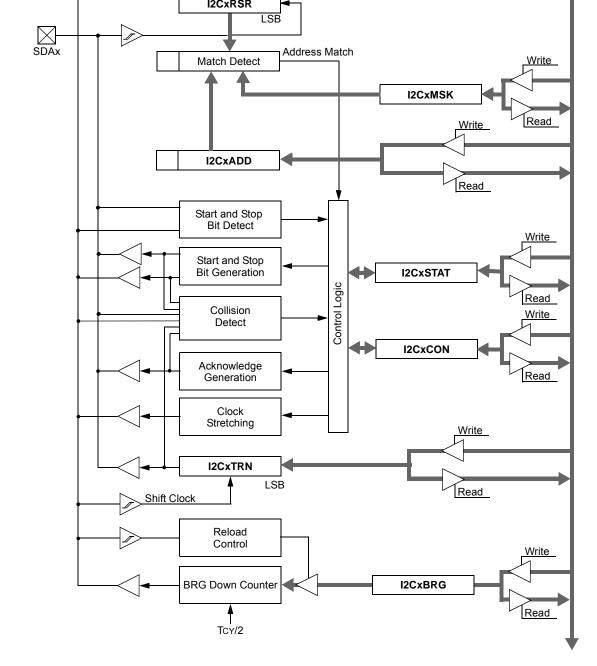

# REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ACKDT: Acknowledge Data bit (When operating as an I<sup>2</sup>C master; applicable during master receive.)</li> <li>Value that will be transmitted when the software initiates an Acknowledge sequence.</li> <li>1 = Sends NACK during Acknowledge</li> <li>0 = Sends ACK during Acknowledge</li> </ul>                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit</li> <li>(When operating as an I<sup>2</sup>C master; applicable during master receive.)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit.<br/>Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <ul> <li>RCEN: Receive Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                                                                  |

| bit 2 | <ul> <li>PEN: Stop Condition Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                                                                             |

| bit 1 | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                                                                    |

| bit 0 | <ul> <li>SEN: Start Condition Enable bit (when operating as an I<sup>2</sup>C master)</li> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                                         |

### REGISTER 19-6: WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0    | U-0    | U-0    | R/W-x  | R/W-x  | R/W-x  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | —      | —      | —      | WDAY2  | WDAY1  | WDAY0  |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

| —      | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| oit | 7 |  |

|-----|---|--|

|     |   |  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit; Contains a value from 0 to 6 |

| bit 7-6   | Unimplemented: Read as '0'                                                           |

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit; Contains a value from 0 to 2

bit 3-0 HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit; Contains a value from 0 to 9

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 19-7: MINSEC: MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| _      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15 Unimplemented: Read as '0'

bit 14-12 MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit; Contains a value from 0 to 5

- bit 11-8 MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit; Contains a value from 0 to 9 bit 7 Unimplemented: Read as '0'

- bit 6-4 SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit; Contains a value from 0 to 5

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit; Contains a value from 0 to 9

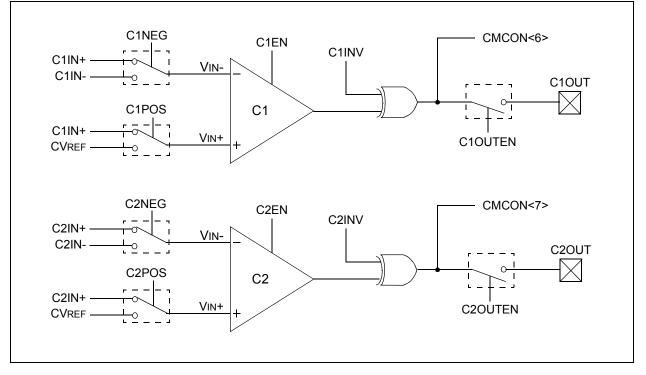

# 22.0 COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 19. "Comparator Module" (DS39710) in the "PIC24F Family Reference Manual" for more information. The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs, multiplexed with I/O pins, as well as the on-chip voltage reference. Block diagrams of the various comparator configurations are shown in Figure 22-1.

# FIGURE 22-1: COMPARATOR I/O OPERATING MODES

#### REGISTER 24-3: DEVID: DEVICE ID REGISTER

| U      | U | U | U | U | U | U | U      |

|--------|---|---|---|---|---|---|--------|

| —      | — | — | — | — | — | — | —      |

| bit 23 |   |   |   |   |   |   | bit 16 |

| U      | U | R      | R      | R      | R      | R      | R      |

|--------|---|--------|--------|--------|--------|--------|--------|

| _      | — | FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 |

| bit 15 |   |        |        |        |        |        | bit 8  |

| R      | R      | R    | R    | R    | R    | R    | R     |

|--------|--------|------|------|------|------|------|-------|

| FAMID1 | FAMID0 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7  |        |      |      |      |      |      | bit 0 |

| Legend:           | x = Bit is unknown    |                                    |                    |  |

|-------------------|-----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | PO = Program Once bit | U = Unimplemented bit, read as '1' |                    |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 23-14 Unimplemented: Read as '0'

bit 13-6 **FAMID<7:0>:** Device Family Identifier bits 00010000 = PIC24FJ128GA010 family

bit 5-0 **DEV<5:0>:** Individual Device Identifier bits 000101 = PIC24FJ64GA006 000110 = PIC24FJ96GA006

000111 = PIC24FJ128GA006

001000 = PIC24FJ64GA008

001001 = PIC24FJ96GA008

001010 = PIC24FJ128GA008

001011 = PIC24FJ64GA010

001100 = PIC24FJ96GA010

001101 = PIC24FJ128GA010

### 24.4 JTAG Interface

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 33. "Programming and Diagnostics" (DS39716) in the "PIC24F Family Reference Manual" for more information.

PIC24FJ128GA010 family devices implement a JTAG interface, which supports boundary scan device testing as well as In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

Refer to the Microchip web site (www.microchip.com) for JTAG support files and additional information.

## 24.5 Program Verification and Code Protection

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 33. "Programming and Diagnostics" (DS39716) in the "PIC24F Family Reference Manual" for more information.

For all devices in the PIC24FJ128GA010 family, the on-chip program memory space is treated as a single block. Code protection for this block is controlled by one Configuration bit, GCP (Flash Configuration Word 1<13>. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

Write protection is controlled by the GWRP bit (Flash Configuration Word 1<12>. When GWRP is programmed to '0', internal write and erase operations to the program memory are blocked.

### 24.5.1 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against inadvertent or unwanted changes, or reads in two ways. The primary protection method is the same as that of the shadow registers, which contain a complimentary value that is constantly compared with the actual value. To safeguard against unpredictable events, Configuration bit changes resulting from individual cell level disruptions (such as ESD events) will cause a parity error and trigger a device Configuration Word Mismatch Reset.

The data for the Configuration registers is derived from the Flash Configuration Words in program memory. As a consequence, when the GCP bit is set, the source data for the device configuration is also protected.

### 24.6 In-Circuit Serial Programming

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 33. "Programming and Diagnostics" (DS39716) in the "PIC24F Family Reference Manual" for more information.

PIC24FJ128GA010 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGCx) and data (PGDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 24.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the In-Circuit Debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the EMUCx (Emulation/Debug Clock) and EMUDx (Emulation/Debug Data) pins.

To use the In-Circuit Debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGCx, PGDx and the EMUDx/EMUCx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

| DC CHARACTERISTICS |                        |              | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |                     |               |  |  |

|--------------------|------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|---------------|--|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Мах          | Units                                                                                                                                            | Conditions         |                     |               |  |  |

| Idle Current (     | (IIDLE): Core (        | Off, Clock C | On Base Curre                                                                                                                                    | ent <sup>(2)</sup> |                     |               |  |  |

| DC40               | 0.7                    | 2            | mA                                                                                                                                               | -40°C              |                     |               |  |  |

| DC40a              | 0.7                    | 2            | mA                                                                                                                                               | +25°C              | 2.5V <sup>(3)</sup> |               |  |  |

| DC40b              | 0.7                    | 2            | mA                                                                                                                                               | +85°C              |                     | 1 MIPS        |  |  |

| DC40d              | 0.7                    | 2            | mA                                                                                                                                               | -40°C              |                     | T MIFS        |  |  |

| DC40e              | 0.7                    | 2            | mA                                                                                                                                               | +25°C              | 3.6V <sup>(4)</sup> |               |  |  |

| DC40f              | 0.7                    | 2            | mA                                                                                                                                               | +85°C              |                     |               |  |  |

| DC43               | 2.1                    | 4            | mA                                                                                                                                               | -40°C              |                     | – 4 MIPS      |  |  |

| DC43a              | 2.1                    | 4            | mA                                                                                                                                               | +25°C              | 2.5V <sup>(3)</sup> |               |  |  |

| DC43b              | 2.1                    | 4            | mA                                                                                                                                               | +85°C              |                     |               |  |  |

| DC43d              | 2.1                    | 4            | mA                                                                                                                                               | -40°C              |                     |               |  |  |

| DC43e              | 2.1                    | 4            | mA                                                                                                                                               | +25°C              | 3.6∨ <b>(4)</b>     |               |  |  |

| DC43f              | 2.1                    | 4            | mA                                                                                                                                               | +85°C              |                     |               |  |  |

| DC47               | 6.8                    | 8            | mA                                                                                                                                               | -40°C              |                     | - 16 MIPS     |  |  |

| DC47a              | 6.8                    | 8            | mA                                                                                                                                               | +25°C              | 2.5V <sup>(3)</sup> |               |  |  |

| DC47b              | 6.8                    | 8            | mA                                                                                                                                               | +85°C              |                     |               |  |  |

| DC47c              | 6.8                    | 8            | mA                                                                                                                                               | -40°C              |                     |               |  |  |

| DC47d              | 6.8                    | 8            | mA                                                                                                                                               | +25°C              | 3.6V <sup>(4)</sup> |               |  |  |

| DC47e              | 6.8                    | 8            | mA                                                                                                                                               | +85°C              |                     |               |  |  |

| DC51               | 70                     | 150          | μΑ                                                                                                                                               | -40°C              |                     |               |  |  |

| DC51a              | 100                    | 200          | μΑ                                                                                                                                               | +25°C              | 2.5∨ <sup>(3)</sup> |               |  |  |

| DC51b              | 150                    | 400          | μΑ                                                                                                                                               | +85°C              |                     | LPRC (31 kHz) |  |  |

| DC51d              | 70                     | 150          | μΑ                                                                                                                                               | -40°C              |                     |               |  |  |

| DC51e              | 100                    | 200          | μΑ                                                                                                                                               | +25°C              | 3.6∨ <sup>(4)</sup> |               |  |  |

| DC51f              | 150                    | 400          | μA                                                                                                                                               | +85°C              |                     |               |  |  |

### TABLE 27-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IIDLE current is measured with core off, clock on, PMD bits set and all modules turned off.

3: On-chip voltage regulator is disabled (ENVREG tied to Vss).

4: On-chip voltage regulator is enabled (ENVREG tied to VDD).

| DC CHARACTERISTICS |        |                                                                       | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |                       |    |                                                                                                                                                  |  |

|--------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|