Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 69                                                                            |

| Program Memory Size        | 96KB (32K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-TQFP                                                                       |

| Supplier Device Package    | 80-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj96ga008-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and busses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 **Program Address Space**

The program address memory space of PIC24FJ128GA010 family devices is 4M instructions. The space is addressable by a 24-bit value derived from

either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces**".

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ128GA010 family of devices are shown in Figure 4-1.

#### FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ128GA010 FAMILY DEVICES

|                            | PIC24FJ64GA                                        | PIC24FJ96GA                                        | PIC24FJ128GA                         |                               |

|----------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------------------|-------------------------------|

| $\mathbf{I}$               | GOTO Instruction                                   | GOTO Instruction                                   | GOTO Instruction                     | 000000h                       |

|                            | Reset Address                                      | Reset Address                                      | Reset Address                        | 000002h<br>000004h            |

|                            | Interrupt Vector Table                             | Interrupt Vector Table                             | Interrupt Vector Table               |                               |

|                            | Reserved                                           | Reserved                                           | Reserved                             | 0000FEh<br>000100h<br>000104h |

|                            | Alternate Vector Table                             | Alternate Vector Table                             | Alternate Vector Table               | 0001FEh                       |

| User Memory Space          | User Flash<br>Program Memory<br>(22K instructions) | User Flash<br>Program Memory<br>(32K instructions) | User Flash                           | 000200h                       |

| Ŝ                          | Flash Config Words                                 | `                                                  | Program Memory<br>(44K instructions) | 00ABFEh                       |

| lory                       |                                                    |                                                    | (1111100000000)                      | 00AC00h                       |

| lem                        |                                                    | Flash Config Words                                 |                                      | 00FFFEh<br>010000h            |

| ≥<br>⊡                     |                                                    |                                                    |                                      |                               |

| ns.                        |                                                    |                                                    | Flash Config Words                   | 0157FEh<br>015800h            |

|                            | Unimplemented                                      |                                                    |                                      | 0100001                       |

|                            | (Read '0's)                                        | Unimplemented                                      |                                      |                               |

|                            | (,                                                 | (Read '0's)                                        | Unimplemented                        |                               |

|                            |                                                    |                                                    | (Read '0's)                          |                               |

|                            |                                                    |                                                    | (1.000 0.0)                          |                               |

|                            |                                                    |                                                    |                                      | 7FFFFEh                       |

| -                          |                                                    |                                                    |                                      | 800000h                       |

| ace                        | Reserved                                           | Reserved                                           | Reserved                             |                               |

| y Sp                       | Device Configuration                               | Device Configuration                               | Device Configuration                 | F7FFFEh<br>F80000h            |

| i mo                       | Registers                                          | Registers                                          | Registers                            | _F8000Eh                      |

| Contiguration Memory Space | Reserved                                           | Reserved                                           | Reserved                             | F80010h                       |

|                            | DEVID (2)                                          | DEVID (2)                                          | DEVID (2)                            | FEFFFEh<br>FF0000h<br>FFFFFEh |

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

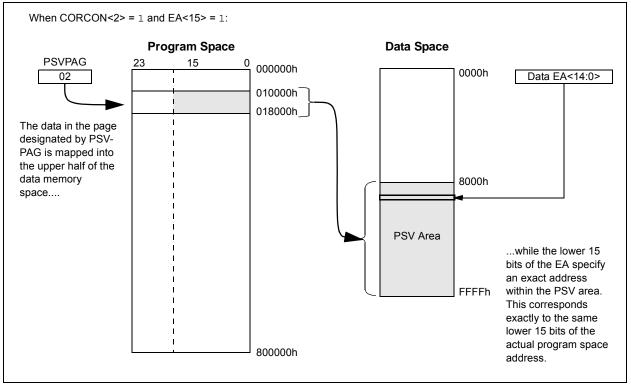

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and Program Space Visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 4. "Program Memory" (DS39715) in the "PIC24F Family Reference Manual" for more information.

The PIC24FJ128GA010 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the specified VDD range.

Flash memory can be programmed in four ways:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- 2. Run-Time Self-Programming (RTSP)

- 3. JTAG

- 4. Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ128GA010 family device to be serially programmed while in the end application circuit. This is simply done with two lines for Programming Clock and Programming Data (which are named PGCx and PGDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user may write program memory data in blocks of 64 instructions (192 bytes) at a time, and erase program memory in blocks of 512 instructions (1536 bytes) at a time.

### 5.1 Table Instructions and Flash Programming

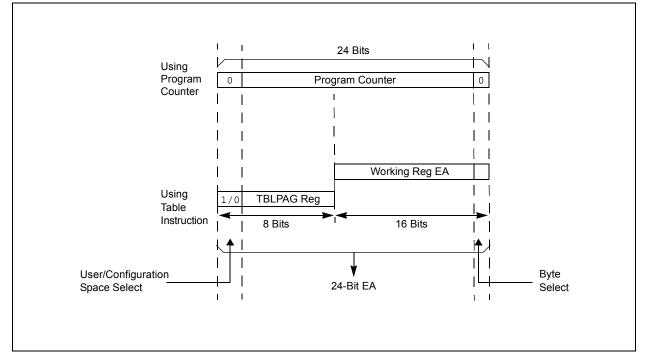

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

© 2005-2012 Microchip Technology Inc.

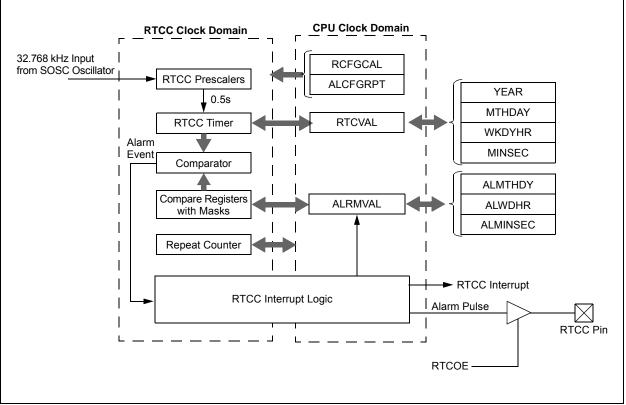

# 19.0 REAL-TIME CLOCK AND **CALENDAR (RTCC)**

This data sheet summarizes the features of Note: this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS39696) in the "PIC24F Family Reference Manual" for more information.

The Real-Time Clock and Calendar hardware module has the following features:

**RTCC BLOCK DIAGRAM**

- · Time: Hours, Minutes and Seconds

- 24-Hour Format (Military Time)

**FIGURE 19-1:**

- · Calendar: Weekday, Date, Month and Year

- · Alarm Configurable

- Year Range: 2000 to 2099

- Leap Year Correction

- · BCD Format for Compact Firmware

- · Optimized for Low-Power Operation

- · User Calibration with Auto-Adjust

- · Calibration Range: ±2.64 Seconds Error per Month

- Requirements: External 32.768 kHz Clock Crystal

- · Alarm Pulse or Seconds Clock Output on RTCC Pin

### REGISTER 19-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

bit 7-0 CAL<7:0>: RTC Drift Calibration bits

- 01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute

- ... 01111111 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute

- 00000000 = No adjustment

...

111111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute

10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute

- **Note 1:** The RCFGCAL Reset value is dependent on the type of Reset.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

#### REGISTER 19-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0           | U-0   | U-0              | U-0 | U-0               | U-0             | U-0                     | U-0                   |

|---------------|-------|------------------|-----|-------------------|-----------------|-------------------------|-----------------------|

|               | —     |                  | _   | —                 | —               | _                       | —                     |

| bit 15        |       |                  |     |                   |                 |                         | bit 8                 |

|               |       |                  |     |                   |                 |                         |                       |

| U-0           | U-0   | U-0              | U-0 | U-0               | U-0             | R/W-0                   | R/W-0                 |

| —             | —     | —                | _   | —                 | —               | RTSECSEL <sup>(1)</sup> | PMPTTL <sup>(2)</sup> |

| bit 7         |       |                  |     |                   |                 |                         | bit 0                 |

|               |       |                  |     |                   |                 |                         |                       |

| Legend:       |       |                  |     |                   |                 |                         |                       |

| R = Readable  | e bit | W = Writable b   | it  | U = Unimplem      | nented bit, rea | d as '0'                |                       |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is clea | ared            | x = Bit is unknow       | vn                    |

|               |       |                  |     |                   |                 |                         | ,                     |

bit 15-2 Unimplemented: Read as '0'

| bit 1 | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup>                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = RTCC seconds clock is selected for the RTCC pin</li> <li>0 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |

| bit 0 | PMPTTL: PMP Module TTL Input Buffer Select bit <sup>(2)</sup>                                                                      |

|       | 1 = PMP module uses TTL input buffers                                                                                              |

|       | 0 = PMP module uses Schmitt input buffers                                                                                          |

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>) bit needs to be set.

**2:** Refer to Table 1-2 for affected PMP inputs.

NOTES:

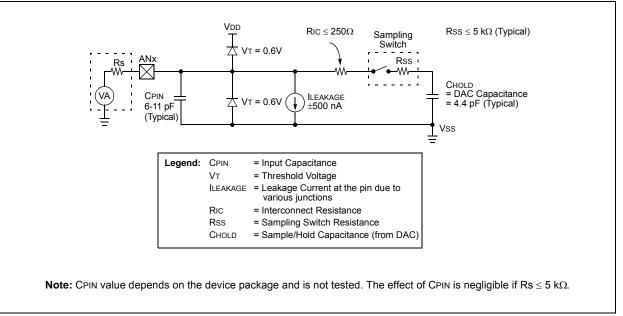

# EQUATION 21-1: A/D CONVERSION CLOCK PERIOD<sup>(1)</sup>

TAD = TCY(ADCS + 1) $ADCS = \frac{TAD}{TCY} - 1$

**Note 1:** Based on TCY = TOSC \* 2; Doze mode and PLL are disabled.

### FIGURE 21-2: 10-BIT A/D CONVERTER ANALOG INPUT MODEL

### REGISTER 24-1: FLASH CONFIGURATION WORD 1

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| r-x    | R/PO-1                | R/PO-1 | R/PO-1 | R/PO-1 | r-1 | U-1 | R/PO-1 |

|--------|-----------------------|--------|--------|--------|-----|-----|--------|

| r      | JTAGEN <sup>(1)</sup> | GCP    | GWRP   | DEBUG  | r   | _   | ICS    |

| bit 15 |                       |        |        |        |     |     | bit 8  |

| R/PO-1 | R/PO-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|--------|-----|--------|--------|--------|--------|--------|

| FWDTEN | WINDIS | —   | FWPSA  | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 |

| bit 7  |        |     |        |        |        |        | bit 0  |

| Legend:                     | x = Bit is unknown                                       | r = Reserved     |                      |

|-----------------------------|----------------------------------------------------------|------------------|----------------------|

| R = Readable bit            | PO = Program Once bit U = Unimplemented bit, read as '0' |                  |                      |

| -n = Value when device is u | inprogrammed                                             | '1' = Bit is set | '0' = Bit is cleared |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | Reserved: Program as '0'. Read value is unknown.                                                                                |

| bit 14    | JTAGEN: JTAG Port Enable bit <sup>(1)</sup>                                                                                     |

|           | <ul> <li>1 = JTAG port is enabled</li> <li>0 = JTAG port is disabled</li> </ul>                                                 |

| bit 13    | GCP: General Segment Program Memory Code Protection bit                                                                         |

|           | <ul> <li>1 = Code protection is disabled</li> <li>0 = Code protection is enabled for the entire program memory space</li> </ul> |

| bit 12    | GWRP: General Segment Code Flash Write Protection bit                                                                           |

|           | <ol> <li>Writes to program memory are allowed</li> <li>Writes to program memory are disabled</li> </ol>                         |

| bit 11    | DEBUG: Background Debugger Enable bit                                                                                           |

|           | <ul> <li>1 = Device resets into Operational mode</li> <li>0 = Device resets into Debug mode</li> </ul>                          |

| bit 10    | Reserved: Program as '1'                                                                                                        |

| bit 9     | Unimplemented: Read as '1'                                                                                                      |

| bit 8     | ICS: Emulator Pin Placement Select bit                                                                                          |

|           | <ul> <li>1 = Emulator/debugger uses EMUC2/EMUD2</li> <li>0 = Emulator/debugger uses EMUC1/EMUD1</li> </ul>                      |

| bit 7     | FWDTEN: Watchdog Timer Enable bit                                                                                               |

|           | <ul> <li>1 = Watchdog Timer is enabled</li> <li>0 = Watchdog Timer is disabled</li> </ul>                                       |

| bit 6     | WINDIS: Windowed Watchdog Timer Disable bit                                                                                     |

|           | <ul> <li>1 = Standard Watchdog Timer is enabled</li> <li>0 = Windowed Watchdog Timer is enabled; FWDTEN must be '1'</li> </ul>  |

| bit 5     | Unimplemented: Read as '1'                                                                                                      |

| bit 4     | FWPSA: WDT Prescaler Ratio Select bit                                                                                           |

|           | 1 = Prescaler ratio of 1:128                                                                                                    |

|           | 0 = Prescaler ratio of 1:32                                                                                                     |

| Note 1:   | JTAGEN bit can not be modified using JTAG programming. It can only change using In-Circuit Seri                                 |

Note 1: JTAGEN bit can not be modified using JTAG programming. It can only change using In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

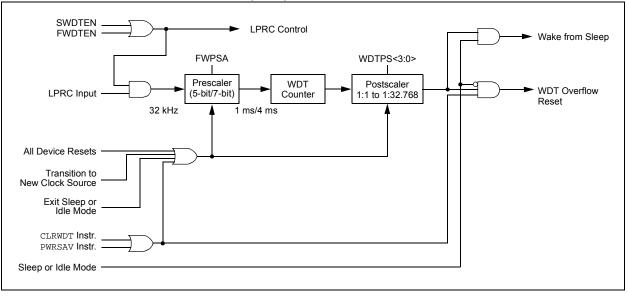

### 24.3 Watchdog Timer (WDT)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 9. "Watchdog Timer (WDT)" (DS39697) in the "PIC24F Family Reference Manual" for more information.

For PIC24FJ128GA010 family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPS<3:0> Configuration bits (Flash Configuration Word 1<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranging from 1 ms to 131 seconds, can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake-up and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3:2>) will need to be cleared in software after the device wakes up.

The WDT Flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### 24.3.1 CONTROL REGISTER

The WDT is enabled or disabled by the FWDTEN Configuration bit. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disables the WDT during non-critical segments for maximum power savings.

#### FIGURE 24-2: WATCHDOG TIMER (WDT) BLOCK DIAGRAM

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|------------------|----------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                                | 2             | 2              | None                     |

|                      | GOTO   | Wn               | Go to Indirect                               | 1             | 2              | None                     |

| INC                  | INC    | f                | f = f + 1                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | f,WREG           | WREG = f + 1                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                  | 1             | 1              | C, DC, N, OV, Z          |

| INC2                 | INC2   | f                | f = f + 2                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | f,WREG           | WREG = f + 2                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | Ws,Wd            | Wd = Ws + 2                                  | 1             | 1              | C, DC, N, OV, Z          |

| IOR                  | IOR    | f                | f = f .IOR. WREG                             | 1             | 1              | N, Z                     |

|                      | IOR    | f,WREG           | WREG = f .IOR. WREG                          | 1             | 1              | N, Z                     |

|                      | IOR    | #lit10,Wn        | Wd = lit10 .IOR. Wd                          | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,Ws,Wd         | Wd = Wb .IOR. Ws                             | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,#lit5,Wd      | Wd = Wb .IOR. lit5                           | 1             | 1              | N, Z                     |

| LNK                  | LNK    | #lit14           | Link Frame Pointer                           | 1             | 1              | None                     |

| LSR                  | LSR    | f                | f = Logical Right Shift f                    | 1             | 1              | C, N, OV, Z              |

| 2010                 | LSR    | f,WREG           | WREG = Logical Right Shift f                 | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Ws,Wd            | Wite S = Logical Right Shift Ws              | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Wb,Wns,Wnd       | Wrd = Logical Right Shift Wb by Wrs          | 1             | 1              | N, Z                     |

|                      |        |                  | Wind = Logical Right Shift Wb by Wils        | 1             | 1              | N, Z                     |

| MOM                  | LSR    | Wb,#lit5,Wnd     | Move f to Wn                                 | 1             | 1              | None                     |

| MOV                  | MOV    | f,Wn             |                                              | 1             | 1              |                          |

|                      | MOV    | [Wns+Slit10],Wnd | Move [Wns+Slit10] to Wnd                     |               |                | None                     |

|                      | MOV    | f                | Move f to f                                  | 1             | 1              | N, Z                     |

|                      | MOV    | f,WREG           | Move f to WREG                               | 1             | 1              | N, Z                     |

|                      | MOV    | #lit16,Wn        | Move 16-Bit Literal to Wn                    | 1             | 1              | None                     |

| -                    | MOV.b  | #lit8,Wn         | Move 8-Bit Literal to Wn                     | 1             | 1              | None                     |

|                      | MOV    | Wn,f             | Move Wn to f                                 | 1             | 1              | None                     |

|                      | MOV    | Wns,[Wns+Slit10] | Move Wns to [Wns+Slit10]                     | 1             | 1              |                          |

|                      | MOV    | Wso,Wdo          | Move Ws to Wd                                | 1             | 1              | None                     |

|                      | MOV    | WREG, f          | Move WREG to f                               | 1             | 1              | N, Z                     |

|                      | MOV.D  | Wns,Wd           | Move Double from W(ns):W(ns+1) to Wd         | 1             | 2              | None                     |

|                      | MOV.D  | Ws,Wnd           | Move Double from Ws to W(nd+1):W(nd)         | 1             | 2              | None                     |

| MUL                  | MUL.SS | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Signed(Ws)       | 1             | 1              | None                     |

|                      | MUL.SU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws)     | 1             | 1              | None                     |

|                      | MUL.US | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Signed(Ws)     | 1             | 1              | None                     |

|                      | MUL.UU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(Ws)   | 1             | 1              | None                     |

|                      | MUL.SU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(lit5)   | 1             | 1              | None                     |

|                      | MUL.UU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(lit5) | 1             | 1              | None                     |

|                      | MUL    | f                | W3:W2 = f * WREG                             | 1             | 1              | None                     |

| NEG                  | NEG    | f                | $f = \overline{f} + 1$                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | f,WREG           | WREG = $\overline{f}$ + 1                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | Ws,Wd            | $Wd = \overline{Ws} + 1$                     | 1             | 1              | C, DC, N, OV, Z          |

| NOP                  | NOP    |                  | No Operation                                 | 1             | 1              | None                     |

| -                    | NOPR   |                  | No Operation                                 | 1             | 1              | None                     |

| POP                  | POP    | f                | Pop f from Top-of-Stack (TOS)                | 1             | 1              | None                     |

|                      | POP    | Wdo              | Pop from Top-of-Stack (TOS) to Wdo           | 1             | 1              | None                     |

|                      | POP.D  | Wnd              | Pop from Top-of-Stack (TOS) to W(nd):W(nd+1) | 1             | 2              | None                     |

|                      | POP.S  | mitt             | Pop Shadow Registers                         | 1             | 1              | All                      |

| PUSH                 | PUSH   | f                | Push f to Top-of-Stack (TOS)                 | 1             | 1              | None                     |

| ruan                 | PUSH   |                  | Push Wso to Top-of-Stack (TOS)               | 1             | 1              | None                     |

|                      |        | Wso              | ,                                            |               | 2              |                          |

|                      | PUSH.D | Wns              | Push W(ns):W(ns+1) to Top-of-Stack (TOS)     | 1             | ۷              | None                     |

#### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| DC CHARACTERISTICS |        |                                                                       | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |                       |       |                                                                                                                                                  |  |

|--------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                                        | Min.                                                                                                                                            | Typ <sup>(1)</sup> | Max.                  | Units | Conditions                                                                                                                                       |  |

| DI60a              | licl   | Input Low Injection Current                                           | 0                                                                                                                                               | _                  | <sub>-5</sub> (2,5)   | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB11, SOSCI, SOSCO, D+,<br>D-, VUSB and VBUS                                             |  |

| DI60b              | ІІСН   | Input High Injection Current                                          | 0                                                                                                                                               | _                  | +5 <sup>(3,4,5)</sup> | mA    | All pins except VDD, Vss,<br>AVDD, AVss, MCLR, VCAP,<br>RB11, SOSCI, SOSCO, D+,<br>D-, VUSB and VBUS, and all<br>5V tolerant pins <sup>(4)</sup> |  |

| DI60c              | ΣΙΙCT  | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | <sub>-20</sub> (6)                                                                                                                              | _                  | +20 <sup>(6)</sup>    | mA    | Absolute instantaneous sum<br>of all $\pm$ input injection cur-<br>rents from all I/O pins<br>(   IICL +   IICH   ) $\leq \Sigma$ IICT           |  |

### TABLE 27-10: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Characterized but not tested.

**3:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

4: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

**5:** Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

6: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

### **TABLE 27-13: COMPARATOR SPECIFICATIONS**

| Param<br>No. | Symbol | Characteristic                             | Min | Тур | Max | Units | Comments |

|--------------|--------|--------------------------------------------|-----|-----|-----|-------|----------|

| D300         | VIOFF  | Input Offset Voltage*                      | _   | 10  | 30  | mV    |          |

| D301         | VICM   | Input Common Mode Voltage*                 | 0   | _   | Vdd | V     |          |

| D302         | CMRR   | Common Mode Rejection<br>Ratio*            | 55  | —   | —   | dB    |          |

| 300          | TRESP  | Response Time* <sup>(1)</sup>              | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid* |     | _   | 10  | μs    |          |

Parameters are characterized but not tested.

Note 1: Response time is measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

### **TABLE 27-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS**

| Operatin     | <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                              |        |     |            |       |          |

|--------------|----------------------------------------------------------------------------------------------|------------------------------|--------|-----|------------|-------|----------|

| Param<br>No. | Symbol                                                                                       | Characteristic               | Min    | Тур | Мах        | Units | Comments |

| VRD310       | CVRES                                                                                        | Resolution                   | VDD/24 | _   | Vdd/32     | LSb   |          |

| VRD311       | CVRAA                                                                                        | Absolute Accuracy            | _      | _   | AVDD – 1.5 | LSb   |          |

| VRD312       | CVRur                                                                                        | Unit Resistor Value (R)      | _      | 2k  | _          | Ω     |          |

| VR310        | TSET                                                                                         | Settling Time <sup>(1)</sup> | _      | —   | 10         | μS    |          |

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

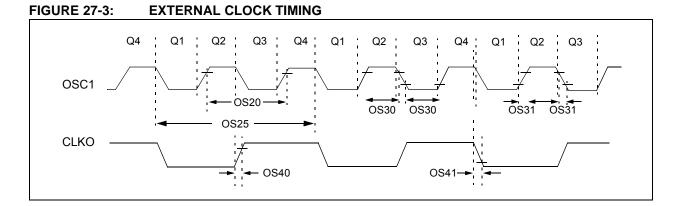

### TABLE 27-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |                     |                          |                                          |  |

|--------------------|---------------|-------------------------------------------------------------------------|------------------------------------------------------|--------------------|---------------------|--------------------------|------------------------------------------|--|

| Param<br>No.       | Sym           | Characteristic                                                          | Min                                                  | Typ <sup>(1)</sup> | Мах                 | Units                    | Conditions                               |  |

| OS10               | Fosc          | External CLKI Frequency<br>(external clocks allowed<br>only in EC mode) | DC<br>3                                              |                    | 32<br>8             | MHz<br>MHz               | EC mode<br>ECPLL mode                    |  |

|                    |               | Oscillator Frequency                                                    | 3.5<br>3.5<br>10<br>31                               |                    | 10<br>8<br>32<br>33 | MHz<br>MHz<br>MHz<br>kHz | XT mode<br>XTPLL mode<br>HS mode<br>SOSC |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                           | —                                                    | —                  | —                   | —                        | See Parameter OS10<br>for Fosc value     |  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                   | 62.5                                                 | _                  | DC                  | ns                       |                                          |  |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                            | 0.45 x Tosc                                          | —                  | —                   | ns                       | EC mode                                  |  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                           | —                                                    | —                  | 20                  | ns                       | EC mode                                  |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                           | —                                                    | 6                  | 10                  | ns                       |                                          |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                           | —                                                    | 6                  | 10                  | ns                       |                                          |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

**3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

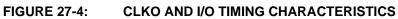

| TABLE 27-21: | <b>CLKO AND I/O TIMING REQUIREMENTS</b> |

|--------------|-----------------------------------------|

|--------------|-----------------------------------------|

| AC CHARACTERISTICS |                    |                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |            |

|--------------------|--------------------|---------------------------------------|------------------------------------------------------|--------------------|-----|-------|------------|

| Param<br>No.       | Sym Characteristic |                                       | Min                                                  | Typ <sup>(1)</sup> | Мах | Units | Conditions |

| DO31               | TioR               | Port Output Rise Time                 | _                                                    | 10                 | 25  | ns    |            |

| DO32               | TIOF               | Port Output Fall Time                 | _                                                    | 10                 | 25  | ns    |            |

| DI35               | Tinp               | INTx Pin High or Low<br>Time (output) | 20                                                   | —                  | —   | ns    |            |

| DI40               | Trbp               | CNx High or Low Time<br>(input)       | 2                                                    | —                  | —   | Тсү   |            |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

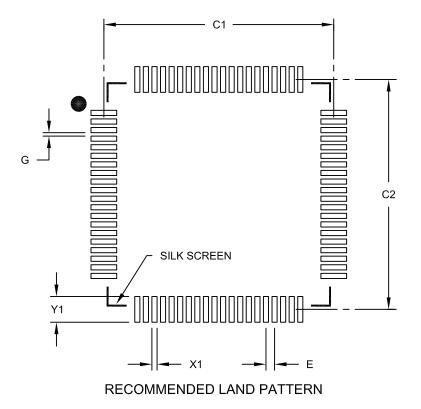

80-Lead Plastic Thin Quad Flatpack (PT) - 12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |       |      |  |  |

|--------------------------|-------------|----------|-------|------|--|--|

| Dimension Limits         |             | MIN      | NOM   | MAX  |  |  |

| Contact Pitch E          |             | 0.50 BSC |       |      |  |  |

| Contact Pad Spacing      | C1          |          | 13.40 |      |  |  |

| Contact Pad Spacing      | C2          |          | 13.40 |      |  |  |

| Contact Pad Width (X80)  | X1          |          |       | 0.30 |  |  |

| Contact Pad Length (X80) | Y1          |          |       | 1.50 |  |  |

| Distance Between Pads    | G           | 0.20     |       |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2092B

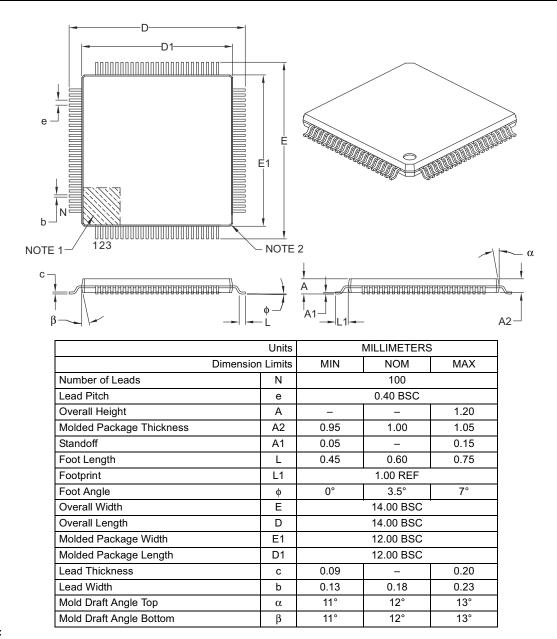

#### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

NOTES:

## INDEX

| Α                                       |     |

|-----------------------------------------|-----|

| A/D                                     |     |

| Conversion Timing Requirements          |     |

| Module Specifications                   |     |

| AC                                      |     |

| Characteristics                         | 227 |

| Load Conditions                         | 227 |

| Temperature and Voltage Specifications  |     |

| Alternate Interrupt Vector Table (AIVT) | 63  |

| Arithmetic Logic Unit (ALU)             | 30  |

| Assembler                               |     |

| MPASM Assembler                         | 214 |

### В

| Block Diagrams                                      |   |

|-----------------------------------------------------|---|

| 10-Bit High-Speed A/D Converter                     | ) |

| 16-Bit Timer1 Module111                             |   |

| 8-Bit Multiplexed Address and Data Application 162  | 2 |

| Accessing Program Memory with                       |   |

| Table Instructions                                  | 3 |

| Addressable Parallel Slave Port                     |   |

| Comparator I/O Operating Modes                      | 9 |

| Comparator Voltage Reference                        |   |

| Connections for On-Chip Voltage Regulator           |   |

| Device Clock                                        | 7 |

| I <sup>2</sup> C                                    | 3 |

| Input Capture119                                    | 9 |

| LCD Control, Byte Mode 162                          | 2 |

| Legacy Parallel Slave Port                          |   |

| Master Mode, Demultiplexed Addressing               | ) |

| Master Mode, Fully Multiplexed Addressing           |   |

| Master Mode, Partially Multiplexed Addressing 161   | 1 |

| Multiplexed Addressing Application                  | 1 |

| Output Compare Module                               | 1 |

| Parallel EEPROM (Up to 15-Bit Address, 16-Bit Data) |   |

| 162                                                 |   |

| Parallel EEPROM (Up to 15-Bit Address, 8-Bit Data)  |   |

| 162                                                 |   |

| Partially Multiplexed Addressing Application        |   |

| PIC24F CPU Core26                                   |   |

| PIC24FJ128GA010 Family (General)10                  |   |

| PMP Module153                                       |   |

| Program Space Visibility Operation49                |   |

| Reset System57                                      | 7 |

| RTCC 163                                            |   |

| Shared Port Structure107                            |   |

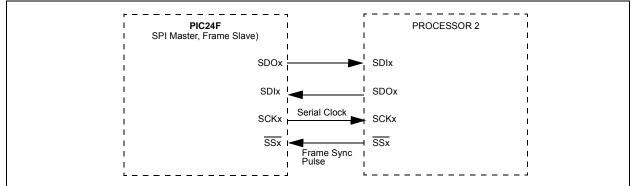

| SPI Master, Frame Master Connection                 |   |

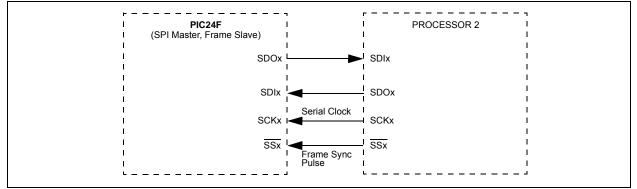

| SPI Master, Frame Slave Connection                  | 5 |

| SPI Master/Slave Connection (Enhanced               |   |

| Buffer Modes) 134                                   |   |

| SPI Master/Slave Connection (Standard Mode) 134     |   |

| SPI Slave, Frame Master Connection                  |   |

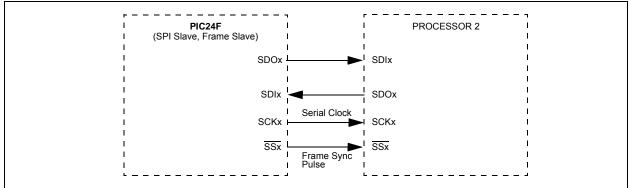

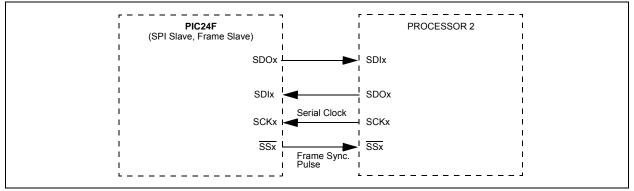

| SPI Slave, Frame Slave Connection135                |   |

| SPIx Module (Enhanced Mode)129                      |   |

| SPIx Module (Standard Mode)128                      |   |

| Timer2 and Timer4 (16-Bit Synchronous)115           |   |

| Timer2/3 and Timer4/5 (32-Bit)114                   |   |

| Timer3 and Timer5 (16-Bit Synchronous)115           |   |

| UARTx                                               |   |

| Watchdog Timer (WDT) 202                            | 2 |

# С

| C Compilers                                 |

|---------------------------------------------|

| MPLAB C18                                   |

| Clock Switching                             |

| Enabling                                    |

| Operation 103                               |

| Oscillator Sequence 103                     |

| Code Examples                               |

| Basic Code Sequence for Clock Switching 104 |

| Erasing a Program Memory Block              |

| Initiating a Programming Sequence           |

| Loading Write Buffers                       |

| Port Write/Read 108                         |

| Programming a Single Word of Flash          |

| Program Memory56                            |

| PWRSAV Instruction Syntax 105               |

| Comparator Module                           |

| Comparator Voltage Reference                |

| Configuring 193                             |

| Configuration Bits 195                      |

| Configuration Register Protection           |

| Core Features                               |

| 16-Bit Architecture7                        |

| Easy Migration8                             |

| Oscillator Options, Features 7              |

| PIC24FJ128GA010 Family Devices              |

| Power-Saving Technology7                    |

| CPU                                         |

| Control Registers                           |

| Programmer's Model 27                       |

| CPU Clocking Scheme                         |

| CRC                                         |

| Example Setup 175                           |

| Operation in Power Save Modes 177           |

| Overview                                    |

| Registers 175                               |

| User Interface 176                          |

| Customer Change Notification Service        |

| Customer Notification Service               |

| Customer Support                            |

| CVRR                                        |

| CVrsrc                                      |

| Ρ                                           |

# Da

| ata Memory                    |    |

|-------------------------------|----|

| Address Space                 | 33 |

| Width                         | 33 |

| Memory Map for PIC24F128GA010 |    |

| Family Devices                | 33 |

| Near Data Space               | 34 |

| Organization and Alignment    | 34 |

| SFR Space                     | 34 |

| Software Stack                | 46 |

|                               |    |

| OSCTUN (FRC Oscillator Tune)102     |

|-------------------------------------|

| PADCFG1 (Pad Configuration Control) |

| PMADDR (Parallel Port Address)      |

| PMAEN (Parallel Port Enable)        |

| PMCON (Parallel Port Control)       |

| PMMODE (Parallel Port Mode)156      |

| PMSTAT (Parallel Port Status)       |

| RCFGCAL (RTCC Calibration           |

| and Configuration)165               |

| RCON (Reset Control)                |

| SPIxCON1 (SPIx Control 1)132        |

| SPIxCON2 (SPIx Control 2)           |

| SPIxSTAT (SPIx Status and Control)  |

| SR (CPU STATUS)                     |

| T1CON (Timer1 Control)112           |

| TxCON (Timer2/4 Control)116         |

| TyCON (Timer3/5 Control)117         |

| UxMODE (UARTx Mode)148              |

| UxSTA (UARTx Status and Control)150 |

| WKDYHR (Weekday and Hours Value)169 |

| YEAR (Year Value)168                |

| Registers Map                       |

| CPU Core                            |

| Reset Sequence                      |

| Resets                              |

| Clock Source Selection              |

| Device Times59                      |

| Revision History                    |

| RTCC                                |

| Alarm172                            |

| Configuring172                      |

| Interrupt172                        |

| ALRMVAL Register Mappings 170       |

| Calibration                         |

| Control Registers165                |

| Module Registers                    |

| Mapping                             |

| RTCVAL Register Mapping168          |

|                                     |

# S

| Serial Peripheral Interface (SPI)1     | 27  |

|----------------------------------------|-----|

| Software Simulator (MPLAB SIM)2        | 15  |

| Software Stack Pointer, Frame Pointer  |     |

| CALL Stack Frame                       | 46  |

| Special Features1                      | 95  |

| Code Protection1                       | 95  |

| Flexible Configuration1                | 95  |

| In-Circuit Emulation1                  | 95  |

| In-Circuit Serial Programming (ICSP)1  | 95  |

| JTAG Boundary Scan Interface1          | 95  |

| Watchdog Timer (WDT)1                  | 95  |

| Special Function Register Reset States | 61  |

| Symbols Used in Opcode Descriptions    | .06 |

# Т

| •                                                      |

|--------------------------------------------------------|

| Table of Contents 5                                    |

| Timer1 Module 111                                      |

| Timer2/3 Module 113                                    |

| Timer4/5 Module                                        |

| Timing Diagrams                                        |

| CLKO and I/O 230                                       |

| External Clock                                         |

| Timing Requirements                                    |

| Capacitive Loading on Output Pin 227                   |

| CLKO and I/O                                           |

| External Clock                                         |

| Timing Specifications                                  |

| Internal RC Oscillator                                 |

| Internal RC Oscillator Accuracy 229                    |

| PLL Clock                                              |

|                                                        |

| U                                                      |

| UARTx                                                  |

| Baud Rate Generator (BRG) 146                          |

| Break and Sync Transmit Sequence 147                   |

| Infrared Support 147                                   |

| IrDA                                                   |

| Built-in Encoder and Decoder 147                       |

| External Support, Clock Output 147                     |

| Operation of UxCTS and UxRTS Control Pins 147          |

| Receiving in                                           |

| 8-Bit or 9-Bit Data Mode 147                           |

| Transmitting                                           |

| 8-Bit Data Mode147                                     |

| Transmitting in                                        |

| 9-Bit Data Mode147                                     |

| Universal Asynchronous Receiver Transmitter (UART) 145 |

| V                                                      |

| VDDCORE/VCAP Pin                                       |

| W                                                      |

| Watchdog Timer (WDT)                                   |

| Control Register                                       |

| Programming Considerations                             |

| WWW Address                                            |

|                                                        |

WWW, On-Line Support ...... 6