Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 84                                                                            |

| Program Memory Size        | 96KB (32K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

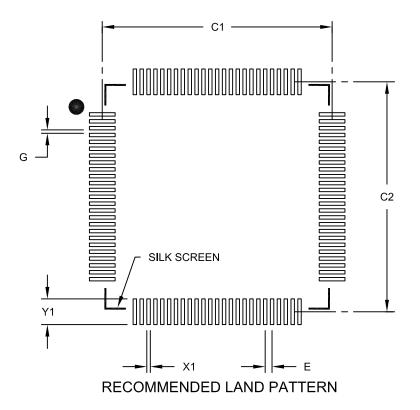

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj96ga010-i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| U-0                  | U-0                                      | U-0                                                                                                                                               | U-0            | U-0                | U-0                | U-0                | R/W-0          |  |  |  |  |

|----------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|--------------------|--------------------|----------------|--|--|--|--|

| _                    | _                                        | _                                                                                                                                                 | _              | _                  | —                  | _                  | DC             |  |  |  |  |

| bit 15               |                                          |                                                                                                                                                   |                |                    |                    |                    | bit 8          |  |  |  |  |

|                      |                                          |                                                                                                                                                   |                |                    |                    |                    |                |  |  |  |  |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>                                                                                                                              | R-0            | R/W-0              | R/W-0              | R/W-0              | R/W-0          |  |  |  |  |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>                      | IPL0 <sup>(2)</sup>                                                                                                                               | RA             | Ν                  | OV                 | Z                  | С              |  |  |  |  |

| bit 7                | •                                        |                                                                                                                                                   |                | •                  | •                  |                    | bit (          |  |  |  |  |

|                      |                                          |                                                                                                                                                   |                |                    |                    |                    |                |  |  |  |  |

| Legend:              |                                          |                                                                                                                                                   |                |                    |                    |                    |                |  |  |  |  |

| R = Readabl          | le bit                                   | W = Writable                                                                                                                                      | bit            | U = Unimpler       | mented bit, read   | d as '0'           |                |  |  |  |  |

| -n = Value at        | t POR                                    | '1' = Bit is set                                                                                                                                  |                | '0' = Bit is cle   | eared              | x = Bit is unk     | nown           |  |  |  |  |

|                      |                                          |                                                                                                                                                   |                |                    |                    |                    |                |  |  |  |  |

| bit 15-9             | Unimplemen                               | ted: Read as '                                                                                                                                    | 0'             |                    |                    |                    |                |  |  |  |  |

| bit 8                | DC: ALU Hali                             | f Carry/Borrow                                                                                                                                    | bit            |                    |                    |                    |                |  |  |  |  |

|                      |                                          |                                                                                                                                                   | low-order bit  | (for byte-sized of | data) or 8th low-  | -order bit (for wo | ord-sized data |  |  |  |  |

|                      |                                          | sult occurred                                                                                                                                     | th or 8th low- | order bit of the   | result has occu    | rred               |                |  |  |  |  |

| bit 7-5              | •                                        | PU Interrupt Pri                                                                                                                                  |                |                    |                    | iicu               |                |  |  |  |  |

|                      |                                          |                                                                                                                                                   |                |                    | ots are disabled   | 1                  |                |  |  |  |  |

|                      |                                          | <ul><li>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled</li><li>110 = CPU Interrupt Priority Level is 6 (14)</li></ul> |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          | 101 = CPU Interrupt Priority Level is 5 (13)                                                                                                      |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          | 100 = CPU Interrupt Priority Level is 4 (12)                                                                                                      |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          | 011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)                                                      |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          | nterrupt Priority                                                                                                                                 |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          | nterrupt Priority                                                                                                                                 |                |                    |                    |                    |                |  |  |  |  |

| bit 4                |                                          | Loop Active bit                                                                                                                                   |                | ,<br>,             |                    |                    |                |  |  |  |  |

|                      |                                          | oop in progres                                                                                                                                    |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          | 0 = REPEAT loop not in progress                                                                                                                   |                |                    |                    |                    |                |  |  |  |  |

| bit 3                | N: ALU Nega                              | itive bit                                                                                                                                         |                |                    |                    |                    |                |  |  |  |  |

|                      | 1 = Result wa                            | •                                                                                                                                                 |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          | as non-negative                                                                                                                                   | e (zero or pos | itive)             |                    |                    |                |  |  |  |  |

| bit 2                | OV: ALU Ove                              |                                                                                                                                                   |                |                    |                    |                    |                |  |  |  |  |

|                      |                                          |                                                                                                                                                   | • ·            | nplement) arithi   | metic in this arit | thmetic operation  | on             |  |  |  |  |

| hit 1                |                                          | ow has occurre                                                                                                                                    | u              |                    |                    |                    |                |  |  |  |  |

| bit 1                | Z: ALU Zero I                            |                                                                                                                                                   | cts the 7 hit  | has set it at sou  | me time in the p   | naet               |                |  |  |  |  |

|                      |                                          |                                                                                                                                                   |                |                    | as cleared it (i.e |                    | esult)         |  |  |  |  |

| bit 0                | C: ALU Carry                             |                                                                                                                                                   | . ,            |                    |                    | ,                  | ,              |  |  |  |  |

| bit 0                |                                          |                                                                                                                                                   | st Significant | bit of the result  | occurred           |                    |                |  |  |  |  |

|                      | •                                        |                                                                                                                                                   | •              | t bit of the resu  |                    |                    |                |  |  |  |  |

| Noto 1. T            | ho IDI Statua hita                       | are read only                                                                                                                                     |                |                    | 15>) - 1           |                    |                |  |  |  |  |

|                      | he IPL Status bits<br>he IPL bits are co | -                                                                                                                                                 |                | -                  |                    |                    | riority Loval  |  |  |  |  |

|                      |                                          |                                                                                                                                                   |                |                    |                    |                    | Honty Level.   |  |  |  |  |

The value in parentheses indicates the IPL when IPL3 = 1.

| TABLE 4-  | -3: C | CPU CO | RE REG             | ISTERS | MAP    |        |        |       |            |               |            |            |             |              |              |       |       |               |

|-----------|-------|--------|--------------------|--------|--------|--------|--------|-------|------------|---------------|------------|------------|-------------|--------------|--------------|-------|-------|---------------|

| File Name | Addr  | Bit 15 | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7         | Bit 6      | Bit 5      | Bit 4       | Bit 3        | Bit 2        | Bit 1 | Bit 0 | All<br>Resets |

| WREG0     | 0000  |        | •                  |        |        |        | •      |       | Working F  | Register 0    | •          |            | -           |              | ·            |       | ·     | 0000          |

| WREG1     | 0002  |        |                    |        |        |        |        |       | Working F  | Register 1    |            |            |             |              |              |       |       | 0000          |

| WREG2     | 0004  |        |                    |        |        |        |        |       | Working F  | Register 2    |            |            |             |              |              |       |       | 0000          |

| WREG3     | 0006  |        |                    |        |        |        |        |       | Working F  | Register 3    |            |            |             |              |              |       |       | 0000          |

| WREG4     | 0008  |        | Working Register 4 |        |        |        |        |       |            |               |            |            | 0000        |              |              |       |       |               |

| WREG5     | 000A  |        | Working Register 5 |        |        |        |        |       |            |               |            |            | 0000        |              |              |       |       |               |

| WREG6     | 000C  |        |                    |        |        |        |        |       | Working F  | Register 6    |            |            |             |              |              |       |       | 0000          |

| WREG7     | 000E  |        |                    |        |        |        |        |       | Working F  | Register 7    |            |            |             |              |              |       |       | 0000          |

| WREG8     | 0010  |        |                    |        |        |        |        |       | Working F  | Register 8    |            |            |             |              |              |       |       | 0000          |

| WREG9     | 0012  |        | Working Register 9 |        |        |        |        |       |            |               |            |            | 0000        |              |              |       |       |               |

| WREG10    | 0014  |        |                    |        |        |        |        |       | Working R  | egister 10    |            |            |             |              |              |       |       | 0000          |

| WREG11    | 0016  |        |                    |        |        |        |        |       | Working R  | egister 11    |            |            |             |              |              |       |       | 0000          |

| WREG12    | 0018  |        |                    |        |        |        |        |       | Working R  | egister 12    |            |            |             |              |              |       |       | 0000          |

| WREG13    | 001A  |        |                    |        |        |        |        |       | Working R  | egister 13    |            |            |             |              |              |       |       | 0000          |

| WREG14    | 001C  |        |                    |        |        |        |        |       | Working R  | egister 14    |            |            |             |              |              |       |       | 0000          |

| WREG15    | 001E  |        |                    |        |        |        |        |       | Working R  | egister 15    |            |            |             |              |              |       |       | 0800          |

| SPLIM     | 0020  |        |                    |        |        |        |        |       | Stack Poi  | nter Limit    |            |            |             |              |              |       |       | xxxx          |

| PCL       | 002E  |        |                    |        |        |        |        | Pr    | ogram Cour | ter Low Wo    | ord        |            |             |              |              |       |       | 0000          |

| PCH       | 0030  | —      | _                  | —      | —      | —      | —      | —     | —          |               |            | Pi         | rogram Cou  | unter High B | yte          |       |       | 0000          |

| TBLPAG    | 0032  | _      | _                  | —      | _      | _      | _      | _     | —          |               |            | Та         | ible Page A | ddress Poir  | nter         |       |       | 0000          |

| PSVPAG    | 0034  | _      | _                  | _      | _      | _      | _      | _     | _          |               | F          | Program Me | mory Visibi | lity Page Ac | Idress Point | ter   |       | 0000          |

| RCOUNT    | 0036  |        |                    |        |        |        |        |       | Repeat Loo | op Counter    |            |            |             |              |              |       |       | xxxx          |

| SR        | 0042  | _      | _                  | _      | _      | _      | _      | _     | DC         | IPL2          | IPL1       | IPL0       | RA          | Ν            | OV           | Z     | С     | 0000          |

| CORCON    | 0044  | _      | _                  | —      | _      | _      | _      | _     | —          | _             | _          | _          | —           | IPL3         | PSV          | —     | —     | 0000          |

| DISICNT   | 0052  | _      | _                  |        |        |        |        |       | [          | Disable Inter | rupts Coun | ter        |             |              |              |       |       | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Clock Source          | SYSRST Delay                                                                                                                                                                                         | System Clock<br>Delay                                                                                                                                                                                                                                                                                                                                                                                       | FSCM<br>Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EC, FRC, FRCDIV, LPRC | TPOR + TSTARTUP + TRST                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1, 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ECPLL, FRCPLL         | TPOR + TSTARTUP + TRST                                                                                                                                                                               | TLOCK                                                                                                                                                                                                                                                                                                                                                                                                       | TFSCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1, 2, 3, 5, 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XT, HS, SOSC          | TPOR + TSTARTUP + TRST                                                                                                                                                                               | Тоѕт                                                                                                                                                                                                                                                                                                                                                                                                        | TFSCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1, 2, 3, 4, 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XTPLL, HSPLL          | TPOR + TSTARTUP + TRST                                                                                                                                                                               | TOST + TLOCK                                                                                                                                                                                                                                                                                                                                                                                                | TFSCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1, 2, 3, 4, 5, 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EC, FRC, FRCDIV, LPRC | TSTARTUP + TRST                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ECPLL, FRCPLL         | TSTARTUP + TRST                                                                                                                                                                                      | TLOCK                                                                                                                                                                                                                                                                                                                                                                                                       | TFSCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2, 3, 5, 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XT, HS, SOSC          | TSTARTUP + TRST                                                                                                                                                                                      | Tost                                                                                                                                                                                                                                                                                                                                                                                                        | TFSCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2, 3, 4, 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| XTPLL, HSPLL          | TSTARTUP + TRST                                                                                                                                                                                      | TOST + TLOCK                                                                                                                                                                                                                                                                                                                                                                                                | TFSCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2, 3, 4, 5, 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Any Clock             | Trst                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Any Clock             | Trst                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Any Clock             | Trst                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Any Clock             | Trst                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Any Clock             | Trst                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Any Clock             | Trst                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | EC, FRC, FRCDIV, LPRC<br>ECPLL, FRCPLL<br>XT, HS, SOSC<br>XTPLL, HSPLL<br>EC, FRC, FRCDIV, LPRC<br>ECPLL, FRCPLL<br>XT, HS, SOSC<br>XTPLL, HSPLL<br>Any Clock<br>Any Clock<br>Any Clock<br>Any Clock | EC, FRC, FRCDIV, LPRCTPOR + TSTARTUP + TRSTECPLL, FRCPLLTPOR + TSTARTUP + TRSTXT, HS, SOSCTPOR + TSTARTUP + TRSTXTPLL, HSPLLTPOR + TSTARTUP + TRSTEC, FRC, FRCDIV, LPRCTSTARTUP + TRSTECPLL, FRCPLLTSTARTUP + TRSTXTPLL, HSPLLTSTARTUP + TRSTXTPLL, HSPLLTSTARTUP + TRSTXTPLL, HSPLLTSTARTUP + TRSTAny ClockTRSTAny ClockTRSTAny ClockTRSTAny ClockTRSTAny ClockTRSTAny ClockTRSTAny ClockTRSTAny ClockTRST | Clock SourceSYSKST DelayDelayEC, FRC, FRCDIV, LPRCTPOR + TSTARTUP + TRST—ECPLL, FRCPLLTPOR + TSTARTUP + TRSTTLOCKXT, HS, SOSCTPOR + TSTARTUP + TRSTTOSTXTPLL, HSPLLTPOR + TSTARTUP + TRSTTOST + TLOCKEC, FRC, FRCDIV, LPRCTSTARTUP + TRST—ECPLL, FRCPLLTSTARTUP + TRSTTLOCKXT, HS, SOSCTSTARTUP + TRSTTOSTXTPLL, HSPLLTSTARTUP + TRSTTOSTXTPLL, HSPLLTSTARTUP + TRSTTOSTAny ClockTRST—Any ClockTRST—Any ClockTRST—Any ClockTRST—Any ClockTRST—Any ClockTRST—Any ClockTRST—Any ClockTRST—Any ClockTRST— | Clock SourceSYSRS I DelayDelayDelayEC, FRC, FRCDIV, LPRCTPOR + TSTARTUP + TRST——ECPLL, FRCPLLTPOR + TSTARTUP + TRSTTLOCKTFSCMXT, HS, SOSCTPOR + TSTARTUP + TRSTTOSTTFSCMXTPLL, HSPLLTPOR + TSTARTUP + TRSTTOST + TLOCKTFSCMEC, FRC, FRCDIV, LPRCTSTARTUP + TRSTTOST + TLOCKTFSCMXT, HS, SOSCTSTARTUP + TRSTTLOCKTFSCMXT, HS, SOSCTSTARTUP + TRSTTOSTTFSCMXT, HS, SOSCTSTARTUP + TRSTTOSTTFSCMXTPLL, HSPLLTSTARTUP + TRSTTOST + TLOCKTFSCMAny ClockTRST——Any ClockTRST——Any ClockTRST——Any ClockTRST——Any ClockTRST——Any ClockTRST——Any ClockTRST—— |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay (10  $\mu$ s nominal).

**2:** TSTARTUP = TVREG (10 μs nominal) if the on-chip regulator is enabled or TPWRT (64 ms nominal) if an on-chip regulator is disabled.

**3:** TRST = Internal state Reset time (20 μs nominal).

**4:** TOST = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

5: TLOCK = PLL lock time.

6: TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

| R/W-0        | R-0                                | U-0              | U-0             | U-0              | U-0              | U-0                | U-0    |

|--------------|------------------------------------|------------------|-----------------|------------------|------------------|--------------------|--------|

| ALTIVT       | DISI                               | _                | _               | —                |                  | _                  | _      |

| bit 15       |                                    |                  |                 |                  |                  |                    | bit 8  |

|              |                                    |                  |                 |                  |                  |                    |        |

| U-0          | U-0                                | U-0              | R/W-0           | R/W-0            | R/W-0            | R/W-0              | R/W-0  |

| —            | —                                  | —                | INT4EP          | INT3EP           | INT2EP           | INT1EP             | INT0EP |

| bit 7        |                                    |                  |                 |                  |                  |                    | bit C  |

|              |                                    |                  |                 |                  |                  |                    |        |

| Legend:      |                                    |                  |                 |                  |                  | <i>(</i> <b>-)</b> |        |

| R = Readab   |                                    | W = Writable     |                 | •                | nented bit, read |                    |        |

| -n = Value a | t POR                              | '1' = Bit is se  | t               | '0' = Bit is cle | ared             | x = Bit is unkn    | own    |

| bit 15       |                                    | la Altarpata li  | atorrupt Vootor | Tabla bit        |                  |                    |        |

|              | 1 = Use altern                     |                  | nterrupt Vector | Table bit        |                  |                    |        |

|              | 0 = Use stand                      |                  |                 |                  |                  |                    |        |

| bit 14       | DISI: DISI In                      | · · ·            |                 |                  |                  |                    |        |

|              | 1 = DISI inst                      | ruction is activ | /e              |                  |                  |                    |        |

|              | 0 = DISI is n                      | ot active        |                 |                  |                  |                    |        |

| bit 13-5     | Unimplemen                         |                  |                 |                  |                  |                    |        |

| bit 4        |                                    | •                | •               | Polarity Select  | bit              |                    |        |

|              | 1 = Interrupt c<br>0 = Interrupt c |                  |                 |                  |                  |                    |        |

| bit 3        | INT3EP: Exte                       | rnal Interrupt   | 3 Edge Detect   | Polarity Select  | bit              |                    |        |

|              | 1 = Interrupt of                   | •                | •               |                  |                  |                    |        |

|              | 0 = Interrupt o                    | •                |                 |                  |                  |                    |        |

| bit 2        |                                    | •                | •               | Polarity Select  | bit              |                    |        |

|              | 1 = Interrupt o<br>0 = Interrupt o |                  |                 |                  |                  |                    |        |

| bit 1        | •                                  | •                | -               | Polarity Select  | bit              |                    |        |

|              | 1 = Interrupt o                    |                  |                 | 5                |                  |                    |        |

|              | 0 = Interrupt o                    | on positive ed   | ge              |                  |                  |                    |        |

| bit 0        |                                    | •                | •               | Polarity Select  | bit              |                    |        |

|              | 1 = Interrupt o                    |                  |                 |                  |                  |                    |        |

|              | 0 = Interrupt o                    | on positive edg  | ge              |                  |                  |                    |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

|               | _                             | _                                                          | -                                 |                  |                  |                 |                                                 |  |  |  |  |

|---------------|-------------------------------|------------------------------------------------------------|-----------------------------------|------------------|------------------|-----------------|-------------------------------------------------|--|--|--|--|

| U-0           | U-0                           | U-0                                                        | U-0                               | U-0              | R/W-1            | R/W-0           | R/W-0                                           |  |  |  |  |

| _             | _                             | _                                                          | _                                 | _                | MI2C2IP2         | MI2C2IP1        | MI2C2IP0                                        |  |  |  |  |

| bit 15        |                               |                                                            | •                                 | •                |                  |                 | bit                                             |  |  |  |  |

|               |                               |                                                            |                                   |                  |                  |                 |                                                 |  |  |  |  |

| U-0           | R/W-1                         | R/W-0                                                      | R/W-0                             | U-0              | U-0              | U-0             | U-0                                             |  |  |  |  |

| —             | SI2C2IP2                      | SI2C2IP1                                                   | SI2C2IP0                          | _                | —                | —               | —                                               |  |  |  |  |

| bit 7         |                               |                                                            |                                   |                  |                  |                 | bit                                             |  |  |  |  |

|               |                               |                                                            |                                   |                  |                  |                 |                                                 |  |  |  |  |

| Legend:       |                               |                                                            |                                   |                  |                  |                 |                                                 |  |  |  |  |

| R = Readable  | e bit                         | W = Writable                                               | bit                               | U = Unimple      | mented bit, read | d as '0'        | MI2C2IP1 MI2C2IP0   bit 8   U-0   —   —   bit 0 |  |  |  |  |

| -n = Value at | POR                           | '1' = Bit is set                                           |                                   | '0' = Bit is cle | eared            | x = Bit is unkr | nown                                            |  |  |  |  |

|               | •<br>•<br>001 = Interru       | pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis |                                   | y interrupt)     |                  |                 |                                                 |  |  |  |  |

| bit 7         |                               | ited: Read as '                                            |                                   |                  |                  |                 |                                                 |  |  |  |  |

| bit 6-4       | SI2C2IP<2:0:<br>111 = Interru | >: Slave I2C2 E<br>pt is Priority 7 (                      | Event Interrup<br>highest priorit | •                |                  |                 |                                                 |  |  |  |  |

| bit 3-0       | Unimplemen                    | ted: Read as '                                             | 0'                                |                  |                  |                 |                                                 |  |  |  |  |

|               |                               |                                                            |                                   |                  |                  |                 |                                                 |  |  |  |  |

### 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features of |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | this group of PIC24F devices. It is not    |  |  |  |  |  |  |  |  |

|       | intended to be a comprehensive reference   |  |  |  |  |  |  |  |  |

|       | source. Refer to Section 6. "Oscillator"   |  |  |  |  |  |  |  |  |

|       | (DS39700) in the "PIC24F Family            |  |  |  |  |  |  |  |  |

|       | Reference Manual" for more information.    |  |  |  |  |  |  |  |  |

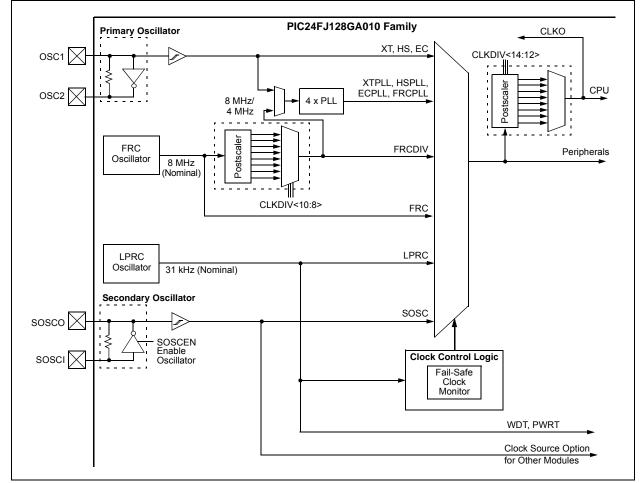

The oscillator system for PIC24FJ128GA010 family devices has the following features:

• A total of four external and internal oscillator options as clock sources, providing 11 different clock modes

- On-chip 4x PLL to boost internal operating frequency on select internal and external oscillator sources

- Software-controllable switching between various clock sources

- Software-controllable postscaler for selective clocking of CPU for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

A simplified diagram of the oscillator system is shown in Figure 8-1.

#### FIGURE 8-1: PIC24FJ128GA010 FAMILY CLOCK DIAGRAM

### 10.3 Input Change Notification

The input change notification function of the I/O ports allows the PIC24FJ128GA010 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 22 external signals (CN0 through CN21) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

When the internal pull-up is selected, the pin pulls up to VDD - 0.7V (typical). Make sure that there is no external pull-up source when the internal pull-ups are enabled, as the voltage difference can cause a current path.

**Note:** Pull-ups on Change Notification (CN) pins should always be disabled whenever the port pin is configured as a digital output.

NOTES:

| R/W-0         | U-0                                                                                                   | R/W-0                       | U-0            | U-0              | U-0              | U-0             | U-0 |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------|-----------------------------|----------------|------------------|------------------|-----------------|-----|--|--|--|--|

| TON           |                                                                                                       | TSIDL                       | —              |                  | _                | _               | _   |  |  |  |  |

| bit 15        |                                                                                                       |                             |                |                  |                  |                 | bit |  |  |  |  |

|               |                                                                                                       |                             |                |                  |                  |                 |     |  |  |  |  |

| U-0           | R/W-0                                                                                                 | R/W-0                       | R/W-0          | U-0              | R/W-0            | R/W-0           | U-0 |  |  |  |  |

| —             | TGATE                                                                                                 | TCKPS1                      | TCKPS0         | —                | TSYNC            | TCS             | —   |  |  |  |  |

| bit 7         |                                                                                                       |                             |                |                  |                  |                 | bit |  |  |  |  |

| Legend:       |                                                                                                       |                             |                |                  |                  |                 |     |  |  |  |  |

| R = Readable  | e bit                                                                                                 | W = Writable                | bit            | U = Unimple      | mented bit, read | d as '0'        |     |  |  |  |  |

| -n = Value at | POR                                                                                                   | '1' = Bit is set            |                | '0' = Bit is cle |                  | x = Bit is unkn | own |  |  |  |  |

|               |                                                                                                       |                             |                |                  |                  |                 |     |  |  |  |  |

| bit 15        | TON: Timer1                                                                                           | On bit                      |                |                  |                  |                 |     |  |  |  |  |

|               | 1 = Starts 16                                                                                         |                             |                |                  |                  |                 |     |  |  |  |  |

|               | 0 = Stops 16                                                                                          | -bit Timer1                 |                |                  |                  |                 |     |  |  |  |  |

| bit 14        | Unimplemen                                                                                            | nted: Read as '             | 0'             |                  |                  |                 |     |  |  |  |  |

| bit 13        | <b>TSIDL:</b> Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode |                             |                |                  |                  |                 |     |  |  |  |  |

|               |                                                                                                       |                             |                |                  | Idle mode        |                 |     |  |  |  |  |

|               | 0 = Continues module operation in Idle mode                                                           |                             |                |                  |                  |                 |     |  |  |  |  |

| bit 12-7      | Unimplemented: Read as '0'                                                                            |                             |                |                  |                  |                 |     |  |  |  |  |

| bit 6         | TGATE: Timer1 Gated Time Accumulation Enable bit                                                      |                             |                |                  |                  |                 |     |  |  |  |  |

|               | <u>When TCS = 1:</u><br>This bit is ignored.                                                          |                             |                |                  |                  |                 |     |  |  |  |  |

|               | When TCS = $0$ :                                                                                      |                             |                |                  |                  |                 |     |  |  |  |  |

|               |                                                                                                       | <u></u><br>ne accumulatio   | n is enabled   |                  |                  |                 |     |  |  |  |  |

|               | 0 = Gated tir                                                                                         | ne accumulatio              | on is disabled |                  |                  |                 |     |  |  |  |  |

| bit 5-4       | TCKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                   |                             |                |                  |                  |                 |     |  |  |  |  |

|               | 11 = 1:256                                                                                            |                             |                |                  |                  |                 |     |  |  |  |  |

|               | 10 = 1:64                                                                                             |                             |                |                  |                  |                 |     |  |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                                                                                  |                             |                |                  |                  |                 |     |  |  |  |  |

| bit 3         |                                                                                                       | ted: Read as '              | ٥'             |                  |                  |                 |     |  |  |  |  |

| bit 2         | -                                                                                                     | er1 External Cl             |                | chronization S   | elect hit        |                 |     |  |  |  |  |

|               | When TCS =                                                                                            |                             | Jok Input Oyn  |                  |                  |                 |     |  |  |  |  |

|               |                                                                                                       | <u></u><br>nizes external o | clock input    |                  |                  |                 |     |  |  |  |  |

|               |                                                                                                       | t synchronize e             |                | input            |                  |                 |     |  |  |  |  |

|               | When TCS =                                                                                            |                             |                |                  |                  |                 |     |  |  |  |  |

|               | This bit is ign                                                                                       |                             |                |                  |                  |                 |     |  |  |  |  |

| bit 1         |                                                                                                       | Clock Source S              |                |                  |                  |                 |     |  |  |  |  |

|               |                                                                                                       | clock from pin,             | 11CK (on the   | e rising edge)   |                  |                 |     |  |  |  |  |

| <b>h</b> # 0  |                                                                                                       | clock (Fosc/2)              | 0'             |                  |                  |                 |     |  |  |  |  |

| bit 0         | Unimplemen                                                                                            | ted: Read as '              | U              |                  |                  |                 |     |  |  |  |  |

#### REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

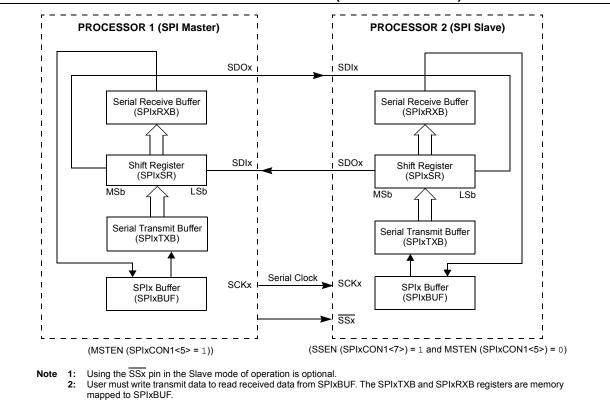

#### FIGURE 15-4: SPI MASTER/SLAVE CONNECTION (ENHANCED BUFFER MODES)

### 16.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C<sup>™</sup>)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. Refer to Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS39702) in the "PIC24F Family Reference Manual" for more information.

The Inter-Integrated Circuit (I<sup>2</sup>C) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent master and slave logic

- 7-bit and 10-bit device addresses

- General call address, as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications.

- Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave, regardless of the address

- Automatic SCL

- A block diagram of the module is shown in Figure 16-1.

### 16.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat Steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC      | R-0, HSC                         | U-0                                         | U-0              | U-0             | R/C-0, HSC                  | R-0, HSC         | R-0, HSC             |  |  |  |  |

|---------------|----------------------------------|---------------------------------------------|------------------|-----------------|-----------------------------|------------------|----------------------|--|--|--|--|

| ACKSTAT       | TRSTAT                           | _                                           | —                | —               | BCL                         | GCSTAT           | ADD10                |  |  |  |  |

| bit 15        |                                  |                                             |                  |                 |                             |                  | bit 8                |  |  |  |  |

|               |                                  |                                             |                  |                 |                             |                  |                      |  |  |  |  |

| R/C-0, HSC    | R/C-0, HSC                       | R-0, HSC                                    | R/C-0, HSC       | R/C-0, HSC      | R-0, HSC                    | R-0, HSC         | R-0, HSC             |  |  |  |  |

| IWCOL         | I2COV                            | D/A                                         | Р                | S               | R/W                         | RBF              | TBF                  |  |  |  |  |