Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                     |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                              |

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 180MHz                                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SDIO, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, LCD, POR, PWM, WDT                                                |

| Number of I/O              | 114                                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 384K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 169-UFBGA                                                                                           |

| Supplier Device Package    | 169-UFBGA (7x7)                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f469aih6                               |

Description STM32F469xx

Table 2. STM32F469xx features and peripheral counts (continued)

| Peripherals                      | STM32F469Vx                                                                                                      | STM32F469Zx | STM32F469Ax          | STM32F469lx         | STM32F469Bx | STM32F469Nx |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------|-------------|----------------------|---------------------|-------------|-------------|--|--|--|

| MIPI-DSI Host                    |                                                                                                                  |             | Y                    | es                  |             |             |  |  |  |

| LCD-TFT                          |                                                                                                                  |             | Y                    | es                  |             |             |  |  |  |

| Chrom-ART Accelerator™ (DMA2D)   | Yes                                                                                                              |             |                      |                     |             |             |  |  |  |

| GPIOs                            | 71                                                                                                               | 106         | 114                  | 131                 | 161         | 161         |  |  |  |

| 12-bit ADC                       | 3                                                                                                                |             |                      |                     |             |             |  |  |  |

| Number of channels               | 14                                                                                                               | 20          | 24                   | 16                  | 24          | 24          |  |  |  |

| 12-bit DAC<br>Number of channels |                                                                                                                  |             |                      | es<br>2             |             |             |  |  |  |

| Maximum CPU frequency            |                                                                                                                  |             | 180                  | MHz                 |             |             |  |  |  |

| Operating voltage                |                                                                                                                  |             | 1.7 to               | 3.6V <sup>(2)</sup> |             |             |  |  |  |

| Operating temperatures           | Ambient operating temperature: -40 to 85 °C / -40 to 105 °C  Junction temperature: -40 to 105 °C / -40 to 125 °C |             |                      |                     |             |             |  |  |  |

| Package                          | LQFP100                                                                                                          | LQPF144     | UFBGA169<br>WLCSP168 | LQFP176<br>UFBGA176 | LQFP208     | TFBGA216    |  |  |  |

<sup>1.</sup> The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

<sup>2.</sup> VDD/VDDA minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.19.2).

STM32F469xx Description

## 1.1.4 TFBGA216 package

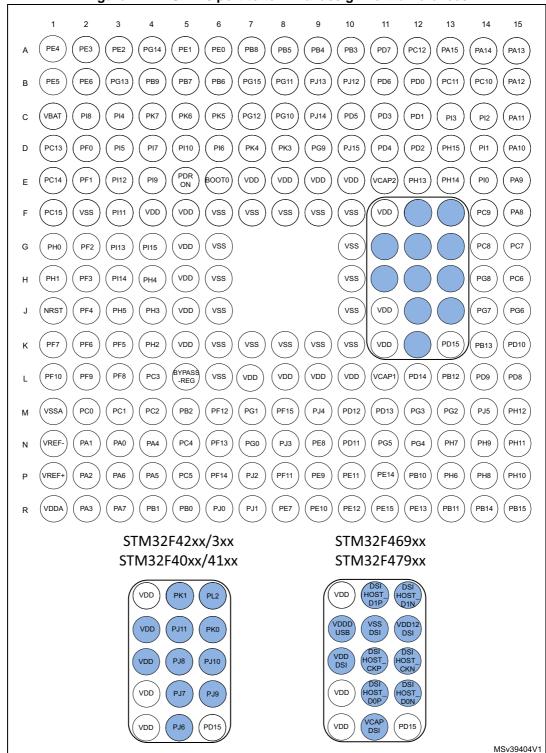

Figure 4. TFBGA216 port-to-terminal assignment differences

1. The highlighted pins are substituted with dedicated DSI IO pins on STM32F469xx/479xx devices.

**Functional overview** STM32F469xx

#### 2.4 **Embedded Flash memory**

The devices embed a Flash memory of up to 2 Mbytes available for storing programs and data.

#### 2.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

#### 2.6 **Embedded SRAM**

All devices embed:

- Up to 384Kbytes of system SRAM including 64 Kbytes of CCM (core coupled memory) data RAM

- RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

- 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

#### 2.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM, FMC, QUADSPI, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

DocID028196 Rev 4 22/217

## 3 Pinouts and pin description

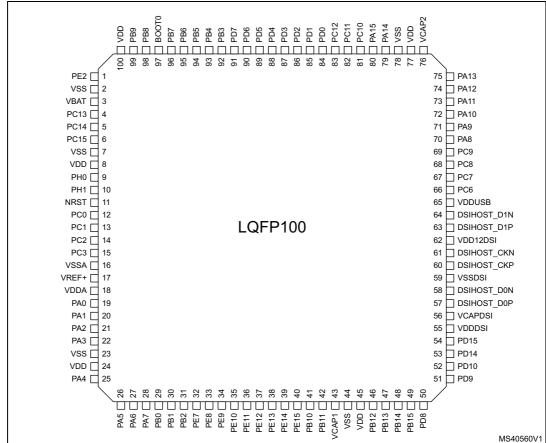

Figure 13. STM32F46x LQFP100 pinout

1. The above figure shows the package top view.

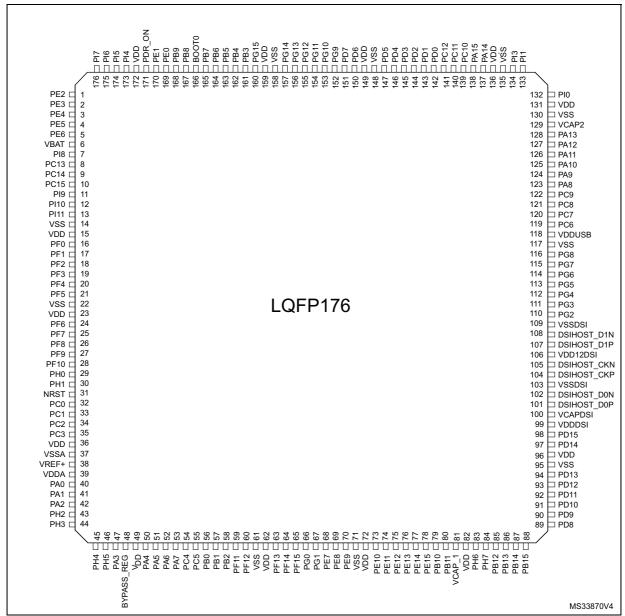

Figure 18. STM32F46x LQFP176 pinout

1. The above figure shows the package top view.

|           |      |     |        |              |                  | T        | able 12.           | Alterna         | te funct                  | ion (cc                            | ntinued                                        |                                         |      |                              |                      |        |              |

|-----------|------|-----|--------|--------------|------------------|----------|--------------------|-----------------|---------------------------|------------------------------------|------------------------------------------------|-----------------------------------------|------|------------------------------|----------------------|--------|--------------|

|           |      | AF0 | AF1    | AF2          | AF3              | AF4      | AF5                | AF6             | AF7                       | AF8                                | AF9                                            | AF10                                    | AF11 | AF12                         | AF13                 | AF14   | AF15         |

| Р         | ort  | sys | TIM1/2 | TIM3/4/<br>5 | TIM8/9/<br>10/11 | I2C1/2/3 | SPI1/2/3<br>/4/5/6 | SPI2/3/<br>SAI1 | SPI2/3/<br>USART<br>1/2/3 | USAR<br>T6/<br>UART<br>4/5/7/<br>8 | CAN1/2/<br>TIM12/<br>13/14/<br>QUAD<br>SPI/LCD | QUAD<br>SPI/OT<br>G2_HS<br>/OTG1<br>_FS | ЕТН  | FMC/<br>SDIO/<br>OTG2_<br>FS | DCMI/<br>DSI<br>HOST | LCD    | sys          |

|           | PJ0  | -   | -      | -            | -                | ı        | -                  | ı               | -                         | -                                  | LCD_R7                                         | -                                       | -    | -                            | -                    | LCD_R1 | EVENT<br>OUT |

|           | PJ1  | -   | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_R2 | EVENT<br>OUT |

|           | PJ2  | -   | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -    | -                            | DSIHOST<br>_TE       | LCD_R3 | EVENT<br>OUT |

|           | PJ3  | -   | -      | -            | -                | ı        | -                  | 1               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_R4 | EVENT<br>OUT |

| Port      | PJ4  | -   | -      | -            | -                | ı        | -                  | 1               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_R5 | EVENT<br>OUT |

| J         | PJ5  | -   | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_R6 | EVENT<br>OUT |

|           | PJ12 | -   | -      | -            | -                | -        | -                  | -               | -                         | -                                  | LCD_G3                                         | -                                       | -    | -                            | -                    | LCD_B0 | EVENT<br>OUT |

|           | PJ13 | -   | -      | -            | -                | ı        | -                  | ı               | -                         | -                                  | LCD_G4                                         | -                                       | -    | -                            | -                    | LCD_B1 | EVENT<br>OUT |

|           | PJ14 | -   | -      | -            | -                | 1        | -                  | ı               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_B2 | EVENT<br>OUT |

|           | PJ15 | -   | -      | -            | -                | ı        | -                  | 1               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_B3 | EVENT<br>OUT |

|           | PK3  | -   | -      | -            | -                | ı        | -                  | 1               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_B4 | EVENT<br>OUT |

|           | PK4  | -   | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_B5 | EVENT<br>OUT |

| Port<br>K | PK5  | -   | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_B6 | EVENT<br>OUT |

|           | PK6  | -   | -      | -            | -                | 1        | -                  | ı               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_B7 | EVENT<br>OUT |

|           | PK7  | -   | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -    | -                            | -                    | LCD_DE | EVENT<br>OUT |

**Table 15. Current characteristics**

| Symbol                             | Ratings                                                                                          | Max.   | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------|--------|------|

| $\Sigma I_{VDD}$                   | Total current into sum of all V <sub>DD_x</sub> power lines (source) <sup>(1)</sup>              | 290    |      |

| Σ I <sub>VSS</sub>                 |                                                                                                  |        |      |

| Σ I <sub>VDDUSB</sub>              |                                                                                                  |        |      |

| I <sub>VDD</sub>                   | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>                   | 100    |      |

| I <sub>VSS</sub>                   | I <sub>VSS</sub> Maximum current out of each V <sub>SS_x</sub> ground line (sink) <sup>(1)</sup> |        |      |

| 1.                                 | Output current sunk by any I/O and control pin                                                   | 25     |      |

| I <sub>IO</sub>                    | Output current sourced by any I/Os and control pin                                               | - 25   |      |

|                                    | Total output current sunk by sum of all I/O and control pins (2)                                 | 120    | mA   |

| $\Sigma I_{IO}$                    | Total output current sunk by sum of all USB I/Os                                                 | 25     |      |

|                                    | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup>                  | - 120  |      |

|                                    | Injected current on FT pins (4)                                                                  | 54.0   |      |

| I <sub>INJ(PIN)</sub> (3)          | Injected current on NRST and BOOT0 pins (4)                                                      | - 5/+0 |      |

|                                    | Injected current on TTa pins <sup>(5)</sup>                                                      | ±5     |      |

| $\Sigma I_{\text{INJ(PIN)}}^{(5)}$ | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                          | ±25    |      |

- All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

- This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

- 3. Negative injection disturbs the analog performance of the device. See note in Section 5.3.24.

- 4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- 5. A positive injection is induced by  $V_{IN} > V_{DDA}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 14* for the values of the maximum allowed input voltage.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the

positive and negative injected currents (instantaneous values).

**Table 16. Thermal characteristics**

| Symbol           | Ratings                      | Value        | Unit |

|------------------|------------------------------|--------------|------|

| T <sub>STG</sub> | Storage temperature range    | - 65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 125          | °C   |

# 5.3 Operating conditions

## 5.3.1 General operating conditions

Table 17. General operating conditions

| Symbol                             | Parameter                                               | Conditions <sup>(1)</sup>                                |                                                                                          | Min                | Тур | Max | Unit |

|------------------------------------|---------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------|-----|-----|------|

|                                    | Internal AHB clock frequency                            | register = 0x01),                                        | Power Scale 3 (VOS[1:0] bits in PWR_CR register = 0x01),<br>Regulator ON, over-drive OFF |                    |     | 120 |      |

|                                    |                                                         | Power Scale 2 (VOS[1:0] bits in PWR CR register = 0x10), | Over-drive<br>OFF                                                                        | 0                  | -   | 144 |      |

| f <sub>HCLK</sub>                  |                                                         | Regulator ON                                             | Over-drive<br>ON                                                                         |                    | -   | 168 |      |

|                                    |                                                         | Power Scale 1 (VOS[1:0] bits in PWR CR register= 0x11),  | Over-drive<br>OFF                                                                        | 0                  | -   | 168 | MHz  |

|                                    |                                                         | Regulator ON                                             | Over-drive<br>ON                                                                         |                    | -   | 180 |      |

| f                                  | Internal ADD1 alook fraguency                           | Over-drive OFF                                           |                                                                                          |                    | -   | 42  |      |

| f <sub>PCLK1</sub>                 | Internal APB1 clock frequency                           | Over-drive ON                                            |                                                                                          | 0                  | -   | 45  |      |

| f                                  | Internal ADD2 alook fraguency                           | Over-drive OFF                                           |                                                                                          | 0                  | -   | 84  |      |

| f <sub>PCLK2</sub>                 | Internal APB2 clock frequency                           | Over-drive ON                                            | 0                                                                                        | -                  | 90  |     |      |

| V <sub>DD</sub>                    | Standard operating voltage                              | -                                                        |                                                                                          | 1.7 <sup>(2)</sup> | -   | 3.6 |      |

| V <sub>DDA</sub> <sup>(3)(4)</sup> | Analog operating voltage (ADC limited to 1.2 M samples) | Must be the same potential as                            | V (5)                                                                                    | 1.7 <sup>(2)</sup> | -   | 2.4 |      |

| VDDA' / /                          | Analog operating voltage (ADC limited to 2.4 M samples) | niusi pe ine same potential as                           | vDD, ,                                                                                   | 2.4                | -   | 3.6 |      |

| .,                                 | USB supply voltage                                      | USB not used                                             |                                                                                          |                    | 3.3 | 3.6 |      |

| V <sub>DDUSB</sub>                 | (supply voltage for PA11, PA12, PB14 and PB15 pins)     | USB used                                                 | 3.0                                                                                      | -                  | 3.6 |     |      |

| V <sub>DDDSI</sub>                 | DSI system operating voltage                            | -                                                        | 1.7 <sup>(2)</sup>                                                                       | -                  | 3.6 |     |      |

| $V_{BAT}$                          | Backup operating voltage                                | -                                                        | 1.65                                                                                     | -                  | 3.6 |     |      |

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- When the regulator is OFF, the V<sub>12</sub> is provided externally, as described in *Table 17:* General operating conditions.

- The voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for f<sub>HCLK</sub> ≤ 120 MHz

- Scale 2 for 120 MHz < f<sub>HCLK</sub>  $\le$  144 MHz

- Scale 1 for 144 MHz < f<sub>HCLK</sub> ≤ 180 MHz. The over-drive is only ON at 180 MHz.

- The system clock is HCLK, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

- External clock frequency is 25 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The typical current consumption values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and for ambient temperature T<sub>A</sub>= 25 °C unless otherwise specified.

- The maximum values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and a maximum ambient temperature (T<sub>A</sub>), unless otherwise specified.

- For the voltage range 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  2.1 V the maximum frequency is 168 MHz.

Table 30. Typical and maximum current consumption in Standby mode

|                      |                                |                                                                     |                         | Typ <sup>(1)</sup>         |                         |                         | Max <sup>(2)</sup>     |                         |      |  |

|----------------------|--------------------------------|---------------------------------------------------------------------|-------------------------|----------------------------|-------------------------|-------------------------|------------------------|-------------------------|------|--|

| Symbol               | Parameter                      | Conditions                                                          | T <sub>A</sub> = 25 °C  |                            |                         | T <sub>A</sub> = 25 °C  | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |  |

|                      |                                |                                                                     | V <sub>DD</sub> = 1.7 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> = 3.3 V | V <sub>DD</sub> = 3.3 V |                        |                         |      |  |

|                      |                                | Backup SRAM ON, RTC and<br>LSE oscillator OFF                       | 1.7                     | 2.5                        | 2.9                     | 6 <sup>(3)</sup>        | 18                     | 35 <sup>(3)</sup>       |      |  |

|                      | Supply current in Standby mode | Backup SRAM OFF, RTC and LSE oscillator OFF                         | 1.0                     | 1.8                        | 2.20                    | 5 <sup>(3)</sup>        | 15                     | 30 <sup>(3)</sup>       | μΑ   |  |

|                      |                                | Backup SRAM OFF, RTC ON and LSE oscillator in Power Drive mode      | 1.7                     | 2.7                        | 3.2                     | 7                       | 20                     | 39                      |      |  |

| I <sub>DD_STBY</sub> |                                | Backup SRAM ON, RTC ON<br>and LSE oscillator in Power<br>Drive mode | 2.4                     | 3.4                        | 4.0                     | 8                       | 25                     | 48                      |      |  |

|                      |                                | Backup SRAM ON, RTC ON<br>and LSE oscillator in High<br>Drive mode  | 3.2                     | 4.2                        | 4.8                     | 10                      | 29                     | 57                      |      |  |

|                      |                                | Backup SRAM OFF, RTC ON<br>and LSE oscillator in High<br>Drive mode | 2.5                     | 3.5                        | 4.1                     | 8                       | 25                     | 48                      |      |  |

<sup>1.</sup> PDR is off for  $V_{DD}$ =1.7 V. When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2  $\mu A$

<sup>2.</sup> Based on characterization, not tested in production unless otherwise specified.

<sup>3.</sup> Based on characterization, tested in production.

Table 31. Typical and maximum current consumption in  $\ensuremath{V_{BAT}}$  mode

|                      |           |                                                                     |                          | Тур                         |                          |                          |                           |                            |      |  |

|----------------------|-----------|---------------------------------------------------------------------|--------------------------|-----------------------------|--------------------------|--------------------------|---------------------------|----------------------------|------|--|

| Symbol               | Parameter | Conditions <sup>(1)</sup>                                           | T <sub>A</sub> = 25 °C   |                             |                          | T <sub>A</sub> = 25 °C   | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|                      |           |                                                                     | V <sub>BAT</sub> = 1.7 V | V <sub>BAT</sub> =<br>2.4 V | V <sub>BAT</sub> = 3.3 V | V <sub>BAT</sub> = 3.3 V |                           |                            |      |  |

|                      |           | Backup SRAM ON, RTC ON<br>and LSE oscillator in Low<br>Power mode   | 1.431                    | 1.577                       | 1.825                    | 1.9                      | 12.0                      | 24.0                       |      |  |

|                      | Backup    | Backup SRAM OFF, RTC ON<br>and LSE oscillator in Low<br>Power mode  | 0.720                    | 0.849                       | 1.060                    | 1.1                      | 7.0                       | 13.9                       | μΑ   |  |

| I <sub>DD_VBAT</sub> |           | Backup SRAM ON, RTC ON<br>and LSE oscillator in High<br>Drive mode  | 2.212                    | 2.368                       | 2.630                    | 2.80                     | 17.3                      | 34.6                       |      |  |

| Ct                   |           | Backup SRAM OFF, RTC ON<br>and LSE oscillator in High<br>Drive mode | 1.499                    | 1.637                       | 1.862                    | 2.0                      | 12.3                      | 24.5                       |      |  |

|                      |           | Backup SRAM ON, RTC and<br>LSE OFF                                  | 0.710                    | 0.720                       | 0.760                    | 0.8 <sup>(3)</sup>       | 5.0                       | 10.0 <sup>(3)</sup>        |      |  |

|                      |           | Backup SRAM OFF, RTC and<br>LSE OFF                                 | 0.018                    | 0.020                       | 0.024                    | 0.2 <sup>(3)</sup>       | 2.0                       | 4.0 <sup>(3)</sup>         |      |  |

- 1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a  $\rm C_L$  of 6 pF for typical values.

- 2. Based on characterization, tested in production.

- 3. Based on test during characterization.

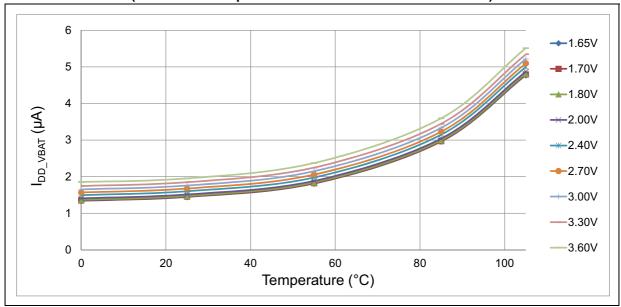

Figure 27. Typical  $V_{BAT}$  current consumption (RTC ON / backup SRAM ON and LSE in Low drive mode)

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the informations given in this paragraph are based on characterization results obtained with typical external components specified in Table 38.

In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| (LSE                                |                                         |                                |       |      |      |      |  |  |  |

|-------------------------------------|-----------------------------------------|--------------------------------|-------|------|------|------|--|--|--|

| Symbol                              | Parameter                               | Conditions                     | Min   | Тур  | Max  | Unit |  |  |  |

| R <sub>F</sub>                      | Feedback resistor                       | -                              | -     | 18.4 | -    | МΩ   |  |  |  |

| I <sub>DD</sub>                     | LSE current consumption                 | Low power mode <sup>(2)</sup>  | -     | -    | 1    | ^    |  |  |  |

|                                     | LSE current consumption                 | High drive mode <sup>(2)</sup> | -     | -    | 3    | μΑ   |  |  |  |

| ACC <sub>LSE</sub> <sup>(3)</sup>   | LSE accuracy                            | -                              | - 500 | -    | 500  | ppm  |  |  |  |

| C crit may                          | Maximum critical crystal g <sub>m</sub> | Low power mode <sup>(2)</sup>  | -     | -    | 0.56 | μΑ/V |  |  |  |

| G <sub>m</sub> _crit_max            |                                         | High drive mode <sup>(2)</sup> | -     | -    | 1.5  | μΑνν |  |  |  |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                            | V <sub>DD</sub> is stabilized  | -     | 2    | -    | s    |  |  |  |

Table 38. LSE oscillator characteristics  $(f_{LSE} = 32.768 \text{ kHz})^{(1)}$

- 2. LSE mode cannot be changed "on the fly" otherwise, a glitch can be generated on OSCIN pin.

- 3. This parameter depends on the crystal used in the application. Refer to application note AN2867.

- $t_{SU(LSE)}$  is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For information on selecting the crystal, refer to the application note AN2867 "Oscillator Note: design guide for ST microcontrollers" available from www.st.com.

Figure 32. Typical application with a 32.768 kHz crystal Resonator with integrated capacitors Cı fLSE . OSC32\_IN Bias 32.768 kHz RF controlled resonator gain OSC32 OUT STM32F ai17531

<sup>1.</sup> Guaranteed by design.

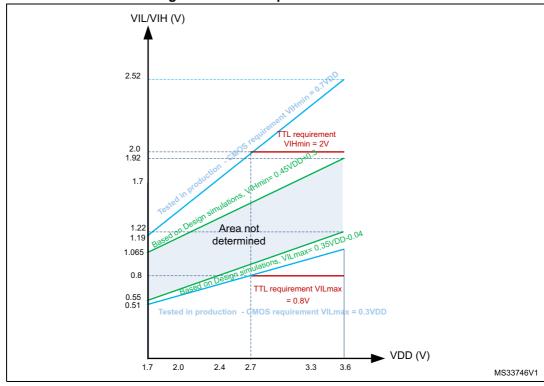

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT I/Os is shown in *Figure 39*.

Figure 39. FT I/O input characteristics

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed  $V_{OL}/V_{OH}$ ) except PC13, PC14, PC15 and PI8 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 and PI8 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15*).

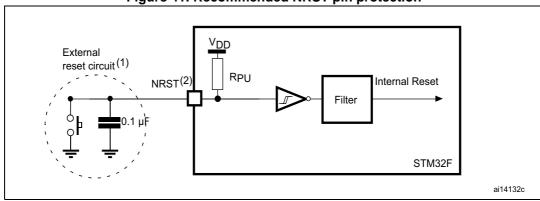

## 5.3.21 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PLI</sub> (see *Table 58*).

Unless otherwise specified, the parameters given in *Table 61* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                               | Parameter Conditions                            |                         | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | 113  |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 61. NRST pin characteristics

2. Guaranteed by design.

Figure 41. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 61. Otherwise the reset is not taken into account by the device.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series

resistance must be minimum (~10% order).

| Symbol                           | Parameter                                                                   | Conditions                                                                            | Min  | Тур | Max   | Unit |

|----------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|-----|-------|------|

|                                  | Total conversion time (including sampling time)                             | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution                                        | 0.50 | -   | 16.40 |      |

| t <sub>CONV</sub> <sup>(2)</sup> |                                                                             | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution                                        | 0.43 | -   | 16.34 | 116  |

|                                  |                                                                             | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution                                         | 0.37 | -   | 16.27 | μs   |

|                                  |                                                                             | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution                                         | 0.30 | -   | 16.20 |      |

|                                  |                                                                             | 9 to 492 (t <sub>S</sub> for sampling +n-bit resolution for successive approximation) |      |     |       |      |

|                                  | Sampling rate $(f_{ADC} = 30 \text{ MHz, and } t_S = 3 \text{ ADC cycles})$ | 12-bit resolution<br>Single ADC                                                       | -    | -   | 2     |      |

| f <sub>S</sub> <sup>(2)</sup>    |                                                                             | 12-bit resolution<br>Interleave Dual ADC<br>mode                                      | -    | -   | 3.75  | Msps |

|                                  |                                                                             | 12-bit resolution<br>Interleave Triple ADC<br>mode                                    | -    | -   | 6     |      |

| I <sub>VREF+</sub> (2)           | ADC V <sub>REF</sub><br>DC current consumption in<br>conversion mode        | -                                                                                     | -    | 300 | 500   | μА   |

| I <sub>VDDA</sub> <sup>(2)</sup> | ADC V <sub>DDA</sub> DC current consumption in conversion mode              | -                                                                                     | -    | 1.6 | 1.8   | mA   |

- 1.  $V_{DDA}$  minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.19.2).

- 2. Based on test during characterization.

- 3.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

- 4.  $R_{ADC}$  maximum value is given for  $V_{DD}$ =1.7 V, and minimum value for  $V_{DD}$ =3.3 V.

- 5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 76*.

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k - 0.5)}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The formula above (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

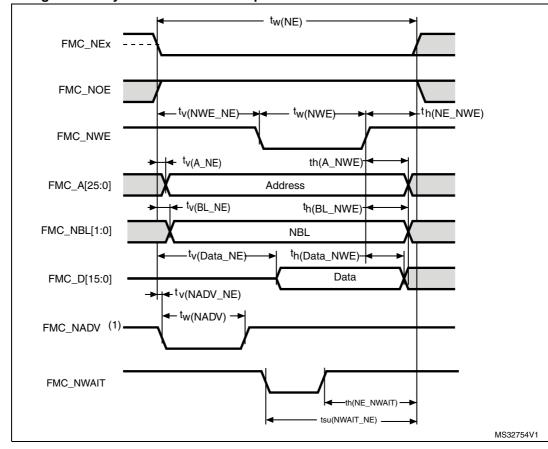

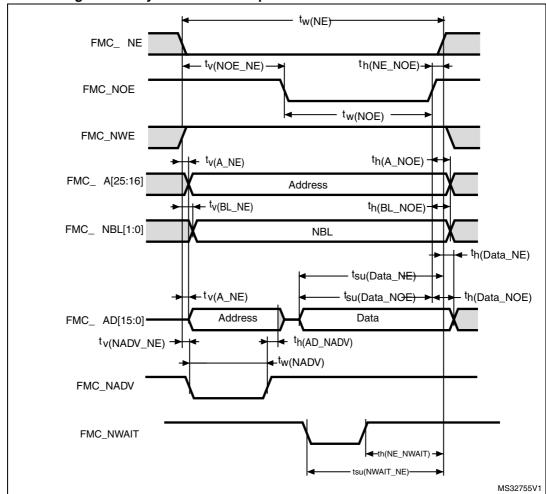

Figure 60. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

Table 90. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings<sup>(1)</sup>

| Table 90. Asynchronous non-multiplexed Strawn Strawnon write tillings |                                       |                         |                         |      |  |  |

|-----------------------------------------------------------------------|---------------------------------------|-------------------------|-------------------------|------|--|--|

| Symbol                                                                | Parameter                             | Min                     | Max                     | Unit |  |  |

| t <sub>w(NE)</sub>                                                    | FMC_NE low time                       | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> +1   |      |  |  |

| t <sub>v(NWE_NE)</sub>                                                | FMC_NEx low to FMC_NWE low            | T <sub>HCLK</sub> - 0.5 | T <sub>HCLK</sub> + 0.5 |      |  |  |

| t <sub>w(NWE)</sub>                                                   | FMC_NWE low time                      | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5 |      |  |  |

| t <sub>h(NE_NWE)</sub>                                                | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> +1.5  | -                       |      |  |  |

| t <sub>v(A_NE)</sub>                                                  | FMC_NEx low to FMC_A valid            | -                       | 0                       |      |  |  |

| t <sub>h(A_NWE)</sub>                                                 | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> +0.5  | -                       |      |  |  |

| t <sub>v(BL_NE)</sub>                                                 | FMC_NEx low to FMC_BL valid           | -                       | 1.5                     | ns   |  |  |

| t <sub>h(BL_NWE)</sub>                                                | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> +0.5  | -                       |      |  |  |

| t <sub>v(Data_NE)</sub>                                               | Data to FMC_NEx low to Data valid     | -                       | T <sub>HCLK</sub> + 2   |      |  |  |

| t <sub>h(Data_NWE)</sub>                                              | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5  | -                       |      |  |  |

| t <sub>v(NADV_NE)</sub>                                               | FMC_NEx low to FMC_NADV low           | -                       | 0.5                     |      |  |  |

| t <sub>w(NADV)</sub>                                                  | FMC_NADV low time                     | -                       | T <sub>HCLK</sub> + 0.5 |      |  |  |

<sup>1.</sup> Based on test during characterization.

Table 91. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings<sup>(1)</sup>

| Symbol                    | Parameter                                 | Min                     | Max                   | Unit |

|---------------------------|-------------------------------------------|-------------------------|-----------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> +1   | 8T <sub>HCLK</sub> +2 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> - 1  | 6T <sub>HCLK</sub> +2 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                     | 1.0  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   | -                     |      |

<sup>1.</sup> Based on test during characterization.

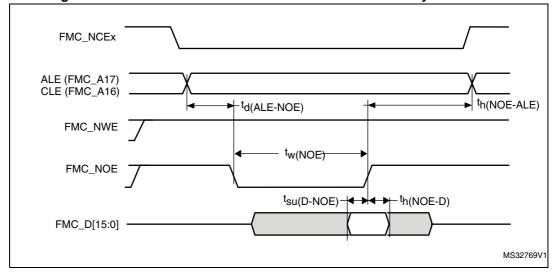

Figure 61. Asynchronous multiplexed PSRAM/NOR read waveforms

FMC\_NCEX

ALE (FMC\_A17)

CLE (FMC\_A16)

FMC\_NWE

FMC\_NOE (NRE)

Th(NWE-ALE)

FMC\_D[15:0]

MS32768V1

Figure 68. NAND controller waveforms for write access

#### **Package information** 6

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

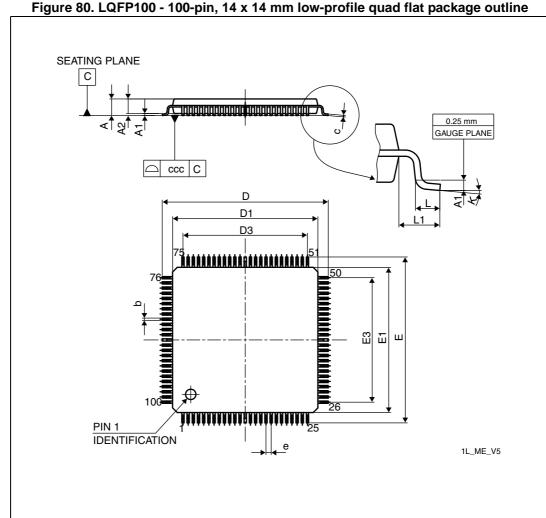

#### LQFP100 package information 6.1

Figure 80. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

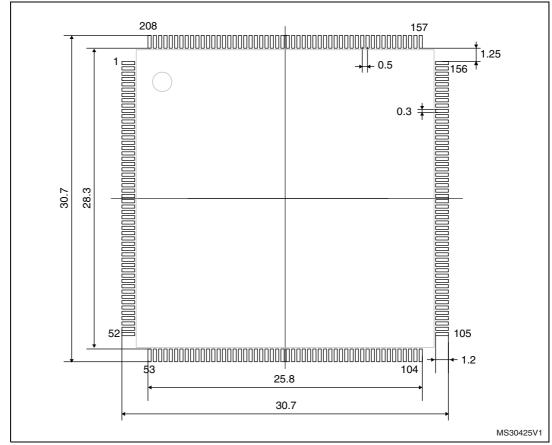

Figure 95. LQFP208 recommended footprint

1. Dimensions are expressed in millimeters.