#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 180MHz                                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SDIO, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 114                                                                                                 |

| Program Memory Size        | 1MB (1M × 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 384K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 201-UFBGA                                                                                           |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f469igh6tr                             |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Description

The STM32F469xx devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 180 MHz. The Cortex<sup>®</sup>-M4 core features a Floating point unit (FPU) single precision which supports all ARM<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F469xx devices incorporate high-speed embedded memories (Flash memory up to 2 Mbytes, up to 384 Kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers, and a true random number generator (RNG). They also feature standard and advanced communication interfaces:

- Up to three I<sup>2</sup>Cs

- Six SPIs, two I<sup>2</sup>Ss full duplex. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus four UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- One SAI serial audio interface

- An SDMMC host interface

- Ethernet and camera interface

- LCD-TFT display controller

- Chrom-ART Accelerator™

- DSI Host.

Advanced peripherals include an SDMMC interface, a flexible memory control (FMC) interface, a Quad-SPI Flash memory, and camera interface for CMOS sensors. Refer to *Table 2* for the list of peripherals available on each part number.

The STM32F469xx devices operate in the -40 to +105 °C temperature range from a 1.7 to 3.6 V power supply. A dedicated supply input for USB (OTG\_FS and OTG\_HS) only in full speed mode, is available on all packages.

The supply voltage can drop to 1.7 V (refer to Section 2.19.2). A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F469xx devices are offered in eight packages, ranging from 100 to 216 pins. The set of included peripherals changes with the device chosen, according to *Table 2*.

# 1.1 Compatibility throughout the family

STM32F469xx devices are not compatible with other STM32F4xx devices.

*Figure 1* and *Figure 2* show incompatible board designs, respectively, for LQFP176 and LQFP208 packages (highlighted pins).

The UFBGA176 and TFBGA216 ballouts are compatible with other STM32F4xx devices, only few IO port pins are substituted, as shown in *Figure 3* and *Figure 4*.

The LQFP100, LQFP144 and UFBGA169 packages are incompatible with other STM32F4xx devices.

## 2.4 Embedded Flash memory

The devices embed a Flash memory of up to 2 Mbytes available for storing programs and data.

# 2.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 2.6 Embedded SRAM

All devices embed:

- Up to 384Kbytes of system SRAM including 64 Kbytes of CCM (core coupled memory) data RAM

- RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

- 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 2.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM, FMC, QUADSPI, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

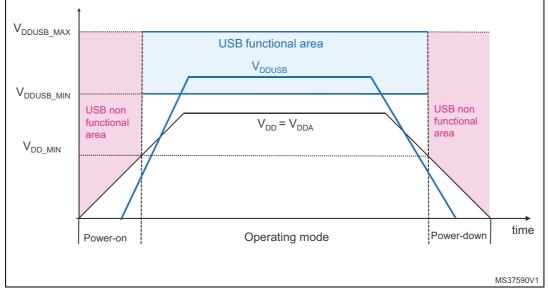

The following conditions must be respected:

- During power-on phase (V<sub>DD</sub> < V<sub>DD\_MIN</sub>), V<sub>DDUSB</sub> should be always lower than  $V_{DD}$

- During power-down phase (V<sub>DD</sub> < V<sub>DD\_MIN</sub>), V<sub>DDUSB</sub> should be always lower than V<sub>DD</sub>

- V<sub>DDUSB</sub> rising and falling time rate specifications must be respected.

- In operating mode phase, V<sub>DDUSB</sub> could be lower or higher than VDD:

- If USB (USB OTG\_HS/OTG\_FS) is used, the associated GPIOs powered by V<sub>DDUSB</sub> are operating between V<sub>DDUSB\_MIN</sub> and V<sub>DDUSB\_MAX</sub>. The V<sub>DDUSB</sub> supplies both USB transceivers (USB OTG\_HS and USB OTG\_FS).

- If only one USB transceiver is used in the application, the GPIOs associated to the other USB transceiver are still supplied by V<sub>DDUSB</sub>.

- If USB (USB OTG\_HS/OTG\_FS) is not used, the associated GPIOs powered by V<sub>DDUSB</sub> are operating between V<sub>DD MIN</sub> and V<sub>DD MAX</sub>.

Figure 7. V<sub>DDUSB</sub> connected to an external independent power supply

The DSI (Display Serial Interface) sub-system uses several power supply pins which are independent from the other supply pins:

- VDDDSI is an independent DSI power supply dedicated for DSI Regulator and MIPI D-PHY. This supply must be connected to global VDD.

- VCAPDSI pin is the output of DSI Regulator (1.2V) which must be connected externally to VDD12DSI.

- VDD12DSI pin is used to supply the MIPI D-PHY, and to supply clock and data lanes pins. An external capacitor of 2.2 uF must be connected on VDD12DSI pin.

- VSSDSI pin is an isolated supply ground used for DSI sub-system.

- If DSI functionality is not used at all, then:

- VDDDSI pin must be connected to global VDD.

- VCAPDSI pin must be connected externally to VDD12DSI but the external capacitor is no more needed.

- VSSDSI pin must be grounded.

| Name                   | Abbreviation                                              | rise specified in brackets below the pin name, the pin function during and aft<br>me as the actual pin name<br>Supply pin<br>Input only pin<br>Input / output pin<br>5 V tolerant I/O<br>3.3 V tolerant I/O directly connected to analog parts<br>Dedicated BOOT0 pin<br>Bidirectional reset pin with weak pull-up resistor<br>rise specified by a note, all I/Os are set as floating inputs during and after reserved through GPIOx_AFR registers |  |  |  |  |

|------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name               |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                        | S                                                         | Supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Pin type               | I                                                         | Input only pin                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                        | I/O                                                       | Input / output pin                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                        | FT                                                        | 5 V tolerant I/O                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| I/O structure          | TTa 3.3 V tolerant I/O directly connected to analog parts |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| I/O structure          | В                                                         | Dedicated BOOT0 pin                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                        | RST                                                       | Bidirectional reset pin with weak pull-up resistor                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Notes                  | Unless otherwise                                          | specified by a note, all I/Os are set as floating inputs during and after reset                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Alternate<br>functions | Functions selected                                        | d through GPIOx_AFR registers                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Additional functions   | Functions directly                                        | selected/enabled through peripheral registers                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

Table 9. Legend/abbreviations used in the pinout table

| Pin name | NOR/PSRAM/SRAM | NOR/PSRAM Mux | NAND16 | SDRAM  |

|----------|----------------|---------------|--------|--------|

| PF8      | -              | -             | -      | -      |

| PF9      | -              | -             | -      | -      |

| PF10     | -              | -             | -      | -      |

| PG6      | -              | -             | -      | -      |

| PG7      | -              | -             | INT    | -      |

| PE0      | NBL0           | NBL0          | -      | NBL0   |

| PE1      | NBL1           | NBL1          | -      | NBL1   |

| PI4      | NBL2           | -             | -      | NBL2   |

| PI5      | NBL3           | -             | -      | NBL3   |

| PG8      | -              | -             | -      | SDCLK  |

| PC0      | -              | -             | -      | SDNWE  |

| PF11     | -              | -             | -      | SDNRAS |

| PG15     | -              | -             | -      | SDNCAS |

| PH2      | -              | -             | -      | SDCKE0 |

| PH3      | -              | -             | -      | SDNE0  |

| PH6      | -              | -             | -      | SDNE1  |

| PH7      | -              | -             | -      | SDCKE1 |

| PH5      | -              | -             | -      | SDNWE  |

| PC2      | -              | -             | -      | SDNE0  |

| PC3      | -              | -             | -      | SDCKE0 |

| PB5      | -              | -             | -      | SDCKE1 |

| PB6      | -              | -             | -      | SDNE1  |

Table 11. FMC pin definition (continued)

| ST  |  |

|-----|--|

| M32 |  |

| F46 |  |

| 9xx |  |

Pinouts and pin description

|                   |      |      |             |        |              |                  | Т        | able 12.           | Alterna         | te funct                  | ion (co                            | ontinued                                       | )                                       |                                           |                              |                      |         |               |

|-------------------|------|------|-------------|--------|--------------|------------------|----------|--------------------|-----------------|---------------------------|------------------------------------|------------------------------------------------|-----------------------------------------|-------------------------------------------|------------------------------|----------------------|---------|---------------|

| 1                 |      |      | AF0         | AF1    | AF2          | AF3              | AF4      | AF5                | AF6             | AF7                       | AF8                                | AF9                                            | AF10                                    | AF11                                      | AF12                         | AF13                 | AF14    | AF15          |

|                   | P    | ort  | SYS         | TIM1/2 | TIM3/4/<br>5 | TIM8/9/<br>10/11 | 12C1/2/3 | SPI1/2/3<br>/4/5/6 | SPI2/3/<br>SAI1 | SPI2/3/<br>USART<br>1/2/3 | USAR<br>T6/<br>UART<br>4/5/7/<br>8 | CAN1/2/<br>TIM12/<br>13/14/<br>QUAD<br>SPI/LCD | QUAD<br>SPI/OT<br>G2_HS<br>/OTG1<br>_FS | ЕТН                                       | FMC/<br>SDIO/<br>OTG2_<br>FS | DCMI/<br>DSI<br>HOST | LCD     | SYS           |

|                   |      | PG0  | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -                                         | FMC_A10                      | -                    | -       | EVENT<br>OUT  |

|                   |      | PG1  | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -                                         | FMC_A11                      | -                    | -       | EVENT<br>OUT  |

|                   |      | PG2  | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -                                         | FMC_A12                      | -                    | -       | EVENT<br>OUT  |

|                   |      | PG3  | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -                                         | FMC_A13                      | -                    | -       | EVENT<br>OUT  |

|                   |      | PG4  | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -                                         | FMC_A14/F<br>MC_BA0          | -                    | -       | EVENT<br>OUT  |

| DocID028196 Rev 4 |      | PG5  | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -                                         | FMC_A15/F<br>MC_BA1          | -                    | -       | EVENT<br>OUT  |

| 0281              |      | PG6  | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | -                                         |                              | DCMI_D12             | LCD_R7  | EVENT<br>OUT  |

| 96 R              |      | PG7  | -           | -      | -            | -                | -        |                    | SAI1<br>_MCLK_A |                           | USART6<br>_CK                      | -                                              | -                                       | -                                         | FMC_INT                      | DCMI_D13             | LCD_CLK | EVENT<br>OUT  |

| ev 4              | Port | PG8  | -           | -      | -            | -                | -        | SPI6_NSS           | -               | -                         | USART6<br>_RTS                     | -                                              | -                                       | ETH_PPS_OU<br>T                           | FMC_SDCL<br>K                |                      | LCD_G7  | EVENT<br>OUT  |

|                   | G    | PG9  | -           | -      | -            | -                | -        | -                  | -               | -                         | USART6<br>_RX                      | QUADSPI_<br>BK2_IO2                            | -                                       | -                                         | FMC_NE2/<br>FMC_NCE          | DCMI_VS<br>YNC       |         | EVENT<br>OUT  |

|                   |      | PG10 | -           | -      | -            | -                | -        | -                  | -               | -                         |                                    | LCD_G3                                         | -                                       | -                                         | FMC_NE3                      | DCMI_D2              | LCD_B2  | EVENT<br>OUT  |

|                   |      | PG11 | -           | -      | -            | -                | -        | -                  | -               | -                         | -                                  | -                                              | -                                       | ETH_MII<br>_TX_EN /<br>ETH_RMII<br>_TX_EN | -                            | DCMI_D3              | LCD_B3  | EVENT<br>OUT  |

|                   |      | PG12 | -           | -      | -            | -                | -        | SPI6_MISO          | -               | -                         | USART6<br>_RTS                     | LCD_B4                                         | -                                       | -                                         | FMC_NE4                      | -                    | LCD_B1  | EVENT<br>OUT  |

|                   |      | PG13 | TRACE<br>D0 | -      | -            | -                | -        | SPI6_SCK           | -               | -                         | USART6<br>_CTS                     | -                                              | -                                       | ETH_MII<br>_TXD0 /<br>ETH_RMII<br>_TXD0   | FMC_A24                      | -                    | LCD_R0  | EVENT<br>OUT  |

| 79,               |      | PG14 | TRACE<br>D1 | -      | -            | -                | -        | SPI6_MOSI          | -               | -                         | USART6<br>_TX                      | QUADSPI_<br>BK2_IO3                            | -                                       | ETH_MII<br>_TXD1 /<br>ETH_RMII<br>_TXD1   | FMC_A25                      | -                    | LCD_B0  | EVENT<br>OUT  |

| 79/217            |      | PG15 | -           | -      | -            | -                | -        | -                  | -               | -                         | USART6<br>_CTS                     | -                                              | -                                       | -                                         | FMC_<br>SDNCAS               | DCMI_D13             | -       | EVENT<br>'OUT |

| S   |

|-----|

| -   |

| _   |

| ~   |

| _   |

|     |

| ω   |

| N   |

| _   |

| Π.  |

| •   |

| -+- |

| 6   |

| ~   |

| G   |

|     |

| ~   |

| 6.2 |

| ×   |

|     |

|     |

Pinouts and pin description

|        |      | AF0 | AF1    | AF2          | AF3              | AF4      | AF5                   | AF6             | AF7                       | AF8                                | AF9                                            | AF10                                    | AF11              | AF12                         | AF13                 | AF14          | AF        |

|--------|------|-----|--------|--------------|------------------|----------|-----------------------|-----------------|---------------------------|------------------------------------|------------------------------------------------|-----------------------------------------|-------------------|------------------------------|----------------------|---------------|-----------|

| Port   |      | SYS | TIM1/2 | TIM3/4/<br>5 | TIM8/9/<br>10/11 | I2C1/2/3 | SPI1/2/3<br>/4/5/6    | SPI2/3/<br>SAI1 | SPI2/3/<br>USART<br>1/2/3 | USAR<br>T6/<br>UART<br>4/5/7/<br>8 | CAN1/2/<br>TIM12/<br>13/14/<br>QUAD<br>SPI/LCD | QUAD<br>SPI/OT<br>G2_HS<br>/OTG1<br>_FS | ETH               | FMC/<br>SDIO/<br>OTG2_<br>FS | DCMI/<br>DSI<br>HOST | LCD           | S         |

|        | P10  | -   | -      | TIM5_CH4     | -                | -        | SPI2_NSS/I<br>2S2_WS  | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D24                      | DCMI_D13             | LCD_G5        | EVE       |

|        | PI1  | -   | -      | -            | -                | -        | SPI2_SCK/I<br>2S2_CK  | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D25                      | DCMI_D8              | LCD_G6        | EVE<br>OL |

|        | Pl2  | -   | -      | -            | TIM8_CH4         | -        | SPI2_MISO             | I2S2ext_S<br>D  | -                         | -                                  | -                                              | -                                       | -                 | FMC_D26                      | DCMI_D9              | LCD_G7        | EVE       |

|        | PI3  | -   | -      | -            | TIM8_ETR         | -        | SPI2_MOSI<br>/I2S2_SD | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D27                      | DCMI_D10             |               | EVE       |

|        | Pl4  | -   | -      | -            | TIM8_BKI<br>N    | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_NBL2                     | DCMI_D5              | LCD_B4        | EVE       |

|        | PI5  | -   | -      | -            | TIM8_CH1         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_NBL3                     | DCMI_VS<br>YNC       | LCD_B5        | EVI       |

|        | PI6  | -   | -      | -            | TIM8_CH2         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D28                      | DCMI_D6              | LCD_B6        | EVI       |

|        | PI7  | -   | -      | -            | TIM8_CH3         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D29                      | DCMI_D7              | LCD_B7        | EVI       |

| Port I | PI8  | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    |               | EVI       |

|        | P19  | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | CAN1_RX                                        | -                                       | -                 | FMC_D30                      | -                    | LCD_VSY<br>NC | EVE       |

|        | PI10 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | ETH_MII_RX_<br>ER | FMC_D31                      | -                    | LCD_HSY<br>NC | EVE       |

|        | PI11 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | LCD_G6                                         | OTG_HS<br>_ULPI<br>_DIR                 | -                 | -                            | -                    | -             | EVE       |

|        | PI12 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_HSY<br>NC | EVE       |

|        | PI13 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_VSY<br>NC | EVI       |

|        | PI14 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_CLK       | EV<br>O   |

|        | PI15 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | LCD_G2                                         | -                                       | -                 | -                            | -                    | LCD_R0        | EVI<br>'O |

81/217

| Table 24. Typical and maximum current consumption in Run mode, code with data processing |

|------------------------------------------------------------------------------------------|

| running from Flash memory (ART accelerator enabled except prefetch) or RAM,              |

| regulator ON                                                                             |

|                 |                                  |                                        | regulati                |     |                           | Max <sup>(1)</sup>        |                            |      |

|-----------------|----------------------------------|----------------------------------------|-------------------------|-----|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter                        | Conditions                             | f <sub>HCLK</sub> (MHz) | Тур | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                                  |                                        | 180                     | 103 | 109 <sup>(4)</sup>        | 142                       | 175 <sup>(4)</sup>         |      |

|                 |                                  |                                        | 168                     | 94  | 99                        | 124                       | 149                        |      |

|                 |                                  |                                        | 150                     | 84  | 89                        | 114                       | 140                        |      |

|                 |                                  |                                        | 144                     | 77  | 81                        | 104                       | 127                        |      |

|                 |                                  |                                        | 120                     | 57  | 60                        | 79                        | 98                         |      |

|                 |                                  | All                                    | 90                      | 43  | 46                        | 64                        | 84                         |      |

|                 |                                  | Peripherals                            | 60                      | 30  | 33                        | 51                        | 70                         |      |

|                 |                                  | enabled <sup>(2)(3)</sup>              | 30                      | 16  | 19                        | 37                        | 57                         |      |

|                 |                                  |                                        | 25                      | 14  | 16                        | 34                        | 54                         | mA   |

|                 |                                  |                                        | 16                      | 7   | 10                        | 28                        | 48                         |      |

|                 |                                  |                                        | 8                       | 4   | 7                         | 26                        | 46                         |      |

|                 |                                  |                                        | 4                       | 3   | 6                         | 24                        | 44                         |      |

|                 | Supply<br>current in<br>RUN mode |                                        | 2                       | 3   | 5                         | 23                        | 43                         |      |

| I <sub>DD</sub> |                                  |                                        | 180                     | 50  | 56 <sup>(4)</sup>         | 89                        | 124 <sup>(4)</sup>         |      |

|                 |                                  |                                        | 168                     | 45  | 51                        | 75                        | 102                        |      |

|                 |                                  |                                        | 150                     | 41  | 46                        | 70                        | 97                         |      |

|                 |                                  |                                        | 144                     | 37  | 42                        | 63                        | 88                         |      |

|                 |                                  |                                        | 120                     | 28  | 31                        | 49                        | 69                         |      |

|                 |                                  | All                                    | 90                      | 21  | 24                        | 42                        | 63                         |      |

|                 |                                  | Peripherals<br>disabled <sup>(2)</sup> | 60                      | 15  | 17                        | 36                        | 56                         |      |

|                 |                                  | disabled <sup>(2)</sup>                | 30                      | 9   | 11                        | 29                        | 49                         |      |

|                 |                                  |                                        | 25                      | 7   | 10                        | 28                        | 48                         |      |

|                 |                                  |                                        | 16                      | 4   | 7                         | 25                        | 45                         | -    |

|                 |                                  |                                        | 8                       | 3   | 6                         | 22                        | 44                         |      |

|                 |                                  |                                        | 4                       | 3   | 5                         | 23                        | 43                         |      |

|                 |                                  |                                        | 2                       | 2   | 5                         | 23                        | 43                         |      |

1. Guaranteed based on test during characterization.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

4. Guaranteed by test in production.

DocID028196 Rev 4

|                                     |                          |                         |                            | Т                 | ур              |                    |                 |                        |                 |                         |                 |      |

|-------------------------------------|--------------------------|-------------------------|----------------------------|-------------------|-----------------|--------------------|-----------------|------------------------|-----------------|-------------------------|-----------------|------|

| Symbol                              | Parameter                | Conditions              | f <sub>HCLK</sub><br>(MHz) |                   |                 | T <sub>A</sub> = 2 | 25 °C           | T <sub>A</sub> = 85 °C |                 | T <sub>A</sub> = 105 °C |                 | Unit |

|                                     |                          |                         |                            | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub>  | I <sub>DD</sub> | I <sub>DD12</sub>      | I <sub>DD</sub> | I <sub>DD12</sub>       | I <sub>DD</sub> |      |

|                                     |                          |                         | 168                        | 70                | 1               | 75                 | 1               | 100                    | 1               | 126                     | 1               |      |

|                                     |                          |                         | 150                        | 63                | 1               | 70                 | 1               | 93                     | 1               | 118                     | 1               |      |

|                                     |                          |                         | 144                        | 57                | 1               | 61                 | 1               | 84                     | 1               | 108                     | 1               |      |

|                                     |                          | All                     | 120                        | 42                | 1               | 45                 | 1               | 64                     | 1               | 84                      | 1               |      |

|                                     | Supply current           | Peripherals<br>enabled  | 90                         | 32                | 1               | 36                 | 1               | 53                     | 1               | 73                      | 1               | mA   |

|                                     |                          |                         | 60                         | 22                | 1               | 24                 | 1               | 43                     | 1               | 63                      | 1               |      |

|                                     |                          |                         | 30                         | 12                | 1               | 14                 | 1               | 33                     | 1               | 53                      | 1               |      |

| 1 /1                                |                          |                         | 25                         | 10                | 1               | 12                 | 1               | 31                     | 1               | 51                      | 1               |      |

| I <sub>DD12</sub> / I <sub>DD</sub> | from V <sub>12</sub> and |                         | 168                        | 20                | 1               | 24                 | 1               | 49                     | 1               | 75                      | 1               |      |

|                                     | $V_{DD}$ supply          |                         | 150                        | 18                | 1               | 22                 | 1               | 47                     | 1               | 73                      | 1               |      |

|                                     |                          |                         | 144                        | 16                | 1               | 19                 | 1               | 42                     | 1               | 66                      | 1               |      |

|                                     |                          | All                     | 120                        | 12                | 1               | 14                 | 1               | 33                     | 1               | 53                      | 1               |      |

|                                     |                          | Peripherals<br>disabled | 90                         | 10                | 1               | 12                 | 1               | 30                     | 1               | 50                      | 1               |      |

|                                     |                          |                         | 60                         | 7                 | 1               | 9                  | 1               | 27                     | 1               | 47                      | 1               |      |

|                                     |                          |                         | 30                         | 4                 | 1               | 6                  | 1               | 24                     | 1               | 44                      | 1               |      |

|                                     |                          |                         | 25                         | 4                 | 1               | 6                  | 1               | 24                     | 1               | 44                      | 1               |      |

1. Guaranteed based on test during characterization.

|                      |                                      |                                                                      |                            | Typ <sup>(1)</sup>         |                            |                           | Max <sup>(2)</sup>        |                            |      |  |

|----------------------|--------------------------------------|----------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------|----------------------------|------|--|

| Symbol               | Parameter                            | Conditions                                                           | Т                          | A = 25 °                   | C                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|                      |                                      |                                                                      | V <sub>DD</sub> =<br>1.7 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | v                         |                           |                            |      |  |

|                      |                                      | Backup SRAM ON, RTC and<br>LSE oscillator OFF                        | 1.7                        | 2.5                        | 2.9                        | 6 <sup>(3)</sup>          | 18                        | 35 <sup>(3)</sup>          |      |  |

|                      | Supply current<br>in Standby<br>mode | Backup SRAM OFF, RTC and<br>LSE oscillator OFF                       | 1.0                        | 1.8                        | 2.20                       | 5 <sup>(3)</sup>          | 15                        | 30 <sup>(3)</sup>          |      |  |

|                      |                                      | Backup SRAM OFF, RTC ON<br>and LSE oscillator in Power<br>Drive mode | 1.7                        | 2.7                        | 3.2                        | 7                         | 20                        | 39                         |      |  |

| I <sub>DD_STBY</sub> |                                      | Backup SRAM ON, RTC ON<br>and LSE oscillator in Power<br>Drive mode  | 2.4                        | 3.4                        | 4.0                        | 8                         | 25                        | 48                         | μA   |  |

|                      |                                      | Backup SRAM ON, RTC ON<br>and LSE oscillator in High<br>Drive mode   | 3.2                        | 4.2                        | 4.8                        | 10                        | 29                        | 57                         |      |  |

|                      |                                      | Backup SRAM OFF, RTC ON<br>and LSE oscillator in High<br>Drive mode  | 2.5                        | 3.5                        | 4.1                        | 8                         | 25                        | 48                         |      |  |

### Table 30. Typical and maximum current consumption in Standby mode

1. PDR is off for V<sub>DD</sub>=1.7 V. When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2  $\mu$ A

2. Based on characterization, not tested in production unless otherwise specified.

3. Based on characterization, tested in production.

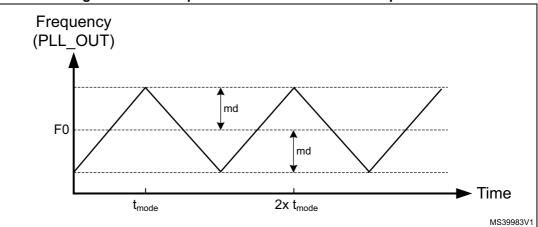

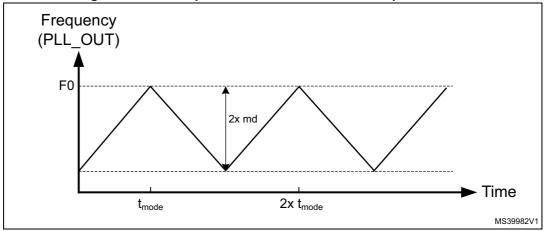

*Figure 35* and *Figure 36* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

$T_{mode}$  is the modulation period. md is the modulation depth.

Figure 36. PLL output clock waveforms in down spread mode

### 5.3.13 MIPI D-PHY characteristics

The parameters given in *Table 45* and *Table 46* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Table 45. MIPI D-PHY characteristics <sup>(1</sup> | Table 45 | MIPI | <b>D-PHY</b> | characteristics( | (1) |

|----------------------------------------------------|----------|------|--------------|------------------|-----|

|----------------------------------------------------|----------|------|--------------|------------------|-----|

| Symbol                                | Parameter        | Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|------------------|------------|-----|-----|------|------|

| Hi-Speed Input/Output Characteristics |                  |            |     |     |      |      |

| U <sub>INST</sub>                     | UI instantaneous | -          | 2   | -   | 12.5 | ns   |

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min                                             | Тур | Мах                | Unit |  |  |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------|-----|--------------------|------|--|--|

|                                               |                                                  |                                                                                 | $C_L$ = 50 pF, $V_{DD} \ge 2.7 V$                           | -                                               | -   | 4                  |      |  |  |

|                                               |                                                  |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 1.7 \text{ V}$             | -                                               | -   | 2                  |      |  |  |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | $C_L$ = 10 pF, $V_{DD} \ge 2.7 V$                           | -                                               | -   | 8                  | MHz  |  |  |

| 00                                            |                                                  |                                                                                 | $C_L = 10 \text{ pF}, V_{DD} \ge 1.8 \text{ V}$             | -                                               | -   | 4                  |      |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 3                  |      |  |  |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V to<br>3.6 V | -                                               | -   | 100                | ns   |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -   | 25                 |      |  |  |

|                                               | f <sub>max(IO)</sub> out                         | ut Maximum frequency <sup>(3)</sup>                                             | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.8 V             | -                                               | -   | 12.5               | MHz  |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 10                 |      |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -   | 50                 |      |  |  |

| 04                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -                                               | -   | 20                 |      |  |  |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 12.5               |      |  |  |

|                                               | t (IO)out/ time                                  |                                                                                 |                                                             | $C_L = 50 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$ | -   | -                  | 10   |  |  |

|                                               |                                                  | Output high to low level fall                                                   | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -   | 6                  | ns   |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 20                 |      |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 10                 | 1    |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -   | 50 <sup>(4)</sup>  |      |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -   | 100 <sup>(4)</sup> | 1    |  |  |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 25                 | MHz  |  |  |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -                                               | -   | 50                 |      |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 42.5               |      |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥2.7 V              | -                                               | -   | 6                  |      |  |  |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -                                               | -   | 4                  |      |  |  |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | $C_L$ = 40 pF, $V_{DD} \ge 1.7 V$                           | -                                               | -   | 10                 | ns   |  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                               | -   | 6                  |      |  |  |

Table 60. I/O AC characteristics<sup>(1)(2)</sup>

### 5.3.22 TIM timer characteristics

The parameters given in *Table 62* are guaranteed by design. Refer to *Section 5.3.20* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                       | Conditions <sup>(3)</sup>                                            | Min | Max                     | Unit                 |

|------------------------|-------------------------------------------------|----------------------------------------------------------------------|-----|-------------------------|----------------------|

| t <sub>res(TIM)</sub>  | Timer resolution time                           | AHB/APBx prescaler=1<br>or 2 or 4, f <sub>TIMxCLK</sub> =<br>180 MHz | 1   | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                 | AHB/APBx prescaler>4,<br>f <sub>TIMxCLK</sub> = 90 MHz               | 1   | -                       | t <sub>TIMxCLK</sub> |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 180 MHz                                       | 0   | f <sub>TIMxCLK</sub> /2 | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                |                                                                      | -   | 16/32                   | bit                  |

| t <sub>MAX_COUNT</sub> | Maximum possible count<br>with 32-bit counter   |                                                                      | -   | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |

| Table 62. TIMx cha | racteristics <sup>(1)(2)</sup> |

|--------------------|--------------------------------|

|--------------------|--------------------------------|

1. TIMx is used as a general term to refer to the TIM1 to TIM12 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 or APB2 is up to 180 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK = 4x PCLKx.

### 5.3.23 Communications interfaces

### I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0386 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 5.3.20 for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 150 <sup>(3)</sup> | ns   |

Table 63. I2C analog filter characteristics<sup>(1)</sup>

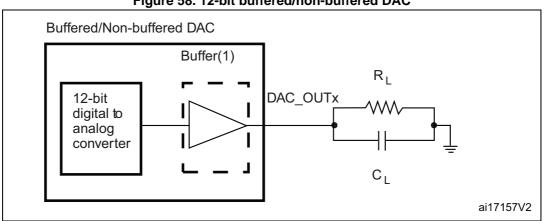

Figure 58. 12-bit buffered/non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register. 1

#### 5.3.29 **FMC** characteristics

Unless otherwise specified, the parameters given in Tables 88 through 101 for the FMC interface are derived from tests performed under the ambient temperature, f<sub>HCLK</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in Table 17, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

Refer to Section 5.3.20 for more details on the input/output characteristics.

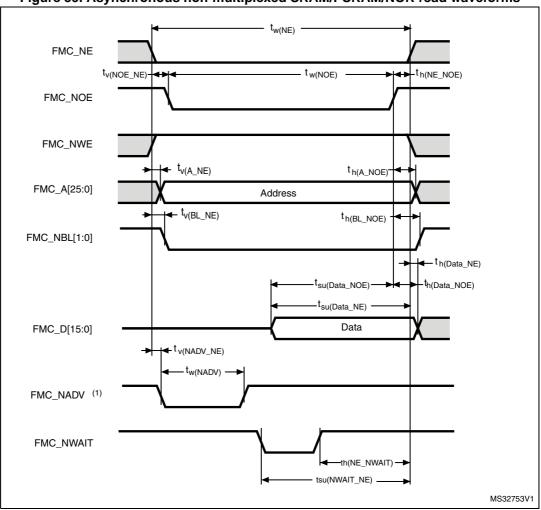

### Asynchronous waveforms and timings

Figures 59 through 62 represent asynchronous waveforms, and Tables 88 through 95 provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode, DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

- Capacitive load  $C_L$  = 30 pF

Figure 59. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

|                           | synchronous non-multiplexed SRAW/P                        |                          | icaa amings              |      |

|---------------------------|-----------------------------------------------------------|--------------------------|--------------------------|------|

| Symbol                    | Parameter                                                 | Min                      | Мах                      | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                                           | 2T <sub>HCLK</sub> – 0.5 | 2 T <sub>HCLK</sub> +0.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low                                | 0                        | 1                        |      |

| t <sub>w(NOE)</sub>       | FMC_NOE low time                                          | 2T <sub>HCLK</sub>       | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                     | 0                        | -                        |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                                | -                        | 2                        |      |

| t <sub>h(A_NOE)</sub>     | h(A_NOE) Address hold time after FMC_NOE high             |                          | -                        |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                               | -                        | 2                        |      |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high                       | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                           | T <sub>HCLK</sub> + 2.5  | -                        |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time                          | T <sub>HCLK</sub> +2     | -                        |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                         | 0                        | -                        |      |

| t <sub>h(Data_NE)</sub>   | t <sub>h(Data_NE)</sub> Data hold time after FMC_NEx high |                          | -                        |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                               | -                        | 0                        | 1    |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                         | -                        | T <sub>HCLK</sub> +1     |      |

Table 88. Asynchronous non-multiplexed SRAM/PSRAM/NOR - read timings<sup>(1)</sup>

1. Based on test during characterization.

| Table 89. Asynchronous non-multiplexed SRAM/PSRAM/NOR read - NWAIT |

|--------------------------------------------------------------------|

| timings <sup>(1)</sup>                                             |

| Symbol                    | Parameter                                 | Min                      | Мах                   | Unit |

|---------------------------|-------------------------------------------|--------------------------|-----------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 7T <sub>HCLK</sub> +0.5  | 7T <sub>HCLK</sub> +1 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> – 1.5 | 5T <sub>HCLK</sub> +2 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> +1.5  | -                     |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1    | -                     |      |

1. Based on test during characterization.

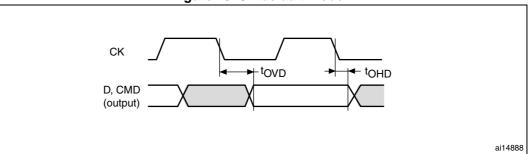

#### Figure 79. SD default mode

|                     | Table 110. Dynamic characteris          | tics: SD / MMC          | character | istics, V <sub>DD</sub> | = 2.7 to 3. | 6 V <sup>(1)</sup> |

|---------------------|-----------------------------------------|-------------------------|-----------|-------------------------|-------------|--------------------|

| Symbol              | Parameter                               | Conditions              | Min       | Тур                     | Max         | Unit               |

| f <sub>PP</sub>     | Clock frequency in data transfer mode   | -                       | 0         | -                       | 50          | MHz                |

| -                   | SDIO_CK/fPCLK2 frequency ratio          | -                       | -         | -                       | 8/3         | -                  |

| t <sub>W(CKL)</sub> | Clock low time                          | f ========              |           | 10.5                    | -           |                    |

| t <sub>W(CKH)</sub> | Clock high time                         | f <sub>pp</sub> =50 MHz | 8.5       | 9.5                     | -           | – ns               |

| CMD, D in           | puts (referenced to CK) in MMC and SE   | OHS mode                |           |                         |             |                    |

| t <sub>ISU</sub>    | Input setup time HS                     | 6 - FO MU-              | 2.0       | -                       | -           |                    |

| t <sub>IH</sub>     | Input hold time HS                      | f <sub>pp</sub> =50 MHz | 2.0       | -                       | -           | ns                 |

| CMD, D ou           | tputs (referenced to CK) in MMC and S   | SD HS mode              |           |                         |             |                    |

| t <sub>OV</sub>     | Output valid time HS                    | £ 50 MUL                | -         | 13                      | 13.5        |                    |

| t <sub>OH</sub>     | Output hold time HS                     | f <sub>pp</sub> =50 MHz | 12.5      | -                       | -           | – ns               |

| CMD, D in           | puts (referenced to CK) in SD default m | node                    |           |                         |             |                    |

| t <sub>ISUD</sub>   | Input setup time SD                     |                         | 2.0       | -                       | -           |                    |

| t <sub>IHD</sub>    | Input hold time SD                      | Input hold time SD      |           | -                       | -           | ns                 |

| CMD, D ou           | tputs (referenced to CK) in SD default  | mode                    |           | -                       |             |                    |

| t <sub>OVD</sub>    | Output valid default time SD            | f -05 ML-               | _         | 1.5                     | 2.0         |                    |

| t <sub>OHD</sub>    | Output hold default time SD             | f <sub>pp</sub> =25 MHz | 1.0       | -                       | -           | – ns               |

1. Guaranteed based on test during characterization.

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |

|--------|--------|-------------|--------|-----------------------|--------|--------|

| Symbol | Min    | Тур         | Max    | Min                   | Тур    | Max    |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| D1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -      | 17.500      | -      | -                     | 0.6890 | -      |

| E      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -      | 17.500      | -      | -                     | 0.6890 | -      |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |

| k      | 0°     | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -      | -           | 0.080  | -                     | -      | 0.0031 |

| Table 114. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package |

|------------------------------------------------------------------------|

| mechanical data                                                        |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

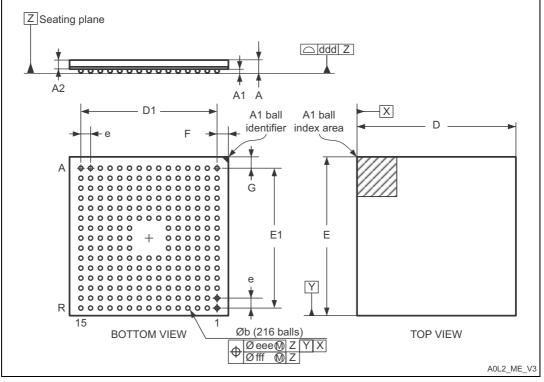

# 6.8 **TFBGA216** package information

Figure 97. TFBGA216 - thin fine pitch ball grid array 13 x 13 x 0.8mm, package outline

1. Drawing is not to scale.

| Table 121. TFBGA216 - thin fine pitch ball grid array 13 × 13 × 0.8mm |

|-----------------------------------------------------------------------|

| package mechanical data                                               |

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |

|--------|--------|-------------|--------|--------|-----------------------|--------|--|

|        | Min    | Тур         | Max    | Min    | Тур                   | Max    |  |

| А      | -      | -           | 1.100  | -      | -                     | 0.0433 |  |

| A1     | 0.150  | -           | -      | 0.0059 | -                     | -      |  |

| A2     | -      | 0.760       | -      | -      | 0.0299                | -      |  |

| A4     | -      | 0.210       | -      | -      | 0.0083                | -      |  |

| b      | 0.350  | 0.400       | 0.450  | 0.0138 | 0.0157                | 0.0177 |  |

| D      | 12.850 | 13.000      | 13.150 | 0.5118 | 0.5118                | 0.5177 |  |

| D1     | -      | 11.200      | -      | -      | 0.4409                | -      |  |

| E      | 12.850 | 13.000      | 13.150 | 0.5118 | 0.5118                | 0.5177 |  |

| E1     | -      | 11.200      | -      | -      | 0.4409                | -      |  |

| е      | -      | 0.800       | -      | -      | 0.0315                | -      |  |

| F      | -      | 0.900       | -      | -      | 0.0354                | -      |  |

| ddd    | -      | -           | 0.080  | -      | -                     | 0.0031 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.